Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 16MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 3                                                                         |

| Program Memory Size        | 896B (512 x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 64 x 8                                                                    |

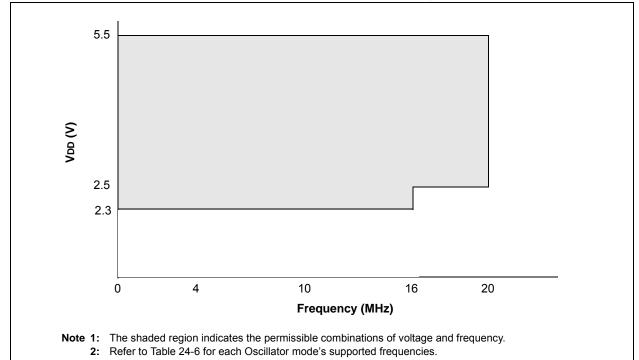

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 3x8b                                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | SOT-23-6                                                                  |

| Supplier Device Package    | SOT-23-6                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic10f322t-i-ot |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Word and Device ID.

#### 3.1 Configuration Word

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word at 2007h.

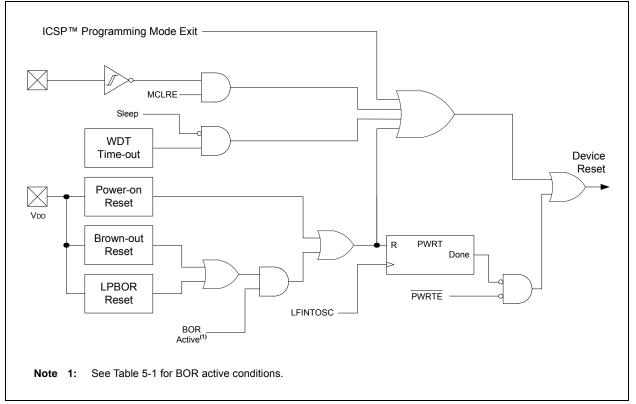

### 5.0 RESETS

There are multiple ways to reset this device:

- Power-On Reset (POR)

- Brown-Out Reset (BOR)

- Low-Power Brown-Out Reset (LPBOR)

- MCLR Reset

- WDT Reset

- · Programming mode exit

To allow VDD to stabilize, an optional Power-up Timer can be enabled to extend the Reset time after a BOR or POR event.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 5-1.

#### FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

#### 5.1 Power-On Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

#### 5.1.1 POWER-UP TIMER (PWRT)

The Power-up Timer provides a nominal 64 ms timeout on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Word.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

#### 5.2 Brown-Out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Word. The four operating modes are:

- BOR is always on

- BOR is off when in Sleep

- · BOR is controlled by software

- · BOR is always off

Refer to Table 5-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Register 3-1.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 5-2 for more information.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Device Operation upon:<br>Release of POR/Wake- up from Sleep |

|------------|--------|-------------|----------|--------------------------------------------------------------|

| 11         | Х      | Х           | Active   | Waits for BOR ready <sup>(1)</sup> (BORRDY = 1)              |

| 1.0        |        | Awake       | Active   | Weite for POP ready (POPPDY = 1)                             |

| 10         | Х      | Sleep       | Disabled | Waits for BOR ready (BORRDY = 1)                             |

| 0.1        | 1      | Х           | Active   | Waits for BOR ready <sup>(1)</sup> (BORRDY = 1)              |

| 01         | 0      | х           | Disabled | Baging immediately (BOBBDY =)                                |

| 00         | Х      | х           | Disabled | Begins immediately (BORRDY = $x$ )                           |

TABLE 5-1: BOR OPERATING MODES

**Note 1:** In these specific cases, "Release of POR" and "Wake-up from Sleep", there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

#### 5.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Word are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

#### 5.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Word are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

#### 5.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Word are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device startup is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

#### 5.4 Low-Power Brown-out Reset (LPBOR)

The Low-Power Brown-Out Reset (LPBOR) is an essential part of the Reset subsystem. Refer to Figure 5-1 to see how the BOR interacts with other modules.

The LPBOR is used to monitor the external VDD pin. When too low of a voltage is detected, the device is held in Reset. When this occurs, a register bit ( $\overline{\text{BOR}}$ ) is changed to indicate that a BOR Reset has occurred. The same bit is set for both the BOR and the LPBOR. Refer to Register 5-2.

#### 5.4.1 ENABLING LPBOR

The LPBOR is controlled by the LPBOR bit of Configuration Word. When the device is erased, the LPBOR module defaults to enabled.

#### 5.4.1.1 LPBOR Module Output

The output of the LPBOR module is a signal indicating whether or not a Reset is to be asserted. This signal is OR'd together with the Reset signal of the BOR module to provide the generic BOR signal which goes to the PCON register and to the power control block.

### 5.5 MCLR

The  $\overline{\text{MCLR}}$  is an optional external input that can reset the device. The  $\overline{\text{MCLR}}$  function is controlled by the MCLRE and the LVP bit of Configuration Word (Table 5-2).

TABLE 5-2: MCLR CONFIGURATION

| MCLRE | LVP | MCLR     |

|-------|-----|----------|

| 0     | 0   | Disabled |

| 1     | 0   | Enabled  |

| x     | 1   | Enabled  |

#### 5.5.1 MCLR ENABLED

When MCLR is enabled and the pin is held low, the device is held in Reset. The MCLR pin is connected to VDD through an internal weak pull-up.

The device has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

```

Note: A Reset does not drive the \overline{\text{MCLR}} pin low.

```

#### 5.5.2 MCLR DISABLED

When MCLR is disabled, the pin functions as a general purpose input and the internal weak pull-up is under software control.

#### 5.6 Watchdog Timer (WDT) Reset

The Watchdog Timer generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The TO and PD bits in the STATUS register are changed to indicate the WDT Reset. See **Section 8.0** "**Watchdog Timer**" for more information.

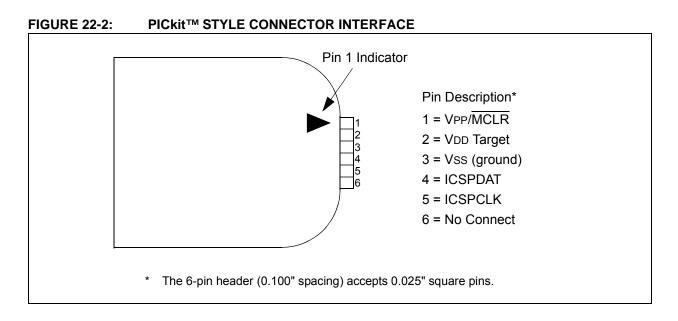

#### 5.7 Programming Mode ICSP Exit

Upon exit of Programming mode, the device will behave as if a POR had just occurred.

#### 5.8 Power-Up Timer

The Power-up Timer optionally delays device execution after a BOR or POR event. This timer is typically used to allow VDD to stabilize before allowing the device to start running.

The Power-up Timer is controlled by the  $\overrightarrow{\text{PWRTE}}$  bit of Configuration Word.

#### 5.9 Start-up Sequence

Upon the release of a POR or BOR, the following must occur before the device will begin executing:

- 1. Power-up Timer runs to completion (if enabled).

- 2. MCLR must be released (if enabled).

The total time-out will vary based on oscillator configuration and Power-up Timer configuration. See **Section 4.0 "Oscillator Module"** for more information.

The Power-up Timer runs independently of MCLR Reset. If MCLR is kept low long enough, the Power-up Timer will expire. Upon bringing MCLR high, the device will begin execution after 10 FOSC cycles (see Figure 5-3). This is useful for testing purposes or to synchronize more than one device operating in parallel.

| Name       | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1  | Bit 0  | Register<br>on Page |

|------------|-------|--------|--------|--------|--------|---------|--------|--------|---------------------|

| INTCON     | GIE   | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF  | INTF   | IOCIF  | 40                  |

| IOCAF      | _     | _      | _      | _      | IOCAF3 | IOCAF2  | IOCAF1 | IOCAF0 | 76                  |

| IOCAN      | _     | _      | _      | _      | IOCAN3 | IOCAN2  | IOCAN1 | IOCAN0 | 75                  |

| IOCAP      | _     | —      | —      | —      | IOCAP3 | IOCAP2  | IOCAP1 | IOCAP0 | 75                  |

| OPTION_REG | WPUEN | INTEDG | TOCS   | T0SE   | PSA    | PS<2:0> |        |        | 95                  |

| PIE1       | _     | ADIE   | _      | NCO1IE | CLC1IE | —       | TMR2IE | -      | 41                  |

| PIR1       |       | ADIF   |        | NCO1IF | CLC1IF | _       | TMR2IF |        | 42                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Interrupts.

#### 7.1.1 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP.

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared.

FIGURE 7-1:

- · If the interrupt occurs during or after the execution of a SLEEP instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

|                      | Q1 Q2 Q3 Q4                                                                                              | Q1 Q2 Q3  Q4                                                       | Q1                                | · ·       | Q1 Q2 Q3 Q4     | Q1 Q2 Q3 Q4       | Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4 |

|----------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------|-----------|-----------------|-------------------|-------------|-------------|

| CLKIN <sup>(1</sup>  |                                                                                                          |                                                                    | ,<br>                             |           |                 |                   |             |             |

| CLKOUT <sup>(2</sup> | )                                                                                                        |                                                                    |                                   | Tost(3)   |                 |                   | <u></u>     |             |

|                      |                                                                                                          |                                                                    | r<br>1                            | · · · · · |                 |                   |             | 1<br>1<br>  |

| Interrupt flag       |                                                                                                          |                                                                    | ·/                                | · · ·     | Interrupt Laten | cy <sup>(4)</sup> |             |             |

| GIE bit              | ii                                                                                                       |                                                                    | Processor in                      | · · ·     |                 |                   |             | 1           |

| (INTCON reg          | ·),                                                                                                      |                                                                    | Sleep                             |           |                 | ·                 | I I         |             |

| struction Flow       |                                                                                                          |                                                                    | ; <u> </u>                        | :         |                 |                   | ;;          |             |

| PC                   | X PC                                                                                                     | ( PC + 1                                                           | X PC                              | + 2       | PC + 2          | PC + 2            | X 0004h     | 0005h       |

| Instruction {        | Inst(PC) = Sleep                                                                                         | Inst(PC + 1)                                                       | 1<br>1<br>1                       | 1         | Inst(PC + 2)    |                   | Inst(0004h) | Inst(0005h) |

| Instruction f        | Inst(PC - 1)                                                                                             | Sleep                                                              | 1<br>1                            | 1         | Inst(PC + 1)    | Forced NOP        | Forced NOP  | Inst(0004h) |

| 3:                   | External clock. Hig<br>CLKOUT is shown<br>Tost= 1024 Tosc;<br><b>Power Brown-out</b><br>GIE = 1 assumed. | here for timing re<br>This delay does no<br><b>Reset (LPBOR)</b> " | ference.<br>ot apply to EC<br>.). | , RC and  |                 |                   |             |             |

WAKE-UP FROM SLEEP THROUGH INTERRUPT

#### TABLE 7-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

| Name   | Bit 7 | Bit 6 | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register on<br>Page |

|--------|-------|-------|------------|-------|-------|-------|-------|--------|---------------------|

| STATUS | IRP   | RP1   | RP0        | TO    | PD    | Z     | DC    | С      | 13                  |

| WDTCON | _     | _     | WDTPS<4:0> |       |       |       |       | SWDTEN | 48                  |

- = unimplemented location, read as '0'. Shaded cells are not used in Power-down mode. Legend:

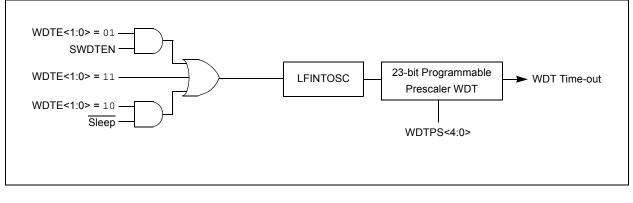

### 8.0 WATCHDOG TIMER

The Watchdog Timer is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events.

The WDT has the following features:

- · Independent clock source

- · Multiple operating modes

- WDT is always on

- WDT is off when in Sleep

- WDT is controlled by software

- WDT is always off

- Configurable time-out period is from 1 ms to 256 seconds (typical)

- Multiple Reset conditions

- Operation during Sleep

#### 8.1 Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1ms. See **Section 24.0 "Electrical Specifications**" for the LFINTOSC tolerances.

#### 8.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Word. See Table 8-1.

#### 8.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Word are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 8.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Word are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

#### 8.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Word are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 8-1 for more details.

#### TABLE 8-1: WDT OPERATING MODES

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |

|-----------|--------|----------------|-------------|

| 11        | Х      | Х              | Active      |

| 10        |        | Awake          | Active      |

| 10        | Х      | Sleep          | Disabled    |

| 0.1       | 1      | х              | Active      |

| 01        | 0      | ~              | Disabled    |

| 00        | х      | Х              | Disabled    |

#### TABLE 8-2:WDT CLEARING CONDITIONS

| Conditions                        | WDT        |  |  |

|-----------------------------------|------------|--|--|

| WDTE<1:0> = 00                    |            |  |  |

| WDTE<1:0> = 01 and SWDTEN = 0     |            |  |  |

| WDTE<1:0> = 10 and enter Sleep    | Cleared    |  |  |

| CLRWDT Command                    |            |  |  |

| Exit Sleep                        |            |  |  |

| Change INTOSC divider (IRCF bits) | Unaffected |  |  |

#### 8.3 Time-Out Period

The WDTPS bits of the WDTCON register set the timeout period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is 2 seconds.

#### 8.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- Any Reset

- CLRWDT instruction is executed

- · Device enters Sleep

- · Device wakes up from Sleep

- Oscillator fail

- WDT is disabled

See Table 8-2 for more information.

#### 8.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. See Section 2.0 "Memory Organization" and *Register 2-1* for more information.

#### 11.6 Interrupt-On-Change Registers

| U-0                                     | U-0 | U-0               | U-0                                                   | R/W-0/0                            | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|-----------------------------------------|-----|-------------------|-------------------------------------------------------|------------------------------------|---------|---------|---------|--|

| —                                       | —   | —                 | —                                                     | IOCAP3                             | IOCAP2  | IOCAP1  | IOCAP0  |  |

| bit 7                                   | •   |                   |                                                       | -                                  |         |         | bit 0   |  |

|                                         |     |                   |                                                       |                                    |         |         |         |  |

| Legend:                                 |     |                   |                                                       |                                    |         |         |         |  |

| R = Readable I                          | bit | W = Writable      | bit                                                   | U = Unimplemented bit, read as '0' |         |         |         |  |

| u = Bit is unchanged x = Bit is unknown |     |                   | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |         |  |

| '1' = Bit is set                        |     | '0' = Bit is clea | ared                                                  |                                    |         |         |         |  |

#### REGISTER 11-1: IOCAP: INTERRUPT-ON-CHANGE PORTA POSITIVE EDGE REGISTER

| bit 7-4 | Unimplemented: Read as '0'. |

|---------|-----------------------------|

|         |                             |

bit 3-0 **IOCAP<3:0>:** Interrupt-on-Change PORTA Positive Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a positive going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.<sup>(1)</sup>

- 0 = Interrupt-on-Change disabled for the associated pin.

**Note 1:** Interrupt-on-change also requires that the IOCIE bit of the INTCON register be set (Register 6-1).

#### REGISTER 11-2: IOCAN: INTERRUPT-ON-CHANGE PORTA NEGATIVE EDGE REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|---------|---------|

| —     | —   | —   | _   | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  |

| bit 7 |     |     |     |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | Unimplemented: Read as '0'. |

|---------|-----------------------------|

|---------|-----------------------------|

bit 3-0

IOCAN<3:0>: Interrupt-on-Change PORTA Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.<sup>(1)</sup>

- 0 = Interrupt-on-Change disabled for the associated pin.

**Note 1:** Interrupt-on-change also requires that the IOCIE bit of the INTCON register be set (Register 6-1).

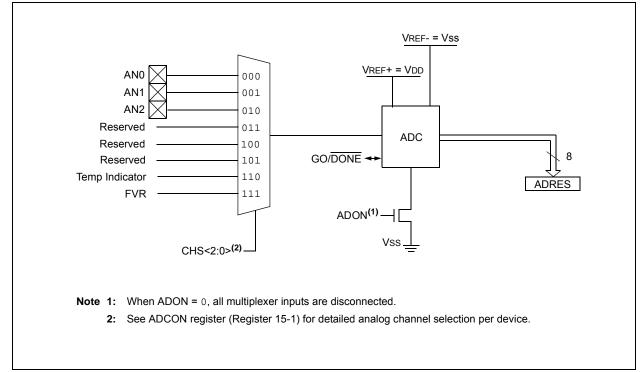

### 15.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) converts an analog input signal to an 8-bit binary representation of that signal. This device uses three analog input channels, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates an 8-bit binary result via successive approximation and stores the conversion result into the ADC result register (ADRES). Figure 15-1 shows the block diagram of the ADC.

The ADC voltage reference is software selectable to be internally generated.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

#### FIGURE 15-1: ADC SIMPLIFIED BLOCK DIAGRAM

#### **15.4** A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 15-3. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 15-3. **The maximum recommended impedance for analog sources is 10 k** $\Omega$ . As the source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an A/D acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 15-1 may be used. This equation assumes that 1/2 LSb error is used (511 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### EQUATION 15-1: ACQUISITION TIME EXAMPLE

sumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega 5.0V$  VDD

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + TC + TCOFF$

$= 2\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

The value for TC can be approximated with the following equations:

$$V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - I}\right) = V_{CHOLD} ; [1] V_{CHOLD} charged to within 1/2 lsb$$

$$V_{APPLIED}\left(1 - e^{\frac{-Tc}{RC}}\right) = V_{CHOLD} ; [2] V_{CHOLD} charge response to V_{APPLIED} (1 - \frac{1}{(2^{n+1}) - I}) ; combining [1] and [2]$$

*Note:* Where n = number of bits of the ADC.

Solving for TC:

As

$$Tc = -CHOLD(RIC + RSS + RS) ln(1/511)$$

=  $-10pF(1k\Omega + 7k\Omega + 10k\Omega) ln(0.001957)$

=  $1.12\mu s$

Therefore:

$$TACQ = 2\mu s + 1.12\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.37\mu s

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is  $10 \text{ k}\Omega$ . This is required to meet the pin leakage specification.

| R/W-1/u              | R/W-1/u                                                                                                                                       | R/W-1/u                                                                                                                                                                                             | R/W-1/u                | R/W-1/u        | R/W-1/u          | R/W-1/u          | R/W-1/u     |  |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------|------------------|------------------|-------------|--|--|

| WPUEN <sup>(1)</sup> | INTEDG                                                                                                                                        | TOCS                                                                                                                                                                                                | T0SE                   | PSA            |                  | PS<2:0>          |             |  |  |

| bit 7                |                                                                                                                                               |                                                                                                                                                                                                     |                        |                |                  |                  | bit 0       |  |  |

|                      |                                                                                                                                               |                                                                                                                                                                                                     |                        |                |                  |                  |             |  |  |

| Legend:              |                                                                                                                                               |                                                                                                                                                                                                     |                        |                |                  |                  |             |  |  |

| R = Readable         | bit                                                                                                                                           | W = Writable                                                                                                                                                                                        | bit                    | •              | mented bit, read |                  |             |  |  |

| u = Bit is uncha     | anged                                                                                                                                         | x = Bit is unkr                                                                                                                                                                                     |                        | -n/n = Value a | at POR and BC    | R/Value at all c | ther Resets |  |  |

| '1' = Bit is set     |                                                                                                                                               | '0' = Bit is cle                                                                                                                                                                                    | ared                   |                |                  |                  |             |  |  |

| bit 7                | WPUEN: Wea                                                                                                                                    | ak Pull-up Enal                                                                                                                                                                                     | ole bit <sup>(1)</sup> |                |                  |                  |             |  |  |

|                      |                                                                                                                                               | l-ups are disab<br>l-ups are enabl                                                                                                                                                                  |                        | al PORT latch  | values           |                  |             |  |  |

| bit 6                | INTEDG: Inte                                                                                                                                  | errupt Edge Sel                                                                                                                                                                                     | ect bit                |                |                  |                  |             |  |  |

|                      |                                                                                                                                               | on rising edge<br>on falling edge                                                                                                                                                                   | •                      |                |                  |                  |             |  |  |

| bit 5                | TOCS: TMR0                                                                                                                                    | 0 Clock Source Select bit                                                                                                                                                                           |                        |                |                  |                  |             |  |  |

|                      |                                                                                                                                               | on T0CKI pin<br>struction cycle                                                                                                                                                                     | clock (Fosc/4          | 4)             |                  |                  |             |  |  |

| bit 4                | TOSE: TMR0                                                                                                                                    | Source Edge S                                                                                                                                                                                       | Select bit             |                |                  |                  |             |  |  |

|                      | <ul> <li>1 = Increment on high-to-low transition on T0CKI pin</li> <li>0 = Increment on low-to-high transition on T0CKI pin</li> </ul>        |                                                                                                                                                                                                     |                        |                |                  |                  |             |  |  |

| bit 3                | PSA: Prescal                                                                                                                                  |                                                                                                                                                                                                     |                        |                |                  |                  |             |  |  |

|                      | <ul> <li>1 = Prescaler is inactive and has no effect on the Timer 0 module</li> <li>0 = Prescaler is assigned to the Timer0 module</li> </ul> |                                                                                                                                                                                                     |                        |                |                  |                  |             |  |  |

| bit 2-0              | <b>PS&lt;2:0&gt;:</b> Pre                                                                                                                     | escaler Rate Se                                                                                                                                                                                     | elect bits             |                |                  |                  |             |  |  |

|                      | Bit                                                                                                                                           | Value TMR0 F                                                                                                                                                                                        | Rate                   |                |                  |                  |             |  |  |

|                      | 0<br>0<br>1<br>1<br>1                                                                                                                         | 000         1:2           001         1:4           100         1:8           011         1:1           000         1:3           001         1:6           10         1:1           10         1:1 | 2<br>4<br>28           |                |                  |                  |             |  |  |

#### REGISTER 16-1: OPTION\_REG: OPTION REGISTER

**Note 1:**  $\overline{\text{WPUEN}}$  does not disable the pull-up for the  $\overline{\text{MCLR}}$  input when  $\overline{\text{MCLR}} = 1$ .

#### TABLE 16-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER0

| Name       | Bit 7                  | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Register on<br>Page |

|------------|------------------------|--------|--------|-------|-------|--------|--------|--------|---------------------|

| INTCON     | GIE                    | PEIE   | TMR0IE | INTE  | IOCIE | TMR0IF | INTF   | IOCIF  | 40                  |

| OPTION_REG | WPUEN                  | INTEDG | TOCS   | T0SE  | PSA   |        | 95     |        |                     |

| TMR0       | Timer0 module Register |        |        |       |       |        |        |        | 40                  |

| TRISA      | —                      | —      | —      | —     | —     | TRISA2 | TRISA1 | TRISA0 | 69                  |

Legend: -= Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Timer0 module.

| Name     | Bit 7                     | Bit 6   | Bit 5   | Bit 4   | Bit 3  | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|----------|---------------------------|---------|---------|---------|--------|---------|---------|---------|---------------------|

| CLC1SEL0 |                           | LC1D2S2 | LC1D2S1 | LC1D2S0 |        | LC1D1S2 | LC1D1S1 | LC1D1S0 | 112                 |

| CLC1SEL1 | _                         | LC1D4S2 | LC1D4S1 | LC1D4S0 | _      | LC1D3S2 | LC1D3S1 | LC1D3S0 | 113                 |

| CWG1CON1 | G1ASDLB<1:0> G1ASDLA<1:0> |         |         | _       | —      | G1IS    | 140     |         |                     |

| INTCON   | GIE                       | PEIE    | TMR0IE  | INTE    | IOCIE  | TMR0IF  | INTF    | IOCIF   | 40                  |

| NCO1ACCH | NCO1ACCH<15:8>            |         |         |         |        |         |         |         | 126                 |

| NCO1ACCL | NCO1ACCL<7:0>             |         |         |         |        |         |         |         | 126                 |

| NCO1ACCU | — NCO1ACCU<19:16          |         |         |         |        |         |         | 126     |                     |

| NCO1CLK  | N1PWS<2:0> —              |         |         | _       | —      | N1CK    | 125     |         |                     |

| NCO1CON  | N1EN                      | N10E    | N1OUT   | N1POL   | _      | —       | -       | N1PFM   | 125                 |

| NCO1INCH | NCO1INCH<15:8>            |         |         |         |        |         |         |         | 127                 |

| NCO1INCL | NCO1INCL<7:0>             |         |         |         |        |         |         |         | 127                 |

| PIE1     | _                         | ADIE    | —       | NCO1IE  | CLC1IE | —       | TMR2IE  | —       | 41                  |

| PIR1     |                           | ADIF    | _       | NCO1IF  | CLC1IF | _       | TMR2IF  | _       | 42                  |

| TRISA    | _                         | _       | _       | _       | _      | TRISA2  | TRISA1  | TRISA0  | 69                  |

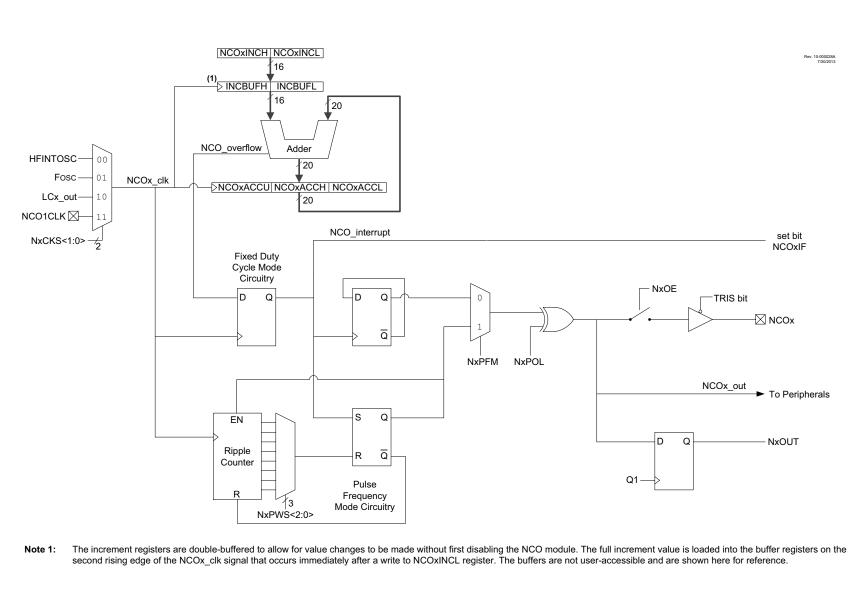

#### TABLE 20-1: SUMMARY OF REGISTERS ASSOCIATED WITH NCOx

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends on condition. Shaded cells are not used for NCO module.

#### 21.0 COMPLEMENTARY WAVEFORM GENERATOR (CWG) MODULE

The Complementary Waveform Generator (CWG) produces a complementary waveform with dead-band delay from a selection of input sources.

The CWG module has the following features:

- · Selectable dead-band clock source control

- Selectable input sources

- Output enable control

- Output polarity control

- Dead-band control with Independent 6-bit rising and falling edge dead-band counters

- Auto-shutdown control with:

- Selectable shutdown sources

- Auto-restart enable

- Auto-shutdown pin override control

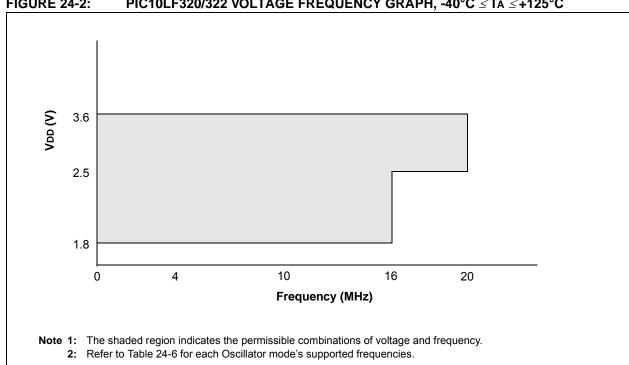

#### **FIGURE 24-2:** PIC10LF320/322 VOLTAGE FREQUENCY GRAPH, -40°C < TA <+125°C

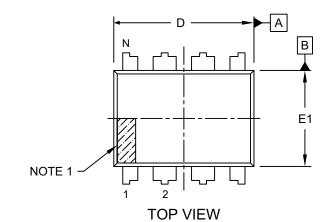

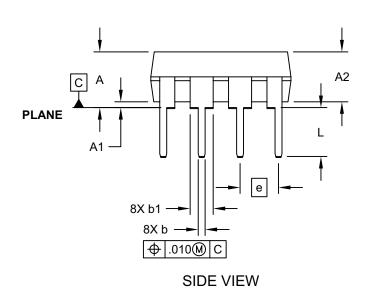

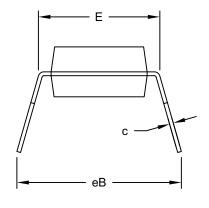

### 8-Lead Plastic Dual In-Line (P) - 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**END VIEW**

Microchip Technology Drawing No. C04-018D Sheet 1 of 2