#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 16MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 3                                                                         |

| Program Memory Size        | 448B (256 x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 64 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 3x8b                                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-VFDFN Exposed Pad                                                       |

| Supplier Device Package    | 8-DFN (2x3)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic10lf320-e-mc |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

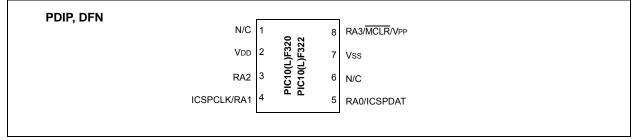

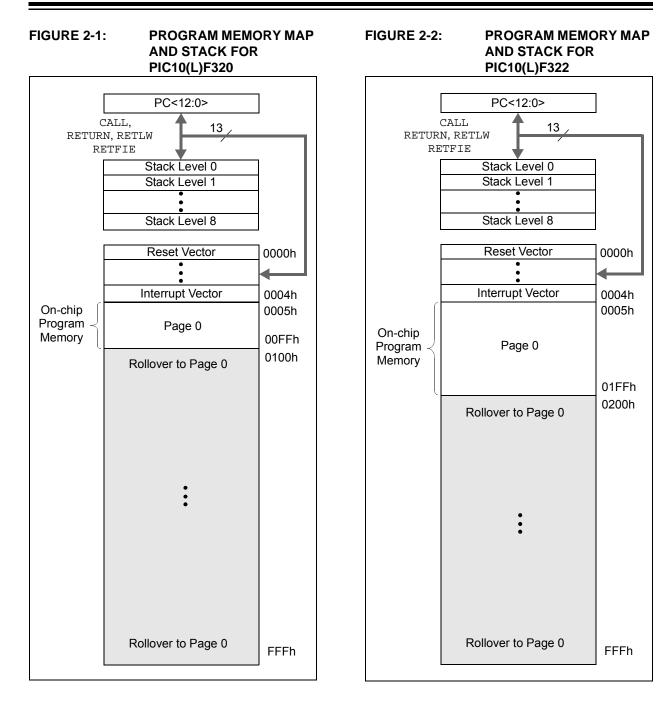

# PIC10(L)F320/322

#### PIC10(L)F320/322 Family Types

| Device       | Data Sheet Index | Program Memory<br>Flash (words) | Data SRAM<br>(bytes) | High Endurance Flash (bytes) | I/O'S <sup>(2)</sup> | 8-Bit ADC (ch) | Timers<br>(8-Bit) | PWM | Complementary Wave<br>Generator (CWG) | Configurable Logic<br>Cell (CLC) | Fixed Voltage<br>Reference (FVR) | Numerically Controlled<br>Oscillator (NCO) | Debug <sup>(1)</sup> | XLP |

|--------------|------------------|---------------------------------|----------------------|------------------------------|----------------------|----------------|-------------------|-----|---------------------------------------|----------------------------------|----------------------------------|--------------------------------------------|----------------------|-----|

| PIC10(L)F320 | (1)              | 256                             | 64                   | 128                          | 4                    | 3              | 2                 | 2   | 1                                     | 1                                | 1                                | 1                                          | Н                    | Y   |

| PIC10(L)F322 | (1)              | 512                             | 64                   | 128                          | 4                    | 3              | 2                 | 2   | 1                                     | 1                                | 1                                | 1                                          | Н                    | Y   |

**Note 1:** I - Debugging, Integrated on Chip; H - Debugging, Available using Debug Header; E - Emulation, Available using Emulation Header.

**2:** One pin is input-only.

#### Data Sheet Index:

1: DS40001585 PIC10(L)F320/322 Data Sheet, 6/8 Pin High Performance, Flash Microcontrollers.

**Note:** For other small form-factor package availability and marking information, please visit http://www.microchip.com/packaging or contact your local sales office.

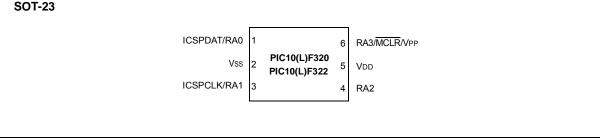

#### FIGURE 1: 6-PIN DIAGRAM, PIC10(L)F320/322

#### SOT-23

#### FIGURE 2: 8-PIN DIAGRAM, PIC10(L)F320/322

#### 6 AND 8-PIN ALLOCATION TABLE, PIC10(L)F320/322 TABLE 1:

| I/O | 6-Pin | 8-Pin | Analog | Timer        | PWM  | Interrupts | Pull-ups | CWG     | NCO     | CLC     | Basic | ICSP    |

|-----|-------|-------|--------|--------------|------|------------|----------|---------|---------|---------|-------|---------|

| RA0 | 1     | 5     | AN0    |              | PWM1 | IOC0       | Y        | CWG1A   |         | CLC1IN0 |       | ICSPDAT |

| RA1 | 3     | 4     | AN1    | _            | PWM2 | IOC1       | Y        | CWG1B   | NCO1CLK | CLC1    | CLKIN | ICSPCLK |

| RA2 | 4     | 3     | AN2    | <b>T0CKI</b> |      | INT/IOC2   | Y        | CWG1FLT | NCO1    | CLC1IN1 | CLKR  |         |

| RA3 | 6     | 8     |        |              |      | IOC3       | Y        | —       |         |         | MCLR  | Vpp     |

| N/C |       | 1     | -      | _            | -    | _          | _        | —       | _       | _       | _     | —       |

| N/C | _     | 6     |        |              |      |            | —        | —       | —       |         | —     | —       |

| Vdd | 5     | 2     | _      | _            | _    | _          | _        | _       | _       |         | Vdd   | _       |

| Vss | 2     | 7     | _      | _            | _    | _          | _        | _       | _       |         | Vss   | _       |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

# PIC10(L)F320/322

#### 3.6 Device ID and Revision ID

The memory location 2006h is where the Device ID and Revision ID are stored. The upper nine bits hold the Device ID. The lower five bits hold the Revision ID. See **Section 9.4 "User ID, Device ID and Configuration Word Access**" for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

### 3.7 Register Definitions: Device and Revision

#### REGISTER 3-2: DEVID: DEVICE ID REGISTER<sup>(1)</sup>

|       |          | R      | R | R   | R        | R | R     |

|-------|----------|--------|---|-----|----------|---|-------|

|       |          |        |   | DEV | <8:3>    |   |       |

|       |          | bit 13 |   |     |          |   | bit 8 |

| R     | R        | R      | R | R   | R        | R | R     |

|       | DEV<2:0> |        |   |     | REV<4:0> |   |       |

| bit 7 |          |        |   |     |          |   | bit 0 |

### Legend:

R = Readable bit '1' = Bit is set

bit 13-5 **DEV<8:0>:** Device ID bits

| Device     | DEVID<13:0> Values |          |  |  |  |  |  |

|------------|--------------------|----------|--|--|--|--|--|

| Device     | DEV<8:0>           | REV<4:0> |  |  |  |  |  |

| PIC10F320  | 10 1001 101        | x xxxx   |  |  |  |  |  |

| PIC10LF320 | 10 1001 111        | x xxxx   |  |  |  |  |  |

| PIC10F322  | 10 1001 100        | x xxxx   |  |  |  |  |  |

| PIC10LF322 | 10 1001 110        | x xxxx   |  |  |  |  |  |

'0' = Bit is cleared

#### bit 4-0 **REV<4:0>:** Revision ID bits

These bits are used to identify the revision.

**Note 1:** This location cannot be written.

# 5.0 RESETS

There are multiple ways to reset this device:

- Power-On Reset (POR)

- Brown-Out Reset (BOR)

- Low-Power Brown-Out Reset (LPBOR)

- MCLR Reset

- WDT Reset

- · Programming mode exit

To allow VDD to stabilize, an optional Power-up Timer can be enabled to extend the Reset time after a BOR or POR event.

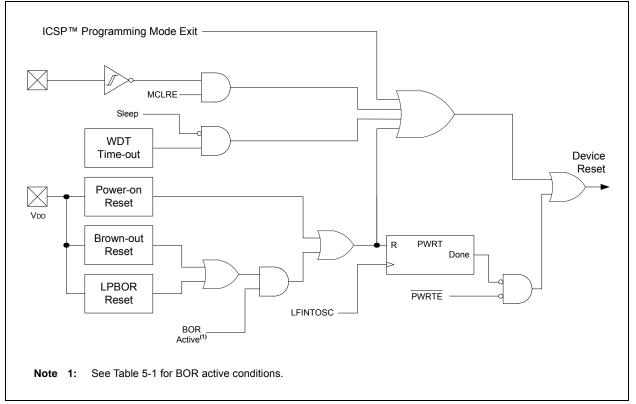

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 5-1.

#### FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

| U-0              | R/W-0/0                                      | U-0                               | R/W-0/0                                                              | R/W-0/0          | U-0              | R/W-0/0           | U-0        |  |  |  |

|------------------|----------------------------------------------|-----------------------------------|----------------------------------------------------------------------|------------------|------------------|-------------------|------------|--|--|--|

|                  | ADIE                                         | —                                 | NCO1IE                                                               | CLC1IE           | —                | TMR2IE            | _          |  |  |  |

| bit 7            |                                              |                                   |                                                                      |                  |                  |                   | bit (      |  |  |  |

|                  |                                              |                                   |                                                                      |                  |                  |                   |            |  |  |  |

| Legend:          |                                              |                                   |                                                                      |                  |                  |                   |            |  |  |  |

| R = Readable     | bit                                          | W = Writable                      | bit                                                                  | U = Unimpler     | nented bit, read | as '0'            |            |  |  |  |

| u = Bit is unch  | anged                                        | x = Bit is unk                    | nown                                                                 | -n/n = Value a   | at POR and BO    | R/Value at all ot | her Resets |  |  |  |

| '1' = Bit is set |                                              | '0' = Bit is cle                  | ared                                                                 |                  |                  |                   |            |  |  |  |

|                  |                                              |                                   |                                                                      |                  |                  |                   |            |  |  |  |

| bit 7            | Unimplemen                                   | ted: Read as '                    | 0'                                                                   |                  |                  |                   |            |  |  |  |

| bit 6            | ADIE: A/D Converter Interrupt Enable bit     |                                   |                                                                      |                  |                  |                   |            |  |  |  |

|                  | 1 = Enables the A/D converter interrupt      |                                   |                                                                      |                  |                  |                   |            |  |  |  |

|                  |                                              | the A/D conve                     |                                                                      |                  |                  |                   |            |  |  |  |

| bit 5            | Unimplemen                                   | ted: Read as '                    | 0'                                                                   |                  |                  |                   |            |  |  |  |

| bit 4            |                                              | •                                 |                                                                      | or Interrupt Ena | ble bit          |                   |            |  |  |  |

|                  |                                              | the NCO overf                     |                                                                      |                  |                  |                   |            |  |  |  |

| 1.11.0           |                                              | the NCO over                      |                                                                      |                  |                  |                   |            |  |  |  |

| bit 3            |                                              | figurable Logic<br>the CLC interr |                                                                      | pt Enable bit    |                  |                   |            |  |  |  |

|                  |                                              | the CLC intern                    |                                                                      |                  |                  |                   |            |  |  |  |

| bit 2            |                                              | ted: Read as '                    | •                                                                    |                  |                  |                   |            |  |  |  |

| bit 1            | -                                            |                                   |                                                                      | nable bit        |                  |                   |            |  |  |  |

|                  |                                              |                                   | 2 to PR2 Match Interrupt Enable bit<br>e TMR2 to PR2 Match interrupt |                  |                  |                   |            |  |  |  |

|                  | 0 = Disables the TMR2 to PR2 Match interrupt |                                   |                                                                      |                  |                  |                   |            |  |  |  |

|                  | Unimplemented: Read as '0'                   |                                   |                                                                      |                  |                  |                   |            |  |  |  |

#### REGISTER 6-2: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

| U-1 <sup>(1</sup>           | ) R/W-0/0                  | R/W-0/0                                                                                                                                             | R/W/HC-0/0     | R/W/HC-0/q <sup>(2)</sup>              | R/W-0/0          | R/S/HC-0/0       | R/S/HC-0/0       |  |  |  |

|-----------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------------------------|------------------|------------------|------------------|--|--|--|

| _                           | CFGS                       | LWLO                                                                                                                                                | FREE           | WRERR                                  | WREN             | WR               | RD               |  |  |  |

| bit 7                       |                            |                                                                                                                                                     |                |                                        |                  |                  | bit C            |  |  |  |

| logondi                     |                            |                                                                                                                                                     |                |                                        |                  |                  |                  |  |  |  |

| L <b>egend:</b><br>R = Read | able bit                   | W = Writable                                                                                                                                        | bit            | U = Unimplemer                         | nted bit. read a | as '0'           |                  |  |  |  |

|                             | in only be set             | x = Bit is unk                                                                                                                                      |                | -n/n = Value at P                      | -                |                  | er Resets        |  |  |  |

| '1' = Bit is                | •                          | '0' = Bit is cle                                                                                                                                    |                | HC = Bit is clear                      |                  |                  |                  |  |  |  |

|                             |                            |                                                                                                                                                     |                |                                        |                  |                  |                  |  |  |  |

| bit 7                       | Unimpleme                  | nted: Read as                                                                                                                                       | '1'            |                                        |                  |                  |                  |  |  |  |

| bit 6                       |                            | iguration Selec                                                                                                                                     |                |                                        |                  |                  |                  |  |  |  |

|                             |                            |                                                                                                                                                     |                | evice ID Registers                     | 5                |                  |                  |  |  |  |

| hit E                       |                            | Flash program                                                                                                                                       | -              |                                        |                  |                  |                  |  |  |  |

| bit 5                       |                            | Write Latches                                                                                                                                       |                | write latch is load                    | led/undated o    | n the next WR (  | ommand           |  |  |  |

|                             |                            |                                                                                                                                                     |                | e latch is loaded/                     |                  |                  |                  |  |  |  |

|                             |                            |                                                                                                                                                     | •              | ext WR command                         |                  | •                | 0                |  |  |  |

| bit 4                       | FREE: Progr                | am Flash Eras                                                                                                                                       | e Enable bit   |                                        |                  |                  |                  |  |  |  |

|                             |                            |                                                                                                                                                     |                | ext WR command                         | l (hardware cl   | eared upon com   | pletion)         |  |  |  |

|                             |                            | -                                                                                                                                                   |                | ext WR command                         |                  |                  |                  |  |  |  |

| bit 3                       |                            | ogram/Erase E                                                                                                                                       | -              |                                        |                  |                  |                  |  |  |  |

|                             |                            |                                                                                                                                                     |                | gram or erase so<br>e '1') of the WR b |                  | npt or terminat  | ion (bit is se   |  |  |  |

|                             |                            |                                                                                                                                                     |                | bleted normally.                       | it).             |                  |                  |  |  |  |

| bit 2                       |                            | ram/Erase Ena                                                                                                                                       |                |                                        |                  |                  |                  |  |  |  |

|                             | -                          | program/erase                                                                                                                                       |                |                                        |                  |                  |                  |  |  |  |

|                             |                            | programming/e                                                                                                                                       |                | am Flash                               |                  |                  |                  |  |  |  |

| bit 1                       | WR: Write C                | ontrol bit                                                                                                                                          |                |                                        |                  |                  |                  |  |  |  |

|                             |                            | a program Flas                                                                                                                                      |                |                                        |                  |                  |                  |  |  |  |

|                             |                            | The operation is self-timed and the bit is cleared by hardware once operation is complete.<br>The WR bit can only be set (not cleared) in software. |                |                                        |                  |                  |                  |  |  |  |

|                             |                            |                                                                                                                                                     |                | is complete and i                      | nactive          |                  |                  |  |  |  |

| bit 0                       | RD: Read Co                | •                                                                                                                                                   |                |                                        | naouvo.          |                  |                  |  |  |  |

|                             |                            |                                                                                                                                                     | sh read. Read  | takes one cycle.                       | RD is cleared    | in hardware. T   | he RD bit ca     |  |  |  |

|                             |                            | set (not cleared                                                                                                                                    |                |                                        |                  |                  |                  |  |  |  |

|                             | 0 = Does no                | ot initiate a prog                                                                                                                                  | ram Flash read | d.                                     |                  |                  |                  |  |  |  |

| Note 1:                     | Unimplemented b            |                                                                                                                                                     |                |                                        |                  |                  |                  |  |  |  |

| 2:                          | The WRERR bit is (WR = 1). | automatically                                                                                                                                       | set by hardwar | e when a program                       | n memory write   | e or erase opera | ition is started |  |  |  |

| э.                          |                            | nored during a                                                                                                                                      |                | on oraca anarati                       |                  | ١                |                  |  |  |  |

#### REGISTER 9-5: PMCON1: PROGRAM MEMORY CONTROL 1 REGISTER

**3:** The LWLO bit is ignored during a program memory erase operation (FREE = 1).

### 10.2 Register Definitions: PORTA

### **REGISTER 10-1: PORTA: PORTA REGISTER**

| U-0   | U-0 | U-0 | U-0 | R-x/x | R/W-x/x | R/W-x/x | R/W-x/x |

|-------|-----|-----|-----|-------|---------|---------|---------|

| —     | —   | —   | —   | RA3   | RA2     | RA1     | RA0     |

| bit 7 |     |     |     |       |         |         | bit 0   |

|       |     |     |     |       |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 RA<3:0>: PORTA I/O Value bits (RA3 is read-only)

**Note 1:** Writes to PORTx are actually written to the corresponding LATx register. Reads from PORTx register return actual I/O pin values.

#### REGISTER 10-2: TRISA: PORTA TRI-STATE REGISTER

| U-0   | U-0 | U-0 | U-0 | U-1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|-----|-----|-----|---------|---------|---------|

| —     | —   | —   | —   | (1) | TRISA2  | TRISA1  | TRISA0  |

| bit 7 |     |     |     |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | Unimplemented: Read as '0'.                                                               |

|---------|-------------------------------------------------------------------------------------------|

| bit 3   | Unimplemented: Read as '1'.                                                               |

| bit 2-0 | TRISA<2:0>: RA<2:0> Port I/O Tri-State Control bits                                       |

|         | <ol> <li>Port output driver is disabled</li> <li>Port output driver is enabled</li> </ol> |

Note 1: Unimplemented, read as '1'.

## 11.0 INTERRUPT-ON-CHANGE

The PORTA pins can be configured to operate as Interrupt-On-Change (IOC) pins. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual PORTA pin, or combination of PORTA pins, can be configured to generate an interrupt. The Interrupt-on-change module has the following features:

- Interrupt-on-Change enable (Master Switch)

- Individual pin configuration

- · Rising and falling edge detection

- Individual pin interrupt flags

Figure 11-1 is a block diagram of the IOC module.

#### 11.1 Enabling the Module

To allow individual PORTA pins to generate an interrupt, the IOCIE bit of the INTCON register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

#### 11.2 Individual Pin Configuration

For each PORTA pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated IOCAPx bit of the IOCAP register is set. To enable a pin to detect a falling edge, the associated IOCANx bit of the IOCAN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting both the IOCAPx bit and the IOCANx bit of the IOCAP and IOCAN registers, respectively.

#### 11.3 Interrupt Flags

The IOCAFx bits located in the IOCAF register are status flags that correspond to the interrupt-on-change pins of PORTA. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the INTCON register reflects the status of all IOCAFx bits.

### 11.4 Clearing Interrupt Flags

The individual status flags, (IOCAFx bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

#### EXAMPLE 11-1: CLEARING INTERRUPT FLAGS

MOVLW 0xff XORWF IOCAF, W ANDWF IOCAF, F

## 11.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the IOCAF register will be updated prior to the first instruction executed out of Sleep.

#### **18.1 PWMx Pin Configuration**

All PWM outputs are multiplexed with the PORT data latch. The user must configure the pins as outputs by clearing the associated TRIS bits.

**Note:** Clearing the PWMxOE bit will relinquish control of the PWMx pin.

#### 18.1.1 FUNDAMENTAL OPERATION

The PWM module produces a 10-bit resolution output. Timer2 and PR2 set the period of the PWM. The PWMxDCL and PWMxDCH registers configure the duty cycle. The period is common to all PWM modules, whereas the duty cycle is independently controlled.

**Note:** The Timer2 postscaler is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

All PWM outputs associated with Timer2 are set when TMR2 is cleared. Each PWMx is cleared when TMR2 is equal to the value specified in the corresponding PWMxDCH (8 MSb) and PWMxDCL<7:6> (2 LSb) registers. When the value is greater than or equal to PR2, the PWM output is never cleared (100% duty cycle).

**Note:** The PWMxDCH and PWMxDCL registers are double buffered. The buffers are updated when Timer2 matches PR2. Care should be taken to update both registers before the timer match occurs.

#### 18.1.2 PWM OUTPUT POLARITY

The output polarity is inverted by setting the PWMxPOL bit of the PWMxCON register.

#### 18.1.3 PWM PERIOD

The PWM period is specified by the PR2 register of Timer2. The PWM period can be calculated using the formula of Equation 18-1.

#### EQUATION 18-1: PWM PERIOD

$PWM Period = [(PR2) + 1] \bullet 4 \bullet Tosc \bullet$ (TMR2 Prescale Value)

Note: Tosc = 1/Fosc

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- · TMR2 is cleared

- The PWM output is active. (Exception: When the PWM duty cycle = 0%, the PWM output will remain inactive.)

- The PWMxDCH and PWMxDCL register values are latched into the buffers.

| Note: | The Timer2 postscaler has no effect on the |

|-------|--------------------------------------------|

|       | PWM operation.                             |

#### 18.1.4 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to the PWMxDCH and PWMxDCL register pair. The PWMxDCH register contains the eight MSbs and the PWMxDCL<7:6>, the two LSbs. The PWMxDCH and PWMxDCL registers can be written to at any time.

Equation 18-2 is used to calculate the PWM pulse width.

Equation 18-3 is used to calculate the PWM duty cycle ratio.

#### EQUATION 18-2: PULSE WIDTH

Pulse Width = (PWMxDCH:PWMxDCL<7:6>) •

TOSC • (TMR2 Prescale Value)

Note: Tosc = 1/Fosc

### EQUATION 18-3: DUTY CYCLE RATIO

$Duty Cycle Ratio = \frac{(PWMxDCH:PWMxDCL<7:6>)}{4(PR2+1)}$

The 8-bit timer TMR2 register is concatenated with the two Least Significant bits of 1/Fosc, adjusted by the Timer2 prescaler to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

#### 18.1.9 SETUP FOR PWM OPERATION USING PWMx PINS

The following steps should be taken when configuring the module for PWM operation using the PWMx pins:

- 1. Disable the PWMx pin output driver(s) by setting the associated TRIS bit(s).

- 2. Clear the PWMxCON register.

- 3. Load the PR2 register with the PWM period value.

- 4. Clear the PWMxDCH register and bits <7:6> of the PWMxDCL register.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register. See Note below.

- Configure the T2CKPS bits of the T2CON register with the Timer2 prescale value.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- Enable PWM output pin and wait until Timer2 overflows, TMR2IF bit of the PIR1 register is set. See Note below.

- Enable the PWMx pin output driver(s) by clearing the associated TRIS bit(s) and setting the PWMxOE bit of the PWMxCON register.

- 8. Configure the PWM module by loading the PWMxCON register with the appropriate values.

- Note 1: In order to send a complete duty cycle and period on the first PWM output, the above steps must be followed in the order given. If it is not critical to start with a complete PWM signal, then move Step 8 to replace Step 4.

- **2:** For operation with other peripherals only, disable PWMx pin outputs.

#### REGISTER 20-3: NCOxACCL: NCOx ACCUMULATOR REGISTER – LOW BYTE

| R/W-0/0        | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0                  | R/W-0/0 | R/W-0/0 |

|----------------|---------|---------|---------|---------|--------------------------|---------|---------|

| _              |         |         | NCOxA   | CC<7:0> |                          |         |         |

| bit 7          |         |         |         |         |                          |         | bit 0   |

|                |         |         |         |         |                          |         |         |

| Legend:        |         |         |         |         |                          |         |         |

| D - Deedekle k | .:.     |         | 1       |         | a a meta al la itura a a | (O'     |         |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 NCOxACC<7:0>: NCOx Accumulator, low byte

Note 1: NxPWS applies only when operating in Pulse Frequency mode.

2: If NCOx pulse width is greater than NCOx overflow period, operation is undefined.

#### REGISTER 20-4: NCOXACCH: NCOX ACCUMULATOR REGISTER – HIGH BYTE

| R/W-0/0 | R/W-0/0       | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|---------|---------------|---------|---------|---------|---------|---------|---------|--|--|

|         | NCOxACC<15:8> |         |         |         |         |         |         |  |  |

| bit 7   | bit 7 bit 0   |         |         |         |         |         |         |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 NCOxACC<15:8>: NCOx Accumulator, high byte

#### REGISTER 20-5: NCOxACCU: NCOx ACCUMULATOR REGISTER – UPPER BYTE

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|----------|---------|

| —     | —   | —   | —   |         | NCOXAC  | C<19:16> |         |

| bit 7 |     |     |     |         |         |          | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 NCOxACC<19:16>: NCOx Accumulator, upper byte

# PIC10(L)F320/322

| Name     | Bit 7         | Bit 6          | Bit 5   | Bit 4   | Bit 3          | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|----------|---------------|----------------|---------|---------|----------------|---------|---------|---------|---------------------|

| CLC1SEL0 |               | LC1D2S2        | LC1D2S1 | LC1D2S0 |                | LC1D1S2 | LC1D1S1 | LC1D1S0 | 112                 |

| CLC1SEL1 | _             | LC1D4S2        | LC1D4S1 | LC1D4S0 | _              | LC1D3S2 | LC1D3S1 | LC1D3S0 | 113                 |

| CWG1CON1 | G1ASD         | LB<1:0>        | G1ASD   | LA<1:0> | _              | —       | G1IS    | <1:0>   | 140                 |

| INTCON   | GIE           | PEIE           | TMR0IE  | INTE    | IOCIE          | TMR0IF  | INTF    | IOCIF   | 40                  |

| NCO1ACCH |               | NCO1ACCH<15:8> |         |         |                |         |         |         | 126                 |

| NCO1ACCL | NCO1ACCL<7:0> |                |         |         |                |         |         | 126     |                     |

| NCO1ACCU |               | -              | _       |         | NCO1ACCU<19:16 |         |         |         | 126                 |

| NCO1CLK  | I             | N1PWS<2:0>     | >       | —       | — — N1CKS<1:0> |         |         | S<1:0>  | 125                 |

| NCO1CON  | N1EN          | N10E           | N1OUT   | N1POL   |                |         | —       | N1PFM   | 125                 |

| NCO1INCH |               |                |         | NCO1IN0 | CH<15:8>       |         |         |         | 127                 |

| NCO1INCL | NCO1INCL<7:0> |                |         |         |                |         |         | 127     |                     |

| PIE1     |               | ADIE           | _       | NCO1IE  | CLC1IE         | _       | TMR2IE  | _       | 41                  |

| PIR1     | _             | ADIF           |         | NCO1IF  | CLC1IF         | —       | TMR2IF  | —       | 42                  |

| TRISA    | _             | _              | _       | _       | _              | TRISA2  | TRISA1  | TRISA0  | 69                  |

#### TABLE 20-1: SUMMARY OF REGISTERS ASSOCIATED WITH NCOx

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends on condition. Shaded cells are not used for NCO module.

#### REGISTER 21-2: CWGxCON1: CWG CONTROL REGISTER 1

| R/W-x/u            | R/W-x/u                                                                                                                                                                                                                                         | R/W-x/u                                                                                                                                                                                                                                                                               | R/W-x/u                                                                                                                                           | U-0                                                                                                                                | U-0                                                                                                            | R/W-0/0                                      | R/W-0/0      |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------|

| GxASDLB<1:0>       |                                                                                                                                                                                                                                                 | GxASDLA<1:0>                                                                                                                                                                                                                                                                          |                                                                                                                                                   |                                                                                                                                    |                                                                                                                | GxIS                                         | <1:0>        |

| bit 7              |                                                                                                                                                                                                                                                 | ·                                                                                                                                                                                                                                                                                     |                                                                                                                                                   |                                                                                                                                    |                                                                                                                |                                              | bit 0        |

|                    |                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                       |                                                                                                                                                   |                                                                                                                                    |                                                                                                                |                                              |              |

| Legend:            |                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                       |                                                                                                                                                   |                                                                                                                                    |                                                                                                                |                                              |              |

| R = Readable       | e bit                                                                                                                                                                                                                                           | W = Writable I                                                                                                                                                                                                                                                                        | oit                                                                                                                                               | U = Unimpler                                                                                                                       | nented bit, read                                                                                               | as '0'                                       |              |

| u = Bit is unch    | nanged                                                                                                                                                                                                                                          | x = Bit is unkn                                                                                                                                                                                                                                                                       | own                                                                                                                                               | -n/n = Value a                                                                                                                     | at POR and BO                                                                                                  | R/Value at all c                             | other Resets |

| '1' = Bit is set   |                                                                                                                                                                                                                                                 | '0' = Bit is clea                                                                                                                                                                                                                                                                     | ared                                                                                                                                              | q = Value dep                                                                                                                      | pends on conditi                                                                                               | ion                                          |              |

| bit 5-4            | 11 = CWGxB<br>10 = CWGxB<br>01 = CWGxB<br>00 = CWGxB<br>control f<br><b>GxASDLA&lt;1</b><br>When an auto<br>00 = CWGxA<br>control f<br>01 = CWGxA<br>10 = CWGxA                                                                                 | 3 pin is driven to<br>3 pin is tri-stated<br>3 pin is tri-stated<br>3 pin is driven to<br>the polarity of th<br>:0>: CWGx Shu<br>o shutdown even<br>a pin is driven to<br>the polarity of th<br>a pin is tri-stated<br>a pin is driven to<br>a pin is driven to<br>a pin is driven to | '1', regardle:<br>'0', regardle:<br>its inactive s<br>e output.<br>utdown State<br>nt is present<br>its inactive s<br>e output.<br>'0', regardle: | ss of the setting<br>ss of the setting<br>tate after the se<br>for CWGxA<br>(GxASE = 1):<br>tate after the se<br>ss of the setting | g of the GxPOLE<br>g of the GxPOLE<br>elected dead-ba<br>elected dead-ba<br>g of the GxPOL/<br>g of the GxPOL/ | 3 bit.<br>Ind interval. G<br>Ind interval. G |              |

| bit 3-2<br>bit 1-0 | <pre>11 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.<br/>Unimplemented: Read as '0'<br/>GxIS&lt;1:0&gt;: CWGx Dead-band Source Select bits<br/>11 = LC1OUT<br/>10 = N1OUT<br/>01 = PWM2OUT<br/>00 = PWM1OUT</pre> |                                                                                                                                                                                                                                                                                       |                                                                                                                                                   |                                                                                                                                    |                                                                                                                |                                              |              |

## 22.0 IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> (ICSP<sup>™</sup>)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the Program Memory, User IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP<sup>TM</sup> refer to the "*PIC10(L)F320/322 Flash Memory Programming Specification*" (DS41572).

#### 22.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

#### 22.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC<sup>®</sup> Flash MCUs to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Word is set to '1', the low-voltage ICSP programming entry is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1. MCLR is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete, MCLR must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section 5.4** "Low-Power **Brown-out Reset (LPBOR)**" for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

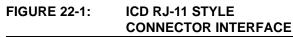

#### 22.3 Common Programming Interfaces

Connection to a target device is typically done through an ICSP<sup>™</sup> header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6 connector) configuration. See Figure 22-1.

Another connector often found in use with the PICkit<sup>™</sup> programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 22-2.

# PIC10(L)F320/322

#### **TABLE 24-4: I/O PORTS**

| Param<br>No. | Sym. | Characteristic                       | Min.              | Тур† | Max.     | Units | Conditions                                       |

|--------------|------|--------------------------------------|-------------------|------|----------|-------|--------------------------------------------------|

|              | VIL  | Input Low Voltage                    |                   |      |          |       |                                                  |

|              |      | I/O PORT:                            |                   |      |          |       |                                                  |

| D032         |      | with TTL buffer                      | —                 | _    | 0.8      | V     | $4.5V \le V\text{DD} \le 5.5V$                   |

| D032A        |      |                                      |                   | _    | 0.15 VDD | V     | $1.8V \leq V\text{DD} \leq 4.5V$                 |

| D033         |      | with Schmitt Trigger buffer          |                   | _    | 0.2 VDD  | V     | $2.0V \le V\text{DD} \le 5.5V$                   |

| D034         |      | MCLR                                 | —                 | _    | 0.2 VDD  | V     |                                                  |

|              | VIH  | Input High Voltage                   | LL                |      |          |       |                                                  |

|              |      | I/O ports:                           |                   |      |          |       |                                                  |

| D040         |      | with TTL buffer                      | 2.0               | _    |          | V     | $4.5V \leq V\text{DD} \leq 5.5V$                 |

| D040A        |      |                                      | 0.25 VDD +<br>0.8 | —    | —        | V     | $1.8V \leq V\text{DD} \leq 4.5V$                 |

| D041         |      | with Schmitt Trigger buffer          | 0.8 VDD           | _    | _        | V     | $2.0V \le V\text{DD} \le 5.5V$                   |

| D042         |      | MCLR                                 | 0.8 VDD           |      | _        | V     |                                                  |

|              | lı∟  | Input Leakage Current <sup>(2)</sup> |                   |      |          |       | I                                                |

| D060         |      | I/O ports                            | —                 | ± 5  | ± 125    | nA    | $VSS \le VPIN \le VDD$ , Pin at                  |

|              |      |                                      |                   |      |          |       | high-impedance @ 85°C                            |

|              |      |                                      |                   | ± 5  | ± 1000   | nA    | 125°C                                            |

| D061         |      | MCLR                                 | —                 | ± 50 | ± 200    | nA    | $VSS \le VPIN \le VDD @ 85^{\circ}C$             |

|              | IPUR | Weak Pull-up Current                 |                   |      | _        | -     |                                                  |

| D070*        |      |                                      | 25                | 100  | 200      |       | VDD = 3.3V, VPIN = VSS                           |

|              |      |                                      | 25                | 140  | 300      | μA    | VDD = 5.0V, VPIN = VSS                           |

|              | VOL  | Output Low Voltage                   | ,                 |      | 1        |       |                                                  |

| D080         |      | I/O ports                            |                   |      | 0.0      | N/    | IOL = 8mA, $VDD = 5V$                            |

|              |      |                                      | —                 | _    | 0.6      | V     | IOL = 6mA, VDD = 3.3V<br>IOL = 1.8mA, VDD = 1.8V |

|              | Voн  | Output High Voltage                  |                   |      |          |       | 10L = 1.011A, VDD = 1.0V                         |

| D090         | VON  | I/O ports                            |                   |      |          |       | ЮН = 3.5mA, VDD = 5V                             |

| 0090         |      |                                      | VDD - 0.7         | _    | _        | V     | 10H = 3.511A, VDD = 5V<br>10H = 3mA, VDD = 3.3V  |

|              |      |                                      |                   |      |          |       | IOH = 1mA, VDD = 1.8V                            |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are t not tested.

Note 1: Negative current is defined as current sourced by the pin.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

#### 24.4 Thermal Considerations

| Stanuar      | Standard Operating Conditions (unless otherwise stated) |                                        |      |       |                                                          |  |  |  |  |

|--------------|---------------------------------------------------------|----------------------------------------|------|-------|----------------------------------------------------------|--|--|--|--|

| Param<br>No. | Sym.                                                    | Characteristic                         | Тур. | Units | Conditions                                               |  |  |  |  |

| TH01         | θJA                                                     | Thermal Resistance Junction to Ambient | 60   | °C/W  | 6-pin SOT-23 package                                     |  |  |  |  |

|              |                                                         |                                        | 80   | °C/W  | 8-pin PDIP package                                       |  |  |  |  |

|              |                                                         |                                        | 90   | °C/W  | 8-pin DFN package                                        |  |  |  |  |

| TH02         | θJC                                                     | Thermal Resistance Junction to Case    | 31.4 | °C/W  | 6-pin SOT-23 package                                     |  |  |  |  |

|              |                                                         |                                        | 24   | °C/W  | 8-pin PDIP package                                       |  |  |  |  |

|              |                                                         |                                        | 24   | °C/W  | 8-pin DFN package                                        |  |  |  |  |

| TH03         | TJMAX                                                   | Maximum Junction Temperature           | 150  | °C    |                                                          |  |  |  |  |

| TH04         | PD                                                      | Power Dissipation                      | _    | W     | PD = PINTERNAL + PI/O                                    |  |  |  |  |

| TH05         | PINTERNAL                                               | Internal Power Dissipation             | _    | W     | PINTERNAL = IDD x VDD <sup>(1)</sup>                     |  |  |  |  |

| TH06         | Pi/o                                                    | I/O Power Dissipation                  | _    | W     | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |  |  |  |  |

| TH07         | Pder                                                    | Derated Power                          | _    | W     | Pder = PDmax (Tj - Ta)/θja <sup>(2)</sup>                |  |  |  |  |

Standard Operating Conditions (unless otherwise stated)

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

2: TA = Ambient Temperature

**3:** T<sub>J</sub> = Junction Temperature

# TABLE 27-1:8-LEAD 2x3 DFN (MC) TOP<br/>MARKING

| Part Number        | Marking |

|--------------------|---------|

| PIC10F322(T)-I/MC  | BAA     |

| PIC10F322(T)-E/MC  | BAB     |

| PIC10F320(T)-I/MC  | BAC     |

| PIC10F320(T)-E/MC  | BAD     |

| PIC10LF322(T)-I/MC | BAF     |

| PIC10LF322(T)-E/MC | BAG     |

| PIC10LF320(T)-I/MC | BAH     |

| PIC10LF320(T)-E/MC | BAJ     |

# TABLE 27-2:6-LEAD SOT-23 (OT)PACKAGE TOP MARKING

| Part Number        | Marking |

|--------------------|---------|

| PIC10F322(T)-I/OT  | LA/LJ   |

| PIC10F322(T)-E/OT  | LB/LK   |

| PIC10F320(T)-I/OT  | LC      |

| PIC10F320(T)-E/OT  | LD      |

| PIC10LF322(T)-I/OT | LE      |

| PIC10LF322(T)-E/OT | LF      |

| PIC10LF320(T)-I/OT | LG      |

| PIC10LF320(T)-E/OT | LH      |

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.                 | [X] <sup>(1)</sup> X     /XX     XXX       T     T     T     T       Tape and Reel Temperature     Package     Pattern       Option     Range | Examples:<br>a) PIC10LF320T - I/OT<br>Tape and Reel.                                                                                                                                                          |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device:                  | PIC10F320, PIC10LF320, PIC10F322, PIC10LF322                                                                                                  | <ul> <li>Industrial temperature,<br/>SOT-23 package</li> <li>b) PIC10F322 - I/P<br/>Industrial temperature<br/>PDIP package</li> <li>c) PIC10F322 - E/MC<br/>Extended temperature,<br/>DFN package</li> </ul> |

| Tape and Reel<br>Option: | Blank = Standard packaging (tube or tray)<br>T = Tape and Reel <sup>(1)</sup>                                                                 |                                                                                                                                                                                                               |

| Temperature<br>Range:    | I = $-40^{\circ}$ C to $+85^{\circ}$ C (Industrial)<br>E = $-40^{\circ}$ C to $+125^{\circ}$ C (Extended)                                     |                                                                                                                                                                                                               |

| Package:                 | OT = SOT-23<br>P = PDIP<br>MC = DFN                                                                                                           | Note 1: Tape and Reel identifier only appears in the catalog part number description. This identifier is used for activity any more and is                                                                    |

| Pattern:                 | QTP, SQTP, Code or Special Requirements (blank otherwise)                                                                                     | identifier is used for ordering purposes and is<br>not printed on the device package. Check<br>with your Microchip Sales Office for package<br>availability with the Tape and Reel option.                    |