Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

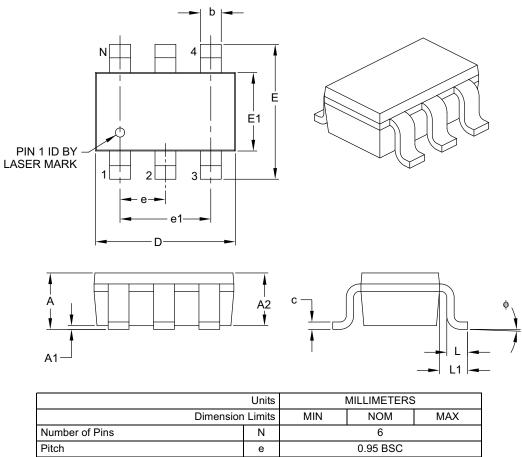

| Product StatusActiveCore ProcessorPICCore Size8-BitSpeed16MHzConnectivity-PeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O3Program Memory Size4488 (256 x 14)Program Memory TypeFLASHEEPROM Size-AtM Size64 x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / CaseSOT-23-6Supplier Device PackageSOT-23-6Purchase URLhttps://www.exfl.com/product-detail/microchip-technology/pic10lf320t-e-ot | Details                    |                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------|

| Core Size8-BitSpeed16MHzConnectivity-PeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O3Program Memory Size448B (256 x 14)Program Memory TypeFLASHEEPROM Size-RAM Size64 x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / CaseSOT-23-6Supplier Device PackageSOT-23-6                                                                                                                           | Product Status             | Active                                                                     |

| Speed16MHzConnectivity-PeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O3Program Memory Size448B (256 x 14)Program Memory TypeFLASHEEPROM Size-RAM Size64 x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / CaseSOT-23-6Supplier Device PackageSOT-23-6                                                                                                                                         | Core Processor             | PIC                                                                        |

| Connectivity-PeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O3Program Memory Size448B (256 x 14)Program Memory TypeFLASHEEPROM Size-RAM Size64 x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / CaseSOT-23-6Surplier Device PackageSOT-23-6                                                                                                                                                   | Core Size                  | 8-Bit                                                                      |

| PeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O3Program Memory Size448B (256 x 14)Program Memory TypeFLASHEEPROM Size-RAM Size64 x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / CaseSOT-23-6SOT-23-6SOT-23-6                                                                                                                                                                               | Speed                      | 16MHz                                                                      |

| Number of I/O3Program Memory Size448B (256 x 14)Program Memory TypeFLASHEEPROM Size-RAM Size64 x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / CaseSOT-23-6Supplier Device PackageSOT-23-6                                                                                                                                                                                                                | Connectivity               | -                                                                          |

| Program Memory Size448B (256 x 14)Program Memory TypeFLASHEEPROM Size-RAM Size64 x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / CaseSOT-23-6Supplier Device PackageSOT-23-6                                                                                                                                                                                                                              | Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Program Memory TypeFLASHEEPROM Size-RAM Size64 x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / CaseSOT-23-6Supplier Device PackageSOT-23-6                                                                                                                                                                                                                                                                | Number of I/O              | 3                                                                          |

| EEPROM Size-RAM Size64 x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / CaseSOT-23-6Supplier Device PackageSOT-23-6                                                                                                                                                                                                                                                                                        | Program Memory Size        | 448B (256 x 14)                                                            |

| RAM Size64 x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / CaseSOT-23-6Supplier Device PackageSOT-23-6                                                                                                                                                                                                                                                                                                    | Program Memory Type        | FLASH                                                                      |

| Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / CaseSOT-23-6Supplier Device PackageSOT-23-6                                                                                                                                                                                                                                                                                                                  | EEPROM Size                | -                                                                          |

| Data ConvertersA/D 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / CaseSOT-23-6Supplier Device PackageSOT-23-6                                                                                                                                                                                                                                                                                                                                                       | RAM Size                   | 64 x 8                                                                     |

| Oscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / CaseSOT-23-6Supplier Device PackageSOT-23-6                                                                                                                                                                                                                                                                                                                                                                              | Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Operating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / CaseSOT-23-6Supplier Device PackageSOT-23-6                                                                                                                                                                                                                                                                                                                                                                                                     | Data Converters            | A/D 3x8b                                                                   |

| Mounting TypeSurface MountPackage / CaseSOT-23-6Supplier Device PackageSOT-23-6                                                                                                                                                                                                                                                                                                                                                                                                                                            | Oscillator Type            | Internal                                                                   |

| Package / Case     SOT-23-6       Supplier Device Package     SOT-23-6                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Supplier Device Package SOT-23-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Mounting Type              | Surface Mount                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Package / Case             | SOT-23-6                                                                   |

| Purchase URL https://www.e-xfl.com/product-detail/microchip-technology/pic10lf320t-e-ot                                                                                                                                                                                                                                                                                                                                                                                                                                    | Supplier Device Package    | SOT-23-6                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic10lf320t-e-ot |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address | Name        | Bit 7     | Bit 6      | Bit 5      | Bit 4         | Bit 3          | Bit 2          | Bit 1         | Bit 0    | Value on<br>POR, BOR | Value on all<br>other resets |

|---------|-------------|-----------|------------|------------|---------------|----------------|----------------|---------------|----------|----------------------|------------------------------|

| Bank 0  | (Continued) |           |            |            |               |                |                |               |          |                      |                              |

| 20h     | PMADRL      |           |            |            | PMA           | ADR<7:0>       |                |               |          | 0000 0000            | 0000 0000                    |

| 21h     | PMADRH      | —         | _          |            | _             |                | _              | _             | PMADR8   | 0                    | (                            |

| 22h     | PMDATL      |           |            |            | PMI           | DAT<7:0>       |                |               |          | xxxx xxxx            | uuuu uuuu                    |

| 23h     | PMDATH      | —         | _          |            | -             | PMD            | AT<13:8>       |               |          | xx xxxx              | uu uuuu                      |

| 24h     | PMCON1      | —         | CFGS       | LWLO       | FREE          | WRERR          | WREN           | WR            | RD       | 1000 0000            | 1000 q000                    |

| 25h     | PMCON2      |           | Pro        | ogram Mem  | ory Control R | egister 2 (not | a physical reg | gister)       |          | 0000 0000            | 0000 0000                    |

| 26h     | CLKRCON     | —         | CLKROE     | —          | —             | —              | —              | —             | —        | -0                   | -0                           |

| 27h     | NCO1ACCL    |           |            |            | NCO1 Acc      | cumulator <7:  | 0>             |               |          | 0000 0000            | 0000 0000                    |

| 28h     | NCO1ACCH    |           |            |            | NCO1 Acc      | umulator <15   | :8>            |               |          | 0000 0000            | 0000 0000                    |

| 29h     | NCO1ACCU    |           | _          | _          |               |                | NCO1 Accum     | ulator <1916> |          | 0000                 | 0000                         |

| 2Ah     | NCO1INCL    |           |            |            | NCO1 In       | crement <7:0>  | >              |               |          | 0000 0001            | 0000 0001                    |

| 2Bh     | NCO1INCH    |           |            |            | NCO1 Inc      | crement <15:8  | >              |               |          | 0000 0000            | 0000 0000                    |

| 2Ch     | —           | Unimpleme | nted       |            |               |                | 1              |               | 1        | —                    | —                            |

| 2Dh     | NCO1CON     | N1EN      | N10E       | N1OUT      | N1POL         |                | _              | —             | N1PFM    | 00000                | 00x00                        |

| 2Eh     | NCO1CLK     |           | N1PWS<2:0> |            | —             | —              | —              | N1CKS         | 6<1:0>   | 00000                | 00000                        |

| 2Fh     | Reserved    |           | <b></b>    |            | R             | eserved        |                |               | 1        | XXXX XXXX            | uuuu uuuu                    |

| 30h     | WDTCON      | —         | —          |            | 1             | WDTPS<4:0      | )>             |               | SWDTEN   | 01 0110              | 01 0110                      |

| 31h     | CLC1CON     | LC1EN     | LC10E      | LC10UT     | LC1INTP       | LC1INTN        | L              | C1MODE<2:0    | >        | 00x0 - 000           | 00x0 -000                    |

| 32h     | CLC1SEL0    | —         | L          | .C1D2S<2:0 | >             | —              |                | LC1D1S<2:0>   |          | -xxx -xxx            | -uuu -uuu                    |

| 33h     | CLC1SEL1    | —         | L          | .C1D4S<2:0 | >             | _              |                | LC1D3S<2:0>   |          | -xxx -xxx            | -uuu -uuu                    |

| 34h     | CLC1POL     | LC1POL    | _          | _          | _             | LC1G4POL       | LC1G3POL       | LC1G2POL      | LC1G1POL | 0 xxxx               | 0 uuuu                       |

| 35h     | CLC1GLS0    | LC1G1D4T  | LC1G1D4N   | LC1G1D3T   | LC1G1D3N      | LC1G1D2T       | LC1G1D2N       | LC1G1D1T      | LC1G1D1N | xxxx xxxx            | uuuu uuuu                    |

| 36h     | CLC1GLS1    | LC1G2D4T  | LC1G2D4N   | LC1G2D3T   | LC1G2D3N      | LC1G2D2T       | LC1G2D2N       | LC1G2D1T      | LC1G2D1N | xxxx xxxx            | uuuu uuuu                    |

| 37h     | CLC1GLS2    | LC1G3D4T  | LC1G3D4N   | LC1G3D3T   | LC1G3D3N      | LC1G3D2T       | LC1G3D2N       | LC1G3D1T      | LC1G3D1N | xxxx xxxx            | uuuu uuuu                    |

| 38h     | CLC1GLS3    | LC1G4D4T  | LC1G4D4N   | LC1G4D3T   | LC1G4D3N      | LC1G4D2T       | LC1G4D2N       | LC1G4D1T      | LC1G4D1N | xxxx xxxx            | uuuu uuuu                    |

| 39h     | CWG1CON0    | G1EN      | G10EB      | G10EA      | G1POLB        | G1POLA         | —              | —             | G1CS0    | 0000 00              | 0000 00                      |

| 3Ah     | CWG1CON1    | G1ASD     | LB<1:0>    | G1ASD      | LA<1:0>       | _              | —              | G1IS<         | <1:0>    | xxxxxx               | uuuuuu                       |

| 3Bh     | CWG1CON2    | G1ASE     | G1ARSEN    | -          | —             | _              | _              | G1ASDCLC1     | G1ASDFLT | xxxx                 | uuuu                         |

| 3Ch     | CWG1DBR     | —         | —          |            |               | CWG1           | DBR<5:0>       | •             | •        | xx xxxx              | uu uuuu                      |

| 3Dh     | CWG1DBF     | —         | —          |            |               | CWG1           | DBF<5:0>       |               |          | xx xxxx              | uu uuuu                      |

| 3Eh     | VREGCON     |           | _          | _          | _             | _              | _              | VREGPM1       | Reserved | 01                   | 01                           |

| 3Fh     | BORCON      | SBOREN    | BORFS      | _          | _             | _              | _              | _             | BORRDY   | 10q                  | uuu                          |

#### SPECIAL FUNCTION REGISTER SUMMARY (BANK 0) (CONTINUED) TABLE 2-3

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: Unimplemented, read as '1'.

# REGISTER 3-1: CONFIG: CONFIGURATION WORD (CONTINUED)

| bit 5   | <b>PWRTE:</b> Power-up Timer Enable bit <sup>(1)</sup><br>1 = PWRT disabled<br>0 = PWRT enabled                                                                                                                                                                                                                            |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4-3 | WDTE<1:0>: Watchdog Timer Enable bit<br>11 = WDT enabled<br>10 = WDT enabled while running and disabled in Sleep<br>01 = WDT controlled by the SWDTEN bit in the WDTCON register<br>00 = WDT disabled                                                                                                                      |

| bit 2-1 | BOREN<1:0>: Brown-out Reset Enable bits<br>11 = Brown-out Reset enabled; SBOREN bit is ignored<br>10 = Brown-out Reset enabled while running, disabled in Sleep; SBOREN bit is ignored<br>01 = Brown-out Reset controlled by the SBOREN bit in the BORCON register<br>00 = Brown-out Reset disabled; SBOREN bit is ignored |

| bit 0   | FOSC: Oscillator Selection bit1 = EC on CLKIN pin0 = INTOSC oscillator I/O function available on CLKIN pin                                                                                                                                                                                                                 |

| Note 1: | Enabling Brown-out Reset does not automatically enable Power-up Timer.                                                                                                                                                                                                                                                     |

- 2: Once enabled, code-protect can only be disabled by bulk erasing the device.

- **3:** See VBOR parameter for specific trip point voltages.

### 6.3 Interrupts During Sleep

Some interrupts can be used to wake from Sleep. To wake from Sleep, the peripheral must be able to operate without the system clock. The interrupt source must have the appropriate Interrupt Enable bit(s) set prior to entering Sleep.

On waking from Sleep, if the GIE bit is also set, the processor will branch to the interrupt vector. Otherwise, the processor will continue executing instructions after the SLEEP instruction. The instruction directly after the SLEEP instruction will always be executed before branching to the ISR. Refer to the Section 7.0 "Power-Down Mode (Sleep)" for more details.

## 6.4 INT Pin

The INT pin can be used to generate an asynchronous edge-triggered interrupt. This interrupt is enabled by setting the INTE bit of the INTCON register. The INTEDG bit of the OPTION\_REG register determines on which edge the interrupt will occur. When the INTEDG bit is set, the rising edge will cause the interrupt. When the INTEDG bit is clear, the falling edge will cause the interrupt. The INTF bit of the INTCON register will be set when a valid edge appears on the INT pin. If the GIE and INTE bits are also set, the processor will redirect program execution to the interrupt vector.

#### 6.5 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (e.g., W and STATUS registers). This must be implemented in software.

Temporary holding registers W\_TEMP and STATUS\_TEMP should be placed in the last 16 bytes of GPR (see Table 1-2). This makes context save and restore operations simpler. The code shown in Example 6-1 can be used to:

- Store the W register

- · Store the STATUS register

- · Execute the ISR code

- Restore the Status (and Bank Select Bit register)

- · Restore the W register

- Note: These devices do not require saving the PCLATH. However, if computed GOTOS are used in both the ISR and the main code, the PCLATH must be saved and restored in the ISR.

#### EXAMPLE 6-1: SAVING STATUS AND W REGISTERS IN RAM

| MOVWF<br>SWAPF | W_TEMP<br>STATUS,W | ;Copy W to TEMP register<br>;Swap status to be saved into W |

|----------------|--------------------|-------------------------------------------------------------|

| MOLTHE         |                    | ;Swaps are used because they do not affect the status bits  |

| MOVWF<br>:     | STATUS_TEMP        | ;Save status to bank zero STATUS_TEMP register              |

| :(ISR)         |                    | ;Insert user code here                                      |

| SWAPF          | STATUS_TEMP,W      | ;Swap STATUS_TEMP register into W                           |

|                |                    | ;(sets bank to original state)                              |

| MOVWF          | STATUS             | ;Move W into STATUS register                                |

| SWAPF          | W_TEMP,F           | ;Swap W_TEMP                                                |

| SWAPF          | W_TEMP,W           | ;Swap W_TEMP into W                                         |

|                |                    |                                                             |

#### 16.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A single software programmable prescaler is available for use with Timer0. The prescaler assignment is controlled by the PSA bit of the OPTION\_REG register. To assign the prescaler to Timer0, the PSA bit must be cleared to a '0'.

There are eight prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION REG register.

The prescaler is not readable or writable. When assigned to the Timer0 module, all instructions writing to the TMR0 register will clear the prescaler.

## 16.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The TMR0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The TMR0IF bit can only be cleared in software. The Timer0 interrupt enable is the TMR0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |  |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|--|

|       | processor from Sleep since the timer is |  |  |  |  |  |  |  |

|       | frozen during Sleep.                    |  |  |  |  |  |  |  |

#### 16.1.5 8-BIT COUNTER MODE SYNCHRONIZATION

When in 8-Bit Counter mode, the incrementing edge on the T0CKI pin must be synchronized to the instruction clock. Synchronization can be accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the instruction clock. The high and low periods of the external clocking source must meet the timing requirements as shown in **Section 24.0** "**Electrical Specifications**".

# 19.2 CLCx Interrupts

An interrupt will be generated upon a change in the output value of the CLCx when the appropriate interrupt enables are set. A rising edge detector and a falling edge detector are present in each CLC for this purpose.

The CLCxIF bit of the associated PIR registers will be set when either edge detector is triggered and its associated enable bit is set. The LCxINTP enables rising edge interrupts and the LCxINTN bit enables falling edge interrupts. Both are located in the CLCxCON register.

To fully enable the interrupt, set the following bits:

- LCxON bit of the CLCxCON register

- CLCxIE bit of the associated PIE registers

- LCxINTP bit of the CLCxCON register (for a rising edge detection)

- LCxINTN bit of the CLCxCON register (for a falling edge detection)

- · PEIE and GIE bits of the INTCON register

The CLCxIF bit of the associated PIR registers must be cleared in software as part of the interrupt service. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

## **19.3** Effects of a Reset

The CLCxCON register is cleared to zero as the result of a Reset. All other selection and gating values remain unchanged.

# **19.4 Operation During Sleep**

The selection, gating, and logic functions are not affected by Sleep. Operation will continue provided that the source signals are also not affected by Sleep.

| U-0                                     | R/W-x/u                                                         | R/W-x/u                                                         | R/W-x/u      | U-0          | R/W-x/u          | R/W-x/u          | R/W-x/u      |  |  |  |  |

|-----------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------|--------------|--------------|------------------|------------------|--------------|--|--|--|--|

| _                                       |                                                                 | LCxD4S<2:0>(1                                                   | )            | —            | L                | _CxD3S<2:0>(1    | )            |  |  |  |  |

| bit 7                                   |                                                                 |                                                                 |              |              |                  |                  | bit 0        |  |  |  |  |

|                                         |                                                                 |                                                                 |              |              |                  |                  |              |  |  |  |  |

| Legend:                                 |                                                                 |                                                                 |              |              |                  |                  |              |  |  |  |  |

| R = Readabl                             | e bit                                                           | W = Writable                                                    | bit          | U = Unimpler | mented bit, read | d as '0'         |              |  |  |  |  |

| u = Bit is unchanged x = Bit is unknown |                                                                 |                                                                 |              | -n/n = Value | at POR and BO    | R/Value at all c | other Resets |  |  |  |  |

| '1' = Bit is se                         | t                                                               | '0' = Bit is clea                                               | ared         |              |                  |                  |              |  |  |  |  |

|                                         |                                                                 |                                                                 |              |              |                  |                  |              |  |  |  |  |

| bit 7                                   | Unimpleme                                                       | ented: Read as '                                                | 0'           |              |                  |                  |              |  |  |  |  |

| bit 6-4                                 | LCxD4S<2                                                        | LCxD4S<2:0>: Input Data 4 Selection Control bits <sup>(1)</sup> |              |              |                  |                  |              |  |  |  |  |

|                                         | 111 = CLCxIN[7] is selected for lcxd4.                          |                                                                 |              |              |                  |                  |              |  |  |  |  |

|                                         | 110 = CLCxIN[6] is selected for lcxd4.                          |                                                                 |              |              |                  |                  |              |  |  |  |  |

|                                         | 101 = CLC                                                       | 101 = CLCxIN[5] is selected for lcxd4                           |              |              |                  |                  |              |  |  |  |  |

|                                         | 100 = CLC                                                       | xIN[4] is selected                                              | d for lcxd4. |              |                  |                  |              |  |  |  |  |

|                                         |                                                                 | xIN[3] is selected                                              |              |              |                  |                  |              |  |  |  |  |

|                                         |                                                                 | 010 = CLCxIN[2] is selected for lcxd4.                          |              |              |                  |                  |              |  |  |  |  |

|                                         |                                                                 | 001 = CLCxIN[1] is selected for lcxd4.                          |              |              |                  |                  |              |  |  |  |  |

|                                         | 000 = CLC                                                       | xIN[0] is selected                                              | d for lcxd4. |              |                  |                  |              |  |  |  |  |

| bit 3                                   | Unimpleme                                                       | ented: Read as '                                                | 0'           |              |                  |                  |              |  |  |  |  |

| bit 2-0                                 | LCxD3S<2:0>: Input Data 3 Selection Control bits <sup>(1)</sup> |                                                                 |              |              |                  |                  |              |  |  |  |  |

|                                         | 111 = CLC                                                       | xIN[7] is selected                                              | d for lcxd3. |              |                  |                  |              |  |  |  |  |

|                                         | 110 = CLC                                                       | 110 = CLCxIN[6] is selected for lcxd3.                          |              |              |                  |                  |              |  |  |  |  |

|                                         | 101 = CLC                                                       | 101 = CLCxIN[5] is selected for lcxd3.                          |              |              |                  |                  |              |  |  |  |  |

|                                         | 100 = CLC                                                       | xIN[4] is selected                                              | d for lcxd3. |              |                  |                  |              |  |  |  |  |

|                                         | 011 = CLC                                                       | xIN[3] is selected                                              | d for lcxd3. |              |                  |                  |              |  |  |  |  |

|                                         | 010 = CLC                                                       | xIN[2] is selected                                              | d for Icxd3. |              |                  |                  |              |  |  |  |  |

|                                         | 001 = CLC                                                       | xIN[1] is selected                                              | d for lcxd3. |              |                  |                  |              |  |  |  |  |

|                                         | 000 = CLC                                                       | xIN[0] is selected                                              | d for lcxd3. |              |                  |                  |              |  |  |  |  |

#### REGISTER 19-4: CLCxSEL1: MULTIPLEXER DATA 3 AND 4 SELECT REGISTER

**Note 1:** See Table 19-1 for signal names associated with inputs.

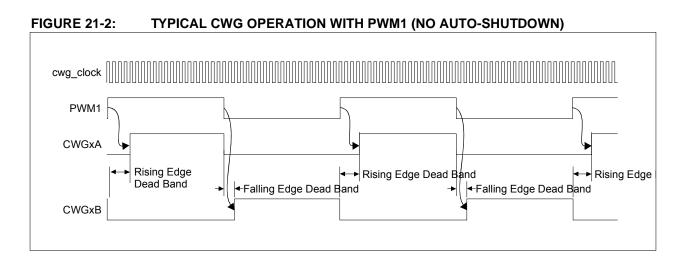

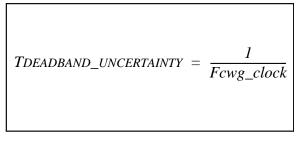

# EQUATION 21-1: DEAD-BAND DELAY TIME UNCERTAINTY

# EXAMPLE 21-1: DEAD-BAND DELAY TIME UNCERTAINTY

$$Fcwg\_clock = 16 MHz$$

Therefore:

$$TDEADBAND\_UNCERTAINTY = \frac{1}{Fcwg\_clock}$$

$$= \frac{1}{16 MHz}$$

$$= 625 ns$$

## 21.9 Auto-shutdown Control

Auto-shutdown is a method to immediately override the CWG output levels with specific overrides that allow for safe shutdown of the circuit. The shutdown state can be either cleared automatically or held until cleared by software.

#### 21.9.1 SHUTDOWN

The Shutdown state can be entered by either of the following two methods:

- Software generated

- External Input

#### 21.9.1.1 Software Generated Shutdown

Setting the GxASE bit of the CWGxCON2 register will force the CWG into the shutdown state.

When auto-restart is disabled, the shutdown state will persist as long as the GxASE bit is set.

When auto-restart is enabled, the GxASE bit will clear automatically and resume operation on the next rising edge event. See Figure 21-6.

#### 21.9.1.2 External Input Source

External shutdown inputs provide the fastest way to safely suspend CWG operation in the event of a Fault condition. When any of the selected shutdown inputs goes high, the CWG outputs will immediately go to the selected override levels without software delay. Any combination of two input sources can be selected to cause a shutdown condition. The two sources are:

- LC10UT

- CWG1FLT

Shutdown inputs are selected using the GxASDS0 and GxASDS1 bits of the CWGxCON2 register. (Register 21-3).

| Note: | Shutdown inputs are level sensitive, not  |

|-------|-------------------------------------------|

|       | edge sensitive. The shutdown state can-   |

|       | not be cleared, except by disabling auto- |

|       | shutdown, as long as the shutdown input   |

|       | level persists.                           |

## 21.10 Operation During Sleep

The CWG module operates independently from the system clock and will continue to run during Sleep, provided that the clock and input sources selected remain active.

The HFINTOSC remains active during Sleep, provided that the CWG module is enabled, the input source is active, and the HFINTOSC is selected as the clock source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and the CWG clock source, when the CWG is enabled and the input source is active, the CPU will go idle during Sleep, but the CWG will continue to operate and the HFINTOSC will remain active.

This will have a direct effect on the Sleep mode current.

# 21.12 CWG Control Registers

| R/W-0/0         | R/W-0/0                    | R/W-0/0                                                                                                              | R/W-0/0      | R/W-0/0        | U-0              | U-0            | R/W-0/0      |  |  |  |  |

|-----------------|----------------------------|----------------------------------------------------------------------------------------------------------------------|--------------|----------------|------------------|----------------|--------------|--|--|--|--|

| GxEN            | GxOEB                      | GxOEA                                                                                                                | GxPOLB       | GxPOLA         | _                | _              | GxCS0        |  |  |  |  |

| bit 7           |                            |                                                                                                                      |              |                |                  |                | bit 0        |  |  |  |  |

|                 |                            |                                                                                                                      |              |                |                  |                |              |  |  |  |  |

| Legend:         |                            |                                                                                                                      |              |                |                  |                |              |  |  |  |  |

| R = Readab      | le bit                     | W = Writable                                                                                                         | bit          | U = Unimplen   | nented bit, read | as '0'         |              |  |  |  |  |

| u = Bit is un   | changed                    | x = Bit is unk                                                                                                       | nown         | -n/n = Value a | at POR and BO    | R/Value at all | other Resets |  |  |  |  |

| '1' = Bit is se | et                         | '0' = Bit is cle                                                                                                     | ared         | q = Value dep  | ends on condit   | ion            |              |  |  |  |  |

|                 |                            |                                                                                                                      |              |                |                  |                |              |  |  |  |  |

| bit 7           | GxEN: CWG                  | x Enable bit                                                                                                         |              |                |                  |                |              |  |  |  |  |

|                 |                            | 1 = Module is enabled                                                                                                |              |                |                  |                |              |  |  |  |  |

|                 | 0 = Module i               |                                                                                                                      |              |                |                  |                |              |  |  |  |  |

| bit 6           |                            | GxOEB: CWGxB Output Enable bit                                                                                       |              |                |                  |                |              |  |  |  |  |

|                 |                            | <ol> <li>CWGxB is available on appropriate I/O pin</li> <li>CWGxB is not available on appropriate I/O pin</li> </ol> |              |                |                  |                |              |  |  |  |  |

| bit 5           |                            |                                                                                                                      |              | le l/O pin     |                  |                |              |  |  |  |  |

| DIL 5           |                            | <b>GxOEA:</b> CWGxA Output Enable bit<br>1 = CWGxA is available on appropriate I/O pin                               |              |                |                  |                |              |  |  |  |  |

|                 |                            | 0 = CWGxA is available on appropriate I/O pin                                                                        |              |                |                  |                |              |  |  |  |  |

| bit 4           |                            | NGxB Output F                                                                                                        |              |                |                  |                |              |  |  |  |  |

|                 |                            | 1 = Output is inverted polarity                                                                                      |              |                |                  |                |              |  |  |  |  |

|                 | 0 = Output is              | s normal polarit                                                                                                     | y            |                |                  |                |              |  |  |  |  |

| bit 3           | GxPOLA: CV                 | NGxA Output F                                                                                                        | olarity bit  |                |                  |                |              |  |  |  |  |

|                 |                            | 1 = Output is inverted polarity                                                                                      |              |                |                  |                |              |  |  |  |  |

|                 |                            | s normal polarit                                                                                                     | •            |                |                  |                |              |  |  |  |  |

| bit 2-1         | Unimplemented: Read as '0' |                                                                                                                      |              |                |                  |                |              |  |  |  |  |

| bit 0           |                            | Gx Clock Source                                                                                                      | e Select bit |                |                  |                |              |  |  |  |  |

|                 | 1 = HFINTO                 | SC                                                                                                                   |              |                |                  |                |              |  |  |  |  |

## REGISTER 21-1: CWGxCON0: CWG CONTROL REGISTER 0

## **REGISTER 21-3:** CWGxCON2: CWG CONTROL REGISTER 2

| R/W/HC/HS-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0   | R/W-0/0  |

|---------------|---------|-----|-----|-----|-----|-----------|----------|

| GxASE         | GxARSEN | —   | _   | —   | _   | GxASDCLC1 | GxASDFLT |

| bit 7         |         |     |     |     |     |           | bit 0    |

| Legend:                     |                      |                                                       |

|-----------------------------|----------------------|-------------------------------------------------------|

| HC = Bit is cleared by hard | lware                | HS = Bit is set by hardware                           |

| R = Readable bit            | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged        | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set            | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | <ul> <li>GxASE: Auto-Shutdown Event Status bit</li> <li>1 = An Auto-Shutdown event has occurred. GxOEB/GxOEA Output Controls overridden, Outputs disabled.</li> <li>0 = No Auto-Shutdown event has occurred, or an Auto-restart has occurred. GxOEB/GxOEA Output Controls enabled.</li> </ul> |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | GxARSEN: Auto-Restart Enable bit<br>1 = Auto-restart is enabled<br>0 = Auto-restart is disabled                                                                                                                                                                                               |

| bit 5-2 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                    |

| bit 1   | <b>GxASDCLC1:</b> CWG Auto-shutdown Source Enable bit 1<br>1 = Shutdown when LC1OUT is high<br>0 = LC1OUT has no effect on shutdown                                                                                                                                                           |

| bit 0   | <b>GxASDFLT:</b> CWG Auto-shutdown Source Enable bit 0<br>1 = <u>Shutdown</u> when CWG1FLT input is low<br>0 = CWG1FLT input has no effect on shutdown                                                                                                                                        |

# REGISTER 21-4: CWGxDBR: COMPLEMENTARY WAVEFORM GENERATOR (CWGx) RISING DEAD-BAND COUNT REGISTER

| U-0                                                                     | U-0 | R/W-x/u      | R/W-x/u      | R/W-x/u      | R/W-x/u          | R/W-x/u     | R/W-x/u |  |  |

|-------------------------------------------------------------------------|-----|--------------|--------------|--------------|------------------|-------------|---------|--|--|

| —                                                                       | _   |              | CWGxDBR<5:0> |              |                  |             |         |  |  |

| bit 7                                                                   |     | ·            |              |              |                  |             | bit 0   |  |  |

|                                                                         |     |              |              |              |                  |             |         |  |  |

| Legend:                                                                 |     |              |              |              |                  |             |         |  |  |

| R = Readable I                                                          | bit | W = Writable | bit          | U = Unimplen | nented bit, read | as '0'      |         |  |  |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Val |     |              |              |              | R/Value at all c | ther Resets |         |  |  |

| '1' = Bit is set '0' = Bit is cleared q = Value depends on condition    |     |              |              |              |                  |             |         |  |  |

|                                                                         |     |              |              |              |                  |             |         |  |  |

bit 7-6 Unimplemented: Read as '0'

| bit 5-0 | CWGxDBR<5:0>: Complementary Waveform Generator (CWGx) Rising Counts bits |

|---------|--------------------------------------------------------------------------|

|         | 11 1111 = 63-64 counts of dead band                                      |

|         | 11 1110 = 62-63 counts of dead band                                      |

|         |                                                                          |

|         | •                                                                        |

- •

- ٠

- 00 0010 = 2-3 counts of dead band

- 00 0001 = 1-2 counts of dead band

00 0000 = 0 counts of dead band

# REGISTER 21-5: CWGxDBF: COMPLEMENTARY WAVEFORM GENERATOR (CWGx) FALLING DEAD-BAND COUNT REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | _   |         |         | CWGxD   | BF<5:0> |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 CWGxDBF<5:0>: Complementary Waveform Generator (CWGx) Falling Counts bits

- 11 1111 = 63-64 counts of dead band

- 11 1110 = 62-63 counts of dead band

- •

- •

- 00 0010 = 2-3 counts of dead band

- 00 0001 = 1-2 counts of dead band

- 00 0000 = 0 counts of dead band. Dead-band generation is bypassed.

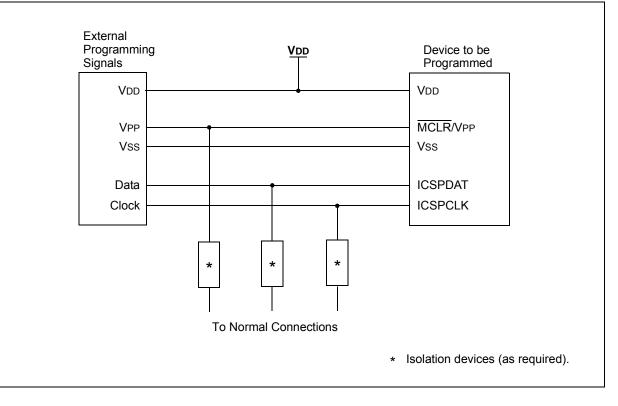

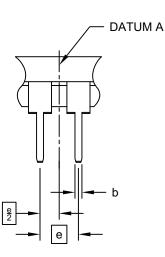

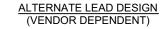

For additional interface recommendations, refer to your specific device programmer manual prior to PCB design.

It is recommended that isolation devices be used to separate the programming pins from other circuitry. The type of isolation is highly dependent on the specific application and may include devices such as resistors, diodes, or even jumpers. See Figure 22-3 for more information.

## FIGURE 22-3: TYPICAL CONNECTION FOR ICSP™ PROGRAMMING

#### TABLE 23-2: INSTRUCTION SET

| Mnemonic,<br>Operands                  |      | Description                  | Cycles       |      | 14-Bit | Opcode | )    | Status   | Notes   |

|----------------------------------------|------|------------------------------|--------------|------|--------|--------|------|----------|---------|

|                                        |      | Description                  | Cycles       | MSb  |        |        | LSb  | Affected | Notes   |

| BYTE-ORIENTED FILE REGISTER OPERATIONS |      |                              |              |      |        |        |      |          |         |

| ADDWF                                  | f, d | Add W and f                  | 1            | 00   | 0111   | dfff   | ffff | C, DC, Z | 1, 2    |

| ANDWF                                  | f, d | AND W with f                 | 1            | 00   | 0101   | dfff   | ffff | Z        | 1, 2    |

| CLRF                                   | f    | Clear f                      | 1            | 00   | 0001   | lfff   | ffff | Z        | 2       |

| CLRW                                   | -    | Clear W                      | 1            | 00   | 0001   | 0xxx   | xxxx | Z        |         |

| COMF                                   | f, d | Complement f                 | 1            | 00   | 1001   | dfff   | ffff | Z        | 1, 2    |

| DECF                                   | f, d | Decrement f                  | 1            | 00   | 0011   | dfff   | ffff | Z        | 1, 2    |

| DECFSZ                                 | f, d | Decrement f, Skip if 0       | 1 <b>(2)</b> | 00   | 1011   | dfff   | ffff |          | 1, 2, 3 |

| INCF                                   | f, d | Increment f                  | 1            | 00   | 1010   | dfff   | ffff | Z        | 1, 2    |

| INCFSZ                                 | f, d | Increment f, Skip if 0       | 1 <b>(2)</b> | 00   | 1111   | dfff   | ffff |          | 1, 2, 3 |

| IORWF                                  | f, d | Inclusive OR W with f        | 1            | 00   | 0100   | dfff   | ffff | Z        | 1, 2    |

| MOVF                                   | f, d | Move f                       | 1            | 00   | 1000   | dfff   | ffff | Z        | 1, 2    |

| MOVWF                                  | f    | Move W to f                  | 1            | 00   | 0000   | lfff   | ffff |          |         |

| NOP                                    | _    | No Operation                 | 1            | 00   | 0000   | 0xx0   | 0000 |          |         |

| RLF                                    | f, d | Rotate Left f through Carry  | 1            | 00   | 1101   | dfff   | ffff | С        | 1, 2    |

| RRF                                    | f, d | Rotate Right f through Carry | 1            | 00   | 1100   | dfff   | ffff | С        | 1, 2    |

| SUBWF                                  | f, d | Subtract W from f            | 1            | 00   | 0010   |        | ffff | C, DC, Z | 1, 2    |

| SWAPF                                  | f, d | Swap nibbles in f            | 1            | 00   | 1110   |        | ffff | -, -,    | 1, 2    |

| XORWF                                  | f, d | Exclusive OR W with f        | 1            | 00   | 0110   | dfff   | ffff | Z        | 1, 2    |

|                                        |      | BIT-ORIENTED FILE F          |              |      | NS     |        |      |          |         |

| BCF                                    | f, b | Bit Clear f                  | 1            | 01   | 00bb   | bfff   | ffff |          | 1, 2    |

| BSF                                    | f, b | Bit Set f                    | 1            | 01   | 01bb   | bfff   |      |          | 1, 2    |

| BTFSC                                  | f, b | Bit Test f, Skip if Clear    | 1 (2)        | 01   | 10bb   |        | ffff |          | 3       |

| BTFSS                                  | f, b | Bit Test f, Skip if Set      | 1 (2)        | 01   | 11bb   | bfff   | ffff |          | 3       |

|                                        | ,    | LITERAL AND CO               | .,           | IONS |        |        |      |          |         |

| ADDLW                                  | k    | Add literal and W            | 1            | 11   | 111x   | kkkk   | kkkk | C, DC, Z |         |

| ANDLW                                  | k    | AND literal with W           | 1            | 11   | 1001   | kkkk   | kkkk | Z        |         |

| CALL                                   | k    | Call Subroutine              | 2            | 10   | 0kkk   | kkkk   | kkkk |          |         |

| CLRWDT                                 | _    | Clear Watchdog Timer         | 1            | 00   | 0000   | 0110   | 0100 | TO, PD   |         |

| GOTO                                   | k    | Go to address                | 2            | 10   | 1kkk   | kkkk   | kkkk |          |         |

| IORLW                                  | k    | Inclusive OR literal with W  | 1            | 11   | 1000   | kkkk   | kkkk | Z        |         |

| MOVLW                                  | k    | Move literal to W            | 1            | 11   | 00xx   | kkkk   | kkkk |          |         |

| RETFIE                                 | _    | Return from interrupt        | 2            | 00   | 0000   | 0000   | 1001 |          |         |

| RETLW                                  | k    | Return with literal in W     | 2            | 11   | 01xx   | kkkk   |      |          |         |

| RETURN                                 | _    | Return from Subroutine       | 2            | 00   | 0000   | 0000   | 1000 |          |         |

| SLEEP                                  | _    | Go into Standby mode         | 1            | 00   | 0000   | 0110   | 0011 | TO, PD   |         |

| SUBLW                                  | k    | Subtract W from literal      | 1            | 11   | 110x   | kkkk   |      | C, DC, Z |         |

| XORLW                                  | k    | Exclusive OR literal with W  | 1            | 11   | 1010   | kkkk   |      | Z        |         |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTA, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

**3:** If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| MOVF             | Move f                                                                                                                                                                                                                                                                                     |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                                  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                         |  |  |  |  |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                                   |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Description:     | The contents of register 'f' is<br>moved to a destination dependent<br>upon the status of 'd'. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register 'f'<br>itself. $d = 1$ is useful to test a file<br>register since Status flag Z is<br>affected. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Example:         | MOVF FSR, 0                                                                                                                                                                                                                                                                                |  |  |  |  |

|                  | After Instruction<br>W = value in FSR<br>register<br>Z = 1                                                                                                                                                                                                                                 |  |  |  |  |

| MOVWF            | Move W to f                                                                                                   |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVWF f                                                                                      |  |  |  |  |

| Operands:        | $0 \leq f \leq 127$                                                                                           |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                                                                                         |  |  |  |  |

| Status Affected: | None                                                                                                          |  |  |  |  |

| Description:     | Move data from W register to<br>register 'f'.                                                                 |  |  |  |  |

| Words:           | 1                                                                                                             |  |  |  |  |

| Cycles:          | 1                                                                                                             |  |  |  |  |

| Example:         | MOVW OPTION_REG<br>F                                                                                          |  |  |  |  |

|                  | Before Instruction<br>$OPTION_REG = 0xFF$<br>W = 0x4F<br>After Instruction<br>$OPTION_REG = 0x4F$<br>W = 0x4F |  |  |  |  |

| MOVLW            | Move literal to W                                                                         |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                         |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                       |  |  |  |  |

| Status Affected: | None                                                                                      |  |  |  |  |

| Description:     | The 8-bit literal 'k' is loaded into W register. The "don't cares" will assemble as '0's. |  |  |  |  |

| Words:           | 1                                                                                         |  |  |  |  |

| Cycles:          | 1                                                                                         |  |  |  |  |

| Example:         | MOVLW 0x5A                                                                                |  |  |  |  |

|                  | After Instruction<br>W = 0x5A                                                             |  |  |  |  |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

| RLF               | Rotate Left f through Carry                                                                                                                                                                                                                                                                          |  |  |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:           | [ <i>label</i> ] RLF f,d                                                                                                                                                                                                                                                                             |  |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                      |  |  |  |  |

| Operation:        | See description below                                                                                                                                                                                                                                                                                |  |  |  |  |

| Status Affected:  | С                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Description:      | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry flag. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is stored<br>back in register 'f'.                                                                                 |  |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Words:            |                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Words:<br>Cycles: | ← C ← Register f ←                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                   | ← C ← Register f ← 1                                                                                                                                                                                                                                                                                 |  |  |  |  |

| Cycles:           | Register f ← C ← Register f ← 1                                                                                                                                                                                                                                                                      |  |  |  |  |

| Cycles:           | REG1 = 1110 0110                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Cycles:           | Register f         I         1         RLF       REG1,0         Before Instruction         REG1       =       1110       0110         C       =       0                                                                                                                                              |  |  |  |  |

| Cycles:           | Register f         1         1         RLF       REG1,0         Before Instruction         REG1       =         C       =       0         After Instruction                                                                                                                                          |  |  |  |  |

| Cycles:           | Register f         C       Register f         1       1         1       RLF       REG1,0         Before Instruction       REG1       =       1110       0110         C       =       0       After Instruction         REG1       =       1110       0110         REG1       =       1110       0110 |  |  |  |  |

| Cycles:           | Register f         1         1         RLF       REG1,0         Before Instruction         REG1       =         C       =       0         After Instruction                                                                                                                                          |  |  |  |  |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                          |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                           |

| Operation:       | See description below                                                                                                                                                                                                 |

| Status Affected: | С                                                                                                                                                                                                                     |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry flag. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is placed<br>back in register 'f'. |

|                  | C Register f                                                                                                                                                                                                          |

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                                     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                        |

| Operands:        | None                                                                                                                                                                                                                                 |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow \underline{W}DT \text{ prescaler}, \\ 1 \rightarrow \underline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                              |

| Status Affected: | TO, PD                                                                                                                                                                                                                               |

| Description:     | The power-down Status bit, $\overline{\text{PD}}$ is cleared. Time-out Status bit, $\overline{\text{TO}}$ is set. Watchdog Timer and its prescaler are cleared.<br>The processor is put into Sleep mode with the oscillator stopped. |

| SUBLW            | Subtract W from literal  |                                                                                  |  |  |  |

|------------------|--------------------------|----------------------------------------------------------------------------------|--|--|--|