# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

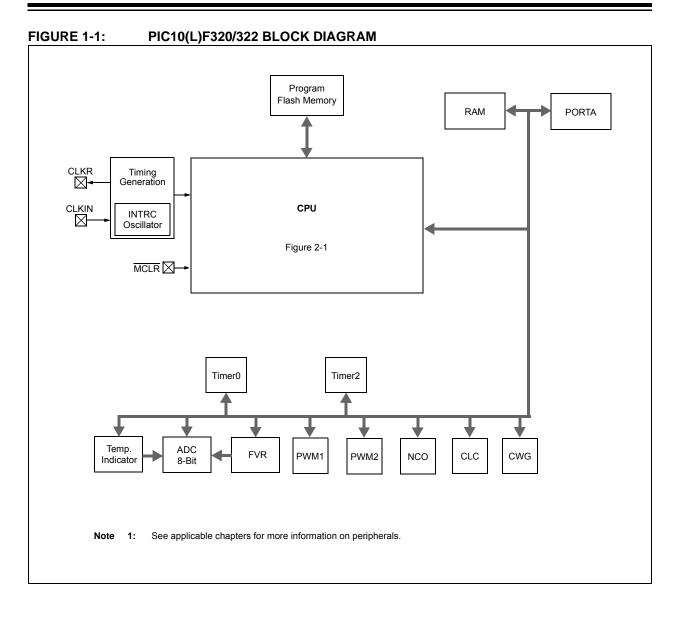

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 16MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 3                                                                        |

| Program Memory Size        | 896B (512 x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | ·                                                                        |

| RAM Size                   | 64 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                              |

| Data Converters            | A/D 3x8b                                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 8-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic10lf322-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

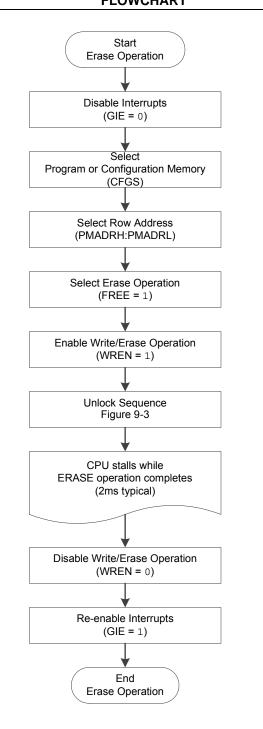

#### 9.2.3 ERASING FLASH PROGRAM MEMORY

While executing code, program memory can only be erased by rows. To erase a row:

- 1. Load the PMADRH:PMADRL register pair with any address within the row to be erased.

- 2. Clear the CFGS bit of the PMCON1 register.

- 3. Set the FREE and WREN bits of the PMCON1 register.

- 4. Write 55h, then AAh, to PMCON2 (Flash programming unlock sequence).

- 5. Set control bit WR of the PMCON1 register to begin the erase operation.

#### See Example 9-2.

After the "BSF PMCON1, WR" instruction, the processor requires two cycles to set up the erase operation. The user must place two NOP instructions after the WR bit is set. The processor will halt internal operations for the typical 2 ms erase time. This is not Sleep mode as the clocks and peripherals will continue to run. After the erase cycle, the processor will resume operation with the third instruction after the PMCON1 write instruction.

#### FIGURE 9-4:

#### FLASH PROGRAM MEMORY ERASE FLOWCHART

#### EXAMPLE 9-2: ERASING ONE ROW OF PROGRAM MEMORY

; This row erase routine assumes the following:

; 1. A valid address within the erase row is loaded in ADDRH:ADDRL

; 2. ADDRH and ADDRL are located in shared data memory  $0\,\mathrm{x}70$  -  $0\,\mathrm{x}7F$  (common RAM)

|                      | BCF<br>BANKSEL<br>MOVF<br>MOVWF<br>MOVWF<br>BCF<br>BSF<br>BSF | INTCON,GIE<br>PMADRL<br>ADDRL,W<br>PMADRL<br>ADDRH,W<br>PMADRH<br>PMCON1,CFGS<br>PMCON1,FREE<br>PMCON1,WREN | <pre>; Disable ints so required sequences will execute properly<br/>; not required on devices with 1 Bank of SFRs<br/>; Load lower 8 bits of erase address boundary<br/>; Load upper 6 bits of erase address boundary<br/>; Not configuration space<br/>; Specify an erase operation<br/>; Enable writes</pre>                                                 |

|----------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Required<br>Sequence | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>BSF<br>NOP<br>NOP         | 55h<br>PMCON2<br>0AAh<br>PMCON2<br>PMCON1,WR                                                                | <pre>; Start of required sequence to initiate erase<br/>; Write 55h<br/>;<br/>; Write AAh<br/>; Set WR bit to begin erase<br/>; NOP instructions are forced as processor starts<br/>; row erase of program memory.<br/>;<br/>;<br/>; The processor stalls until the erase process is complete<br/>; after erase processor continues with 3rd instruction</pre> |

|                      | BCF<br>BSF                                                    | PMCON1,WREN<br>INTCON,GIE                                                                                   | ; Disable writes<br>; Enable interrupts                                                                                                                                                                                                                                                                                                                        |

| W-0/0            | W-0/0    | W-0/0             | W-0/0      | W-0/0          | W-0/0            | W-0/0            | W-0/0        |

|------------------|----------|-------------------|------------|----------------|------------------|------------------|--------------|

|                  |          | Prog              | ram Memory | Control Regist | ter 2            |                  |              |

| bit 7            |          |                   |            |                |                  |                  | bit 0        |

|                  |          |                   |            |                |                  |                  |              |

| Legend:          |          |                   |            |                |                  |                  |              |

| R = Readable     | bit      | W = Writable b    | bit        | U = Unimpler   | nented bit, read | l as '0'         |              |

| S = Bit can onl  | y be set | x = Bit is unkn   | iown       | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set |          | '0' = Bit is clea | ared       |                |                  |                  |              |

## REGISTER 9-6: PMCON2: PROGRAM MEMORY CONTROL 2 REGISTER

#### bit 7-0 Flash Memory Unlock Pattern bits

To unlock writes, a 55h must be written first, followed by an AAh, before setting the WR bit of the PMCON1 register. The value written to this register is used to unlock the writes. There are specific timing requirements on these writes.

#### TABLE 9-3: SUMMARY OF REGISTERS ASSOCIATED WITH FLASH PROGRAM MEMORY

| Name      | Bit 7                | Bit 6 | Bit 5  | Bit 4      | Bit 3         | Bit 2  | Bit 1 | Bit 0  | Register on<br>Page |

|-----------|----------------------|-------|--------|------------|---------------|--------|-------|--------|---------------------|

| INTCON    | GIE                  | PEIE  | TMR0IE | INTE       | IOCIE         | TMR0IF | INTF  | IOCIF  | 40                  |

| PMCON1    | _                    | CFGS  | LWLO   | FREE       | WRERR         | WREN   | WR    | RD     | 65                  |

| PMCON2    |                      |       | Prog   | ram Memory | Control Regis | ster 2 |       |        | 66                  |

| PMADRL    |                      |       |        | PMAD       | R<7:0>        |        |       |        | 64                  |

| PMADRH    | _                    | _     | _      | _          | -             | _      | _     | PMADR8 | 64                  |

| PMDATL    | PMDAT<7:0>           |       |        |            |               |        |       |        | 63                  |

| PMDATH    | — — РМDAT<13:8>      |       |        |            |               |        |       |        | 63                  |

| المسمسيان | s and the set of the |       |        |            |               |        |       |        |                     |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Flash program memory module.

#### TABLE 9-4: SUMMARY OF CONFIGURATION WORD WITH FLASH PROGRAM MEMORY

| Name   | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3  | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|--------|------|---------|---------|----------|----------|-----------|----------|---------|---------|---------------------|

|        | 13:8 |         |         | _        | WRT      | WRT<1:0>  |          | LPBOR   | LVP     | 20                  |

| CONFIG | 7:0  | CP      | MCLR    | PWRTE    | WDTE     | WDTE<1:0> |          | N<1:0>  | FOSC    | 20                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Flash program memory.

# 10.2 Register Definitions: PORTA

# **REGISTER 10-1: PORTA: PORTA REGISTER**

| U-0   | U-0 | U-0 | U-0 | R-x/x | R/W-x/x | R/W-x/x | R/W-x/x |

|-------|-----|-----|-----|-------|---------|---------|---------|

| —     | —   | —   | —   | RA3   | RA2     | RA1     | RA0     |

| bit 7 |     |     |     |       |         |         | bit 0   |

|       |     |     |     |       |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 RA<3:0>: PORTA I/O Value bits (RA3 is read-only)

**Note 1:** Writes to PORTx are actually written to the corresponding LATx register. Reads from PORTx register return actual I/O pin values.

### REGISTER 10-2: TRISA: PORTA TRI-STATE REGISTER

| U-0   | U-0 | U-0 | U-0 | U-1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|-----|-----|-----|---------|---------|---------|

| —     | —   | —   | —   | (1) | TRISA2  | TRISA1  | TRISA0  |

| bit 7 |     |     |     |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | Unimplemented: Read as '0'.                                                               |

|---------|-------------------------------------------------------------------------------------------|

| bit 3   | Unimplemented: Read as '1'.                                                               |

| bit 2-0 | TRISA<2:0>: RA<2:0> Port I/O Tri-State Control bits                                       |

|         | <ol> <li>Port output driver is disabled</li> <li>Port output driver is enabled</li> </ol> |

Note 1: Unimplemented, read as '1'.

### TABLE 10-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|-------|-------|-------|-------|--------|--------|--------|--------|---------------------|

| ANSELA | —     | _     | —     | _     | —      | ANSA2  | ANSA1  | ANSA0  | 70                  |

| IOCAF  | —     | -     | —     | -     | IOCAF3 | IOCAF2 | IOCAF1 | IOCAF0 | 76                  |

| IOCAN  | —     | -     | —     | -     | IOCAN3 | IOCAN2 | IOCAN1 | IOCAN0 | 75                  |

| IOCAP  | —     | -     | —     | -     | IOCAP3 | IOCAP2 | IOCAP1 | IOCAP0 | 75                  |

| LATA   | —     | -     | —     | -     | —      | LATA2  | LATA1  | LATA0  | 70                  |

| PORTA  | —     |       | —     |       | RA3    | RA2    | RA1    | RA0    | 69                  |

| TRISA  | —     | —     | —     | —     | _(1)   | TRISA2 | TRISA1 | TRISA0 | 69                  |

| WPUA   | —     |       | _     |       | WPUA3  | WPUA2  | WPUA1  | WPUA0  | 71                  |

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note 1: Unimplemented, read as '1'.

### TABLE 15-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

| ADC Clock P         | eriod (TAD) | Device Frequency (Fosc)     |                             |                             |                             |  |  |  |

|---------------------|-------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|--|--|--|

| ADC<br>Clock Source | ADCS<2:0>   | 16 MHz                      | 8 MHz                       | 4 MHz                       | 1 MHz                       |  |  |  |

| Fosc/2              | 000         | 125 ns <sup>(1)</sup>       | 250 ns <sup>(1)</sup>       | 500 ns <sup>(1)</sup>       | 2.0 μs                      |  |  |  |

| Fosc/4              | 100         | 250 ns <sup>(1)</sup>       | 500 ns <sup>(1)</sup>       | 1.0 μs                      | 4.0 μs                      |  |  |  |

| Fosc/8              | 001         | 0.5 μs <sup>(1)</sup>       | 1.0 μs                      | 2.0 μs                      | 8.0 μs <sup>(2)</sup>       |  |  |  |

| Fosc/16             | 101         | 1.0 μs                      | 2.0 μs                      | 4.0 μs                      | 16.0 μs <sup>(2)</sup>      |  |  |  |

| Fosc/32             | 010         | 2.0 μs                      | 4.0 μs                      | 8.0 μs <sup>(2)</sup>       | 32.0 μs <sup>(2)</sup>      |  |  |  |

| Fosc/64             | 110         | 4.0 μs                      | 8.0 μs <sup>(2)</sup>       | 16.0 μs <sup>(2)</sup>      | 64.0 μs <sup>(2)</sup>      |  |  |  |

| FRC                 | x11         | 1.0-6.0 μs <sup>(1,3)</sup> | 1.0-6.0 μs <sup>(1,3)</sup> | 1.0-6.0 μs <sup>(1,3)</sup> | 1.0-6.0 μs <sup>(1,3)</sup> |  |  |  |

Legend: Shaded cells are outside of recommended range.

**Note 1:** These values violate the minimum required TAD time.

2: For faster conversion times, the selection of another clock source is recommended.

3: The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock FOSC. However, the FRC clock source must be used when conversions are to be performed with the device in Sleep mode.

## **18.1 PWMx Pin Configuration**

All PWM outputs are multiplexed with the PORT data latch. The user must configure the pins as outputs by clearing the associated TRIS bits.

**Note:** Clearing the PWMxOE bit will relinquish control of the PWMx pin.

#### 18.1.1 FUNDAMENTAL OPERATION

The PWM module produces a 10-bit resolution output. Timer2 and PR2 set the period of the PWM. The PWMxDCL and PWMxDCH registers configure the duty cycle. The period is common to all PWM modules, whereas the duty cycle is independently controlled.

**Note:** The Timer2 postscaler is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

All PWM outputs associated with Timer2 are set when TMR2 is cleared. Each PWMx is cleared when TMR2 is equal to the value specified in the corresponding PWMxDCH (8 MSb) and PWMxDCL<7:6> (2 LSb) registers. When the value is greater than or equal to PR2, the PWM output is never cleared (100% duty cycle).

**Note:** The PWMxDCH and PWMxDCL registers are double buffered. The buffers are updated when Timer2 matches PR2. Care should be taken to update both registers before the timer match occurs.

#### 18.1.2 PWM OUTPUT POLARITY

The output polarity is inverted by setting the PWMxPOL bit of the PWMxCON register.

#### 18.1.3 PWM PERIOD

The PWM period is specified by the PR2 register of Timer2. The PWM period can be calculated using the formula of Equation 18-1.

### EQUATION 18-1: PWM PERIOD

$PWM Period = [(PR2) + 1] \bullet 4 \bullet Tosc \bullet$ (TMR2 Prescale Value)

Note: Tosc = 1/Fosc

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- · TMR2 is cleared

- The PWM output is active. (Exception: When the PWM duty cycle = 0%, the PWM output will remain inactive.)

- The PWMxDCH and PWMxDCL register values are latched into the buffers.

| Note: | The Timer2 postscaler has no effect on the |

|-------|--------------------------------------------|

|       | PWM operation.                             |

#### 18.1.4 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to the PWMxDCH and PWMxDCL register pair. The PWMxDCH register contains the eight MSbs and the PWMxDCL<7:6>, the two LSbs. The PWMxDCH and PWMxDCL registers can be written to at any time.

Equation 18-2 is used to calculate the PWM pulse width.

Equation 18-3 is used to calculate the PWM duty cycle ratio.

### EQUATION 18-2: PULSE WIDTH

Pulse Width = (PWMxDCH:PWMxDCL<7:6>) •

TOSC • (TMR2 Prescale Value)

Note: Tosc = 1/Fosc

# EQUATION 18-3: DUTY CYCLE RATIO

$Duty Cycle Ratio = \frac{(PWMxDCH:PWMxDCL<7:6>)}{4(PR2+1)}$

The 8-bit timer TMR2 register is concatenated with the two Least Significant bits of 1/Fosc, adjusted by the Timer2 prescaler to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

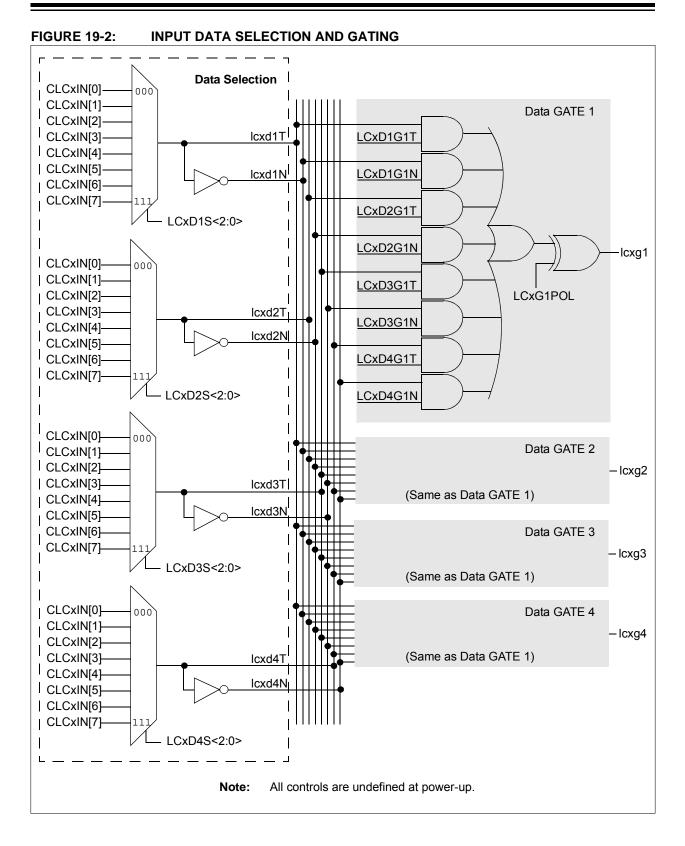

| R/W-x/u          | R/W-x/u                                                                          | R/W-x/u                           | R/W-x/u        | R/W-x/u       | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|------------------|----------------------------------------------------------------------------------|-----------------------------------|----------------|---------------|------------------|------------------|-------------|

| LCxG2D4T         | LCxG2D4N                                                                         | LCxG2D3T                          | LCxG2D3N       | LCxG2D2T      | LCxG2D2N         | LCxG2D1T         | LCxG2D1N    |

| bit 7            |                                                                                  |                                   |                |               |                  |                  | bit 0       |

| Legend:          |                                                                                  |                                   |                |               |                  |                  |             |

| R = Readable I   | ait                                                                              | W = Writable                      | hit            | II – Unimplor | nented bit, read | ac 'O'           |             |

| u = Bit is uncha |                                                                                  | x = Bit is unkn                   |                | -             | at POR and BO    |                  | thor Posote |

| '1' = Bit is set | angeu                                                                            | 6'' = Bit is clear                |                |               | at FOR and BO    | N value at all u | The Resets  |

| I - DILIS SEL    |                                                                                  |                                   | areu           |               |                  |                  |             |

| bit 7            | LCxG2D4T: (                                                                      | Gate 2 Data 4 T                   | rue (non-inver | rted) bit     |                  |                  |             |

|                  | 1 = Icxd4T is                                                                    | gated into lcxg                   | 2              | -             |                  |                  |             |

|                  | 0 = Icxd4T is                                                                    | not gated into                    | lcxg2          |               |                  |                  |             |

| bit 6            | LCxG2D4N:                                                                        | Gate 2 Data 4 I                   | Negated (inver | ted) bit      |                  |                  |             |

|                  |                                                                                  | gated into lcxg                   |                |               |                  |                  |             |

|                  |                                                                                  | not gated into                    | •              |               |                  |                  |             |

| bit 5            |                                                                                  | Gate 2 Data 3 T                   | `              | rted) bit     |                  |                  |             |

|                  |                                                                                  | gated into lcxg<br>not gated into |                |               |                  |                  |             |

| bit 4            |                                                                                  | •                                 | •              | tod) bit      |                  |                  |             |

| DIL 4            | LCxG2D3N: Gate 2 Data 3 Negated (inverted) bit<br>1 = lcxd3N is gated into lcxg2 |                                   |                |               |                  |                  |             |

|                  |                                                                                  | not gated into                    |                |               |                  |                  |             |

| bit 3            |                                                                                  | Gate 2 Data 2 T                   | •              | rted) bit     |                  |                  |             |

|                  |                                                                                  | gated into lcxg                   | ,              | ,             |                  |                  |             |

|                  |                                                                                  | not gated into                    |                |               |                  |                  |             |

| bit 2            | LCxG2D2N:                                                                        | Gate 2 Data 2 I                   | Negated (inver | ted) bit      |                  |                  |             |

|                  |                                                                                  | gated into lcxg                   |                |               |                  |                  |             |

|                  | 0 = Icxd2N is                                                                    | not gated into                    | lcxg2          |               |                  |                  |             |

| bit 1            | LCxG2D1T: 0                                                                      | Gate 2 Data 1 T                   | rue (non-inver | rted) bit     |                  |                  |             |

|                  |                                                                                  | gated into lcxg                   |                |               |                  |                  |             |

|                  |                                                                                  | not gated into                    | •              |               |                  |                  |             |

| bit 0            |                                                                                  | Gate 2 Data 1 M                   | -              | ted) bit      |                  |                  |             |

|                  |                                                                                  | gated into lcxg<br>not gated into |                |               |                  |                  |             |

|                  |                                                                                  | not gated into                    | icxyz          |               |                  |                  |             |

# REGISTER 19-6: CLCxGLS1: GATE 2 LOGIC SELECT REGISTER

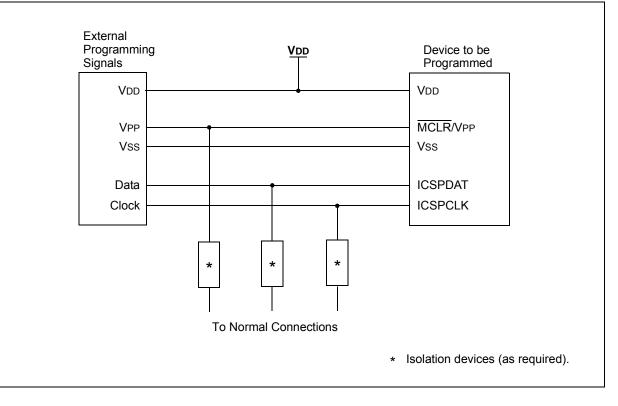

For additional interface recommendations, refer to your specific device programmer manual prior to PCB design.

It is recommended that isolation devices be used to separate the programming pins from other circuitry. The type of isolation is highly dependent on the specific application and may include devices such as resistors, diodes, or even jumpers. See Figure 22-3 for more information.

# FIGURE 22-3: TYPICAL CONNECTION FOR ICSP™ PROGRAMMING

# 24.3 DC Characteristics

# TABLE 24-1: SUPPLY VOLTAGE

| PIC10LF320/322<br>PIC10F320/322 |        |                                                                                  | Standard Operating Conditions (unless otherwise stated) |      |            |        |                                                                                                                                                                                                                                                                                         |  |

|---------------------------------|--------|----------------------------------------------------------------------------------|---------------------------------------------------------|------|------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                 |        |                                                                                  |                                                         |      |            |        |                                                                                                                                                                                                                                                                                         |  |

| Param.<br>No.                   | Sym.   | Characteristic                                                                   | Min.                                                    | Тур† | Max.       | Units  | Conditions                                                                                                                                                                                                                                                                              |  |

| D001 VDD Supply Voltage         |        |                                                                                  |                                                         |      |            |        |                                                                                                                                                                                                                                                                                         |  |

|                                 |        |                                                                                  | 1.8<br>2.5                                              | _    | 3.6<br>3.6 | V<br>V | Fosc ≤ 16 MHz:<br>Fosc ≤ 20 MHz                                                                                                                                                                                                                                                         |  |

| D001                            |        |                                                                                  | 2.3<br>2.5                                              | _    | 5.5<br>5.5 | V<br>V | Fosc ≤ 16 MHz:<br>Fosc ≤ 20 MHz                                                                                                                                                                                                                                                         |  |

| D002*                           | Vdr    | RAM Data Retention Voltage <sup>(1)</sup>                                        |                                                         |      |            |        |                                                                                                                                                                                                                                                                                         |  |

|                                 |        |                                                                                  | 1.5                                                     | _    | —          | V      | Device in Sleep mode                                                                                                                                                                                                                                                                    |  |

| D002*                           |        |                                                                                  | 1.7                                                     | —    | _          | V      | Device in Sleep mode                                                                                                                                                                                                                                                                    |  |

|                                 | VPOR*  | Power-on Reset Release Voltage                                                   | —                                                       | 1.6  | _          | V      |                                                                                                                                                                                                                                                                                         |  |

|                                 | VPORR* | Power-on Reset Rearm Voltage                                                     | —                                                       | 0.8  | _          | V      | Device in Sleep mode                                                                                                                                                                                                                                                                    |  |

|                                 |        |                                                                                  | —                                                       | 1.7  | _          | V      | Device in Sleep mode                                                                                                                                                                                                                                                                    |  |

| D003                            | VFVR   | Fixed Voltage Reference Voltage                                                  |                                                         |      |            |        |                                                                                                                                                                                                                                                                                         |  |

|                                 |        | 1x gain (1.024V nominal)<br>2x gain (2.048V nominal)<br>4x gain (4.096V nominal) | -8                                                      | _    | +6         | %      | $ \begin{array}{l} V{\rm DD} \geq 2.5V, \ -40^{\circ}{\rm C} \leq {\rm TA} \leq +85^{\circ}{\rm C} \\ V{\rm DD} \geq 2.5V, \ -40^{\circ}{\rm C} \leq {\rm TA} \leq +85^{\circ}{\rm C} \\ V{\rm DD} \geq 4.75V, \ -40^{\circ}{\rm C} \leq {\rm TA} \leq +85^{\circ}{\rm C} \end{array} $ |  |

| D004*                           | SVDD   | VDD Rise Rate to ensure internal<br>Power-on Reset signal                        | 0.05                                                    | _    | —          | V/ms   | See Section 5.1 "Power-On Reset (POR)" for details.                                                                                                                                                                                                                                     |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

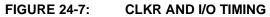

| TABLE 24-8: 0 | CLKR AND I/O | <b>TIMING PARAMETERS</b> |

|---------------|--------------|--------------------------|

|---------------|--------------|--------------------------|

| Standar       | Standard Operating Conditions (unless otherwise stated) |                                                             |               |          |          |       |                                                                      |

|---------------|---------------------------------------------------------|-------------------------------------------------------------|---------------|----------|----------|-------|----------------------------------------------------------------------|

| Param.<br>No. | Sym.                                                    | Characteristic                                              | Min.          | Тур†     | Max.     | Units | Conditions                                                           |

| OS11          | TosH2ckL                                                | Fosc↑ to CLKOUT↓ <sup>(1)</sup>                             | _             | —        | 70       | ns    | $3.3V \le V\text{DD} \le 5.0V$                                       |

| OS12          | TosH2ckH                                                | Fosc↑ to CLKOUT↑ <sup>(1)</sup>                             | _             | —        | 72       | ns    | $3.3V \le V\text{DD} \le 5.0V$                                       |

| OS13          | TckL2ioV                                                | CLKOUT↓ to Port out valid <sup>(1)</sup>                    | —             | _        | 20       | ns    |                                                                      |

| OS14          | TioV2ckH                                                | Port input valid before CLKOUT <sup>(1)</sup>               | Tosc + 200 ns | —        | _        | ns    |                                                                      |

| OS15          | TosH2ioV                                                | Fosc↑ (Q1 cycle) to Port out valid                          | —             | 50       | 70*      | ns    | $3.3V \le V\text{DD} \le 5.0V$                                       |

| OS16          | TosH2iol                                                | Fosc↑ (Q2 cycle) to Port input invalid (I/O in setup time)  | 50            | _        | —        | ns    | $3.3V \le V\text{DD} \le 5.0V$                                       |

| OS17          | TioV2osH                                                | Port input valid to Fosc↑ (Q2 cycle)<br>(I/O in setup time) | 20            | —        | —        | ns    |                                                                      |

| OS18*         | TioR                                                    | Port output rise time                                       |               | 40<br>15 | 72<br>32 | ns    | $\begin{array}{l} VDD = 1.8V \\ 3.3V \leq VDD \leq 5.0V \end{array}$ |

| OS19*         | TioF                                                    | Port output fall time                                       |               | 28<br>15 | 55<br>30 | ns    | $\begin{array}{l} VDD = 1.8V \\ 3.3V \leq VDD \leq 5.0V \end{array}$ |

| OS20*         | Tinp                                                    | INT pin input high or low time                              | 25            |          |          | ns    |                                                                      |

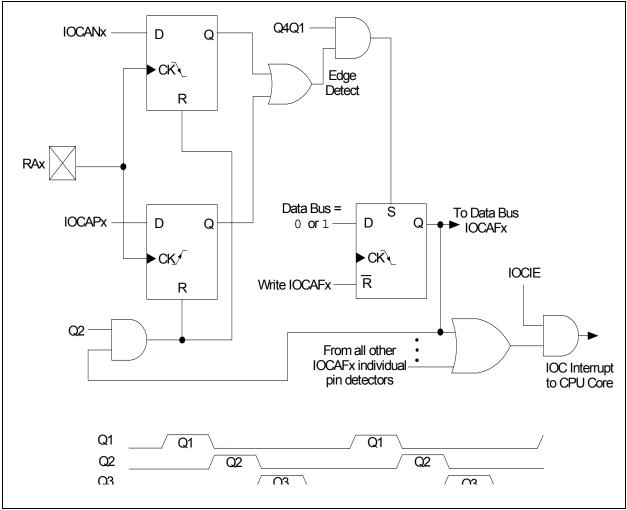

| OS21*         | Tioc                                                    | Interrupt-on-change new input level time                    | 25            | —        | —        | ns    |                                                                      |

| Standard Operating Conditions (unless otherwise stated) |  |

|---------------------------------------------------------|--|

|                                                         |  |

|                                                         |  |

|                                                         |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated.

Note 1: Measurements are taken in EXTRC mode where CLKOUT output is 4 x Tosc.

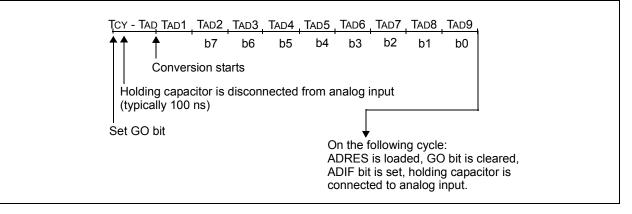

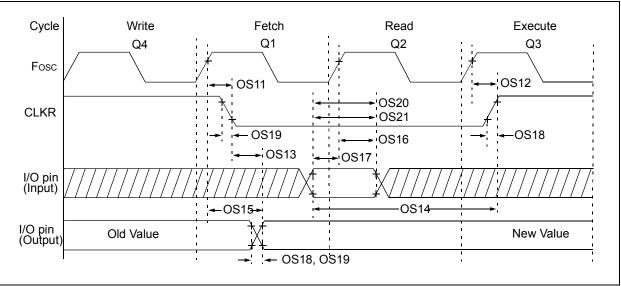

#### FIGURE 24-12: A/D CONVERSION TIMING (NORMAL MODE)

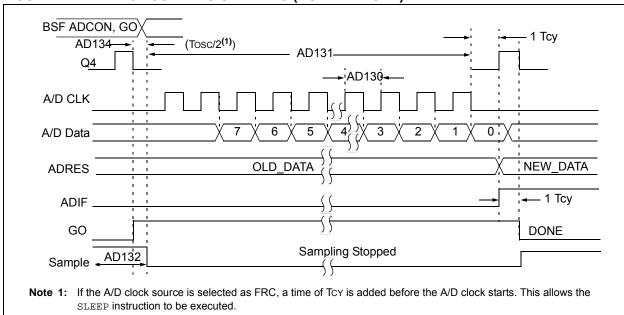

# FIGURE 24-13: A/D CONVERSION TIMING (SLEEP MODE)

## 26.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 26.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

# 27.0 PACKAGING INFORMATION

# 27.1 Package Marking Information

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

can be found on the outer packaging for this package.

# 27.2 Package Details

The following sections give the technical details of the packages.

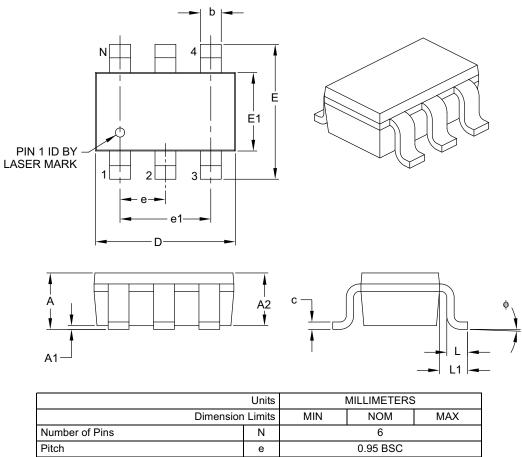

# 6-Lead Plastic Small Outline Transistor (OT) [SOT-23]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | 01113            |      |          |      |  |  |  |

|--------------------------|------------------|------|----------|------|--|--|--|

|                          | Dimension Limits |      | NOM      | MAX  |  |  |  |

| Number of Pins           | Number of Pins N |      | 6        |      |  |  |  |

| Pitch                    | е                |      | 0.95 BSC |      |  |  |  |

| Outside Lead Pitch       | e1               |      | 1.90 BSC |      |  |  |  |

| Overall Height           | А                | 0.90 | -        | 1.45 |  |  |  |

| Molded Package Thickness | A2               | 0.89 | -        | 1.30 |  |  |  |

| Standoff                 | A1               | 0.00 | -        | 0.15 |  |  |  |

| Overall Width            | E                | 2.20 | -        | 3.20 |  |  |  |

| Molded Package Width     | E1               | 1.30 | -        | 1.80 |  |  |  |

| Overall Length           | D                | 2.70 | -        | 3.10 |  |  |  |

| Foot Length              | L                | 0.10 | -        | 0.60 |  |  |  |

| Footprint                | L1               | 0.35 | -        | 0.80 |  |  |  |

| Foot Angle               | ф                | 0°   | -        | 30°  |  |  |  |

| Lead Thickness           | С                | 0.08 | -        | 0.26 |  |  |  |

| Lead Width               | b                | 0.20 | -        | 0.51 |  |  |  |

#### Notes:

1. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.127 mm per side.

2. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-028B

# APPENDIX A: DATA SHEET REVISION HISTORY

# Revision A (07/2011)

Original release.

### Revision B (02/2014)

Electrical Specifications update and new formats; Minor edits.

## Revision C (05/2015)

Updated Figures 7-1 and 11-1. Update Sections 5.4.1, 24.1, and 24.3. Updated Tables 24-2 and 24-9.

## Revision D (11/2015)

Updated the "eXtreme Low-Power (XLP) Features" section; added "Memory" section. Updated "Family Types" table; Updated Table 2-1, 24-5, 24-7, 24-9, 24-12 and 24-13; Updated Figure 7-1, 24-6 and section 15.2.5; Other minor corrections.

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.                                          | [X] <sup>(1)</sup> X     /XX     XXX       T     T     T     T       Tape and Reel     Temperature     Package     Pattern       Option     Range                                          | Examples:<br>a) PIC10LF320T - I/OT<br>Tape and Reel.                                                                                                                                       |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device:                                           | PIC10F320, PIC10LF320, PIC10F322, PIC10LF322                                                                                                                                               | Industrial temperature,<br>SOT-23 package<br>b) PIC10F322 - I/P<br>Industrial temperature<br>PDIP package<br>c) PIC10F322 - E/MC                                                           |

| Tape and Reel<br>Option:<br>Temperature<br>Range: | Blank = Standard packaging (tube or tray)<br>T = Tape and Reel <sup>(1)</sup><br>I = $-40^{\circ}$ C to $+85^{\circ}$ C (Industrial)<br>E = $-40^{\circ}$ C to $+125^{\circ}$ C (Extended) | Extended temperature,<br>DFN package                                                                                                                                                       |

| Package:                                          | OT = SOT-23<br>P = PDIP<br>MC = DFN                                                                                                                                                        | Note 1: Tape and Reel identifier only appears in the catalog part number description. This                                                                                                 |

| Pattern:                                          | QTP, SQTP, Code or Special Requirements (blank otherwise)                                                                                                                                  | identifier is used for ordering purposes and is<br>not printed on the device package. Check<br>with your Microchip Sales Office for package<br>availability with the Tape and Reel option. |