#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 16MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 3                                                                         |

| Program Memory Size        | 896B (512 x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 64 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 3x8b                                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-VFDFN Exposed Pad                                                       |

| Supplier Device Package    | 8-DFN (2x3)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic10lf322-i-mc |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

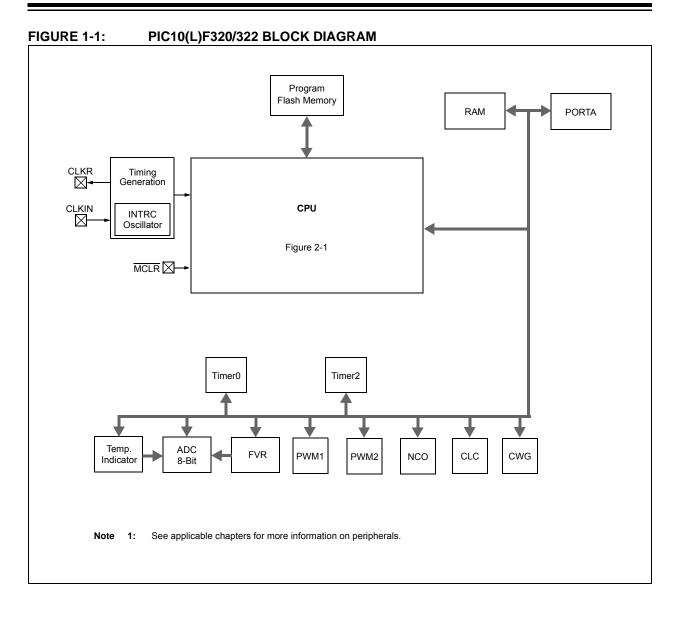

# PIC10(L)F320/322

## 2.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- Program Memory

- Configuration Word

- Device ID

- User ID

- Flash Program Memory

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- Indirect Addressing

### TABLE 2-1: DEVICE SIZES AND ADDRESSES

| 2.1          | Program    | Memory | <sup>v</sup> Organization |

|--------------|------------|--------|---------------------------|

| <b>A</b> • • | I I Vgi um |        | Guineauon                 |

The mid-range core has a 13-bit program counter capable of addressing 8K x 14 program memory space. This device family only implements up to 512 words of the 8K program memory space. Table 2-1 shows the memory sizes implemented for the PIC10(L)F320/322 family. Accessing a location above these boundaries will cause a wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figures 2-1, and 2-2).

| Device Program Memory<br>Space (Words) |     | Last Program Memory<br>Address | High-Endurance Flash<br>Memory Address Range <sup>(1)</sup> |  |  |

|----------------------------------------|-----|--------------------------------|-------------------------------------------------------------|--|--|

| PIC10(L)F320                           | 256 | 00FFh                          | 0080h-00FFh                                                 |  |  |

| PIC10(L)F322                           | 512 | 01FFh                          | 0180h-01FFh                                                 |  |  |

**Note 1:** High-endurance Flash applies to low byte of each address in the range.

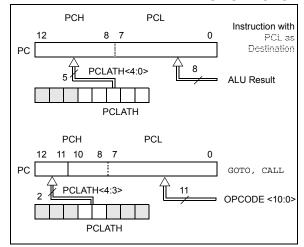

## 2.3 PCL and PCLATH

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 2-3 shows the two situations for the loading of the PC. The upper example in Figure 2-3 shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in Figure 2-3 shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

### FIGURE 2-3: LOADING OF PC IN DIFFERENT SITUATIONS

### 2.3.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<12:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper five bits to the PCLATH register. When the lower eight bits are written to the PCL register, all 13 bits of the program counter will change to the values contained in the PCLATH register and those being written to the PCL register.

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). Care should be exercised when jumping into a look-up table or program branch table (computed GOTO) by modifying the PCL register. Assuming that PCLATH is set to the table start address, if the table length is greater than 255 instructions or if the lower eight bits of the memory address rolls over from 0xFF to 0x00 in the middle of the table, then PCLATH must be incremented for each address rollover that occurs between the table beginning and the target location within the table.

For more information refer to Application Note AN556, *"Implementing a Table Read"* (DS00556).

## 2.3.2 STACK

All devices have an 8-level x 13-bit wide hardware stack (see Figure 2-1). The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

| Note 1: | There are no Status bits to indicate Stack<br>Overflow or Stack Underflow conditions.                                                                                                                |  |  |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 2:      | There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address. |  |  |  |  |  |  |

## 2.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no operation (although Status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR and the IRP bit of the STATUS register, as shown in Figure 2-4.

A simple program to clear RAM location 40h-7Fh using indirect addressing is shown in Example 2-1.

| EXAMPLE 2-1: | INDIRECT ADDRESSING |

|--------------|---------------------|

|--------------|---------------------|

|        | MOVLW    | 0x40  | ;initialize pointer  |  |  |

|--------|----------|-------|----------------------|--|--|

|        | MOVWF    | FSR   | ;to RAM              |  |  |

| NEXT   | CLRF     | INDF  | ;clear INDF register |  |  |

|        | INCF     | FSR   | ;inc pointer         |  |  |

|        | BTFSS    | FSR,7 | ;all done?           |  |  |

|        | GOTO     | NEXT  | ;no clear next       |  |  |

| CONTIN | CONTINUE |       | ;yes continue        |  |  |

|        |          |       |                      |  |  |

## 3.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection and data memory protection are controlled independently. Internal access to the program memory and data memory are unaffected by any code protection setting.

### 3.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Word. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See **Section 3.4** "Write **Protection**" for more information.

### 3.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as boot loader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Word define the size of the program memory block that is protected.

### 3.5 User ID

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See **Section 3.6 "Device ID and Revision ID**" for more information on accessing these memory locations. For more information on checksum calculation, see the "PIC10(L)F320/322 Flash Memory Programming Specification" (DS41572).

### 3.6 Device ID and Revision ID

The memory location 2006h is where the Device ID and Revision ID are stored. The upper nine bits hold the Device ID. The lower five bits hold the Revision ID. See **Section 9.4 "User ID, Device ID and Configuration Word Access**" for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

## 3.7 Register Definitions: Device and Revision

### REGISTER 3-2: DEVID: DEVICE ID REGISTER<sup>(1)</sup>

|       |          | R      | R        | R | R | R | R     |  |  |

|-------|----------|--------|----------|---|---|---|-------|--|--|

|       |          |        | DEV<8:3> |   |   |   |       |  |  |

|       |          | bit 13 |          |   |   |   | bit 8 |  |  |

| R     | R        | R      | R        | R | R | R | R     |  |  |

|       | DEV<2:0> |        | REV<4:0> |   |   |   |       |  |  |

| bit 7 |          |        |          |   |   |   | bit 0 |  |  |

## Legend:

R = Readable bit '1' = Bit is set

bit 13-5 **DEV<8:0>:** Device ID bits

| Device     | DEVID<13:0> Values |          |  |  |  |  |

|------------|--------------------|----------|--|--|--|--|

| Device     | DEV<8:0>           | REV<4:0> |  |  |  |  |

| PIC10F320  | 10 1001 101        | x xxxx   |  |  |  |  |

| PIC10LF320 | 10 1001 111        | x xxxx   |  |  |  |  |

| PIC10F322  | 10 1001 100        | x xxxx   |  |  |  |  |

| PIC10LF322 | 10 1001 110        | x xxxx   |  |  |  |  |

'0' = Bit is cleared

### bit 4-0 **REV<4:0>:** Revision ID bits

These bits are used to identify the revision.

**Note 1:** This location cannot be written.

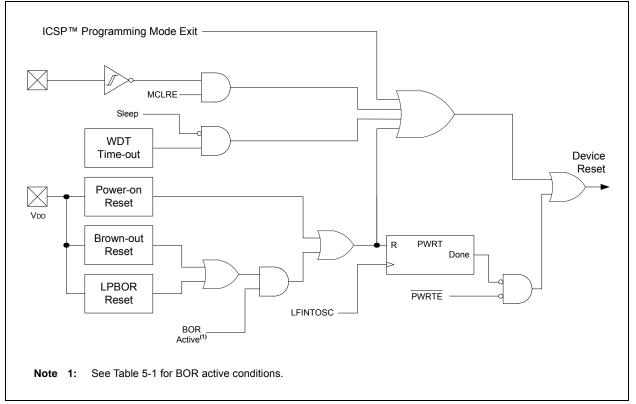

## 5.0 RESETS

There are multiple ways to reset this device:

- Power-On Reset (POR)

- Brown-Out Reset (BOR)

- Low-Power Brown-Out Reset (LPBOR)

- MCLR Reset

- WDT Reset

- · Programming mode exit

To allow VDD to stabilize, an optional Power-up Timer can be enabled to extend the Reset time after a BOR or POR event.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 5-1.

### FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

## 6.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- · GIE bit of the INTCON register

- Interrupt Enable bit(s) for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIE1 register)

The INTCON and PIR1 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- · Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The  ${\tt RETFIE}$  instruction exits the ISR by popping the previous address from the stack, and setting the GIE bit.

For additional information on a specific interrupt's operation, refer to its peripheral chapter.

- Note 1: Individual interrupt flag bits are set, regardless of the state of any other enable bits.

- 2: All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced when the GIE bit is set again.

### 6.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is three or four instruction cycles. For asynchronous interrupts, the latency is three to five instruction cycles, depending on when the interrupt occurs. See Figure 6-2 and **Section 6.3 "Interrupts During Sleep"** for more details.

| FIGURE 6  | IGURE 6-2: INTERRUPT LATENCY |               |                                          |                  |       |             |             |                  |  |

|-----------|------------------------------|---------------|------------------------------------------|------------------|-------|-------------|-------------|------------------|--|

|           |                              |               |                                          |                  |       |             |             |                  |  |

| INTOSC    |                              |               | ∏, ∏, ∏, ∏, ∏, ∏, ∏, ∏, ∏, ∏, ∏, ∏, ∏, ∏ |                  |       |             |             | ∩<br>Q1 Q2 Q3 Q4 |  |

| CLKR      |                              |               | Interru                                  | pt Sampled<br>Q1 |       |             |             |                  |  |

| Interrupt |                              |               |                                          |                  |       |             |             |                  |  |

| GIE       |                              |               |                                          |                  |       |             |             |                  |  |

| PC        | PC-1                         | PC            | PC                                       | +1               | 0004h | 0005h       |             | ()               |  |

| Execute   | 1 Cycle Instr                | ruction at PC | Inst(PC)                                 | NOP              | NOP   | Inst(0004h) |             |                  |  |

|           |                              |               |                                          |                  |       |             |             |                  |  |

| Interrupt |                              |               |                                          |                  |       |             |             |                  |  |

| GIE       |                              |               |                                          |                  |       |             |             |                  |  |

| PC        | PC-1                         | PC            | PC+1/FSR<br>ADDR                         | New PC/<br>PC+1  | 0004h | 0005h       |             |                  |  |

| Execute-  | 2 Cycle Instr                | ruction at PC | Inst(PC)                                 | NOP              | NOP   | Inst(0004h) |             |                  |  |

|           |                              |               |                                          | 1                |       |             |             |                  |  |

| Interrupt |                              |               |                                          |                  |       |             |             |                  |  |

| GIE       |                              |               |                                          |                  |       |             |             |                  |  |

| PC        | PC-1                         | PC            | FSR ADDR                                 | PC+1             | PC+2  | 0004h       | 0005h       | )                |  |

| Execute   | 3 Cycle Instr                | ruction at PC | INST(PC)                                 | NOP              | NOP   | NOP         | Inst(0004h) | Inst(0005h)      |  |

| Interrupt |                              |               |                                          |                  |       |             |             |                  |  |

| GIE       |                              |               |                                          |                  |       |             |             |                  |  |

| PC        | PC-1                         | PC            | FSR ADDR                                 | PC+1             | PC    | +2          | 0004h       | 0005h            |  |

| Execute   | 3 Cycle Instr                | uction at PC  | INST(PC)                                 | NOP              | NOP   | NOP         | NOP         | Inst(0004h)      |  |

|           |                              |               |                                          |                  |       |             |             |                  |  |

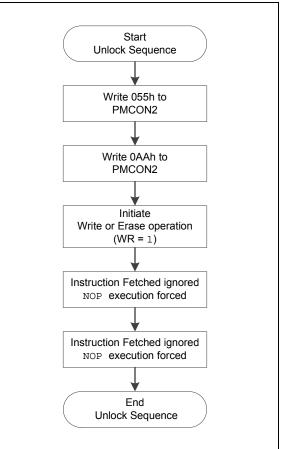

### 9.2.2 FLASH MEMORY UNLOCK SEQUENCE

Note: A delay of at least 100 μs is required after Power-On Reset (POR) before executing a Flash memory unlock sequence.

The unlock sequence is a mechanism that protects the Flash program memory from unintended self-write programming or erasing. The sequence must be executed and completed without interruption to successfully complete any of the following operations:

- Row Erase

- · Load program memory write latches

- Write of program memory write latches to program memory

- Write of program memory write latches to User IDs

The unlock sequence consists of the following steps:

- 1. Write 55h to PMCON2

- 2. Write AAh to PMCON2

- 3. Set the WR bit in PMCON1

- 4. NOP instruction

- 5. NOP instruction

Once the WR bit is set, the processor will always force two NOP instructions. When an Erase Row or Program Row operation is being performed, the processor will stall internal operations (typical 2 ms), until the operation is complete and then resume with the next instruction. When the operation is loading the program memory write latches, the processor will always force the two NOP instructions and continue uninterrupted with the next instruction.

Since the unlock sequence must not be interrupted, global interrupts should be disabled prior to the unlock sequence and re-enabled after the unlock sequence is completed.

### FIGURE 9-3:

### FLASH PROGRAM MEMORY UNLOCK SEQUENCE FLOWCHART

## 9.2.4 WRITING TO FLASH PROGRAM MEMORY

Program memory is programmed using the following steps:

- 1. Load the address in PMADRH:PMADRL of the row to be programmed.

- 2. Load each write latch with data.

- 3. Initiate a programming operation.

- 4. Repeat steps 1 through 3 until all data is written.

Before writing to program memory, the word(s) to be written must be erased or previously unwritten. Program memory can only be erased one row at a time. No automatic erase occurs upon the initiation of the write.

Program memory can be written one or more words at a time. The maximum number of words written at one time is equal to the number of write latches. See Figure 9-5 (row writes to program memory with 16 write latches) for more details.

The write latches are aligned to the Flash row address boundary defined by the upper ten bits of PMADRH:PMADRL, (PMADRH<6:0>:PMADRL<7:5>) with the lower five bits of PMADRL, (PMADRL<7:0>) determining the write latch being loaded. Write operations do not cross these boundaries. At the completion of a program memory write operation, the data in the write latches is reset to contain 0x3FFF. The following steps should be completed to load the write latches and program a row of program memory. These steps are divided into two parts. First, each write latch is loaded with data from the PMDATH:PMDATL using the unlock sequence with LWLO = 1. When the last word to be loaded into the write latch is ready, the LWLO bit is cleared and the unlock sequence executed. This initiates the programming operation, writing all the latches into Flash program memory.

- Note: The special unlock sequence is required to load a write latch with data or initiate a Flash programming operation. If the unlock sequence is interrupted, writing to the latches or program memory will not be initiated.

- 1. Set the WREN bit of the PMCON1 register.

- 2. Clear the CFGS bit of the PMCON1 register.

- Set the LWLO bit of the PMCON1 register. When the LWLO bit of the PMCON1 register is '1', the write sequence will only load the write latches and will not initiate the write to Flash program memory.

- 4. Load the PMADRH:PMADRL register pair with the address of the location to be written.

- 5. Load the PMDATH:PMDATL register pair with the program memory data to be written.

- Execute the unlock sequence (Section 9.2.2 "Flash Memory Unlock Sequence"). The write latch is now loaded.

- 7. Increment the PMADRH:PMADRL register pair to point to the next location.

- 8. Repeat steps 5 through 7 until all but the last write latch has been loaded.

- Clear the LWLO bit of the PMCON1 register. When the LWLO bit of the PMCON1 register is '0', the write sequence will initiate the write to Flash program memory.

- 10. Load the PMDATH:PMDATL register pair with the program memory data to be written.

- 11. Execute the unlock sequence (Section 9.2.2 "Flash Memory Unlock Sequence"). The entire program memory latch content is now written to Flash program memory.

- **Note:** The program memory write latches are reset to the blank state (0x3FFF) at the completion of every write or erase operation. As a result, it is not necessary to load all the program memory write latches. Unloaded latches will remain in the blank state.

An example of the complete write sequence is shown in Example 9-3. The initial address is loaded into the PMADRH:PMADRL register pair; the data is loaded using indirect addressing.

### REGISTER 9-3: PMADRL: PROGRAM MEMORY ADDRESS LOW

| R/W-0/0                                                              | R/W-0/0 | R/W-0/0           | R/W-0/0                                             | R/W-0/0 | R/W-0/0 | R/W-0/0          | R/W-0/0     |  |  |  |

|----------------------------------------------------------------------|---------|-------------------|-----------------------------------------------------|---------|---------|------------------|-------------|--|--|--|

| PMADR<7:0>                                                           |         |                   |                                                     |         |         |                  |             |  |  |  |

| bit 7 bit 0                                                          |         |                   |                                                     |         |         |                  |             |  |  |  |

|                                                                      |         |                   |                                                     |         |         |                  |             |  |  |  |

| Legend:                                                              |         |                   |                                                     |         |         |                  |             |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |         |                   |                                                     |         |         | l as '0'         |             |  |  |  |

| u = Bit is unch                                                      | anged   | x = Bit is unkn   | Bit is unknown -n/n = Value at POR and BOR/Value at |         |         | R/Value at all c | ther Resets |  |  |  |

| '1' = Bit is set                                                     |         | '0' = Bit is clea | ared                                                |         |         |                  |             |  |  |  |

bit 7-0 PMADR<7:0>: Program Memory Read Address low bits

## REGISTER 9-4: PMADRH: PROGRAM MEMORY ADDRESS HIGH

| U-0                                   | U-0                                     | U-0            | U-0 | U-0                                                   | U-0 | U-0 | R/W-0/0 |  |  |

|---------------------------------------|-----------------------------------------|----------------|-----|-------------------------------------------------------|-----|-----|---------|--|--|

| —                                     | _                                       | —              | —   | —                                                     | —   | —   | PMADR8  |  |  |

| bit 7 bit 0                           |                                         |                |     |                                                       |     |     |         |  |  |

|                                       |                                         |                |     |                                                       |     |     |         |  |  |

| Legend:                               |                                         |                |     |                                                       |     |     |         |  |  |

| R = Readable b                        | oit                                     | W = Writable I | bit | U = Unimplemented bit, read as '0'                    |     |     |         |  |  |

| u = Bit is uncha                      | u = Bit is unchanged x = Bit is unknown |                |     | -n/n = Value at POR and BOR/Value at all other Resets |     |     |         |  |  |

| '1' = Bit is set '0' = Bit is cleared |                                         |                |     |                                                       |     |     |         |  |  |

bit 7-1 Unimplemented: Read as '0'

bit 0 PMADR8: Program Memory Read Address High bit

# PIC10(L)F320/322

### TABLE 10-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|-------|-------|-------|-------|--------|--------|--------|--------|---------------------|

| ANSELA | —     | —     | —     | —     | —      | ANSA2  | ANSA1  | ANSA0  | 70                  |

| IOCAF  | —     | —     | —     | -     | IOCAF3 | IOCAF2 | IOCAF1 | IOCAF0 | 76                  |

| IOCAN  | —     | —     | —     | -     | IOCAN3 | IOCAN2 | IOCAN1 | IOCAN0 | 75                  |

| IOCAP  | —     | —     | —     | -     | IOCAP3 | IOCAP2 | IOCAP1 | IOCAP0 | 75                  |

| LATA   | —     | —     | —     | -     | —      | LATA2  | LATA1  | LATA0  | 70                  |

| PORTA  | —     | _     | _     |       | RA3    | RA2    | RA1    | RA0    | 69                  |

| TRISA  | —     | —     | —     | —     | _(1)   | TRISA2 | TRISA1 | TRISA0 | 69                  |

| WPUA   | —     | _     | _     |       | WPUA3  | WPUA2  | WPUA1  | WPUA0  | 71                  |

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note 1: Unimplemented, read as '1'.

## 11.0 INTERRUPT-ON-CHANGE

The PORTA pins can be configured to operate as Interrupt-On-Change (IOC) pins. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual PORTA pin, or combination of PORTA pins, can be configured to generate an interrupt. The Interrupt-on-change module has the following features:

- Interrupt-on-Change enable (Master Switch)

- Individual pin configuration

- · Rising and falling edge detection

- Individual pin interrupt flags

Figure 11-1 is a block diagram of the IOC module.

### 11.1 Enabling the Module

To allow individual PORTA pins to generate an interrupt, the IOCIE bit of the INTCON register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

### 11.2 Individual Pin Configuration

For each PORTA pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated IOCAPx bit of the IOCAP register is set. To enable a pin to detect a falling edge, the associated IOCANx bit of the IOCAN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting both the IOCAPx bit and the IOCANx bit of the IOCAP and IOCAN registers, respectively.

### 11.3 Interrupt Flags

The IOCAFx bits located in the IOCAF register are status flags that correspond to the interrupt-on-change pins of PORTA. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the INTCON register reflects the status of all IOCAFx bits.

## 11.4 Clearing Interrupt Flags

The individual status flags, (IOCAFx bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

### EXAMPLE 11-1: CLEARING INTERRUPT FLAGS

MOVLW 0xff XORWF IOCAF, W ANDWF IOCAF, F

## 11.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the IOCAF register will be updated prior to the first instruction executed out of Sleep.

| R/W-1/u              | R/W-1/u                           | R/W-1/u                                                                                                                                                                                             | R/W-1/u                | R/W-1/u        | R/W-1/u          | R/W-1/u          | R/W-1/u      |

|----------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------|------------------|------------------|--------------|

| WPUEN <sup>(1)</sup> | INTEDG                            | TOCS                                                                                                                                                                                                | T0SE                   | PSA            |                  | PS<2:0>          |              |

| bit 7                |                                   |                                                                                                                                                                                                     |                        |                |                  |                  | bit 0        |

|                      |                                   |                                                                                                                                                                                                     |                        |                |                  |                  |              |

| Legend:              |                                   |                                                                                                                                                                                                     |                        |                |                  |                  |              |

| R = Readable         |                                   | W = Writable                                                                                                                                                                                        |                        | •              | mented bit, read |                  |              |

| u = Bit is uncha     | anged                             | x = Bit is unkr                                                                                                                                                                                     |                        | -n/n = Value a | at POR and BC    | R/Value at all c | other Resets |

| '1' = Bit is set     |                                   | '0' = Bit is clea                                                                                                                                                                                   | ared                   |                |                  |                  |              |

| bit 7                | WPUEN: Wea                        | ak Pull-up Enal                                                                                                                                                                                     | ble bit <sup>(1)</sup> |                |                  |                  |              |

|                      |                                   | l-ups are disab<br>l-ups are enabl                                                                                                                                                                  |                        | al PORT latch  | values           |                  |              |

| bit 6                | INTEDG: Inte                      | errupt Edge Sel                                                                                                                                                                                     | ect bit                |                |                  |                  |              |

|                      |                                   | on rising edge o<br>on falling edge                                                                                                                                                                 | •                      |                |                  |                  |              |

| bit 5                | TOCS: TMR0                        | ) Clock Source Select bit                                                                                                                                                                           |                        |                |                  |                  |              |

|                      |                                   | on T0CKI pin<br>struction cycle                                                                                                                                                                     | clock (Fosc/4          | 4)             |                  |                  |              |

| bit 4                | T0SE: TMR0 Source Edge Select bit |                                                                                                                                                                                                     |                        |                |                  |                  |              |

|                      |                                   | t on high-to-lov<br>t on low-to-high                                                                                                                                                                |                        |                |                  |                  |              |

| bit 3                | PSA: Prescal                      | er Assignment                                                                                                                                                                                       | bit                    |                |                  |                  |              |

|                      |                                   | is inactive and is assigned to                                                                                                                                                                      |                        |                | 0 module         |                  |              |

| bit 2-0              | <b>PS&lt;2:0&gt;:</b> Pre         | escaler Rate Se                                                                                                                                                                                     | elect bits             |                |                  |                  |              |

|                      | Bit                               | Value TMR0 F                                                                                                                                                                                        | Rate                   |                |                  |                  |              |

|                      | 0<br>0<br>1<br>1<br>1             | 000         1:2           001         1:4           010         1:8           011         1:1           000         1:3           001         1:6           10         1:1           11         1:2 | 6<br>2<br>4<br>28      |                |                  |                  |              |

### REGISTER 16-1: OPTION\_REG: OPTION REGISTER

**Note 1:**  $\overline{\text{WPUEN}}$  does not disable the pull-up for the  $\overline{\text{MCLR}}$  input when  $\overline{\text{MCLR}} = 1$ .

### TABLE 16-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER0

| Name       | Bit 7                  | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1   | Bit 0  | Register on<br>Page |

|------------|------------------------|--------|--------|-------|-------|--------|---------|--------|---------------------|

| INTCON     | GIE                    | PEIE   | TMR0IE | INTE  | IOCIE | TMR0IF | INTF    | IOCIF  | 40                  |

| OPTION_REG | WPUEN                  | INTEDG | TOCS   | T0SE  | PSA   |        | PS<2:0> |        | 95                  |

| TMR0       | Timer0 module Register |        |        |       |       |        | 40      |        |                     |

| TRISA      | —                      | _      | —      | —     | —     | TRISA2 | TRISA1  | TRISA0 | 69                  |

Legend: -= Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Timer0 module.

## 19.1.3 LOGIC FUNCTION

There are eight available logic functions including:

- AND-OR

- OR-XOR

- AND

- S-R Latch

- D Flip-Flop with Set and Reset

- D Flip-Flop with Reset

- J-K Flip-Flop with Reset

- Transparent Latch with Set and Reset

Logic functions are shown in Figure 19-3. Each logic function has four inputs and one output. The four inputs are the four data gate outputs of the previous stage. The output is fed to the inversion stage and from there to other peripherals, an output pin, and back to the CLCx itself.

### 19.1.4 OUTPUT POLARITY

The last stage in the configurable logic cell is the output polarity. Setting the LCxPOL bit of the CLCxCON register inverts the output signal from the logic stage. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

### 19.1.5 CLCX SETUP STEPS

The following steps should be followed when setting up the CLCx:

- Disable CLCx by clearing the LCxEN bit.

- Select desired inputs using CLCxSEL0 and CLCxSEL1 registers (See Table 19-1).

- · Clear any associated ANSEL bits.

- Set all TRIS bits associated with inputs.

- · Clear all TRIS bits associated with outputs.

- Enable the chosen inputs through the four gates using CLCxGLS0, CLCxGLS1, CLCxGLS2, and CLCxGLS3 registers.

- Select the gate output polarities with the LCxPOLy bits of the CLCxPOL register.

- Select the desired logic function with the LCxMODE<2:0> bits of the CLCxCON register.

- Select the desired polarity of the logic output with the LCxPOL bit of the CLCxPOL register. (This step may be combined with the previous gate output polarity step).

- If driving the CLCx pin, set the LCxOE bit of the CLCxCON register and also clear the TRIS bit corresponding to that output.

- If interrupts are desired, configure the following bits:

- Set the LCxINTP bit in the CLCxCON register for rising event.

- Set the LCxINTN bit in the CLCxCON register or falling event.

- Set the CLCxIE bit of the associated PIE registers.

- Set the GIE and PEIE bits of the INTCON register.

- Enable the CLCx by setting the LCxEN bit of the CLCxCON register.

| R/W-x/u                                                             | U-0                                                                                                                | U-0                                     | U-0             | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------|----------------|------------------|------------------|-------------|

| LCxPOL                                                              | —                                                                                                                  | —                                       | —               | LCxG4POL       | LCxG3POL         | LCxG2POL         | LCxG1POL    |

| bit 7                                                               |                                                                                                                    |                                         |                 |                |                  |                  | bit 0       |

|                                                                     |                                                                                                                    |                                         |                 |                |                  |                  |             |

| Legend:                                                             |                                                                                                                    |                                         |                 |                |                  |                  |             |

| R = Readable                                                        | bit                                                                                                                | W = Writable I                          | bit             | U = Unimpler   | mented bit, read | l as '0'         |             |

| u = Bit is unch                                                     | anged                                                                                                              | x = Bit is unkn                         | own             | -n/n = Value a | at POR and BO    | R/Value at all c | other Reset |

| '1' = Bit is set                                                    |                                                                                                                    | '0' = Bit is clea                       | ared            |                |                  |                  |             |

|                                                                     |                                                                                                                    |                                         |                 |                |                  |                  |             |

| bit 7                                                               | LCxPOL: LCO                                                                                                        | OUT Polarity Co                         | ontrol bit      |                |                  |                  |             |

|                                                                     | •                                                                                                                  | ut of the logic c                       |                 |                |                  |                  |             |

|                                                                     | 0 = The outp                                                                                                       | ut of the logic c                       | ell is not inve | rted           |                  |                  |             |

| bit 6-4                                                             | Unimplemen                                                                                                         | ted: Read as '0                         | )'              |                |                  |                  |             |

| bit 3                                                               | LCxG4POL:                                                                                                          | Gate 4 Output I                         | Polarity Contr  | ol bit         |                  |                  |             |

| 1 = The output of gate 4 is inverted when applied to the logic cell |                                                                                                                    |                                         |                 |                |                  |                  |             |

|                                                                     |                                                                                                                    | ut of gate 4 is n                       |                 |                |                  |                  |             |

| bit 2                                                               |                                                                                                                    | Gate 3 Output I                         | •               |                |                  |                  |             |

|                                                                     |                                                                                                                    | ut of gate 3 is in<br>ut of gate 3 is n |                 | applied to the | logic cell       |                  |             |

| bit 1                                                               | <ul> <li>0 = The output of gate 3 is not inverted</li> <li>LCxG2POL: Gate 2 Output Polarity Control bit</li> </ul> |                                         |                 |                |                  |                  |             |

|                                                                     |                                                                                                                    | ut of gate 2 is in                      | 5               |                |                  |                  |             |

|                                                                     |                                                                                                                    | ut of gate 2 is in<br>ut of gate 2 is n |                 | applied to the | logic cell       |                  |             |

| bit 0                                                               | •                                                                                                                  | Gate 1 Output I                         |                 | ol bit         |                  |                  |             |

| 1 = The output of gate 1 is inverted when applied to the logic cell |                                                                                                                    |                                         |                 |                |                  |                  |             |

|                                                                     |                                                                                                                    | ut of gate 1 is n                       |                 |                | -                |                  |             |

### REGISTER 19-2: CLCxPOL: SIGNAL POLARITY CONTROL REGISTER

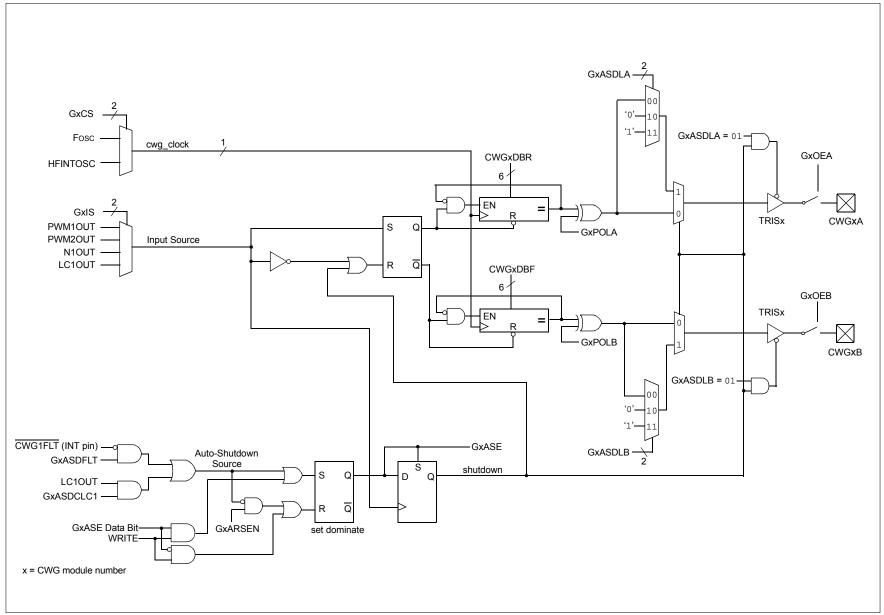

### FIGURE 21-1: CWG BLOCK DIAGRAM

PIC10(L)F320/322

# PIC10(L)F320/322

| ADDLW            | Add literal and W                                                                                                      |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] ADDLW k                                                                                                        |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                      |  |  |

| Status Affected: | C, DC, Z                                                                                                               |  |  |

| Description:     | The contents of the W register<br>are added to the 8-bit literal 'k'<br>and the result is placed in the<br>W register. |  |  |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ label ] BCF f,b                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| ADDWF            | Add W and f                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                    |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                              |

| Status Affected: | C, DC, Z                                                                                                                                                                           |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back<br>in register 'f'. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND literal with W                                                                                                 |

|------------------|--------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                           |

| Operands:        | $0 \le k \le 255$                                                                                                  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                    |

| Status Affected: | Z                                                                                                                  |

| Description:     | The contents of W register are<br>AND'ed with the 8-bit literal 'k'.<br>The result is placed in the W<br>register. |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                             |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.<br>If bit 'b' in register 'f' is '0', the next instruction is discarded, and a NOP is executed instead, making this a 2-cycle instruction. |

| ANDWF            | AND W with f                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ANDWF f,d                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |

| Status Affected: | Z                                                                                                                                                               |

| Description:     | AND the W register with register<br>'f'. If 'd' is '0', the result is stored in<br>the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |

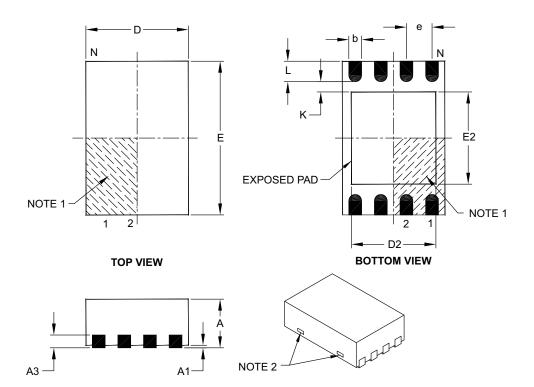

### 8-Lead Plastic Dual Flat, No Lead Package (MC) – 2x3x0.9 mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            |          | MILLIMETERS | 5    |  |

|------------------------|------------------|----------|-------------|------|--|

|                        | Dimension Limits |          | NOM         | MAX  |  |

| Number of Pins         | N                | 8        |             |      |  |

| Pitch                  | e                |          | 0.50 BSC    |      |  |

| Overall Height         | A                | 0.80     | 0.90        | 1.00 |  |

| Standoff               | A1               | 0.00     | 0.02        | 0.05 |  |

| Contact Thickness      | A3               |          | 0.20 REF    |      |  |

| Overall Length         | D                | 2.00 BSC |             |      |  |

| Overall Width          | E                | 3.00 BSC |             |      |  |

| Exposed Pad Length     | D2               | 1.30     | -           | 1.55 |  |

| Exposed Pad Width      | E2               | 1.50     | -           | 1.75 |  |

| Contact Width          | b                | 0.20     | 0.25        | 0.30 |  |

| Contact Length         | L                | 0.30     | 0.40        | 0.50 |  |

| Contact-to-Exposed Pad | К                | 0.20     | -           | _    |  |

### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package may have one or more exposed tie bars at ends.

- 3. Package is saw singulated.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-123C

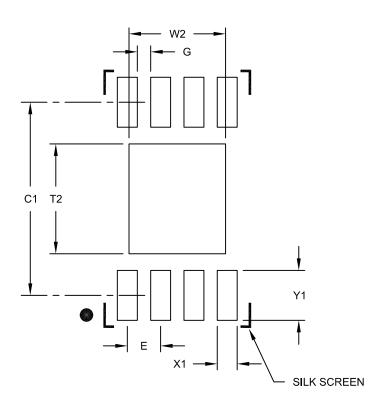

8-Lead Plastic Dual Flat, No Lead Package (MC) - 2x3x0.9mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

| Units                      |    | MILLIMETERS |          |      |  |

|----------------------------|----|-------------|----------|------|--|

| Dimension Limits           |    | MIN         | NOM      | MAX  |  |

| Contact Pitch              | E  |             | 0.50 BSC |      |  |

| Optional Center Pad Width  | W2 |             |          | 1.45 |  |

| Optional Center Pad Length | T2 |             |          | 1.75 |  |

| Contact Pad Spacing        | C1 |             | 2.90     |      |  |

| Contact Pad Width (X8)     | X1 |             |          | 0.30 |  |

| Contact Pad Length (X8)    | Y1 |             |          | 0.75 |  |

| Distance Between Pads      | G  | 0.20        |          |      |  |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2123B