#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

$\cdot \times F$

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 16MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 3                                                                          |

| Program Memory Size        | 896B (512 x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 64 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 3x8b                                                                   |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-VFDFN Exposed Pad                                                        |

| Supplier Device Package    | 8-DFN (2x3)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic10lf322t-i-mc |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.2 Data Memory Organization

The data memory is in one bank, which contains the General Purpose Registers (GPR) and the Special Function Registers (SFR). The RP<1:0> bits of the STATUS register are the bank select bits.

#### <u>RP1</u> <u>RP0</u>

$0 \quad 0 \quad \rightarrow \text{Bank 0 is selected}$

The bank extends up to 7Fh (128 bytes). The lower locations of the bank are reserved for the Special Function Registers. Above the Special Function Registers are the General Purpose Registers, implemented as Static RAM.

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as  $64 \times 8$  in the PIC10(L)F320/322. Each register is accessed, either directly or indirectly, through the File Select Register (FSR) (see Section 2.4 "Indirect Addressing, INDF and FSR Registers").

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (see Table 2-3). These registers are static RAM.

The special registers can be classified into two sets: core and peripheral. The Special Function Registers associated with the "core" are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

| R/W-0/0          | R/W-0/0                                                     | R/W-0/0                                                                                                                | R-1/q           | R-1/q              | R/W-x/u                      | R/W-x/u          | R/W-x/u     |  |  |  |  |

|------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------|------------------------------|------------------|-------------|--|--|--|--|

| IRP              | RP1                                                         | RP0                                                                                                                    | TO              | PD                 | Z                            | DC               | С           |  |  |  |  |

| bit 7            |                                                             |                                                                                                                        |                 |                    |                              | •                | bit 0       |  |  |  |  |

|                  |                                                             |                                                                                                                        |                 |                    |                              |                  |             |  |  |  |  |

| Legend:          |                                                             |                                                                                                                        |                 |                    |                              |                  |             |  |  |  |  |

| R = Readable     | e bit                                                       | W = Writable b                                                                                                         | oit             | U = Unimplei       | mented bit, read             | as '0'           |             |  |  |  |  |

| u = Bit is uncl  | hanged                                                      | x = Bit is unkn                                                                                                        | own             | -n/n = Value       | at POR and BO                | R/Value at all o | ther Resets |  |  |  |  |

| '1' = Bit is set |                                                             | '0' = Bit is clea                                                                                                      | ared            | q = Value de       | pends on condit              | ion              |             |  |  |  |  |

|                  |                                                             |                                                                                                                        |                 |                    |                              |                  |             |  |  |  |  |

| bit 7            | IRP: Reserve                                                | d(2)                                                                                                                   |                 |                    |                              |                  |             |  |  |  |  |

| bit 6-5          | <b>RP&lt;1:0&gt;:</b> Re                                    | served <sup>(2)</sup>                                                                                                  |                 |                    |                              |                  |             |  |  |  |  |

| bit 4            | TO: Time-out                                                | O: Time-out bit                                                                                                        |                 |                    |                              |                  |             |  |  |  |  |

|                  | 1 = After power-up, CLRWDT instruction or SLEEP instruction |                                                                                                                        |                 |                    |                              |                  |             |  |  |  |  |

|                  |                                                             | me-out occurre                                                                                                         | d               |                    |                              |                  |             |  |  |  |  |

| bit 3            |                                                             | PD: Power-Down bit                                                                                                     |                 |                    |                              |                  |             |  |  |  |  |

|                  |                                                             | <ul> <li>1 = After power-up or by the CLRWDT instruction</li> <li>0 = By execution of the SLEEP instruction</li> </ul> |                 |                    |                              |                  |             |  |  |  |  |

| bit 2            | <b>Z</b> : Zero bit                                         |                                                                                                                        |                 |                    |                              |                  |             |  |  |  |  |

|                  |                                                             | It of an arithmet                                                                                                      | tic or loaic or | peration is zero   |                              |                  |             |  |  |  |  |

|                  |                                                             | It of an arithmet                                                                                                      |                 |                    |                              |                  |             |  |  |  |  |

| bit 1            | DC: Digit Car                                               | ry/Borrow bit (A                                                                                                       | DDWF, ADDLI     | W, SUBLW, SUBW     | ∉ instructions) <sup>(</sup> | 1)               |             |  |  |  |  |

|                  | 1 = A carry-c                                               | out from the 4th                                                                                                       | low-order bit   | t of the result of | ccurred                      |                  |             |  |  |  |  |

|                  | 0 = No carry                                                | -out from the 4t                                                                                                       | h low-order b   | oit of the result  |                              |                  |             |  |  |  |  |

| bit 0            |                                                             | Carry/Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                              |                 |                    |                              |                  |             |  |  |  |  |

|                  |                                                             | out from the Mos                                                                                                       | 0               |                    |                              |                  |             |  |  |  |  |

|                  | 0 = No carry                                                | -out from the Me                                                                                                       | ost Significar  | nt bit of the resu | ult occurred                 |                  |             |  |  |  |  |

## REGISTER 2-1: STATUS: STATUS REGISTER

- **Note 1:** For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low-order bit of the source register.

- 2: Maintain as '0'.

| Address | Name       | Bit 7  | Bit 6                                | Bit 5        | Bit 4        | Bit 3          | Bit 2         | Bit 1              | Bit 0     | Value on<br>POR, BOR | Value on all<br>other resets |

|---------|------------|--------|--------------------------------------|--------------|--------------|----------------|---------------|--------------------|-----------|----------------------|------------------------------|

| Bank 0  |            |        |                                      |              |              |                |               |                    |           |                      |                              |

| 00h     | INDF       | Addres | sing this loca                       | tion uses co | ntents of FS | R to address   | data memory   | (not a physical    | register) | xxxx xxxx            | xxxx xxxx                    |

| 01h     | TMR0       |        |                                      |              | Timer0 N     | lodule Registe | er            |                    |           | XXXX XXXX            | uuuu uuuu                    |

| 02h     | PCL        |        |                                      | Progra       | m Counter (F | PC) Least Sigi | nificant Byte |                    |           | 0000 0000            | 0000 0000                    |

| 03h     | STATUS     | IRP    | RP1                                  | RP0          | TO           | PD             | Z             | DC                 | С         | 0001 1xxx            | 000q quuu                    |

| 04h     | FSR        |        | Indirect Data Memory Address Pointer |              |              |                |               |                    | XXXX XXXX | uuuu uuuu            |                              |

| 05h     | PORTA      | _      | _                                    | _            | _            | RA3            | RA2           | RA1                | RA0       | xxxx                 | uuuu                         |

| 06h     | TRISA      | _      | _                                    | _            | _            | _(1)           | TRISA2        | TRISA1             | TRISA0    | 1111                 | 1111                         |

| 07h     | LATA       | _      | _                                    | _            | _            | _              | LATA2         | LATA1              | LATA0     | xxx                  | uuu                          |

| 08h     | ANSELA     | _      | _                                    | _            | _            | _              | ANSA2         | ANSA1              | ANSA0     | 111                  | 111                          |

| 09h     | WPUA       | _      | _                                    | _            | _            | WPUA3          | WPUA2         | WPUA1              | WPUA0     | 1111                 | 1111                         |

| 0Ah     | PCLATH     | -      | _                                    |              | _            | _              | _             | _                  | PCLH0     | 0                    | 0                            |

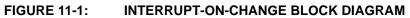

| 0Bh     | INTCON     | GIE    | PEIE                                 | TMR0IE       | INTE         | IOCIE          | TMR0IF        | INTF               | IOCIF     | 0000 0000            | 0000 000u                    |

| 0Ch     | PIR1       | _      | ADIF                                 | _            | NCO1IF       | CLC1IF         | _             | TMR2IF             | _         | -0-0 0-0-            | -0-0 0-0-                    |

| 0Dh     | PIE1       | -      | ADIE                                 |              | NCO1IE       | CLC1IE         | _             | TMR2IE             | _         | -0-0 0-0-            | -0-0 0-0-                    |

| 0Eh     | OPTION_REG | WPUEN  | INTEDG                               | TOCS         | T0SE         | PSA            | PS<2:0>       |                    |           | 1111 1111            | uuuu uuuu                    |

| 0Fh     | PCON       | _      | _                                    | _            | _            | _              | _             | POR                | BOR       | dd                   | uu                           |

| 10h     | OSCCON     | _      |                                      | IRCF<2:0>    |              | HFIOFR         | _             | LFIOFR             | HFIOFS    | -110 0-00            | -110 0-00                    |

| 11h     | TMR2       |        |                                      |              | Timer2 M     | lodule Registe | er            |                    |           | 0000 0000            | 0000 0000                    |

| 12h     | PR2        |        |                                      |              | Timer2 F     | Period Registe | r             |                    |           | 1111 1111            | 1111 1111                    |

| 13h     | T2CON      | _      |                                      | TOUT         | PS<3:0>      |                | TMR2ON        | T2CKP              | S<1:0>    | -000 0000            | -000 0000                    |

| 14h     | PWM1DCL    | PWM1D  | CL<1:0>                              | _            | _            | _              | _             | —                  | _         | xx                   | uu                           |

| 15h     | PWM1DCH    |        |                                      |              | PWM          | 1DCH<7:0>      |               |                    |           | xxxx xxxx            | uuuu uuuu                    |

| 16h     | PWM1CON    | PWM1EN | PWM10E                               | PWM10UT      | PWM1POL      | _              | _             | —                  | —         | 0000                 | 0000                         |

| 17h     | PWM2DCL    | PWM2D  | CL<1:0>                              | _            | _            | _              | _             | —                  | _         | xx                   | uu                           |

| 18h     | PWM2DCH    |        |                                      |              | PWM          | 2DCH<7:0>      |               |                    |           | xxxx xxxx            | uuuu uuuu                    |

| 19h     | PWM2CON    | PWM2EN | PWM2OE                               | PWM2OUT      | PWM2POL      | _              | _             | —                  | _         | 0000                 | 0000                         |

| 1Ah     | IOCAP      | _      | _                                    | _            | _            | IOCAP3         | IOCAP2        | IOCAP1             | IOCAP0    | 0000                 | 0000                         |

| 1Bh     | IOCAN      | _      | _                                    | _            | _            | IOCAN3         | IOCAN2        | IOCAN1             | IOCAN0    | 0000                 | 0000                         |

| 1Ch     | IOCAF      | _      | _                                    | _            | _            | IOCAF3         | IOCAF2        | IOCAF1             | IOCAF0    | 0000                 | 0000                         |

| 1Dh     | FVRCON     | FVREN  | FVRRDY                               | TSEN         | TSRNG        | _              | _             | ADFVF              | R<1:0>    | 0x0000               | 0x0000                       |

| 1Eh     | ADRES      |        |                                      |              | A/D Re       | sult Register  |               |                    |           | xxxx xxxx            | uuuu uuuu                    |

| 1Fh     | ADCON      |        | ADCS<2:0>                            |              |              | CHS<2:0>       |               | <u>GO/</u><br>DONE | ADON      | 0000 0000            | 0000 0000                    |

| TABLE 2-3: | SPECIAL I | FUNCTION REGI | STER SUMMARY | (BANK 0) |

|------------|-----------|---------------|--------------|----------|

|            |           |               |              |          |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: Unimplemented, read as '1'.

## 8.6 Watchdog Control Register

### REGISTER 8-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| U-0              | U-0              | R/W-0/0                                                          | R/W-1/1        | R/W-0/0         | R/W-1/1          | R/W-1/1          | R/W-0/0      |

|------------------|------------------|------------------------------------------------------------------|----------------|-----------------|------------------|------------------|--------------|

| _                | —                |                                                                  |                | WDTPS<4:02      | >                |                  | SWDTEN       |

| bit 7            |                  | ·                                                                |                |                 |                  |                  | bit (        |

|                  |                  |                                                                  |                |                 |                  |                  |              |

| Legend:          |                  |                                                                  |                |                 |                  |                  |              |

| R = Readable     | bit              | W = Writable                                                     | bit            | U = Unimpler    | mented bit, read | d as '0'         |              |

| u = Bit is unch  | anged            | x = Bit is unkr                                                  | nown           | -n/n = Value a  | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set |                  | '0' = Bit is cle                                                 | ared           |                 |                  |                  |              |

| h# 7 0           |                  | inted: Dood oo (                                                 | 0'             |                 |                  |                  |              |

| bit 7-6          | •                | ented: Read as '                                                 |                | alaat hita(1)   |                  |                  |              |

| bit 5-1          |                  | 0>: Watchdog Ti                                                  | mer Periou Si  |                 |                  |                  |              |

|                  |                  | Prescale Rate                                                    |                | internal (1-00) |                  |                  |              |

|                  | 11111 = R        | eserved. Result                                                  | s in minimum   | interval (1:32) |                  |                  |              |

|                  | •                |                                                                  |                |                 |                  |                  |              |

|                  | •                |                                                                  |                |                 |                  |                  |              |

|                  | 10011 = R        | eserved. Result                                                  | s in minimum   | interval (1:32) |                  |                  |              |

|                  | 10010 = <b>1</b> | :8388608 (2 <sup>23</sup> ) (                                    | Interval 256s  | nominal)        |                  |                  |              |

|                  |                  | :4194304 (2 <sup>22</sup> ) (                                    |                |                 |                  |                  |              |

|                  |                  | :2097152 (2 <sup>21</sup> ) (                                    |                |                 |                  |                  |              |

|                  | 01111 <b>= 1</b> | :1048576 (2 <sup>20</sup> ) (                                    | Interval 32s n | ominal)         |                  |                  |              |

|                  | 01110 = 1        | :524288 (2 <sup>19</sup> ) (Ir<br>:262144 (2 <sup>18</sup> ) (Ir | nterval 16s no | minal)          |                  |                  |              |

|                  | 01101 = 1        | :262144 (2 <sup>10</sup> ) (Ir                                   | iterval 8s non | ninal)          |                  |                  |              |

|                  |                  | :131072 (2 <sup>17</sup> ) (Ir<br>:65536 (Interval               |                |                 |                  |                  |              |

|                  |                  | :32768 (Interval                                                 |                | Reset value)    |                  |                  |              |

|                  |                  | :16384 (Interval                                                 |                | nal)            |                  |                  |              |

|                  |                  | :8192 (Interval 2                                                |                | ,               |                  |                  |              |

|                  |                  | :4096 (Interval 1                                                |                | ,               |                  |                  |              |

|                  |                  | :2048 (Interval 6                                                |                | ,               |                  |                  |              |

|                  |                  | :1024 (Interval 3                                                |                | )               |                  |                  |              |

|                  |                  | :512 (Interval 16                                                |                |                 |                  |                  |              |

|                  |                  | :256 (Interval 8 r<br>:128 (Interval 4 r                         |                |                 |                  |                  |              |

|                  |                  | :64 (Interval 2 m                                                | ,              |                 |                  |                  |              |

|                  |                  | :32 (Interval 1 m                                                |                |                 |                  |                  |              |

| bit 0            |                  | Software Enable                                                  |                | /atchdog Timer  | bit              |                  |              |

|                  | If WDTE<1:       |                                                                  |                |                 |                  |                  |              |

|                  | This bit is ig   |                                                                  |                |                 |                  |                  |              |

|                  | If WDTE<1:       |                                                                  |                |                 |                  |                  |              |

|                  | 1 = WDT is       |                                                                  |                |                 |                  |                  |              |

|                  | 0 = WDT is       |                                                                  |                |                 |                  |                  |              |

|                  | If WDTE<1:       |                                                                  |                |                 |                  |                  |              |

|                  | This bit is ig   | nored.                                                           |                |                 |                  |                  |              |

| Name   | Bit 7 | Bit 6     | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1  | Bit 0  | Register<br>on Page |

|--------|-------|-----------|-------|-------|-----------|-------|--------|--------|---------------------|

| OSCCON | —     | IRCF<2:0> |       |       | HFIOFR    | —     | LFIOFR | HFIOFS | 26                  |

| STATUS | IRP   | RP1       | RP0   | TO    | PD        | Z     | DC     | С      | 13                  |

| WDTCON |       |           |       | ١     | WDTPS<4:0 | >     |        | SWDTEN | 48                  |

#### TABLE 8-3: SUMMARY OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by Watchdog Timer.

| TABLE 8-4: | SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER |

|------------|---------------------------------------------------|

|            |                                                   |

| Name   | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4  | Bit 11/3 | Bit 10/2            | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|--------|------|---------|---------|----------|-----------|----------|---------------------|---------|---------|---------------------|

| CONFIG | 13:8 |         | _       | _        | WRT       | WRT<1:0> |                     | LPBOR   | LVP     | 20                  |

| CONFIG | 7:0  | CP      | MCLRE   | PWRTE    | WDTE<1:0> |          | WDTE<1:0> BOREN<1:0 |         | FOSC    | 20                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Watchdog Timer.

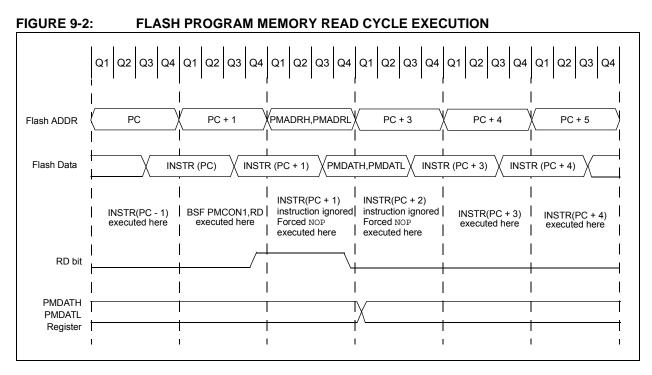

### EXAMPLE 9-1: FLASH PROGRAM MEMORY READ

\* This code block will read 1 word of program

- \* memory at the memory address:

- PROG\_ADDR\_HI: PROG\_ADDR\_LO

- \* data will be returned in the variables;

- \* PROG\_DATA\_HI, PROG\_DATA\_LO

| BANKSEL<br>MOVLW<br>MOVWF | PMADRL<br>PROG_ADDR_LO<br>PMADRL | <pre>; not required on devices with 1 Bank of SFRs ; ; Store LSB of address</pre>                          |

|---------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------|

| MOVLW                     | PROG_ADDR_HI                     | ;                                                                                                          |

| MOVWF                     | PMADRH                           | ; Store MSB of address                                                                                     |

| BCF<br>BSF<br>NOP<br>NOP  | PMCON1,CFGS<br>PMCON1,RD         | ; Do not select Configuration Space<br>; Initiate read<br>; Ignored (Figure 9-2)<br>; Ignored (Figure 9-2) |

| MOVF                      | PMDATL,W                         | ; Get LSB of word                                                                                          |

| MOVWF                     | PROG_DATA_LO                     | ; Store in user location                                                                                   |

| MOVF                      | PMDATH,W                         | ; Get MSB of word                                                                                          |

| MOVWF                     | PROG_DATA_HI                     | ; Store in user location                                                                                   |

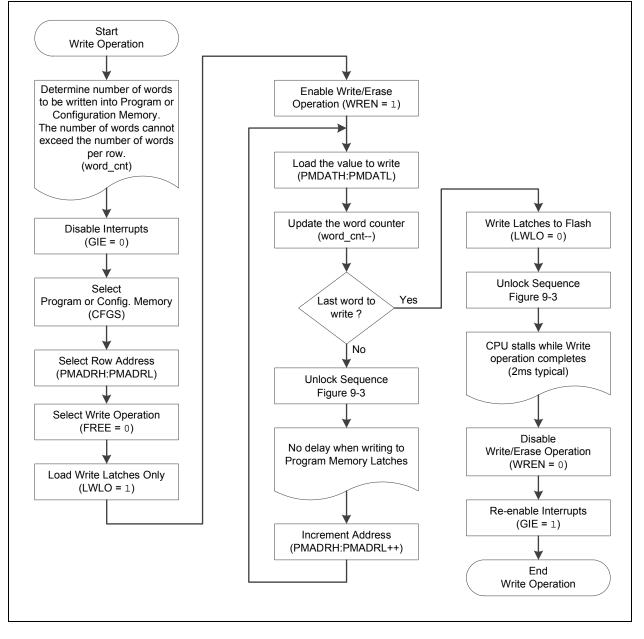

### FLASH PROGRAM MEMORY WRITE FLOWCHART

|        | 0011111             |           |       |       |                      |       |             |       | OATON               |

|--------|---------------------|-----------|-------|-------|----------------------|-------|-------------|-------|---------------------|

| Name   | Bit 7               | Bit 6     | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1       | Bit 0 | Register<br>on Page |

| FVRCON | FVREN               | FVRRDY    | TSEN  | TSRNG | TSRNG — — ADFVR<1:0> |       |             |       | 78                  |

| ADCON  |                     | ADCS<2:0> |       |       | CHS<2:0>             |       | GO/<br>DONE | ADON  | 88                  |

| ADRES  | A/D Result Register |           |       |       |                      |       |             | 89    |                     |

|        |                     |           |       |       |                      |       |             | · · · |                     |

### TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE TEMPERATURE INDICATOR

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the temperature indicator module.

### 15.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- Port configuration

- · Channel selection

- ADC conversion clock source

- · Interrupt control

#### 15.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. Refer to **Section 10.0 "I/O Port"** for more information.

| Note: | Analog voltages on any pin that is defined  |

|-------|---------------------------------------------|

|       | as a digital input may cause the input buf- |

|       | fer to conduct excess current.              |

#### 15.1.2 CHANNEL SELECTION

There are up to five channel selections available:

- AN<2:0> pins

- Temperature Indicator

- FVR (Fixed Voltage Reference) Output

Refer to Section 12.0 "Fixed Voltage Reference (FVR)" and Section 14.0 "Temperature Indicator Module" for more information on these channel selections.

The CHS bits of the ADCON register determine which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion. Refer to **Section 15.2 "ADC Operation"** for more information.

#### 15.1.3 ADC VOLTAGE REFERENCE

There is no external voltage reference connections to the ADC. Only VDD can be used as a reference source. The FVR is only available as an input channel and not a VREF+ input to the ADC.

#### 15.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ADCON register (Register 15-1). There are seven possible clock options:

- · Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- FRC (dedicated internal RC oscillator)

The time to complete one bit conversion is defined as TAD. One full 8-bit conversion requires 9.5 TAD periods as shown in Figure 15-2.

For correct conversion, the appropriate TAD specification must be met. Refer to the A/D conversion requirements in **Section 24.0 "Electrical Specifications"** for more information. Table 15-1 gives examples of appropriate ADC clock selections.

**Note:** Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

| R/W-1/u              | R/W-1/u                   | R/W-1/u                                                                                                                                                                                              | R/W-1/u                | R/W-1/u        | R/W-1/u          | R/W-1/u          | R/W-1/u     |  |  |

|----------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------|------------------|------------------|-------------|--|--|

| WPUEN <sup>(1)</sup> | INTEDG                    | TOCS                                                                                                                                                                                                 | T0SE                   | PSA            |                  | PS<2:0>          |             |  |  |

| bit 7                |                           |                                                                                                                                                                                                      |                        |                |                  |                  | bit C       |  |  |

|                      |                           |                                                                                                                                                                                                      |                        |                |                  |                  |             |  |  |

| Legend:              |                           |                                                                                                                                                                                                      |                        |                |                  |                  |             |  |  |

| R = Readable         | bit                       | W = Writable                                                                                                                                                                                         | bit                    |                | mented bit, read |                  |             |  |  |

| u = Bit is uncha     | anged                     | x = Bit is unkr                                                                                                                                                                                      |                        | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |  |  |

| '1' = Bit is set     |                           | '0' = Bit is cle                                                                                                                                                                                     | ared                   |                |                  |                  |             |  |  |

| bit 7                | WPUEN: Wea                | ak Pull-up Enal                                                                                                                                                                                      | ble bit <sup>(1)</sup> |                |                  |                  |             |  |  |

|                      |                           | l-ups are disab<br>l-ups are enabl                                                                                                                                                                   |                        | al PORT latch  | values           |                  |             |  |  |

| bit 6                | INTEDG: Inte              | errupt Edge Sel                                                                                                                                                                                      | ect bit                |                |                  |                  |             |  |  |

|                      | •                         | on rising edge<br>on falling edge                                                                                                                                                                    | •                      |                |                  |                  |             |  |  |

| bit 5                | TOCS: TMR0                | Clock Source Select bit                                                                                                                                                                              |                        |                |                  |                  |             |  |  |

|                      |                           | on T0CKI pin<br>struction cycle                                                                                                                                                                      | clock (Fosc/4          | 4)             |                  |                  |             |  |  |

| bit 4                | TOSE: TMR0                | ) Source Edge Select bit                                                                                                                                                                             |                        |                |                  |                  |             |  |  |

|                      |                           | t on high-to-lov<br>t on low-to-higł                                                                                                                                                                 |                        |                |                  |                  |             |  |  |

| bit 3                | PSA: Prescal              | er Assignment                                                                                                                                                                                        | bit                    |                |                  |                  |             |  |  |

|                      |                           | is inactive and is assigned to                                                                                                                                                                       |                        |                | ) module         |                  |             |  |  |

| bit 2-0              | <b>PS&lt;2:0&gt;:</b> Pre | escaler Rate Se                                                                                                                                                                                      | elect bits             |                |                  |                  |             |  |  |

|                      | Bit                       | Value TMR0 F                                                                                                                                                                                         | Rate                   |                |                  |                  |             |  |  |

|                      | 0<br>0<br>1<br>1<br>1     | 000         1:2           001         1:4           010         1:8           011         1:1           000         1:3           001         1:6           100         1:1           11         1:2 | 6<br>2<br>4<br>28      |                |                  |                  |             |  |  |

### REGISTER 16-1: OPTION\_REG: OPTION REGISTER

**Note 1:**  $\overline{\text{WPUEN}}$  does not disable the pull-up for the  $\overline{\text{MCLR}}$  input when  $\overline{\text{MCLR}} = 1$ .

#### TABLE 16-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER0

| Name       | Bit 7 | Bit 6                  | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1   | Bit 0  | Register on<br>Page |  |

|------------|-------|------------------------|--------|-------|-------|--------|---------|--------|---------------------|--|

| INTCON     | GIE   | PEIE                   | TMR0IE | INTE  | IOCIE | TMR0IF | INTF    | IOCIF  | 40                  |  |

| OPTION_REG | WPUEN | INTEDG                 | TOCS   | T0SE  | PSA   |        | PS<2:0> |        |                     |  |

| TMR0       |       | Timer0 module Register |        |       |       |        |         |        | 40                  |  |

| TRISA      | —     | _                      | —      | —     | —     | TRISA2 | TRISA1  | TRISA0 | 69                  |  |

Legend: -= Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Timer0 module.

| U-0            | R/W-0/0                    | R/W-0/0          | R/W-0/0       | R/W-0/0       | R/W-0/0          | R/W-0/0 | R/W-0/0      |

|----------------|----------------------------|------------------|---------------|---------------|------------------|---------|--------------|

| _              |                            | TOUTF            | °S<3:0>       |               | TMR2ON           | T2CKF   | °S<1:0>      |

| bit 7          |                            |                  |               |               |                  |         | bit          |

| Legend:        |                            |                  |               |               |                  |         |              |

| R = Readat     | ole bit                    | W = Writable     | bit           | U = Unimpler  | mented bit, read | as '0'  |              |

| u = Bit is ur  | changed                    | x = Bit is unkr  | nown          |               | at POR and BO    |         | other Resets |

| '1' = Bit is s | -                          | '0' = Bit is cle |               |               |                  |         |              |

|                |                            |                  | _             |               |                  |         |              |

| bit 7          | -                          | nted: Read as '  |               |               |                  |         |              |

| bit 6-3        |                            | 0>: Timer2 Out   | put Postscale | r Select bits |                  |         |              |

|                | 1111 = 1:16                |                  |               |               |                  |         |              |

|                | 1110 = 1:15                |                  |               |               |                  |         |              |

|                | 1101 = 1:14<br>1100 = 1:13 |                  |               |               |                  |         |              |

|                | 1000 = 1.13<br>1011 = 1:12 |                  |               |               |                  |         |              |

|                | 1011 = 1.12<br>1010 = 1:11 |                  |               |               |                  |         |              |

|                | 1001 = 1:10                |                  |               |               |                  |         |              |

|                | 1000 = <b>1</b> :9         | Postscaler       |               |               |                  |         |              |

|                | 0111 = <b>1</b> :8         | Postscaler       |               |               |                  |         |              |

|                | 0110 = <b>1</b> :7         |                  |               |               |                  |         |              |

|                | 0101 = 1:6                 |                  |               |               |                  |         |              |

|                | 0100 = 1:5                 |                  |               |               |                  |         |              |

|                | 0011 = 1:4                 |                  |               |               |                  |         |              |

|                | 0010 = 1:3<br>0001 = 1:2   |                  |               |               |                  |         |              |

|                | 0000 = 1:2                 |                  |               |               |                  |         |              |

| bit 2          | TMR2ON: T                  |                  |               |               |                  |         |              |

|                | 1 = Timer2 i               |                  |               |               |                  |         |              |

|                | 0 = Timer2 i               | is off           |               |               |                  |         |              |

| bit 1-0        | T2CKPS<1:                  | 0>: Timer2 Cloc  | k Prescale Se | elect bits    |                  |         |              |

|                | 11 = Presc                 | aler is 64       |               |               |                  |         |              |

|                | 10 = Presc                 |                  |               |               |                  |         |              |

|                | 01 = Presc                 | aler is 4        |               |               |                  |         |              |

|                | 00 = Presc                 | aler is 1        |               |               |                  |         |              |

|                |                            |                  |               |               |                  |         |              |

| TABLE 17-      | 1: SUMMAR                  | RY OF REGIS      | TERS ASSO     | CIATED WIT    | H TIMER2         |         |              |

### REGISTER 17-1: T2CON: TIMER2 CONTROL REGISTER

| TABLE ' | 17-1: \$ | SUMMAR | Y OF REG | ISTERS A | ASSOCIATED | ) WITH TI | MER2 |

|---------|----------|--------|----------|----------|------------|-----------|------|

|         |          |        |          |          |            |           |      |

| Name   | Bit 7                  | Bit 6 | Bit 5                          | Bit 4     | Bit 3            | Bit 2  | Bit 1  | Bit 0 | Register on<br>Page |

|--------|------------------------|-------|--------------------------------|-----------|------------------|--------|--------|-------|---------------------|

| INTCON | GIE                    | PEIE  | TMR0IE                         | INTE      | IOCIE            | TMR0IF | INTF   | IOCIF | 40                  |

| PIE1   | _                      | ADIE  |                                | NCO1IE    | CLC1IE           |        | TMR2IE |       | 41                  |

| PIR1   | -                      | ADIF  | _                              | NCO1IF    | CLC1IF           | _      | TMR2IF |       | 42                  |

| PR2    |                        |       |                                | Timer2 mo | odule Period Reg | ister  |        |       | 96                  |

| TMR2   | Timer2 module Register |       |                                |           |                  |        |        |       | 96                  |

| T2CON  | _                      |       | TOUTPS<3:0> TMR2ON T2CKPS<1:0> |           |                  |        |        |       | 97                  |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for Timer2 module.

| U-0                                   | R/W-x/u                                                           | R/W-x/u                                | R/W-x/u      | U-0                       | R/W-x/u         | R/W-x/u          | R/W-x/u     |  |  |  |  |

|---------------------------------------|-------------------------------------------------------------------|----------------------------------------|--------------|---------------------------|-----------------|------------------|-------------|--|--|--|--|

| _                                     |                                                                   | LCxD2S<2:0>(1)                         |              | _                         | -               | _CxD1S<2:0>(1)   | -           |  |  |  |  |

| bit 7                                 |                                                                   |                                        |              |                           |                 |                  | bit 0       |  |  |  |  |

|                                       |                                                                   |                                        |              |                           |                 |                  |             |  |  |  |  |

| Legend:                               |                                                                   |                                        |              |                           |                 |                  |             |  |  |  |  |

| R = Readable                          | e bit                                                             | W = Writable b                         | bit          | U = Unimplei              | mented bit, rea | d as '0'         |             |  |  |  |  |

| u = Bit is unch                       | nanged                                                            | x = Bit is unkn                        | own          | -n/n = Value              | at POR and BC   | R/Value at all o | ther Resets |  |  |  |  |

| '1' = Bit is set '0' = Bit is cleared |                                                                   |                                        |              |                           |                 |                  |             |  |  |  |  |

|                                       |                                                                   |                                        |              |                           |                 |                  |             |  |  |  |  |

| bit 7                                 | t 7 Unimplemented: Read as '0'                                    |                                        |              |                           |                 |                  |             |  |  |  |  |

| bit 6-4                               | 4 LCxD2S<2:0>: Input Data 2 Selection Control bits <sup>(1)</sup> |                                        |              |                           |                 |                  |             |  |  |  |  |

|                                       | 111 = CLCx                                                        | 111 = CLCxIN[7] is selected for lcxd2. |              |                           |                 |                  |             |  |  |  |  |

|                                       | 110 = CLC×                                                        | (IN[6] is selected                     | for lcxd2.   |                           |                 |                  |             |  |  |  |  |

|                                       |                                                                   | (IN[5] is selected                     |              |                           |                 |                  |             |  |  |  |  |

|                                       |                                                                   | (IN[4] is selected                     |              |                           |                 |                  |             |  |  |  |  |

|                                       |                                                                   | (IN[3] is selected                     |              |                           |                 |                  |             |  |  |  |  |

|                                       |                                                                   | (IN[2] is selected                     |              |                           |                 |                  |             |  |  |  |  |

|                                       |                                                                   | (IN[1] is selected                     |              |                           |                 |                  |             |  |  |  |  |

|                                       | 000 = CLCx                                                        | (IN[0] is selected                     | for lcxd2.   |                           |                 |                  |             |  |  |  |  |

| bit 3                                 | Unimpleme                                                         | nted: Read as '0                       | )'           |                           |                 |                  |             |  |  |  |  |

| bit 2-0                               | LCxD1S<2:0                                                        | 0>: Input Data 1                       | Selection Co | ntrol bits <sup>(1)</sup> |                 |                  |             |  |  |  |  |

|                                       | 111 = CLCx                                                        | (IN[7] is selected                     | for lcxd1.   |                           |                 |                  |             |  |  |  |  |

|                                       | 110 = CLCx                                                        | (IN[6] is selected                     | for lcxd1.   |                           |                 |                  |             |  |  |  |  |

|                                       | 101 = CLCx                                                        | 101 = CLCxIN[5] is selected for lcxd1. |              |                           |                 |                  |             |  |  |  |  |

|                                       | 100 = CLCx                                                        | (IN[4] is selected                     | for lcxd1.   |                           |                 |                  |             |  |  |  |  |

|                                       |                                                                   | (IN[3] is selected                     |              |                           |                 |                  |             |  |  |  |  |

|                                       |                                                                   | (IN[2] is selected                     |              |                           |                 |                  |             |  |  |  |  |

|                                       |                                                                   | 001 = CLCxIN[1] is selected for lcxd1. |              |                           |                 |                  |             |  |  |  |  |

|                                       | 000 = CLCx                                                        | (IN[0] is selected                     | for lcxd1.   |                           |                 |                  |             |  |  |  |  |

#### REGISTER 19-3: CLCxSEL0: MULTIPLEXER DATA 1 AND 2 SELECT REGISTER

**Note 1:** See Table 19-1 for signal names associated with inputs.

| R/W-x/u          | R/W-x/u       | R/W-x/u                                                                                                         | R/W-x/u         | R/W-x/u         | R/W-x/u          | R/W-x/u  | R/W-x/u     |  |  |

|------------------|---------------|-----------------------------------------------------------------------------------------------------------------|-----------------|-----------------|------------------|----------|-------------|--|--|

| LCxG3D4T         | LCxG3D4N      | LCxG3D3T                                                                                                        | LCxG3D3N        | LCxG3D2T        | LCxG3D2N         | LCxG3D1T | LCxG3D1N    |  |  |

| bit 7            |               |                                                                                                                 |                 |                 |                  |          | bit         |  |  |

| Legend:          |               |                                                                                                                 |                 |                 |                  |          |             |  |  |

| R = Readable     | bit           | W = Writable                                                                                                    | hit             | II – I Inimpler | nented bit, read | as '0'   |             |  |  |

| u = Bit is uncha |               | x = Bit is unkr                                                                                                 |                 |                 | at POR and BO    |          | thar Resots |  |  |

| '1' = Bit is set | liged         | 0' = Bit is cle                                                                                                 |                 |                 |                  |          |             |  |  |

|                  |               |                                                                                                                 |                 |                 |                  |          |             |  |  |

| bit 7            | LCxG3D4T:     | Gate 3 Data 4 1                                                                                                 | Frue (non-invei | rted) bit       |                  |          |             |  |  |

|                  |               | gated into Icxo                                                                                                 |                 | ,               |                  |          |             |  |  |

|                  | 0 = Icxd4T is | not gated into                                                                                                  | lcxg3           |                 |                  |          |             |  |  |

| bit 6            | LCxG3D4N:     | LCxG3D4N: Gate 3 Data 4 Negated (inverted) bit                                                                  |                 |                 |                  |          |             |  |  |

|                  |               | gated into lcx                                                                                                  |                 |                 |                  |          |             |  |  |

|                  |               | D = lcxd4N is not gated into lcxg3                                                                              |                 |                 |                  |          |             |  |  |

| bit 5            |               | Gate 3 Data 3                                                                                                   | ,               | rted) bit       |                  |          |             |  |  |

|                  |               | gated into lcxg<br>not gated into                                                                               |                 |                 |                  |          |             |  |  |

| bit 4            |               | Gate 3 Data 3                                                                                                   | 0               | ted) hit        |                  |          |             |  |  |

|                  |               | gated into lcx                                                                                                  | •               |                 |                  |          |             |  |  |

|                  |               | not gated into                                                                                                  |                 |                 |                  |          |             |  |  |

| bit 3            | LCxG3D2T: 0   | Gate 3 Data 2 1                                                                                                 | Frue (non-invei | rted) bit       |                  |          |             |  |  |

|                  |               | gated into Icxo                                                                                                 |                 |                 |                  |          |             |  |  |

|                  |               | not gated into                                                                                                  | •               |                 |                  |          |             |  |  |

| bit 2            |               | Gate 3 Data 2                                                                                                   | -               | ted) bit        |                  |          |             |  |  |

|                  |               | gated into Icx                                                                                                  | •               |                 |                  |          |             |  |  |

| hit 1            |               | <ul> <li>0 = lcxd2N is not gated into lcxg3</li> <li>LCxG3D1T: Gate 3 Data 1 True (non-inverted) bit</li> </ul> |                 |                 |                  |          |             |  |  |

| bit 1            |               | gated into lcx                                                                                                  |                 | teu) bit        |                  |          |             |  |  |

|                  |               | not gated into                                                                                                  |                 |                 |                  |          |             |  |  |

| bit 0            |               | Gate 3 Data 1                                                                                                   | •               | ted) bit        |                  |          |             |  |  |

|                  |               | gated into lcx                                                                                                  | •               | ,               |                  |          |             |  |  |

|                  | 0 = lcxd1N is | 0                                                                                                               |                 |                 |                  |          |             |  |  |

### REGISTER 19-7: CLCxGLS2: GATE 3 LOGIC SELECT REGISTER

#### REGISTER 20-6: NCOxINCL: NCOx INCREMENT REGISTER – LOW BYTE

| R/W-0/0 | R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | NCOxIN  | C<7:0>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Logond  |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 NCOxINC<7:0>: NCOx Increment, low byte

#### REGISTER 20-7: NCOxINCH: NCOx INCREMENT REGISTER – HIGH BYTE

| R/W-0/0       | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------------|---------|---------|---------|---------|---------|---------|---------|

| NCOxINC<15:8> |         |         |         |         |         |         |         |

| bit 7 bit     |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 NCOxINC<15:8>: NCOx Increment, high byte

| Name     | Bit 7                     | Bit 6                                        | Bit 5   | Bit 4   | Bit 3          | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|----------|---------------------------|----------------------------------------------|---------|---------|----------------|---------|---------|---------|---------------------|

| CLC1SEL0 |                           | LC1D2S2                                      | LC1D2S1 | LC1D2S0 |                | LC1D1S2 | LC1D1S1 | LC1D1S0 | 112                 |

| CLC1SEL1 | _                         | LC1D4S2                                      | LC1D4S1 | LC1D4S0 | _              | LC1D3S2 | LC1D3S1 | LC1D3S0 | 113                 |

| CWG1CON1 | G1ASDLB<1:0> G1ASDLA<1:0> |                                              |         | _       | —              | G1IS    | <1:0>   | 140     |                     |

| INTCON   | GIE                       | GIE PEIE TMR0IE INTE IOCIE TMR0IF INTF IOCIF |         |         |                |         | 40      |         |                     |

| NCO1ACCH | NCO1ACCH<15:8>            |                                              |         |         |                |         |         |         | 126                 |

| NCO1ACCL |                           | NCO1ACCL<7:0>                                |         |         |                |         |         |         | 126                 |

| NCO1ACCU |                           | -                                            | _       |         | NCO1ACCU<19:16 |         |         |         | 126                 |

| NCO1CLK  | I                         | N1PWS<2:0>                                   | >       | —       | — — N1CKS<1:0> |         |         |         | 125                 |

| NCO1CON  | N1EN                      | N10E                                         | N1OUT   | N1POL   | _              | —       | —       | N1PFM   | 125                 |

| NCO1INCH |                           |                                              |         | NCO1IN0 | CH<15:8>       |         |         |         | 127                 |

| NCO1INCL |                           |                                              |         | NCO1IN  | CL<7:0>        |         |         |         | 127                 |

| PIE1     |                           | ADIE                                         | _       | NCO1IE  | CLC1IE         | _       | TMR2IE  | _       | 41                  |

| PIR1     | _                         | ADIF                                         |         | NCO1IF  | CLC1IF         | —       | TMR2IF  | —       | 42                  |

| TRISA    | _                         | _                                            | _       | _       | _              | TRISA2  | TRISA1  | TRISA0  | 69                  |

#### TABLE 20-1: SUMMARY OF REGISTERS ASSOCIATED WITH NCOx

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends on condition. Shaded cells are not used for NCO module.

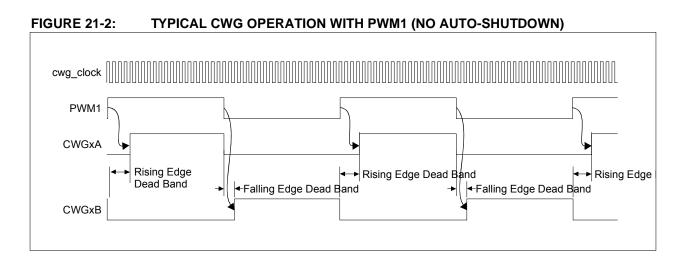

## 23.0 INSTRUCTION SET SUMMARY

The PIC10(L)F320/322 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- · Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 23-1, while the various opcode fields are summarized in Table 23-1.

Table 23-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8-bit or 11-bit constant, or literal value.

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a normal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

### 23.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (RMW) operation. The register is read, the data is modified, and the result is stored according to either the instruction or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

For example, a CLRF PORTA instruction will read PORTA, clear all the data bits, then write the result back to PORTA. This example would have the unintended consequence of clearing the condition that set the IOCIF flag.

#### TABLE 23-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                              |

| W     | Working register (accumulator)                                                                                                                                                    |

| b     | Bit address within an 8-bit file register                                                                                                                                         |

| k     | Literal field, constant data or label                                                                                                                                             |

| x     | Don't care location (= $0$ or 1).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                     |

| PC    | Program Counter                                                                                                                                                                   |

| TO    | Time-out bit                                                                                                                                                                      |

| С     | Carry bit                                                                                                                                                                         |

| DC    | Digit carry bit                                                                                                                                                                   |

| Z     | Zero bit                                                                                                                                                                          |