# E·XFL

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                            |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Active                                                                                                              |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 2 Core, 32-Bit                                                                                                      |

| Speed                              | 1.0GHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                                              |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | SATA 3Gbps (1)                                                                                                      |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | -20°C ~ 105°C (TJ)                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-LFBGA, FCBGA                                                                                                    |

| Supplier Device Package            | 624-FCPBGA (21x21)                                                                                                  |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6d5eym10ae                                             |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Introduction

- High-end mobile Internet devices (MID)

- High-end PDAs

- High-end portable media players (PMP) with HD video capability

- Gaming consoles

- Portable navigation devices (PND)

The i.MX 6Dual/6Quad processors offers numerous advanced features, such as:

- Applications processors—The processors enhance the capabilities of high-tier portable applications by fulfilling the ever increasing MIPS needs of operating systems and games. The Dynamic Voltage and Frequency Scaling (DVFS) provides significant power reduction, allowing the device to run at lower voltage and frequency with sufficient MIPS for tasks such as audio decode.

- Multilevel memory system—The multilevel memory system of each processor is based on the L1 instruction and data caches, L2 cache, and internal and external memory. The processors support many types of external memory devices, including DDR3, DDR3L, LPDDR2, NOR Flash, PSRAM, cellular RAM, NAND Flash (MLC and SLC), OneNAND<sup>™</sup>, and managed NAND, including eMMC up to rev 4.4/4.41.

- Smart speed technology—The processors have power management throughout the device that enables the rich suite of multimedia features and peripherals to consume minimum power in both active and various low power modes. Smart speed technology enables the designer to deliver a feature-rich product, requiring levels of power far lower than industry expectations.

- Dynamic voltage and frequency scaling—The processors improve the power efficiency of devices by scaling the voltage and frequency to optimize performance.

- Multimedia powerhouse—The multimedia performance of each processor is enhanced by a multilevel cache system, Neon<sup>®</sup> MPE (Media Processor Engine) co-processor, a multi-standard hardware video codec, 2 autonomous and independent image processing units (IPU), and a programmable smart DMA (SDMA) controller.

- Powerful graphics acceleration—Each processor provides three independent, integrated graphics processing units: an OpenGL<sup>®</sup> ES 2.0 3D graphics accelerator with four shaders (up to 200 MTri/s and OpenCL support), 2D graphics accelerator, and dedicated OpenVG<sup>TM</sup> 1.1 accelerator.

- Interface flexibility—Each processor supports connections to a variety of interfaces: LCD controller for up to four displays (including parallel display, HDMI1.4, MIPI display, and LVDS display), dual CMOS sensor interface (parallel or through MIPI), high-speed USB on-the-go with PHY, high-speed USB host with PHY, multiple expansion card ports (high-speed MMC/SDIO host and other), 10/100/1000 Mbps Gigabit Ethernet controller, and a variety of other popular interfaces (such as UART, I<sup>2</sup>C, and I<sup>2</sup>S serial audio, SATA-II, and PCIe-II).

- Advanced security—The processors deliver hardware-enabled security features that enable secure e-commerce, digital rights management (DRM), information encryption, secure boot, and secure software downloads. The security features are discussed in detail in the i.MX 6Dual/6Quad security reference manual (IMX6DQ6SDLSRM).

- Integrated power management—The processors integrate linear regulators and internally generate voltage levels for different domains. This significantly simplifies system power management structure.

| Block<br>Mnemonic | Block Name                      | Subsystem                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|---------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WDOG-2<br>(TZ)    | Watchdog<br>(TrustZone)         | Timer<br>Peripherals        | The TrustZone Watchdog (TZ WDOG) timer module protects against<br>TrustZone starvation by providing a method of escaping normal mode and<br>forcing a switch to the TZ mode. TZ starvation is a situation where the<br>normal OS prevents switching to the TZ mode. Such a situation is<br>undesirable as it can compromise the system's security. Once the TZ<br>WDOG module is activated, it must be serviced by TZ software on a<br>periodic basis. If servicing does not take place, the timer times out. Upon<br>a time-out, the TZ WDOG asserts a TZ mapped interrupt that forces<br>switching to the TZ mode. If it is still not served, the TZ WDOG asserts a<br>security violation signal to the CSU. The TZ WDOG module cannot be<br>programmed or deactivated by a normal mode Software. |

| EIM               | NOR-Flash /PSRAM<br>interface   | Connectivity<br>Peripherals | <ul> <li>The EIM NOR-FLASH / PSRAM provides:</li> <li>Support 16-bit (in muxed IO mode only) PSRAM memories (sync and async operating modes), at slow frequency</li> <li>Support 16-bit (in muxed IO mode only) NOR-Flash memories, at slow frequency</li> <li>Multiple chip selects</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| XTALOSC           | Crystal Oscillator<br>interface | —                           | The XTALOSC module enables connectivity to external crystal oscillator device. In a typical application use-case, it is used for 24 MHz oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Table 2. i.MX 6Dual/6Quad Modules List (continued)

# 3.1 Special Signal Considerations

The package contact assignments can be found in Section 6, "Package Information and Contact Assignments." Signal descriptions are defined in the i.MX 6Dual/6Quad reference manual (IMX6DQRM). Special signal consideration information is contained in the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG).

# 3.2 Recommended Connections for Unused Analog Interfaces

The recommended connections for unused analog interfaces can be found in the section, "Unused analog interfaces," of the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG).

| Mode                             | Test Conditions    | Supply   | Typical Current | Unit |

|----------------------------------|--------------------|----------|-----------------|------|

| P1: Transmitter idle, Rx powered | Single Transceiver | SATA_VP  | 0.67            | mA   |

| down, LOS disabled               | -                  | SATA_VPH | 0.23            |      |

|                                  | Clock Module       | SATA_VP  | 6.9             |      |

|                                  | -                  | SATA_VPH | 6.2             |      |

| P2: Powered-down state, only     | Single Transceiver | SATA_VP  | 0.53            | mA   |

| LOS and POR enabled              |                    | SATA_VPH | 0.11            |      |

|                                  | Clock Module       | SATA_VP  | 0.036           |      |

|                                  | -                  | SATA_VPH | 0.12            |      |

| PDDQ mode <sup>3</sup>           | Single Transceiver | SATA_VP  | 0.13            | mA   |

|                                  | -                  | SATA_VPH | 0.012           |      |

|                                  | Clock Module       | SATA_VP  | 0.008           | 1    |

|                                  | -                  | SATA_VPH | 0.004           | 1    |

### Table 11. SATA PHY Current Drain (continued)

<sup>1</sup> Programmed for 1.0 V peak-to-peak Tx level.

<sup>2</sup> Programmed for 0.9 V peak-to-peak Tx level with no boost or attenuation.

<sup>3</sup> LOW power non-functional.

## 4.1.9 PCIe 2.0 Maximum Power Consumption

Table 12 provides PCIe PHY currents for certain operating modes.

Table 12. PCIe PHY Current Drain

| Mode                        | Test Conditions | Supply            | Max Current | Unit |

|-----------------------------|-----------------|-------------------|-------------|------|

| P0: Normal Operation        | 5G Operations   | PCIE_VP (1.1 V)   | 40          | mA   |

|                             |                 | PCIE_VPTX (1.1 V) | 20          |      |

|                             |                 | PCIE_VPH (2.5 V)  | 21          |      |

|                             | 2.5G Operations | PCIE_VP (1.1 V)   | 27          |      |

|                             |                 | PCIE_VPTX (1.1 V) | 20          | 1    |

|                             |                 | PCIE_VPH (2.5 V)  | 20          | 1    |

| P0s: Low Recovery Time      | 5G Operations   | PCIE_VP (1.1 V)   | 30          | mA   |

| Latency, Power Saving State |                 | PCIE_VPTX (1.1 V) | 2.4         | 1    |

|                             |                 | PCIE_VPH (2.5 V)  | 18          | 1    |

|                             | 2.5G Operations | PCIE_VP (1.1 V)   | 20          |      |

|                             |                 | PCIE_VPTX (1.1 V) | 2.4         | 1    |

|                             |                 | PCIE_VPH (2.5 V)  | 18          | ]    |

system to determine when the load capability of the regulator is being exceeded to take the necessary steps. Current-limiting can be enabled to allow for in-rush current requirements during start-up, if needed. Active-pull-down can also be enabled for systems requiring this feature.

For information on external capacitor requirements for this regulator, see the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG).

For additional information, see the i.MX 6Dual/6Quad reference manual (IMX6DQRM).

# 4.3.2.2 LDO\_2P5

The LDO\_2P5 module implements a programmable linear-regulator function from VDD\_HIGH\_IN (see Table 6 for min and max input requirements). Typical Programming Operating Range is 2.25 V to 2.75 V with the nominal default setting as 2.5 V. The LDO\_2P5 supplies the SATA PHY, USB PHY, LVDS PHY, HDMI PHY, MIPI PHY, E-fuse module and PLLs. A programmable brown-out detector is included in the regulator that can be used by the system to determine when the load capability of the regulator is being exceeded, to take the necessary steps. Current-limiting can be enabled to allow for in-rush current requirements during start-up, if needed. Active-pull-down can also be enabled for systems requiring this feature. An alternate self-biased low-precision weak-regulator is included that can be enabled for applications needing to keep the output voltage alive during low-power modes where the main regulator driver and its associated global bandgap reference module are disabled. The output of the weak-regulator is not programmable and is a function of the input supply as well as the load current. Typically, with a 3 V input supply the weak-regulator output is 2.525 V and its output impedance is approximately  $40 \, \Omega$ .

For information on external capacitor requirements for this regulator, see the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG).

For additional information, see the i.MX 6Dual/6Quad reference manual (IMX6DQRM).

# 4.3.2.3 LDO\_USB

The LDO\_USB module implements a programmable linear-regulator function from the USB\_OTG\_VBUS and USB\_H1\_VBUS voltages (4.4 V–5.25 V) to produce a nominal 3.0 V output voltage. A programmable brown-out detector is included in the regulator that can be used by the system to determine when the load capability of the regulator is being exceeded, to take the necessary steps. This regulator has a built in power-mux that allows the user to select to run the regulator from either VBUS supply, when both are present. If only one of the VBUS voltages is present, then the regulator automatically selects this supply. Current limit is also included to help the system meet in-rush current targets. If no VBUS voltage is present, then the VBUSVALID threshold setting will prevent the regulator from being enabled.

For information on external capacitor requirements for this regulator, see the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG).

For additional information, see the i.MX 6Dual/6Quad reference manual (IMX6DQRM).

# 4.8.1 GPIO Output Buffer Impedance

Table 34 shows the GPIO output buffer impedance (OVDD 1.8 V).

### Table 34. GPIO Output Buffer Average Impedance (OVDD 1.8 V)

| Parameter     | Symbol | Drive Strength (DSE) | Typ Value | Unit |

|---------------|--------|----------------------|-----------|------|

|               |        | 001                  | 260       |      |

|               | Rdrv   | 010                  | 130       |      |

|               |        | 011                  | 90        |      |

| Output Driver |        | 100                  | 60        | Ω    |

| Impedance     |        | 101                  | 50        |      |

|               |        | 110                  | 40        |      |

|               |        | 111                  | 33        |      |

Table 35 shows the GPIO output buffer impedance (OVDD 3.3 V).

### Table 35. GPIO Output Buffer Average Impedance (OVDD 3.3 V)

| Parameter     | Symbol | Drive Strength (DSE) | Typ Value | Unit |

|---------------|--------|----------------------|-----------|------|

|               |        | 001                  | 150       |      |

|               | Rdrv   | 010                  | 75        |      |

|               |        | 011                  | 50        |      |

| Output Driver |        | 100                  | 37        | Ω    |

| Impedance     |        | 101                  | 30        |      |

|               |        | 110                  | 25        |      |

|               |        | 111                  | 20        |      |

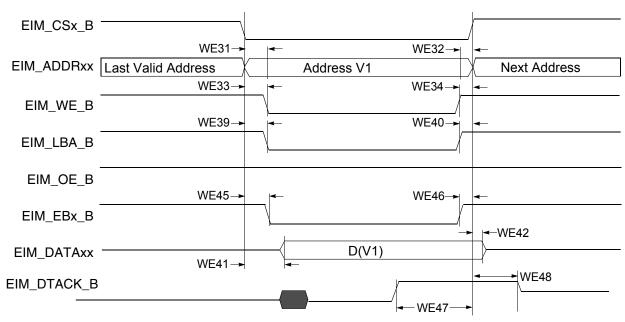

Figure 23. DTACK Mode Write Access (DAP=0)

| Ref No.                 | Parameter                                               | Determination by Synchronous<br>measured parameters | Min                             | Мах                                    | Unit |

|-------------------------|---------------------------------------------------------|-----------------------------------------------------|---------------------------------|----------------------------------------|------|

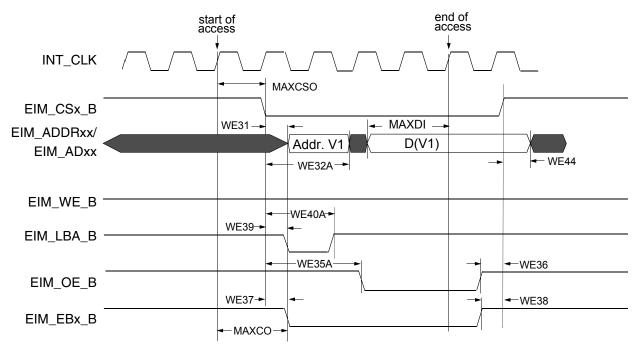

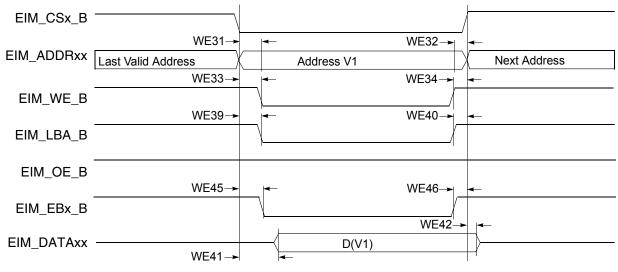

| WE31                    | EIM_CSx_B valid to Address Valid                        | WE4-WE6-CSA×t                                       | -3.5-CSA×t                      | 3.5-CSA×t                              | ns   |

| WE32                    | Address Invalid to EIM_CSx_B<br>Invalid                 | WE7-WE5-CSN×t                                       | -3.5-CSN×t                      | 3.5-CSN×t                              | ns   |

| WE32A<br>(muxed<br>A/D) | EIM_CSx_B valid to Address<br>Invalid                   | t+WE4-WE7+<br>(ADVN+ADVA+1-CSA)×t                   | t - 3.5+(ADVN+A<br>DVA+1-CSA)×t | t + 3.5+(ADVN+ADVA+<br>1-CSA)×t        | ns   |

| WE33                    | EIM_CSx_B Valid to EIM_WE_B<br>Valid                    | WE8-WE6+(WEA-WCSA)×t                                | -3.5+(WEA-WCS<br>A)×t           | 3.5+(WEA-WCSA)×t                       | ns   |

| WE34                    | EIM_WE_B Invalid to EIM_CSx_B<br>Invalid                | WE7-WE9+(WEN-WCSN)×t                                | -3.5+(WEN-WCS<br>N)×t           | 3.5+(WEN-WCSN)×t                       | ns   |

| WE35                    | EIM_CSx_B Valid to EIM_OE_B<br>Valid                    | WE10- WE6+(OEA-RCSA)×t                              | -3.5+(OEA-RCS<br>A)×t           | 3.5+(OEA-RCSA)×t                       | ns   |

| WE35A<br>(muxed<br>A/D) | EIM_CSx_B Valid to EIM_OE_B<br>Valid                    | WE10-WE6+(OEA+RADVN+R<br>ADVA+ADH+1-RCSA)×t         | ``                              | 3.5+(OEA+RADVN+RA<br>DVA+ADH+1-RCSA)×t | ns   |

| WE36                    | EIM_OE_B Invalid to EIM_CSx_B<br>Invalid                | WE7-WE11+(OEN-RCSN)×t                               | -3.5+(OEN-RCS<br>N)×t           | 3.5+(OEN-RCSN)×t                       | ns   |

| WE37                    | EIM_CSx_B Valid to EIM_EBx_B<br>Valid (Read access)     | WE12-WE6+(RBEA-RCSA)×t                              | -3.5+(RBEA- RC<br>SA)×t         | 3.5+(RBEA - RCSA)×t                    | ns   |

| WE38                    | EIM_EBx_B Invalid to<br>EIM_CSx_B Invalid (Read access) | WE7-WE13+(RBEN-RCSN)×t                              | -3.5+<br>(RBEN-RCSN)×t          | 3.5+(RBEN-RCSN)×t                      | ns   |

| WE39                    | EIM_CSx_B Valid to EIM_LBA_B<br>Valid                   | WE14-WE6+(ADVA-CSA)×t                               | -3.5+<br>(ADVA-CSA)×t           | 3.5+(ADVA-CSA)×t                       | ns   |

| Table 42. | EIM | Asynchronous | Timing | Parameters | <b>Relative to</b> | Chip Select <sup>1, 2</sup> |

|-----------|-----|--------------|--------|------------|--------------------|-----------------------------|

|-----------|-----|--------------|--------|------------|--------------------|-----------------------------|

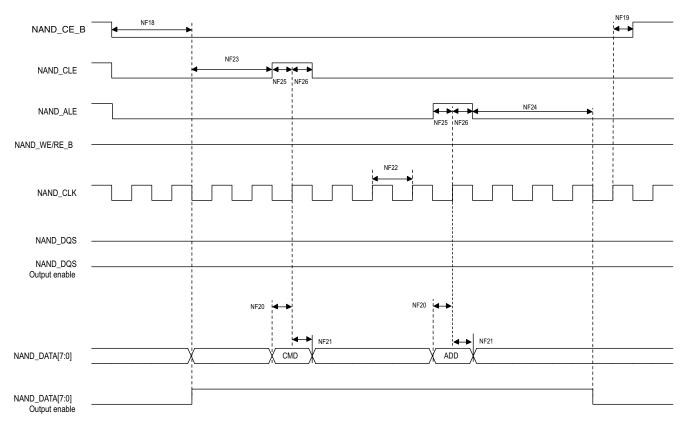

# 4.11.2 Source Synchronous Mode AC Timing (ONFI 2.x Compatible)

Figure 29 shows the write and read timing of Source Synchronous mode.

Figure 29. Source Synchronous Mode Command and Address Timing Diagram

| ID   | Parameter                        | Symbol             | Timing<br>T = GPMI Clock C | Cycle | Unit |

|------|----------------------------------|--------------------|----------------------------|-------|------|

|      |                                  |                    | Min                        | Max   |      |

| NF28 | Data write setup                 | tDS <sup>6</sup>   | 0.25 × tCK - 0.32          | _     | ns   |

| NF29 | Data write hold                  | tDH <sup>6</sup>   | 0.25 × tCK - 0.79          | _     | ns   |

| NF30 | NAND_DQS/NAND_DQ read setup skew | tDQSQ <sup>7</sup> | —                          | 3.18  | —    |

| NF31 | NAND_DQS/NAND_DQ read hold skew  | tQHS <sup>7</sup>  | —                          | 3.27  | —    |

### Table 46. Samsung Toggle Mode Timing Parameters<sup>1</sup> (continued)

<sup>1</sup> The GPMI toggle mode output timing can be controlled by the module's internal registers HW\_GPMI\_TIMING0\_ADDRESS\_SETUP, HW\_GPMI\_TIMING0\_DATA\_SETUP, and HW\_GPMI\_TIMING0\_DATA\_HOLD. This AC timing depends on these registers settings. In the table, AS/DS/DH represents each of these settings.

<sup>2</sup> AS minimum value can be 0, while DS/DH minimum value is 1.

<sup>3</sup> T = tCK (GPMI clock period) -0.075ns (half of maximum p-p jitter).

<sup>4</sup> CE\_DELAY represents HW\_GPMI\_TIMING2[CE\_DELAY]. NF18 is met automatically by the design. Read/Write operation is started with enough time of ALE/CLE assertion to low level.

<sup>5</sup> PRE\_DELAY+1)  $\geq$  (AS+DS)

<sup>6</sup> Shown in Figure 30.

<sup>7</sup> Shown in Figure 31.

Figure 32 shows the timing diagram of NAND\_DQS/NAND\_DATAxx read valid window. For DDR Toggle mode, the typical value of tDQSQ is 1.4 ns (max) and 1.4 ns (max) for tQHS at 133 MB/s. GPMI will sample NAND\_DATA[7:0] at both rising and falling edge of a delayed NAND\_DQS signal, which is provided by an internal DPLL. The delay value of this register can be controlled by GPMI register GPMI\_READ\_DDR\_DLL\_CTRL.SLV\_DLY\_TARGET (see the GPMI chapter of the i.MX 6Dual/6Quad reference manual (IMX6DQRM)). Generally, the typical delay value is equal to 0x7 which means 1/4 clock cycle delay expected. However, if the board delay is large enough and cannot be ignored, the delay value should be made larger to compensate the board delay.

# 4.12 External Peripheral Interface Parameters

The following subsections provide information on external peripheral interfaces.

# 4.12.1 AUDMUX Timing Parameters

The AUDMUX provides a programmable interconnect logic for voice, audio, and data routing between internal serial interfaces (SSIs) and external serial interfaces (audio and voice codecs). The AC timing of AUDMUX external pins is governed by the SSI module. For more information, see the respective SSI electrical specifications found within this document.

# 4.12.2 ECSPI Timing Parameters

This section describes the timing parameters of the ECSPI block. The ECSPI has separate timing parameters for master and slave modes.

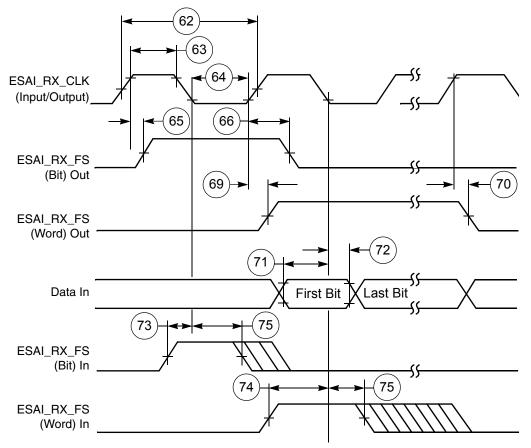

Figure 38. ESAI Receiver Timing

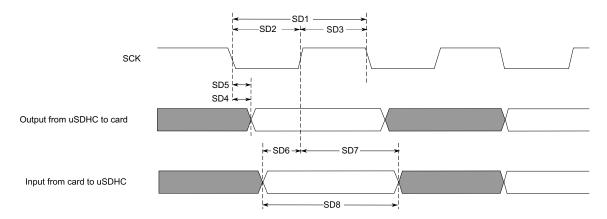

# 4.12.4.3 SDR50/SDR104 AC Timing

Figure 41 depicts the timing of SDR50/SDR104, and Table 52 lists the SDR50/SDR104 timing characteristics.

Figure 41. SDR50/SDR104 Timing

| ID                                                                                       | Parameter                        | Symbols          | Min                  | Мах                  | Unit |  |  |  |

|------------------------------------------------------------------------------------------|----------------------------------|------------------|----------------------|----------------------|------|--|--|--|

| Card Input Clock                                                                         |                                  |                  |                      |                      |      |  |  |  |

| SD1                                                                                      | Clock Frequency Period           | t <sub>CLK</sub> | 4.8                  | _                    | ns   |  |  |  |

| SD2                                                                                      | Clock Low Time                   | t <sub>CL</sub>  | $0.46 	imes t_{CLK}$ | $0.54 	imes t_{CLK}$ | ns   |  |  |  |

| SD3                                                                                      | Clock High Time                  | t <sub>CH</sub>  | $0.46 	imes t_{CLK}$ | $0.54 	imes t_{CLK}$ | ns   |  |  |  |

| uSDHC Output/Card Inputs SD_CMD, SDx_DATAx in SDR50 (Reference to SDx_CLK)               |                                  |                  |                      |                      |      |  |  |  |

| SD4                                                                                      | uSDHC Output Delay               | t <sub>OD</sub>  | -3                   | 1                    | ns   |  |  |  |

|                                                                                          | uSDHC Output/Card Inputs SD_CMD, | SDx_DATAx in S   | DR104 (Refer         | ence to SDx_C        | LK)  |  |  |  |

| SD5                                                                                      | uSDHC Output Delay               | t <sub>OD</sub>  | -1.6                 | 0.74                 | ns   |  |  |  |

|                                                                                          | uSDHC Input/Card Outputs SD_CMD, | SDx_DATAx in S   | SDR50 (Refere        | ence to SDx_CI       | _K)  |  |  |  |

| SD6                                                                                      | uSDHC Input Setup Time           | t <sub>ISU</sub> | 2.5                  | _                    | ns   |  |  |  |

| SD7                                                                                      | uSDHC Input Hold Time            | t <sub>IH</sub>  | 1.5                  | —                    | ns   |  |  |  |

| uSDHC Input/Card Outputs SD_CMD, SDx_DATAx in SDR104 (Reference to SDx_CLK) <sup>1</sup> |                                  |                  |                      |                      |      |  |  |  |

| SD8                                                                                      | Card Output Data Window          | t <sub>ODW</sub> | $0.5 	imes t_{CLK}$  | —                    | ns   |  |  |  |

### Table 52. SDR50/SDR104 Interface Timing Specification

<sup>1</sup>Data window in SDR100 mode is variable.

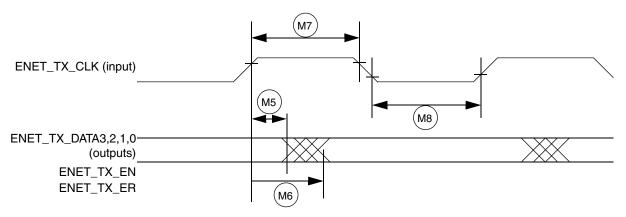

### 4.12.5.1.2 MII Transmit Signal Timing (ENET\_TX\_DATA3,2,1,0, ENET\_TX\_EN, ENET\_TX\_ER, and ENET\_TX\_CLK)

The transmitter functions correctly up to an ENET\_TX\_CLK maximum frequency of 25 MHz + 1%. There is no minimum frequency requirement. Additionally, the processor clock frequency must exceed twice the ENET\_TX\_CLK frequency.

Figure 43 shows MII transmit signal timings. Table 54 describes the timing parameters (M5–M8) shown in the figure.

Figure 43. MII Transmit Signal Timing Diagram

| Table | 54. | MII | Transmit | Signal | Timing |

|-------|-----|-----|----------|--------|--------|

|-------|-----|-----|----------|--------|--------|

| ID | Characteristic <sup>1</sup>                                           | Min | Max | Unit               |

|----|-----------------------------------------------------------------------|-----|-----|--------------------|

| M5 | ENET_TX_CLK to ENET_TX_DATA3,2,1,0, ENET_TX_EN,<br>ENET_TX_ER invalid | 5   | _   | ns                 |

| M6 | ENET_TX_CLK to ENET_TX_DATA3,2,1,0, ENET_TX_EN,<br>ENET_TX_ER valid   | _   | 20  | ns                 |

| M7 | ENET_TX_CLK pulse width high                                          | 35% | 65% | ENET_TX_CLK period |

| M8 | ENET_TX_CLK pulse width low                                           | 35% | 65% | ENET_TX_CLK period |

<sup>1</sup> ENET\_TX\_EN, ENET\_TX\_CLK, and ENET0\_TXD0 have the same timing in 10-Mbps 7-wire interface mode.

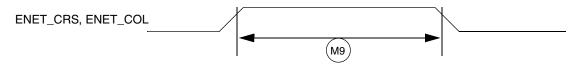

### 4.12.5.1.3 MII Asynchronous Inputs Signal Timing (ENET\_CRS and ENET\_COL)

Figure 44 shows MII asynchronous input timings. Table 55 describes the timing parameter (M9) shown in the figure.

Figure 44. MII Async Inputs Timing Diagram

| i.MX 6Dual/6Quad        |                             |        |       | LCD                    |        |      |      |                                  |

|-------------------------|-----------------------------|--------|-------|------------------------|--------|------|------|----------------------------------|

|                         | RGB,                        | R      | GB/TV | Comment <sup>1,2</sup> |        |      |      |                                  |

| Port Name<br>(x = 0, 1) | Signal<br>Name<br>(General) |        |       | 20-bit<br>YCrCb        |        |      |      |                                  |

| IPUx_DISPx_DAT05        | DAT[5]                      | G[0]   | B[5]  | B[5]                   | Y/C[5] | C[5] | C[5] | _                                |

| IPUx_DISPx_DAT06        | DAT[6]                      | G[1]   | G[0]  | B[6]                   | Y/C[6] | C[6] | C[6] | _                                |

| IPUx_DISPx_DAT07        | DAT[7]                      | G[2]   | G[1]  | B[7]                   | Y/C[7] | C[7] | C[7] | _                                |

| IPUx_DISPx_DAT08        | DAT[8]                      | G[3]   | G[2]  | G[0]                   |        | Y[0] | C[8] | _                                |

| IPUx_DISPx_DAT09        | DAT[9]                      | G[4]   | G[3]  | G[1]                   | _      | Y[1] | C[9] | _                                |

| IPUx_DISPx_DAT10        | DAT[10]                     | G[5]   | G[4]  | G[2]                   |        | Y[2] | Y[0] | _                                |

| IPUx_DISPx_DAT11        | DAT[11]                     | R[0]   | G[5]  | G[3]                   |        | Y[3] | Y[1] | _                                |

| IPUx_DISPx_DAT12        | DAT[12]                     | R[1]   | R[0]  | G[4]                   |        | Y[4] | Y[2] | _                                |

| IPUx_DISPx_DAT13        | DAT[13]                     | R[2]   | R[1]  | G[5]                   |        | Y[5] | Y[3] | _                                |

| IPUx_DISPx_DAT14        | DAT[14]                     | R[3]   | R[2]  | G[6]                   |        | Y[6] | Y[4] | _                                |

| IPUx_DISPx_DAT15        | DAT[15]                     | R[4]   | R[3]  | G[7]                   |        | Y[7] | Y[5] | _                                |

| IPUx_DISPx_DAT16        | DAT[16]                     |        | R[4]  | R[0]                   | —      | _    | Y[6] | _                                |

| IPUx_DISPx_DAT17        | DAT[17]                     |        | R[5]  | R[1]                   |        |      | Y[7] | _                                |

| IPUx_DISPx_DAT18        | DAT[18]                     |        |       | R[2]                   | —      |      | Y[8] | _                                |

| IPUx_DISPx_DAT19        | DAT[19]                     |        |       | R[3]                   | —      |      | Y[9] | _                                |

| IPUx_DISPx_DAT20        | DAT[20]                     |        |       | R[4]                   | —      |      | _    | _                                |

| IPUx_DISPx_DAT21        | DAT[21]                     |        |       | R[5]                   | —      | _    | _    | _                                |

| IPUx_DISPx_DAT22        | DAT[22]                     | —      | —     | R[6]                   |        | —    | —    | _                                |

| IPUx_DISPx_DAT23        | DAT[23]                     | —      | —     | R[7]                   |        |      | —    | _                                |

| IPUx_DIx_DISP_CLK       |                             | PixCLK |       |                        |        |      |      | _                                |

| IPUx_DIx_PIN01          |                             |        |       |                        |        |      |      | May be required for anti-tearing |

| IPUx_DIx_PIN02          | HSYNC                       |        |       |                        |        |      | _    |                                  |

| IPUx_DIx_PIN03          | VSYNC                       |        |       |                        |        |      |      | VSYNC out                        |

### Table 64. Video Signal Cross-Reference (continued)

### Table 65 shows timing characteristics of signals presented in Figure 63 and Figure 64.

| ID   | Parameter                      | Symbol | Value                                 | Description                                                                                                                                                                                                                                                                                                               | Unit |

|------|--------------------------------|--------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| IP5  | Display interface clock period | Tdicp  | (see <sup>1</sup> )                   | Display interface clock IPP_DISP_CLK                                                                                                                                                                                                                                                                                      | ns   |

| IP6  | Display pixel clock period     | Tdpcp  | DISP_CLK_PER_PIXEL<br>X Tdicp         | Time of translation of one pixel to display,<br>DISP_CLK_PER_PIXEL—number of pixel<br>components in one pixel (1. <i>n</i> ).<br>The DISP_CLK_PER_PIXEL is virtual<br>parameter to define display pixel clock<br>period.<br>The DISP_CLK_PER_PIXEL is received by<br>DC/DI one access division to <i>n</i><br>components. | ns   |

| IP7  | Screen width time              | Tsw    | (SCREEN_WIDTH)<br>× Tdicp             | SCREEN_WIDTH—screen width in,<br>interface clocks. horizontal blanking<br>included.<br>The SCREEN_WIDTH should be built by<br>suitable DI's counter <sup>2</sup> .                                                                                                                                                        | ns   |

| IP8  | HSYNC width time               | Thsw   | (HSYNC_WIDTH)                         | HSYNC_WIDTH—Hsync width in DI_CLK<br>with 0.5 DI_CLK resolution. Defined by DI's<br>counter.                                                                                                                                                                                                                              | ns   |

| IP9  | Horizontal blank interval 1    | Thbi1  | BGXP × Tdicp                          | BGXP—width of a horizontal blanking<br>before a first active data in a line (in<br>interface clocks). The BGXP should be built<br>by suitable DI's counter.                                                                                                                                                               | ns   |

| IP10 | Horizontal blank interval 2    | Thbi2  | (SCREEN_WIDTH –<br>BGXP – FW) × Tdicp | Width a horizontal blanking after a last<br>active data in a line (in interface clocks)<br>FW—with of active line in interface clocks.<br>The FW should be built by suitable DI's<br>counter.                                                                                                                             | ns   |

| IP12 | Screen height                  | Tsh    | (SCREEN_HEIGHT)<br>× Tsw              | SCREEN_HEIGHT—screen height in lines<br>with blanking.<br>The SCREEN_HEIGHT is a distance<br>between 2 VSYNCs.<br>The SCREEN_HEIGHT should be built by<br>suitable DI's counter.                                                                                                                                          | ns   |

| IP13 | VSYNC width                    | Tvsw   | VSYNC_WIDTH                           | VSYNC_WIDTH—Vsync width in DI_CLK<br>with 0.5 DI_CLK resolution. Defined by DI's<br>counter.                                                                                                                                                                                                                              | ns   |

| IP14 | Vertical blank interval 1      | Tvbi1  | BGYP X Tsw                            | BGYP—width of first Vertical<br>blanking interval in line. The BGYP should<br>be built by suitable DI's counter.                                                                                                                                                                                                          | ns   |

| IP15 | Vertical blank interval 2      | Tvbi2  | (SCREEN_HEIGHT –<br>BGYP – FH) × Tsw  | Width of second vertical blanking interval in line. The FH should be built by suitable DI's counter.                                                                                                                                                                                                                      | ns   |

### Table 65. Synchronous Display Interface Timing Characteristics (Pixel Level)

|                                                                                                                             | . <u> </u>                                               |                       |            |            |                |

|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------|------------|------------|----------------|

| Parameter                                                                                                                   | Symbol                                                   | Test Conditions       | Min        | Max        | Unit           |

| Common-mode output voltage:<br>(V <sub>O+</sub> - V <sub>O-</sub> ) / 2                                                     | V <sub>OCM</sub>                                         | _                     | 1.0        | 1.5        | V              |

| Difference in common-mode output between<br>(high/low) steady-states:<br>I V <sub>OCM, high</sub> - V <sub>OCM, low</sub> I | ΔV <sub>OCM</sub>                                        | _                     | -50        | 50         | mV             |

| Variations on common-mode output during a logic state transitions                                                           | V <sub>CMV</sub>                                         | See Note <sup>2</sup> | —          | 150        | mVpp           |

| Short circuit current                                                                                                       | I <sub>OS</sub>                                          | See Note <sup>3</sup> | —          | 43         | mA             |

| Differential output impedance                                                                                               | Z <sub>O</sub>                                           | —                     | 1.6        | —          | kΩ             |

|                                                                                                                             | Receive                                                  | er Characteristics    |            |            |                |

| Differential clock input:<br>• logic low steady-state<br>• logic high steady-state<br>• hysteresis                          | V <sub>ILC</sub><br>V <sub>IHC</sub><br>V <sub>HSC</sub> | See Note <sup>4</sup> | 50<br>-25  | -50<br>25  | mV<br>mV<br>mV |

| Differential signal/data input:<br>• logic low steady-state<br>• logic high steady-state                                    | V <sub>ILS</sub><br>V <sub>IHS</sub>                     | _                     | <br>50     | -50<br>—   | mV<br>mV       |

| Signal-ended input voltage (steady-state):<br>• MLB_SIG_P, MLB_DATA_P<br>• MLB_SIG_N, MLB_DATA_N                            | V <sub>IN+</sub><br>V <sub>IN-</sub>                     | _                     | 0.5<br>0.5 | 2.0<br>2.0 | V<br>V         |

Table 72. MediaLB 6-Pin Interface Electrical DC Specifications (continued)

<sup>1</sup> The signal-ended output voltage of a driver is defined as V<sub>O+</sub> on MLB\_CLK\_P, MLB\_SIG\_P, and MLB\_DATA\_P. The signal-ended output voltage of a driver is defined as V<sub>O-</sub> on MLB\_CLK\_N, MLB\_SIG\_N, and MLB\_DATA\_N.

<sup>2</sup> Variations in the common-mode voltage can occur between logic states (for example, during state transitions) as a result of differences in the transition rate of V<sub>Q+</sub> and V<sub>Q-</sub>.

$^3\,$  Short circuit current is applicable when V\_{O\_{+}} and V\_{O\_{-}} are shorted together and/or shorted to ground.

$^4\,$  The logic state of the receiver is undefined when -50 mV < V\_{ID} < 50 mV.

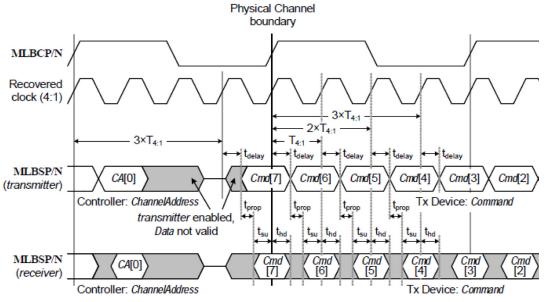

| Parameter                                                                                                              | Symbol              | Min  | Max | Unit | Comment |

|------------------------------------------------------------------------------------------------------------------------|---------------------|------|-----|------|---------|

| Cycle-to-cycle system jitter                                                                                           | t <sub>jitter</sub> | _    | 600 | ps   | —       |

| Transmitter MLB_SIG_P/_N<br>(MLB_DATA_P/_N) output valid from transition<br>of MLB_CLK_P/_N (low-to-high) <sup>1</sup> | t <sub>delay</sub>  | 0.6  | 1.3 | ns   | _       |

| Disable turnaround time from transition of MLB_CLK_P/_N (low-to-high)                                                  | t <sub>phz</sub>    | 0.6  | 3.5 | ns   | _       |

| Enable turnaround time from transition of MLB_CLK_P/_N (low-to-high)                                                   | t <sub>plz</sub>    | 0.6  | 5.6 | ns   | —       |

| MLB_SIG_P/_N (MLB_DATA_P/_N) valid to transition of MLB_CLK_P/_N (low-to-high)                                         | t <sub>su</sub>     | 0.05 | —   | ns   | _       |

| MLB_SIG_P/_N (MLB_DATA_P/_N) hold from transition of MLB_CLK_P/_N (low-to-high) <sup>2</sup>                           | t <sub>hd</sub>     | 0.6  | —   | ns   | _       |

Table 75. MLB 6-Pin Interface Timing Parameters

t<sub>delay</sub>, t<sub>phz</sub>, t<sub>plz</sub>, t<sub>su</sub>, and t<sub>hd</sub> may also be referenced from a low-to-high transition of the recovered clock for 2:1 and 4:1 recovered-to-external clock ratios.

<sup>2</sup> The transmitting device must ensure valid data on MLB\_SIG\_P/\_N (MLB\_DATA\_P/\_N) for at least t<sub>hd(min)</sub> following the rising edge of MLBCP/N; receivers must latch MLB\_SIG\_P/\_N (MLB\_DATA\_P/\_N) data within t<sub>hd(min)</sub> of the rising edge of MLB\_CLK\_P/\_N.

Figure 82. MLB 6-Pin Delay, Setup, and Hold Times

### 4.12.15 PCIe PHY Parameters

The PCIe interface complies with PCIe specification Gen2 x1 lane and supports the PCI Express 1.1/2.0 standard.

1

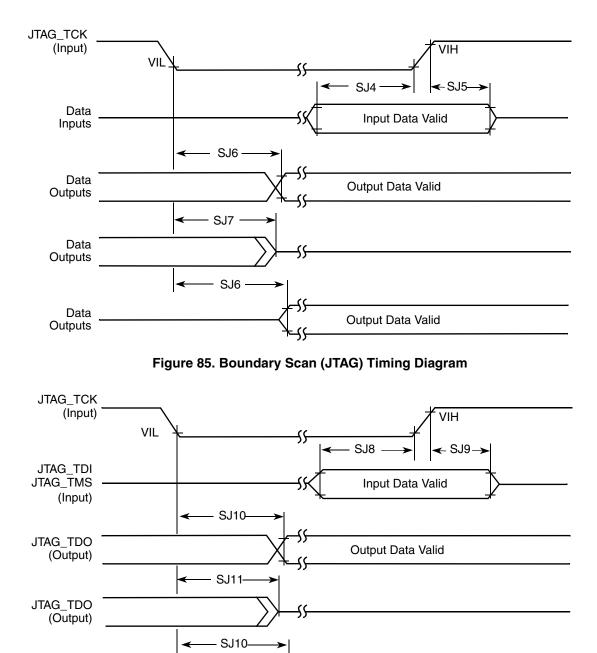

Figure 86. Test Access Port Timing Diagram

Output Data Valid

i.MX 6Dual/6Quad Applications Processors for Consumer Products, Rev. 5, 09/2017

JTAG\_TDO

(Output)

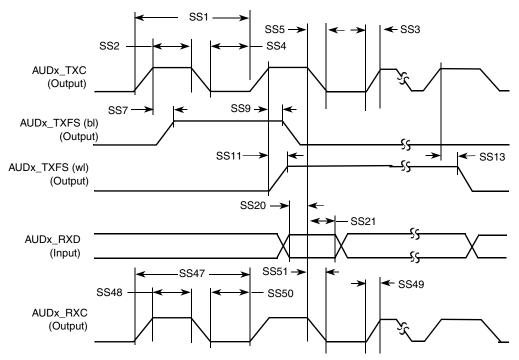

### 4.12.20.2 SSI Receiver Timing with Internal Clock

Figure 91 depicts the SSI receiver internal clock timing and Table 83 lists the timing parameters for the receiver timing with the internal clock.

Figure 91. SSI Receiver Internal Clock Timing Diagram

| Table 83. SSI Receiver | Timing with | Internal | Clock |

|------------------------|-------------|----------|-------|

|                        |             |          |       |

| ID   | Parameter                               | Min  | Мах  | Unit |

|------|-----------------------------------------|------|------|------|

|      | Internal Clock Operatio                 | n    |      |      |

| SS1  | AUDx_TXC/AUDx_RXC clock period          | 81.4 | —    | ns   |

| SS2  | AUDx_TXC/AUDx_RXC clock high period     | 36.0 | _    | ns   |

| SS3  | AUDx_TXC/AUDx_RXC clock rise time       | —    | 6.0  | ns   |

| SS4  | AUDx_TXC/AUDx_RXC clock low period      | 36.0 | _    | ns   |

| SS5  | AUDx_TXC/AUDx_RXC clock fall time       | —    | 6.0  | ns   |

| SS7  | AUDx_RXC high to AUDx_TXFS (bl) high    | —    | 15.0 | ns   |

| SS9  | AUDx_RXC high to AUDx_TXFS (bl) low     | —    | 15.0 | ns   |

| SS11 | AUDx_RXC high to AUDx_TXFS (wl) high    | —    | 15.0 | ns   |

| SS13 | AUDx_RXC high to AUDx_TXFS (wI) low     | —    | 15.0 | ns   |

| SS20 | AUDx_RXD setup time before AUDx_RXC low | 10.0 |      | ns   |

| SS21 | AUDx_RXD hold time after AUDx_RXC low   | 0.0  |      | ns   |

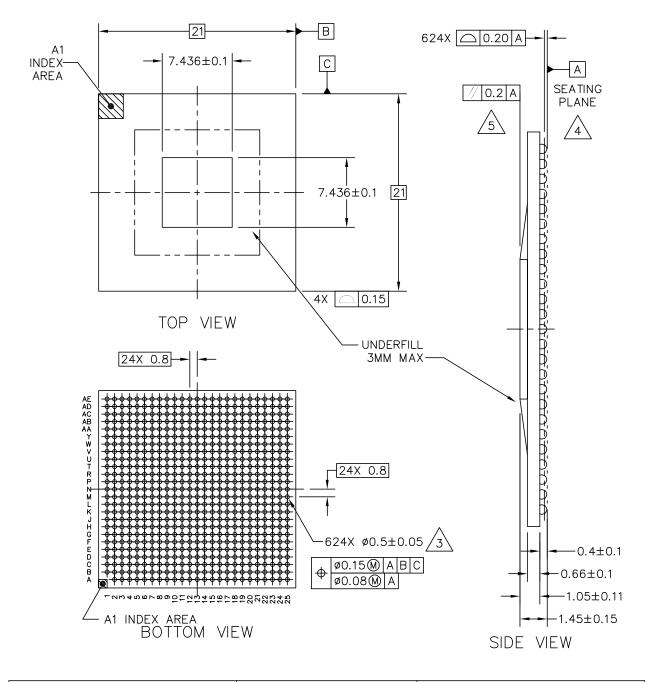

Package Information and Contact Assignments

| NXP SEMICONDUCTORS N.V.<br>ALL RIGHTS RESERVED |                     | MECHANICAL OU | TLINE              | PRINT VERSION NO | DT TO SCALE |

|------------------------------------------------|---------------------|---------------|--------------------|------------------|-------------|

| TITLE:                                         | 624 I/O FC PB0      | DOCUMEN       | NT NO: 98ASA00329D | REV: B           |             |

|                                                | 21 X 21 PŔG, 0.8 MM |               | STANDAR            | RD: JEDEC MS-034 |             |

|                                                | NO LID              |               |                    | -1               | 07 JAN 2016 |

Figure 100. 21 x 21 mm Bare Die Package Top, Bottom, and Side Views (Sheet 1 of 2)

### Package Information and Contact Assignments

|                           |      |             |           | Out of Reset Condition <sup>1</sup> |                                   |              |                    |  |  |  |

|---------------------------|------|-------------|-----------|-------------------------------------|-----------------------------------|--------------|--------------------|--|--|--|

| Ball Name                 | Ball | Power Group | Ball Type | Default<br>Mode<br>(Reset<br>Mode)  | Default Function<br>(Signal Name) | Input/Output | Value <sup>2</sup> |  |  |  |

| EIM_DA6                   | K25  | NVCC_EIM2   | GPIO      | ALT0                                | EIM_AD06                          | Input        | PU (100K)          |  |  |  |

| EIM_DA7                   | L25  | NVCC_EIM2   | GPIO      | ALT0                                | EIM_AD07                          | Input        | PU (100K)          |  |  |  |

| EIM_DA8                   | L24  | NVCC_EIM2   | GPIO      | ALT0                                | EIM_AD08                          | Input        | PU (100K)          |  |  |  |

| EIM_DA9                   | M21  | NVCC_EIM2   | GPIO      | ALT0                                | EIM_AD09                          | Input        | PU (100K)          |  |  |  |

| EIM_DA10                  | M22  | NVCC_EIM2   | GPIO      | ALT0                                | EIM_AD10                          | Input        | PU (100K)          |  |  |  |

| EIM_DA11                  | M20  | NVCC_EIM2   | GPIO      | ALT0                                | EIM_AD11                          | Input        | PU (100K)          |  |  |  |

| EIM_DA12                  | M24  | NVCC_EIM2   | GPIO      | ALT0                                | EIM_AD12                          | Input        | PU (100K)          |  |  |  |

| EIM_DA13                  | M23  | NVCC_EIM2   | GPIO      | ALT0                                | EIM_AD13                          | Input        | PU (100K)          |  |  |  |

| EIM_DA14                  | N23  | NVCC_EIM2   | GPIO      | ALT0                                | EIM_AD14                          | Input        | PU (100K)          |  |  |  |

| EIM_DA15                  | N24  | NVCC_EIM2   | GPIO      | ALT0                                | EIM_AD15                          | Input        | PU (100K)          |  |  |  |

| EIM_EB0                   | K21  | NVCC_EIM2   | GPIO      | ALT0                                | EIM_EB0_B                         | Output       | 1                  |  |  |  |

| EIM_EB1                   | K23  | NVCC_EIM2   | GPIO      | ALT0                                | EIM_EB1_B                         | Output       | 1                  |  |  |  |

| EIM_EB2                   | E22  | NVCC_EIM0   | GPIO      | ALT5                                | GPIO2_IO30                        | Input        | PU (100K)          |  |  |  |

| EIM_EB3                   | F23  | NVCC_EIM0   | GPIO      | ALT5                                | GPIO2_IO31                        | Input        | PU (100K)          |  |  |  |

| EIM_LBA                   | K22  | NVCC_EIM1   | GPIO      | ALT0                                | EIM_LBA_B                         | Output       | 1                  |  |  |  |

| EIM_OE                    | J24  | NVCC_EIM1   | GPIO      | ALT0                                | EIM_OE                            | Output       | 1                  |  |  |  |

| EIM_RW                    | K20  | NVCC_EIM1   | GPIO      | ALT0                                | EIM_RW                            | Output       | 1                  |  |  |  |

| EIM_WAIT                  | M25  | NVCC_EIM2   | GPIO      | ALT0                                | EIM_WAIT                          | Input        | PU (100K)          |  |  |  |

| ENET_CRS_DV               | U21  | NVCC_ENET   | GPIO      | ALT5                                | GPIO1_IO25                        | Input        | PU (100K)          |  |  |  |

| ENET_MDC                  | V20  | NVCC_ENET   | GPIO      | ALT5                                | GPIO1_IO31                        | Input        | PU (100K)          |  |  |  |

| ENET_MDIO                 | V23  | NVCC_ENET   | GPIO      | ALT5                                | GPIO1_IO22                        | Input        | PU (100K)          |  |  |  |

| ENET_REF_CLK <sup>3</sup> | V22  | NVCC_ENET   | GPIO      | ALT5                                | GPIO1_IO23                        | Input        | PU (100K)          |  |  |  |

| ENET_RX_ER                | W23  | NVCC_ENET   | GPIO      | ALT5                                | GPIO1_IO24                        | Input        | PU (100K)          |  |  |  |

| ENET_RXD0                 | W21  | NVCC_ENET   | GPIO      | ALT5                                | GPI01_I027                        | Input        | PU (100K)          |  |  |  |

| ENET_RXD1                 | W22  | NVCC_ENET   | GPIO      | ALT5                                | GPIO1_IO26                        | Input        | PU (100K)          |  |  |  |

| ENET_TX_EN                | V21  | NVCC_ENET   | GPIO      | ALT5                                | GPIO1_IO28                        | Input        | PU (100K)          |  |  |  |

| ENET_TXD0                 | U20  | NVCC_ENET   | GPIO      | ALT5                                | GPIO1_IO30                        | Input        | PU (100K)          |  |  |  |

| ENET_TXD1                 | W20  | NVCC_ENET   | GPIO      | ALT5                                | GPIO1_IO29                        | Input        | PU (100K)          |  |  |  |

| GPIO_0                    | T5   | NVCC_GPIO   | GPIO      | ALT5                                | GPIO1_IO00                        | Input        | PD (100K)          |  |  |  |

| GPIO_1                    | T4   | NVCC_GPIO   | GPIO      | ALT5                                | GPIO1_IO01                        | Input        | PU (100K)          |  |  |  |

| GPIO_16                   | R2   | NVCC_GPIO   | GPIO      | ALT5                                | GPIO7_IO11                        | Input        | PU (100K)          |  |  |  |

| GPIO_17                   | R1   | NVCC_GPIO   | GPIO      | ALT5                                | GPIO7_IO12                        | Input        | PU (100K)          |  |  |  |

| GPIO_18                   | P6   | NVCC_GPIO   | GPIO      | ALT5                                | GPIO7_IO13                        | Input        | PU (100K)          |  |  |  |

| GPIO_19                   | P5   | NVCC_GPIO   | GPIO      | ALT5                                | GPIO4_IO05                        | Input        | PU (100K)          |  |  |  |

| GPIO_2                    | T1   | NVCC_GPIO   | GPIO      | ALT5                                | GPIO1_IO02                        | Input        | PU (100K)          |  |  |  |

| GPIO_3                    | R7   | NVCC_GPIO   | GPIO      | ALT5                                | GPIO1_IO03                        | Input        | PU (100K)          |  |  |  |

Table 96. 21 x 21 mm Functional Contact Assignments (continued)