# E·XFL

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                            |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Active                                                                                                              |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 4 Core, 32-Bit                                                                                                      |

| Speed                              | 1.0GHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                                              |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | SATA 3Gbps (1)                                                                                                      |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | -20°C ~ 105°C (TJ)                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-LFBGA, FCBGA                                                                                                    |

| Supplier Device Package            | 624-FCPBGA (21x21)                                                                                                  |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6q5eym10aer                                            |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.1 Ordering Information

Table 1 shows examples of orderable part numbers covered by this data sheet. This table does not include all possible orderable part numbers. The latest part numbers are available on nxp.com/imx6series. If your desired part number is not listed in the table, or you have questions about available parts, see nxp.com/imx6series or contact your NXP representative.

| Part Number     | Quad/Dual CPU | Options                    | Speed <sup>1</sup><br>Grade | Temperature<br>Grade   | Package                                             |

|-----------------|---------------|----------------------------|-----------------------------|------------------------|-----------------------------------------------------|

| MCIMX6Q5EYM10AC | i.MX 6Quad    | Includes VPU, GPU          | 1 GHz                       | Extended<br>Commercial | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (non-lidded) |

| MCIMX6Q5EYM10AD | i.MX 6Quad    | Includes VPU, GPU          | 1 GHz                       | Extended<br>Commercial | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (non-lidded) |

| MCIMX6Q5EYM10AE | i.MX 6Quad    | Includes VPU, GPU          | 1 GHz                       | Extended<br>Commercial | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (non-lidded) |

| SCIMX6Q5EYM10CC | i.MX 6Quad    | Includes VPU, GPU,<br>HDCP | 1 GHz                       | Extended<br>Commercial | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (non-lidded) |

| SCIMX6Q5EYM10CD | i.MX 6Quad    | Includes VPU, GPU,<br>HDCP | 1 GHz                       | Extended<br>Commercial | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (non-lidded) |

| SCIMX6Q5EYM10CE | i.MX 6Quad    | Includes VPU, GPU,<br>HDCP | 1 GHz                       | Extended<br>Commercial | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (non-lidded) |

| MCIMX6D5EYM10AC | i.MX 6Dual    | Includes VPU, GPU          | 1 GHz                       | Extended<br>Commercial | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (non-lidded) |

| MCIMX6D5EYM10AD | i.MX 6Dual    | Includes VPU, GPU          | 1 GHz                       | Extended<br>Commercial | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (non-lidded) |

| MCIMX6D5EYM10AE | i.MX 6Dual    | Includes VPU, GPU          | 1 GHz                       | Extended<br>Commercial | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (non-lidded) |

| SCIMX6D5EYM10CC | i.MX 6Dual    | Includes VPU, GPU,<br>HDCP | 1 GHz                       | Extended<br>Commercial | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (non-lidded) |

| SCIMX6D5EYM10CD | i.MX 6Dual    | Includes VPU, GPU,<br>HDCP | 1 GHz                       | Extended<br>Commercial | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (non-lidded) |

| SCIMX6D5EYM10CE | i.MX 6Dual    | Includes VPU, GPU,<br>HDCP | 1 GHz                       | Extended<br>Commercial | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (non-lidded) |

| MCIMX6Q5EYM12AC | i.MX 6Quad    | Includes VPU, GPU          | 1.2 GHz                     | Extended<br>Commercial | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (non-lidded) |

| MCIMX6Q5EYM12AD | i.MX 6Quad    | Includes VPU, GPU          | 1.2 GHz                     | Extended<br>Commercial | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (non-lidded) |

| MCIMX6Q5EYM12AE | i.MX 6Quad    | Includes VPU, GPU          | 1.2 GHz                     | Extended<br>Commercial | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (non-lidded) |

| SCIMX6Q5EYM12CC | i.MX 6Quad    | Includes VPU, GPU,<br>HCP  | 1.2 GHz                     | Extended<br>Commercial | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (non-lidded) |

| SCIMX6Q5EYM12CD | i.MX 6Quad    | Includes VPU, GPU,<br>HCP  | 1.2 GHz                     | Extended<br>Commercial | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (non-lidded) |

| Table 1. | Example | Orderable | Part | Numbers |

|----------|---------|-----------|------|---------|

|----------|---------|-----------|------|---------|

| Table 2. i.MX 6Dual/6Quad Modules List (d | continued) |

|-------------------------------------------|------------|

|-------------------------------------------|------------|

| Block<br>Mnemonic                | Block Name                    | Subsystem                                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------|-------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LDB                              | LVDS Display Bridge           | Connectivity<br>Peripherals                 | <ul> <li>LVDS Display Bridge is used to connect the IPU (Image Processing Unit) to External LVDS Display Interface. LDB supports two channels; each channel has following signals:</li> <li>One clock pair</li> <li>Four data pairs</li> <li>Each signal pair contains LVDS special differential pad (PadP, PadM).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MLB150                           | MediaLB                       | Connectivity /<br>Multimedia<br>Peripherals | The MLB interface module provides a link to a MOST <sup>®</sup> data network, using the standardized MediaLB protocol (up to 150 Mbps). The module is backward compatible to MLB-50.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MMDC                             | Multi-Mode DDR<br>Controller  | Connectivity<br>Peripherals                 | <ul> <li>DDR Controller has the following features:</li> <li>Supports 16/32/64-bit DDR3 / DDR3L or LPDDR2</li> <li>Supports both dual x32 for LPDDR2 and x64 DDR3 / LPDDR2 configurations (including 2x32 interleaved mode)</li> <li>Supports up to 4 GByte DDR memory space</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OCOTP_CTRL                       | OTP Controller                | Security                                    | The On-Chip OTP controller (OCOTP_CTRL) provides an interface for reading, programming, and/or overriding identification and control information stored in on-chip fuse elements. The module supports electrically-programmable poly fuses (eFUSEs). The OCOTP_CTRL also provides a set of volatile software-accessible signals that can be used for software control of hardware elements, not requiring non-volatility. The OCOTP_CTRL provides the primary user-visible mechanism for interfacing with on-chip fuse elements. Among the uses for the fuses are unique chip identifiers, mask revision numbers, cryptographic keys, JTAG secure mode, boot characteristics, and various control signals, requiring permanent non-volatility. |

| OCRAM                            | On-Chip Memory<br>Controller  | Data Path                                   | The On-Chip Memory controller (OCRAM) module is designed as an interface between system's AXI bus and internal (on-chip) SRAM memory module.<br>In i.MX 6Dual/6Quad processors, the OCRAM is used for controlling the 256 KB multimedia RAM through a 64-bit AXI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| OSC 32 kHz                       | OSC 32 kHz                    | Clocking                                    | Generates 32.768 kHz clock from an external crystal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PCle                             | PCI Express 2.0               | Connectivity<br>Peripherals                 | The PCIe IP provides PCI Express Gen 2.0 functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PMU                              | Power-Management<br>Functions | Data Path                                   | Integrated power management unit. Used to provide power to various SoC domains.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PWM-1<br>PWM-2<br>PWM-3<br>PWM-4 | Pulse Width<br>Modulation     | Connectivity<br>Peripherals                 | The pulse-width modulator (PWM) has a 16-bit counter and is optimized to generate sound from stored sample audio images and it can also generate tones. It uses 16-bit resolution and a 4x16 data FIFO to generate sound.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RAM<br>16 KB                     | Secure/non-secure<br>RAM      | Secured<br>Internal<br>Memory               | Secure/non-secure Internal RAM, interfaced through the CAAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RAM<br>256 KB                    | Internal RAM                  | Internal<br>Memory                          | Internal RAM, which is accessed through OCRAM memory controllers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

### **Modules List**

| Block<br>Mnemonic | Block Name                                  | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|---------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROM<br>96 KB      | Boot ROM                                    | Internal<br>Memory               | Supports secure and regular Boot Modes. Includes read protection on 4K region for content protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ROMCP             | ROM Controller with Patch                   | Data Path                        | ROM Controller with ROM Patch support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SATA              | Serial ATA                                  | Connectivity<br>Peripherals      | The SATA controller and PHY is a complete mixed-signal IP solution designed to implement SATA II, 3.0 Gbps HDD connectivity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SDMA              | Smart Direct Memory<br>Access               | System<br>Control<br>Peripherals | <ul> <li>The SDMA is multi-channel flexible DMA engine. It helps in maximizing system performance by off-loading the various cores in dynamic data routing. It has the following features:</li> <li>Powered by a 16-bit Instruction-Set micro-RISC engine</li> <li>Multi-channel DMA supporting up to 32 time-division multiplexed DMA channels</li> <li>48 events with total flexibility to trigger any combination of channels</li> <li>Memory accesses including linear, FIFO, and 2D addressing</li> <li>Shared peripherals between ARM and SDMA</li> <li>Very fast context-switching with 2-level priority based preemptive multi-tasking</li> <li>DMA units with auto-flush and prefetch capability</li> <li>Flexible address management for DMA transfers (increment, decrement, and no address changes on source and destination address)</li> <li>DMA ports can handle unit-directional and bi-directional flows (copy mode)</li> <li>Up to 8-word buffer for configurable burst transfers</li> <li>Support of byte-swapping and CRC calculations</li> <li>Library of Scripts and API is available</li> </ul> |

| SJC               | System JTAG<br>Controller                   | System<br>Control<br>Peripherals | The SJC provides JTAG interface, which complies with JTAG TAP standards, to internal logic. The i.MX 6Dual/6Quad processors use JTAG port for production, testing, and system debugging. In addition, the SJC provides BSR (Boundary Scan Register) standard support, which complies with IEEE1149.1 and IEEE1149.6 standards. The JTAG port must be accessible during platform initial laboratory bring-up, for manufacturing tests and troubleshooting, as well as for software debugging by authorized entities. The i.MX 6Dual/6Quad SJC incorporates three security modes for protecting against unauthorized accesses. Modes are selected through eFUSE configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SNVS              | Secure Non-Volatile<br>Storage              | Security                         | Secure Non-Volatile Storage, including Secure Real Time Clock, Security State Machine, Master Key Control, and Violation/Tamper Detection and reporting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SPDIF             | Sony Philips Digital<br>Interconnect Format | Multimedia<br>Peripherals        | A standard audio file transfer format, developed jointly by the Sony and<br>Phillips corporations. It supports Transmitter and Receiver functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Table 2. i.MX 6Dual/6Quad Modules List (ce | continued) |

|--------------------------------------------|------------|

|--------------------------------------------|------------|

| Table 2. i.MX 6Dual/6Quad Modules List (continued) |

|----------------------------------------------------|

|----------------------------------------------------|

| Block<br>Mnemonic                              | Block Name                                   | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------|----------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSI-1<br>SSI-2<br>SSI-3                        | I2S/SSI/AC97<br>Interface                    | Connectivity<br>Peripherals      | The SSI is a full-duplex synchronous interface, which is used on the processor to provide connectivity with off-chip audio peripherals. The SSI supports a wide variety of protocols (SSI normal, SSI network, I2S, and AC-97), bit depths (up to 24 bits per word), and clock / frame sync options. The SSI has two pairs of 8x24 FIFOs and hardware support for an external DMA controller to minimize its impact on system performance. The second pair of FIFOs provides hardware interleaving of a second audio stream that reduces CPU overhead in use cases where two time slots are being used simultaneously. |

| TEMPMON                                        | Temperature Monitor                          | System<br>Control<br>Peripherals | The temperature monitor/sensor IP module for detecting high temperature conditions. The temperature read out does not reflect case or ambient temperature. It reflects the temperature in proximity of the sensor location on the die. Temperature distribution may not be uniformly distributed; therefore, the read out value may not be the reflection of the temperature value for the entire die.                                                                                                                                                                                                                 |

| TZASC                                          | Trust-Zone Address<br>Space Controller       | Security                         | The TZASC (TZC-380 by ARM) provides security address region control functions required for intended application. It is used on the path to the DRAM controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| UART-1<br>UART-2<br>UART-3<br>UART-4<br>UART-5 | UART Interface                               | Connectivity<br>Peripherals      | <ul> <li>Each of the UARTv2 modules support the following serial data transmit/receive protocols and configurations:</li> <li>7- or 8-bit data words, 1 or 2 stop bits, programmable parity (even, odd or none)</li> <li>Programmable baud rates up to 5 MHz</li> <li>32-byte FIFO on Tx and 32 half-word FIFO on Rx supporting auto-baud</li> <li>IrDA 1.0 support (up to SIR speed of 115200 bps)</li> <li>Option to operate as 8-pins full UART, DCE, or DTE</li> </ul>                                                                                                                                             |

| USBOH3A                                        | USB 2.0 High Speed<br>OTG and 3x HS<br>Hosts | Connectivity<br>Peripherals      | <ul> <li>USBOH3 contains:</li> <li>One high-speed OTG module with integrated HS USB PHY</li> <li>One high-speed Host module with integrated HS USB PHY</li> <li>Two identical high-speed Host modules connected to HSIC USB ports.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                          |

| Parameter Description                                                       | Symbol                            | Min  | Мах                     | Unit |

|-----------------------------------------------------------------------------|-----------------------------------|------|-------------------------|------|

| Core supply input voltage (LDO enabled)                                     | VDD_ARM_IN                        |      |                         |      |

|                                                                             | VDD_ARM23_IN                      | -0.3 | 1.6                     | V    |

|                                                                             | VDD_SOC_IN                        |      |                         |      |

| Core supply input voltage (LDO bypass)                                      | VDD_ARM_IN                        |      |                         |      |

|                                                                             | VDD_ARM23_IN                      | -0.3 | 1.4                     | V    |

|                                                                             | VDD_SOC_IN                        |      |                         |      |

| Core supply output voltage (LDO enabled)                                    | VDD_ARM_CAP                       |      |                         |      |

|                                                                             | VDD_SOC_CAP                       | -0.3 | 1.4                     | V    |

|                                                                             | VDD_PU_CAP                        | 0.0  |                         | •    |

|                                                                             | NVCC_PLL_OUT                      |      |                         |      |

| VDD_HIGH_IN supply voltage                                                  | VDD_HIGH_IN                       | -0.3 | 3.7                     | V    |

| DDR I/O supply voltage                                                      | NVCC_DRAM                         | -0.4 | 1.975 (See note 1)      | V    |

| GPIO I/O supply voltage                                                     | NVCC_CSI                          |      |                         |      |

|                                                                             | NVCC_EIM                          |      |                         |      |

|                                                                             | NVCC_ENET                         |      |                         |      |

|                                                                             | NVCC_GPIO                         | -0.5 | 3.7                     | V    |

|                                                                             | NVCC_LCD                          |      |                         |      |

|                                                                             | NVCC_NAND                         |      |                         |      |

|                                                                             | NVCC_SD                           |      |                         |      |

|                                                                             | NVCC_JTAG                         |      |                         |      |

| HDMI, PCIe, and SATA PHY high (VPH) supply voltage                          | HDMI_VPH                          | 0.0  | 0.05                    | V    |

|                                                                             | PCIE_VPH                          | -0.3 | 2.85                    | v    |

|                                                                             | SATA_VPH                          |      |                         |      |

| HDMI, PCIe, and SATA PHY low (VP) supply voltage                            |                                   | -0.3 | 1.4                     | V    |

|                                                                             | PCIE_VP<br>SATA_VP                | -0.3 | 1.4                     | v    |

| LVDO MUD and MUDI //O anarchinestrate (O E) / anarchi)                      |                                   |      |                         |      |

| LVDS, MLB, and MIPI I/O supply voltage (2.5V supply)                        | NVCC_LVDS_2P5<br>NVCC_MIPI        | -0.3 | 2.85                    | V    |

| PCIe PHY supply voltage                                                     | PCIE_VPTX                         | -0.3 | 1.4                     | V    |

| RGMII I/O supply voltage                                                    | NVCC_RGMII                        | -0.5 | 2.725                   | V    |

| SNVS IN supply voltage                                                      | VDD_SNVS_IN                       | -0.3 | 3.4                     | V    |

| (Secure Non-Volatile Storage and Real Time Clock)                           |                                   | 0.0  | 0.4                     | v    |

| USB I/O supply voltage                                                      | USB_H1_DN                         |      |                         |      |

|                                                                             | USB_H1_DP                         |      |                         |      |

|                                                                             | USB_OTG_DN                        | -0.3 | 3.73                    | V    |

|                                                                             | USB_OTG_DP                        |      |                         |      |

|                                                                             | USB_OTG_CHD_B                     |      |                         |      |

| USB VBUS supply voltage                                                     | USB_H1_VBUS                       |      | 5.35                    | V    |

|                                                                             | USB_OTG_VBUS                      |      |                         | v    |

| V <sub>in</sub> /V <sub>out</sub> input/output voltage range (non-DDR pins) | V <sub>in</sub> /V <sub>out</sub> | -0.5 | OVDD+0.3 (See note 2)   | V    |

| V <sub>in</sub> /V <sub>out</sub> input/output voltage range (DDR pins)     | V <sub>in</sub> /V <sub>out</sub> | -0.5 | OVDD+0.4 (See notes1&2) | V    |

| ESD immunity (HBM)                                                          | V <sub>esd_HBM</sub>              | —    | 2000                    | V    |

| ESD immunity (CDM)                                                          | V <sub>esd_CDM</sub>              | —    | 500                     | V    |

| Storage temperature range                                                   | T <sub>storage</sub>              | -40  | 150                     | °C   |

|                                                                             | Sidiage                           | L    | l                       |      |

### **Table 4. Absolute Maximum Ratings**

<sup>1</sup> The absolute maximum voltage includes an allowance for 400 mV of overshoot on the IO pins. Per JEDEC standards, the allowed signal overshoot must be derated if NVCC\_DRAM exceeds 1.575V.

<sup>2</sup> OVDD is the I/O supply voltage.

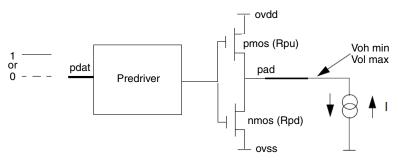

Figure 3. Circuit for Parameters Voh and Vol for I/O Cells

# 4.6.1 XTALI and RTC\_XTALI (Clock Inputs) DC Parameters

Table 21 shows the DC parameters for the clock inputs.

| Table 21. XTALI and RTC_ | XTALI DC Parameters |

|--------------------------|---------------------|

|--------------------------|---------------------|

| Parameter                              | Symbol                     | Test Conditions                                                                              | Min                | Тур | Max                         | Unit |

|----------------------------------------|----------------------------|----------------------------------------------------------------------------------------------|--------------------|-----|-----------------------------|------|

| XTALI high-level DC input voltage      | Vih                        | _                                                                                            | 0.8 x NVCC_PLL_OUT | —   | NVCC_PLL_ OUT               | V    |

| XTALI low-level DC input voltage       | Vil                        | —                                                                                            | 0                  | —   | 0.2                         | V    |

| RTC_XTALI high-level DC input voltage  | Vih                        | —                                                                                            | 0.8                | _   | 1.1 <sup>(See note 1)</sup> | V    |

| RTC_XTALI low-level DC input voltage   | Vil                        | —                                                                                            | 0                  | _   | 0.2                         | V    |

| Input capacitance                      | C <sub>IN</sub>            | Simulated data                                                                               | —                  | 5   | —                           | pF   |

| XTALI input leakage current at startup | I <sub>XTALI_STARTUP</sub> | Power-on startup for<br>0.15 msec with a driven<br>32 KHz RTC clock<br>@ 1.1 V. <sup>2</sup> | _                  | —   | 600                         | μA   |

| DC input current                       | I <sub>XTALI_DC</sub>      | —                                                                                            | —                  | —   | 2.5                         | μΑ   |

<sup>1</sup> This voltage specification must not be exceeded and, as such, is an absolute maximum specification.

<sup>2</sup> This current draw is present even if an external clock source directly drives XTALI.

### NOTE

The Vil and Vih specifications only apply when an external clock source is used. If a crystal is used, Vil and Vih do not apply.

# 4.6.2 General Purpose I/O (GPIO) DC Parameters

Table 22 shows DC parameters for GPIO pads. The parameters in Table 22 are guaranteed per the operating ranges in Table 6, unless otherwise noted.

| Parameter                              | Symbol                   | Test Conditions                                                      | Min       | Max       | Units |

|----------------------------------------|--------------------------|----------------------------------------------------------------------|-----------|-----------|-------|

| High-level output voltage <sup>1</sup> | V <sub>OH</sub>          | loh= -0.1 mA (DSE=001,010)<br>loh= -1.0 mA (DSE=011,100,101,110,111) | OVDD-0.15 | _         | V     |

| Low-level output voltage <sup>1</sup>  | V <sub>OL</sub>          | lol= 0.1 mA (DSE=001,010)<br>lol= 1.0 mA (DSE=011,100,101,110,111)   | —         | 0.15      | V     |

| Input Reference Voltage                | V <sub>ref</sub>         | _                                                                    | 0.49xOVDD | 0.51xOVDD | V     |

| High-Level input voltage 2, 3          | V <sub>IH</sub>          | _                                                                    | 0.7xOVDD  | OVDD      | V     |

| Low-Level input voltage 2, 3           | V <sub>IL</sub>          | _                                                                    | 0         | 0.3xOVDD  | V     |

| Input Hysteresis(OVDD=1.8V)            | V <sub>HYS_HighVDD</sub> | OVDD=1.8V                                                            | 250       | _         | mV    |

| Input Hysteresis(OVDD=2.5V)            | V <sub>HYS_HighVDD</sub> | OVDD=2.5V                                                            | 250       | _         | mV    |

| Schmitt trigger VT+ 3, 4               | V <sub>TH+</sub>         |                                                                      | 0.5xOVDD  | —         | mV    |

| Schmitt trigger VT- 3, 4               | V <sub>TH-</sub>         | _                                                                    | —         | 0.5xOVDD  | mV    |

| Pull-up resistor (22 k $\Omega$ PU)    | R <sub>PU_22K</sub>      | V <sub>in</sub> =0V                                                  | —         | 212       | μA    |

| Pull-up resistor (22 k $\Omega$ PU)    | R <sub>PU_22K</sub>      | V <sub>in</sub> =OVDD                                                | —         | 1         | μA    |

| Pull-up resistor (47 k $\Omega$ PU)    | R <sub>PU_47K</sub>      | V <sub>in</sub> =0V                                                  | —         | 100       | μA    |

| Pull-up resistor (47 k $\Omega$ PU)    | R <sub>PU_47K</sub>      | V <sub>in</sub> =OVDD                                                | —         | 1         | μA    |

| Pull-up resistor (100 k $\Omega$ PU)   | R <sub>PU_100K</sub>     | V <sub>in</sub> =0V                                                  | —         | 48        | μA    |

| Pull-up resistor (100 k $\Omega$ PU)   | R <sub>PU_100K</sub>     | V <sub>in</sub> =OVDD                                                | —         | 1         | μA    |

| Pull-down resistor (100 k $\Omega$ PD) | R <sub>PD_100K</sub>     | V <sub>in</sub> =OVDD                                                | —         | 48        | μA    |

| Pull-down resistor (100 k $\Omega$ PD) | R <sub>PD_100K</sub>     | V <sub>in</sub> =0V                                                  | -         | 1         | μA    |

| Keeper Circuit Resistance              | R <sub>keep</sub>        | —                                                                    | 105       | 165       | kΩ    |

| Input current (no pull-up/down)        | l <sub>in</sub>          | $V_{I} = 0, VI = OVDD$                                               | -2.9      | 2.9       | μA    |

Input Mode Selection: SW\_PAD\_CTL\_GRP\_DDR\_TYPE\_RGMII = 10 (1.8V Mode) SW\_PAD\_CTL\_GRP\_DDR\_TYPE\_RGMII = 11 (2.5V Mode)

<sup>2</sup> Overshoot and undershoot conditions (transitions above OVDD and below GND) on switching pads must be held below 0.6 V, and the duration of the overshoot/undershoot must not exceed 10% of the system clock cycle. Overshoot/ undershoot must be controlled through printed circuit board layout, transmission line impedance matching, signal line termination, or other methods. Non-compliance to this specification may affect device reliability or cause permanent damage to the device.

<sup>3</sup> To maintain a valid level, the transition edge of the input must sustain a constant slew rate (monotonic) from the current DC level through to the target DC level, Vil or Vih. Monotonic input transition time is from 0.1 ns to 1 s.

<sup>4</sup> Hysteresis of 250 mV is guaranteed over all operating conditions when hysteresis is enabled (register IOMUXC\_SW\_PAD\_CTL\_PAD\_RGMII\_TXC[HYS]= 0).

# 4.6.4.1 LPDDR2 Mode I/O DC Parameters

For details on supported DDR memory configurations, see Section 4.10.2, "MMDC Supported DDR3/DDR3L/LPDDR2 Configurations."

The parameters in Table 24 are guaranteed per the operating ranges in Table 6, unless otherwise noted.

# 4.11.1 Asynchronous Mode AC Timing (ONFI 1.0 Compatible)

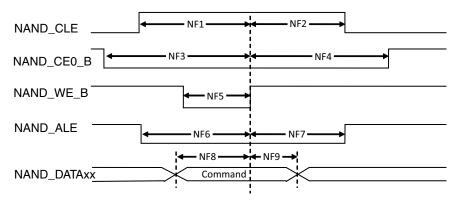

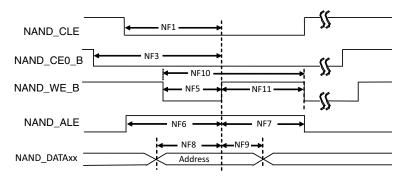

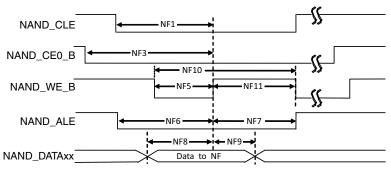

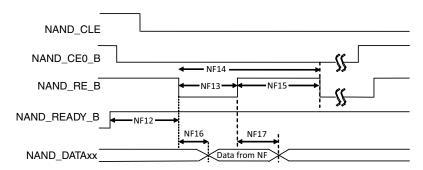

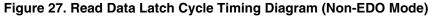

Asynchronous mode AC timings are provided as multiplications of the clock cycle and fixed delay. The Maximum I/O speed of GPMI in Asynchronous mode is about 50 MB/s. Figure 24 through Figure 27 depict the relative timing between GPMI signals at the module level for different operations under Asynchronous mode. Table 44 describes the timing parameters (NF1–NF17) that are shown in the figures.

Figure 24. Command Latch Cycle Timing Diagram

Figure 25. Address Latch Cycle Timing Diagram

Figure 28. Read Data Latch Cycle Timing Diagram (EDO Mode)

| ID   | Parameter                | Symbol           | Tim<br>T = GPMI C                          |                             | Unit |

|------|--------------------------|------------------|--------------------------------------------|-----------------------------|------|

|      |                          |                  | Min                                        | Мах                         |      |

| NF1  | NAND_CLE setup time      | tCLS             | (AS + DS) × T - 0.12 [see <sup>2,3</sup> ] |                             | ns   |

| NF2  | NAND_CLE hold time       | tCLH             | DH × T - 0.                                | .72 [see <sup>2</sup> ]     | ns   |

| NF3  | NAND_CEx_B setup time    | tCS              | (AS + DS + 1)                              | ) × T [see <sup>3,2</sup> ] | ns   |

| NF4  | NAND_CEx_B hold time     | tCH              | (DH+1) × T                                 | - 1 [see <sup>2</sup> ]     | ns   |

| NF5  | NAND_WE_B pulse width    | tWP              | $DS \times T$ [see <sup>2</sup> ]          |                             | ns   |

| NF6  | NAND_ALE setup time      | tALS             | (AS + DS) × T - 0.49 [see <sup>3,2</sup> ] |                             | ns   |

| NF7  | NAND_ALE hold time       | tALH             | (DH × T - 0                                | .42 [see <sup>2</sup> ]     | ns   |

| NF8  | Data setup time          | tDS              | DS × T - 0.                                | 26 [see <sup>2</sup> ]      | ns   |

| NF9  | Data hold time           | tDH              | DH × T - 1.                                | .37 [see <sup>2</sup> ]     | ns   |

| NF10 | Write cycle time         | tWC              | (DS + DH)                                  | × T [see <sup>2</sup> ]     | ns   |

| NF11 | NAND_WE_B hold time      | tWH              | DH 	imes T                                 | [see <sup>2</sup> ]         | ns   |

| NF12 | Ready to NAND_RE_B low   | tRR <sup>4</sup> | (AS + 2) × T [see <sup>3,2</sup> ] —       |                             | ns   |

| NF13 | NAND_RE_B pulse width    | tRP              | $DS \times T$ [see <sup>2</sup> ]          |                             | ns   |

| NF14 | READ cycle time          | tRC              | $(DS + DH) \times T [see ^2]$              |                             | ns   |

| NF15 | NAND_RE_B high hold time | tREH             | DH × T                                     | [see <sup>2</sup> ]         | ns   |

| Table 44. As | synchronous | Mode | Timing | Parameters <sup>1</sup> | l |

|--------------|-------------|------|--------|-------------------------|---|

|--------------|-------------|------|--------|-------------------------|---|

# 4.12.4.4 Bus Operation Condition for 3.3 V and 1.8 V Signaling

Signalling level of SD/eMMC4.3 and eMMC4.4/4.41 modes is 3.3 V. Signalling level of SDR104/SDR50 mode is 1.8 V. The DC parameters for the NVCC\_SD1, NVCC\_SD2, and NVCC\_SD3 supplies are identical to those shown in Table 22, "GPIO I/O DC Parameters," on page 40.

# 4.12.5 Ethernet Controller (ENET) AC Electrical Specifications

# 4.12.5.1 ENET MII Mode Timing

This subsection describes MII receive, transmit, asynchronous inputs, and serial management signal timings.

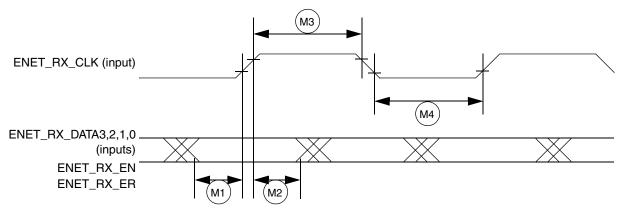

# 4.12.5.1.1 MII Receive Signal Timing (ENET\_RX\_DATA3,2,1,0, ENET\_RX\_EN, ENET\_RX\_ER, and ENET\_RX\_CLK)

The receiver functions correctly up to an ENET\_RX\_CLK maximum frequency of 25 MHz + 1%. There is no minimum frequency requirement. Additionally, the processor clock frequency must exceed twice the ENET\_RX\_CLK frequency.

Figure 42 shows MII receive signal timings. Table 53 describes the timing parameters (M1–M4) shown in the figure.

Figure 42. MII Receive Signal Timing Diagram

| Table 53 | MII | Receive | Signal | Timing |

|----------|-----|---------|--------|--------|

|----------|-----|---------|--------|--------|

| ID | Characteristic <sup>1</sup>                                        | Min | Max | Unit               |

|----|--------------------------------------------------------------------|-----|-----|--------------------|

| M1 | ENET_RX_DATA3,2,1,0, ENET_RX_EN, ENET_RX_ER to ENET_RX_CLK setup   | 5   | _   | ns                 |

| M2 | ENET_RX_CLK to ENET_RX_DATA3,2,1,0, ENET_RX_EN,<br>ENET_RX_ER hold | 5   | _   | ns                 |

| М3 | ENET_RX_CLK pulse width high                                       | 35% | 65% | ENET_RX_CLK period |

| M4 | ENET_RX_CLK pulse width low                                        | 35% | 65% | ENET_RX_CLK period |

<sup>1</sup> ENET\_RX\_EN, ENET\_RX\_CLK, and ENET0\_RXD0 have the same timing in 10 Mbps 7-wire interface mode.

| Table 55. MII Asynchronous | Inputs | Signal 7 | Гiming |

|----------------------------|--------|----------|--------|

|----------------------------|--------|----------|--------|

| ID              | Characteristic                           | Min | Max | Unit               |

|-----------------|------------------------------------------|-----|-----|--------------------|

| M9 <sup>1</sup> | ENET_CRS to ENET_COL minimum pulse width | 1.5 |     | ENET_TX_CLK period |

<sup>1</sup> ENET\_COL has the same timing in 10-Mbit 7-wire interface mode.

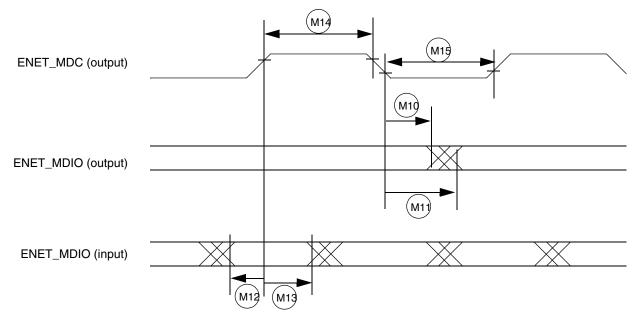

## 4.12.5.1.4 MII Serial Management Channel Timing (ENET\_MDIO and ENET\_MDC)

The MDC frequency is designed to be equal to or less than 2.5 MHz to be compatible with the IEEE 802.3 MII specification. However the ENET can function correctly with a maximum MDC frequency of 15 MHz.

Figure 45 shows MII asynchronous input timings. Table 56 describes the timing parameters (M10–M15) shown in the figure.

Figure 45. MII Serial Management Channel Timing Diagram

| Table 56. MII Serial Management Cha | nnel Timing |

|-------------------------------------|-------------|

|-------------------------------------|-------------|

| ID  | Characteristic                                                                | Min | Max | Unit            |

|-----|-------------------------------------------------------------------------------|-----|-----|-----------------|

| M10 | ENET_MDC falling edge to ENET_MDIO output invalid (minimum propagation delay) | 0   | _   | ns              |

| M11 | ENET_MDC falling edge to ENET_MDIO output valid (maximum propagation delay)   | _   | 5   | ns              |

| M12 | ENET_MDIO (input) to ENET_MDC rising edge setup                               | 18  | —   | ns              |

| M13 | ENET_MDIO (input) to ENET_MDC rising edge hold                                | 0   | —   | ns              |

| M14 | ENET_MDC pulse width high                                                     | 40% | 60% | ENET_MDC period |

| M15 | ENET_MDC pulse width low                                                      | 40% | 60% | ENET_MDC period |

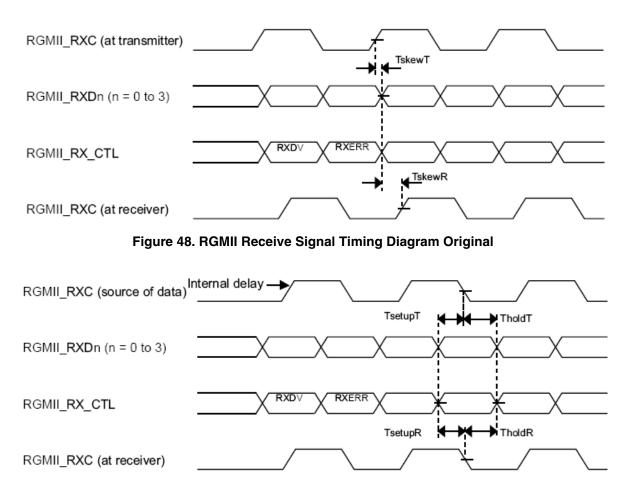

Figure 49. RGMII Receive Signal Timing Diagram with Internal Delay

# 4.12.6 Flexible Controller Area Network (FlexCAN) AC Electrical Specifications

The Flexible Controller Area Network (FlexCAN) module is a communication controller implementing the CAN protocol according to the CAN 2.0B protocol specification. The processor has two CAN modules available for systems design. Tx and Rx ports for both modules are multiplexed with other I/O pins. See the IOMUXC chapter of the i.MX 6Dual/6Quad reference manual (IMX6DQRM) to see which pins expose Tx and Rx pins; these ports are named FLEXCAN\_TX and FLEXCAN\_RX, respectively.

# 4.12.7 HDMI Module Timing Parameters

# 4.12.7.1 Latencies and Timing Information

Power-up time (time between TX\_PWRON assertion and TX\_READY assertion) for the HDMI 3D Tx PHY while operating with the slowest input reference clock supported (13.5 MHz) is 3.35 ms.

| Symbol                                     | Parameters                | Test Conditions | Min | Тур | Max | Unit |  |

|--------------------------------------------|---------------------------|-----------------|-----|-----|-----|------|--|

| LP Line Receiver DC Specifications         |                           |                 |     |     |     |      |  |

| V <sub>IL</sub>                            | Input low voltage         | _               | —   | —   | 550 | mV   |  |

| V <sub>IH</sub>                            | Input high voltage        | _               | 920 | _   | _   | mV   |  |

| V <sub>HYST</sub>                          | Input hysteresis          | _               | 25  | _   | _   | mV   |  |

| Contention Line Receiver DC Specifications |                           |                 |     |     |     |      |  |

| V <sub>ILF</sub>                           | Input low fault threshold | _               | 200 | _   | 450 | mV   |  |

### Table 68. Electrical and Timing Information (continued)

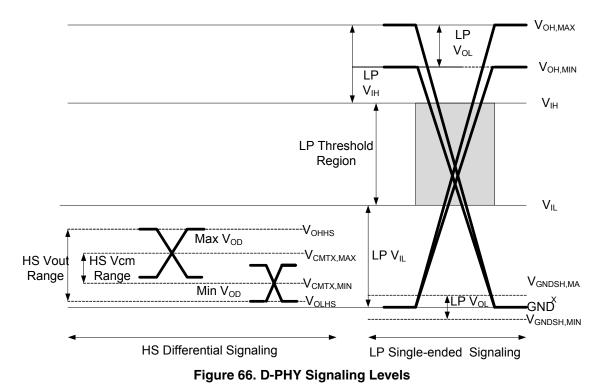

## 4.12.12.2 D-PHY Signaling Levels

The signal levels are different for differential HS mode and single-ended LP mode. Figure 66 shows both the HS and LP signal levels on the left and right sides, respectively. The HS signalling levels are below the LP low-level input threshold such that LP receiver always detects low on HS signals.

| Symbol         | Parameters                             | Test Conditions | Min | Тур | Max  | Unit |

|----------------|----------------------------------------|-----------------|-----|-----|------|------|

| L <sub>S</sub> | Equivalent wire bond series inductance | _               |     | _   | 1.5  | nH   |

| R <sub>S</sub> | Equivalent wire bond series resistance | _               | _   | _   | 0.15 | Ω    |

| RL             | Load Resistance                        | _               | 80  | 100 | 125  | Ω    |

### Table 69. Electrical and Timing Information (continued)

# 4.12.12.6 High-Speed Clock Timing

## 4.12.12.7 Forward High-Speed Data Transmission Timing

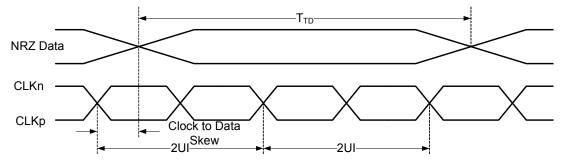

The timing relationship of the DDR Clock differential signal to the Data differential signal is shown in Figure 70:

Figure 70. Data to Clock Timing Definitions

# 4.12.12.8 Reverse High-Speed Data Transmission Timing

Figure 71. Reverse High-Speed Data Transmission Timing at Slave Side

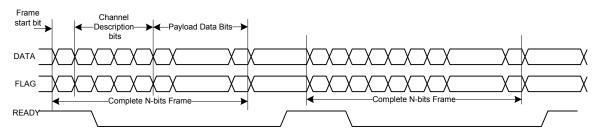

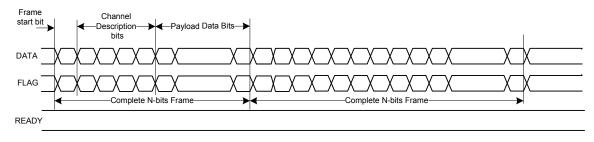

Figure 78. Frame Transmission Mode Transfer of Two Frames (Synchronized Data Flow)

# 4.12.13.7 Frame Transmission Mode (Pipelined Data Flow)

### Figure 79. Frame Transmission Mode Transfer of Two Frames (Pipelined Data Flow)

# 4.12.13.8 DATA and FLAG Signal Timing Requirement for a 15 pF Load

### Table 70. DATA and FLAG Timing

| Parameter                                         | Description                                                                                                                                                       | 1 Mbit/s | 100 Mbit/s |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------|

| t <sub>Bit, nom</sub>                             | Nominal bit time                                                                                                                                                  | 1000 ns  | 10 ns      |

| $t_{\text{Rise, min}}$ and $t_{\text{Fall, min}}$ | Minimum allowed rise and fall time                                                                                                                                | 2 ns     | 2 ns       |

| t <sub>TxToRxSkew</sub> , maxfq                   | Maximum skew between transmitter and receiver package pins                                                                                                        | 50 ns    | 0.5 ns     |

| t <sub>EageSepTx</sub> , min                      | Minimum allowed separation of signal transitions at transmitter package pins, including all timing defects, for example, jitter and skew, inside the transmitter. | 400 ns   | 4 ns       |

| t <sub>EageSepRx, min</sub>                       | Minimum separation of signal transitions, measured at the receiver package pins, including all timing defects, for example, jitter and skew, inside the receiver. | 350 ns   | 3.5 ns     |

|                                                                                                                             | . <u> </u>                                               |                       |            |            |                |  |

|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------|------------|------------|----------------|--|

| Parameter                                                                                                                   | Symbol                                                   | Test Conditions       | Min        | Max        | Unit           |  |

| Common-mode output voltage:<br>(V <sub>O+</sub> - V <sub>O-</sub> ) / 2                                                     | V <sub>OCM</sub>                                         | _                     | 1.0        | 1.5        | V              |  |

| Difference in common-mode output between<br>(high/low) steady-states:<br>I V <sub>OCM, high</sub> - V <sub>OCM, low</sub> I | ΔV <sub>OCM</sub>                                        | _                     | -50        | 50         | mV             |  |

| Variations on common-mode output during a logic state transitions                                                           | V <sub>CMV</sub>                                         | See Note <sup>2</sup> | —          | 150        | mVpp           |  |

| Short circuit current                                                                                                       | I <sub>OS</sub>                                          | See Note <sup>3</sup> | —          | 43         | mA             |  |

| Differential output impedance                                                                                               | Z <sub>0</sub> —                                         |                       | 1.6        | —          | kΩ             |  |

|                                                                                                                             | Receive                                                  | er Characteristics    |            |            |                |  |

| Differential clock input:<br>• logic low steady-state<br>• logic high steady-state<br>• hysteresis                          | V <sub>ILC</sub><br>V <sub>IHC</sub><br>V <sub>HSC</sub> | See Note <sup>4</sup> | 50<br>-25  | -50<br>25  | mV<br>mV<br>mV |  |

| Differential signal/data input:<br>• logic low steady-state<br>• logic high steady-state                                    | V <sub>ILS</sub><br>V <sub>IHS</sub>                     | _                     | <br>50     | -50<br>—   | mV<br>mV       |  |

| Signal-ended input voltage (steady-state):<br>• MLB_SIG_P, MLB_DATA_P<br>• MLB_SIG_N, MLB_DATA_N                            | V <sub>IN+</sub><br>V <sub>IN-</sub>                     | _                     | 0.5<br>0.5 | 2.0<br>2.0 | V<br>V         |  |

Table 72. MediaLB 6-Pin Interface Electrical DC Specifications (continued)

<sup>1</sup> The signal-ended output voltage of a driver is defined as V<sub>O+</sub> on MLB\_CLK\_P, MLB\_SIG\_P, and MLB\_DATA\_P. The signal-ended output voltage of a driver is defined as V<sub>O-</sub> on MLB\_CLK\_N, MLB\_SIG\_N, and MLB\_DATA\_N.

<sup>2</sup> Variations in the common-mode voltage can occur between logic states (for example, during state transitions) as a result of differences in the transition rate of V<sub>Q+</sub> and V<sub>Q-</sub>.

$^3\,$  Short circuit current is applicable when V\_{O\_{+}} and V\_{O\_{-}} are shorted together and/or shorted to ground.

$^4\,$  The logic state of the receiver is undefined when -50 mV < V\_{ID} < 50 mV.

| Parameter                                                                               | Symbol  | Timing Para | Unit                |      |

|-----------------------------------------------------------------------------------------|---------|-------------|---------------------|------|

| Falameter                                                                               | Symbol  | Min         | Max                 | Onit |

| SPDIF_IN Skew: asynchronous inputs, no specs apply                                      | —       | —           | 0.7                 | ns   |

| SPDIF_OUT output (Load = 50pf)<br>• Skew<br>• Transition rising<br>• Transition falling |         |             | 1.5<br>24.2<br>31.3 | ns   |

| SPDIF_OUT output (Load = 30pf)<br>• Skew<br>• Transition rising<br>• Transition falling |         |             | 1.5<br>13.6<br>18.0 | ns   |

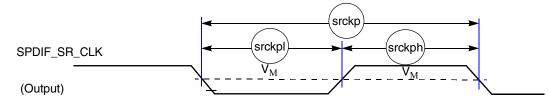

| Modulating Rx clock (SPDIF_SR_CLK) period                                               | srckp   | 40.0        | _                   | ns   |

| SPDIF_SR_CLK high period                                                                | srckph  | 16.0        |                     | ns   |

| SPDIF_SR_CLK low period                                                                 | srckpl  | 16.0        | _                   | ns   |

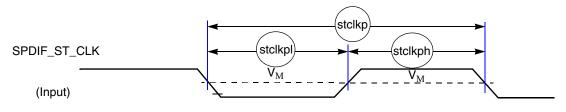

| Modulating Tx clock (SPDIF_ST_CLK) period                                               | stclkp  | 40.0        | _                   | ns   |

| SPDIF_ST_CLK high period                                                                | stclkph | 16.0        |                     | ns   |

| SPDIF_ST_CLK low period                                                                 | stclkpl | 16.0        | _                   | ns   |

| Table | 80. | SPDIF | Timing | Parameters |

|-------|-----|-------|--------|------------|

|-------|-----|-------|--------|------------|

Figure 88. SPDIF\_SR\_CLK Timing Diagram

Figure 89. SPDIF\_ST\_CLK Timing Diagram

# 4.12.21.2.3 UART IrDA Mode Timing

The following subsections give the UART transmit and receive timings in IrDA mode.

## **UART IrDA Mode Transmitter**

Figure 96 depicts the UART IrDA mode transmit timing, with 8 data bit/1 stop bit format. Table 89 lists the transmit timing characteristics.

Figure 96. UART IrDA Mode Transmit Timing Diagram

### Table 89. IrDA Mode Transmit Timing Parameters

| ID  | Parameter                      | Symbol                | Min                                                                       | Мах                                             | Unit |

|-----|--------------------------------|-----------------------|---------------------------------------------------------------------------|-------------------------------------------------|------|

| UA3 | Transmit Bit Time in IrDA mode | t <sub>TIRbit</sub>   | 1/F <sub>baud_rate</sub> <sup>1</sup> – T <sub>ref_clk</sub> <sup>2</sup> | 1/F <sub>baud_rate</sub> + T <sub>ref_clk</sub> | —    |

| UA4 | Transmit IR Pulse Duration     | t <sub>TIRpulse</sub> | $(3/16) \times (1/F_{baud\_rate}) - T_{ref\_clk}$                         | $(3/16) \times (1/F_{baud_rate}) + T_{ref_clk}$ | —    |

<sup>1</sup> F<sub>baud rate</sub>: Baud rate frequency. The maximum baud rate the UART can support is (*ipg\_perclk* frequency)/16.

<sup>2</sup> T<sub>ref clk</sub>: The period of UART reference clock *ref\_clk* (*ipg\_perclk* after RFDIV divider).

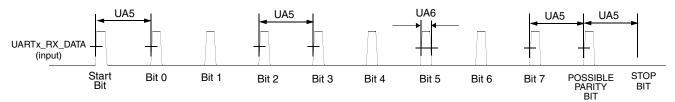

### **UART IrDA Mode Receiver**

Figure 97 depicts the UART IrDA mode receive timing, with 8 data bit/1 stop bit format. Table 90 lists the receive timing characteristics.

Figure 97. UART IrDA Mode Receive Timing Diagram

Table 90. IrDA Mode Receive Timing Parameters

| ID  | Parameter                                  | Symbol                | Min                                                                         | Мах                                                            | Unit |

|-----|--------------------------------------------|-----------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------|------|

| UA5 | Receive Bit Time <sup>1</sup> in IrDA mode | t <sub>RIRbit</sub>   | 1/F <sub>baud_rate</sub> <sup>2</sup> –<br>1/(16 × F <sub>baud_rate</sub> ) | 1/F <sub>baud_rate</sub> +<br>1/(16 × F <sub>baud_rate</sub> ) | _    |

| UA6 | Receive IR Pulse Duration                  | t <sub>RIRpulse</sub> | 1.41 μs                                                                     | $(5/16) \times (1/F_{baud_rate})$                              | —    |

The UART receiver can tolerate  $1/(16 \times F_{baud_rate})$  tolerance in each bit. But accumulation tolerance in one frame must not exceed  $3/(16 \times F_{baud_rate})$ .

<sup>2</sup> F<sub>baud rate</sub>: Baud rate frequency. The maximum baud rate the UART can support is (*ipg\_perclk* frequency)/16.

### **Boot Mode Configuration**

| Interface  | IP Instance    | Allocated Pads During Boot                                                                                                                 | Comment                        |

|------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| NAND Flash | GPMI           | NANDF_CLE, NANDF_ALE, NANDF_WP_B,<br>SD4_CMD, SD4_CLK, NANDF_RB0, SD4_DAT0,<br>NANDF_CS0, NANDF_CS1, NANDF_CS2,<br>NANDF_CS3, NANDF_D[7:0] | 8 bit<br>Only CS0 is supported |

| SD/MMC     | USDHC-1        | SD1_CLK, SD1_CMD,SD1_DAT0, SD1_DAT1,<br>SD1_DAT2, SD1_DAT3, NANDF_D0, NANDF_D1,<br>NANDF_D2, NANDF_D3, KEY_COL1                            | 1, 4, or 8 bit                 |

| SD/MMC     | USDHC-2        | SD2_CLK, SD2_CMD, SD2_DAT0, SD2_DAT1,<br>SD2_DAT2, SD2_DAT3, NANDF_D4, NANDF_D5,<br>NANDF_D6, NANDF_D7, KEY_ROW1                           | 1, 4, or 8 bit                 |

| SD/MMC     | USDHC-3        | SD3_CLK, SD3_CMD, SD3_DAT0, SD3_DAT1,<br>SD3_DAT2, SD3_DAT3, SD3_DAT4, SD3_DAT5,<br>SD3_DAT6, SD3_DAT7, GPI0_18                            | 1, 4, or 8 bit                 |

| SD/MMC     | USDHC-4        | SD4_CLK, SD4_CMD, SD4_DAT0, SD4_DAT1,<br>SD4_DAT2, SD4_DAT3, SD4_DAT4, SD4_DAT5,<br>SD4_DAT6, SD4_DAT7, NANDF_CS1                          | 1, 4, or 8 bit                 |

| I2C        | I2C-1          | EIM_D28, EIM_D21                                                                                                                           | —                              |

| I2C        | I2C-2          | EIM_D16, EIM_EB2                                                                                                                           | —                              |

| I2C        | I2C-3          | EIM_D18, EIM_D17                                                                                                                           | —                              |

| SATA       | SATA_PHY       | SATA_TXM, SATA_TXP, SATA_RXP, SATA_RXM,<br>SATA_REXT                                                                                       | _                              |

| USB        | USB-OTG<br>PHY | USB_OTG_DP<br>USB_OTG_DN<br>USB_OTG_VBUS                                                                                                   | _                              |

### Package Information and Contact Assignments

|           |      |               |           | Out of Reset Condition <sup>1</sup> |                                   |              |                    |  |

|-----------|------|---------------|-----------|-------------------------------------|-----------------------------------|--------------|--------------------|--|

| Ball Name | Ball | Power Group   | Ball Type | Default<br>Mode<br>(Reset<br>Mode)  | Default Function<br>(Signal Name) | Input/Output | Value <sup>2</sup> |  |

| DRAM_CS1  | AD17 | NVCC_DRAM     | DDR       | ALT0                                | DRAM_CS1_B                        | Output       | 0                  |  |

| DRAM_D0   | AD2  | NVCC_DRAM     | DDR       | ALT0                                | DRAM_DATA00                       | Input        | PU (100K)          |  |

| DRAM_D1   | AE2  | NVCC_DRAM     | DDR       | ALT0                                | DRAM_DATA01                       | Input        | PU (100K           |  |

| DRAM_D10  | AA6  | NVCC_DRAM     | DDR       | ALT0                                | DRAM_DATA10                       | Input        | PU (100K)          |  |

| DRAM_D11  | AE7  | NVCC_DRAM     | DDR       | ALT0                                | DRAM_DATA11                       | Input        | PU (100K           |  |

| DRAM_D12  | AB5  | NVCC_DRAM     | DDR       | ALT0                                | DRAM_DATA12                       | Input        | PU (100K           |  |

| DRAM_D13  | AC5  | NVCC_DRAM     | DDR       | ALT0                                | DRAM_DATA13                       | Input        | PU (100K           |  |

| DRAM_D14  | AB6  | NVCC_DRAM     | DDR       | ALT0                                | DRAM_DATA14                       | Input        | PU (100K           |  |

| DRAM_D15  | AC7  | NVCC_DRAM     | DDR       | ALT0                                | DRAM_DATA15                       | Input        | PU (100K           |  |

| DRAM_D16  | AB7  | NVCC_DRAM     | DDR       | ALT0                                | DRAM_DATA16                       | Input        | PU (100K           |  |

| DRAM_D17  | AA8  | NVCC_DRAM     | DDR       | ALT0                                | DRAM_DATA17                       | Input        | PU (100K           |  |

| DRAM_D18  | AB9  | NVCC_DRAM     | DDR       | ALT0                                | DRAM_DATA18                       | Input        | PU (100K           |  |

| DRAM_D19  | Y9   | NVCC_DRAM     | DDR       | ALT0                                | DRAM_DATA19                       | Input        | PU (100K           |  |

| DRAM_D2   | AC4  | NVCC_DRAM     | DDR       | ALT0                                | DRAM_DATA02                       | Input        | PU (100K           |  |

| DRAM_D20  | Y7   | NVCC_DRAM     | DDR       | ALT0                                | DRAM_DATA20                       | Input        | PU (100K           |  |

| DRAM_D21  | Y8   | NVCC_DRAM     | DDR       | ALT0                                | DRAM_DATA21                       | Input        | PU (100K           |  |

| DRAM_D22  | AC8  | NVCC_DRAM     | DDR       | ALT0                                | DRAM_DATA22                       | Input        | PU (100K           |  |

| DRAM_D23  | AA9  | NVCC_DRAM     | DDR       | ALT0                                | DRAM_DATA23                       | Input        | PU (100K           |  |