# E·XFL

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                            |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Active                                                                                                              |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 4 Core, 32-Bit                                                                                                      |

| Speed                              | 1.0GHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON <sup>™</sup> SIMD                                                                                  |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | SATA 3Gbps (1)                                                                                                      |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | -20°C ~ 105°C (TJ)                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-LFBGA, FCBGA                                                                                                    |

| Supplier Device Package            | 624-FCPBGA (21x21)                                                                                                  |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6q5eym10ce                                             |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Introduction

- Two Master AXI (64-bit) bus interfaces output of L2 cache

- Frequency of the core (including Neon and L1 cache) as per Table 6.

- NEON MPE coprocessor

- SIMD Media Processing Architecture

- NEON register file with 32x64-bit general-purpose registers

- NEON Integer execute pipeline (ALU, Shift, MAC)

- NEON dual, single-precision floating point execute pipeline (FADD, FMUL)

- NEON load/store and permute pipeline

The SoC-level memory system consists of the following additional components:

- Boot ROM, including HAB (96 KB)

- Internal multimedia / shared, fast access RAM (OCRAM, 256 KB)

- Secure/non-secure RAM (16 KB)

- External memory interfaces:

- 16-bit, 32-bit, and 64-bit DDR3-1066, DDR3L-1066, and 1/2 LPDDR2-800 channels, supporting DDR interleaving mode, for dual x32 LPDDR2

- 8-bit NAND-Flash, including support for Raw MLC/SLC, 2 KB, 4 KB, and 8 KB page size, BA-NAND, PBA-NAND, LBA-NAND, OneNAND<sup>TM</sup> and others. BCH ECC up to 40 bit.

- 16/32-bit NOR Flash. All EIMv2 pins are muxed on other interfaces.

- 16/32-bit PSRAM, Cellular RAM

Each i.MX 6Dual/6Quad processor enables the following interfaces to external devices (some of them are muxed and not available simultaneously):

- Hard Disk Drives—SATA II, 3.0 Gbps

- Displays—Total five interfaces available. Total raw pixel rate of all interfaces is up to 450 Mpixels/sec, 24 bpp. Up to four interfaces may be active in parallel.

- One Parallel 24-bit display port, up to 225 Mpixels/sec (for example, WUXGA at 60 Hz or dual HD1080 and WXGA at 60 Hz)

- LVDS serial ports—One port up to 170 Mpixels/sec (for example, WUXGA at 60 Hz) or two ports up to 85 MP/sec each

- HDMI 1.4 port

- MIPI/DSI, two lanes at 1 Gbps

- Camera sensors:

- Parallel Camera port (up to 20 bit and up to 240 MHz peak)

- MIPI CSI-2 serial camera port, supporting up to 1000 Mbps/lane in 1/2/3-lane mode and up to 800 Mbps/lane in 4-lane mode. The CSI-2 Receiver core can manage one clock lane and up to four data lanes. Each i.MX 6Dual/6Quad processor has four lanes.

- Expansion cards:

- Four MMC/SD/SDIO card ports all supporting:

- 1-bit or 4-bit transfer mode specifications for SD and SDIO cards up to UHS-I SDR-104 mode (104 MB/s max)

- 1-bit, 4-bit, or 8-bit transfer mode specifications for MMC cards up to 52 MHz in both SDR and DDR modes (104 MB/s max)

- USB:

- One High Speed (HS) USB 2.0 OTG (Up to 480 Mbps), with integrated HS USB PHY

- Three USB 2.0 (480 Mbps) hosts:

- One HS host with integrated High Speed PHY

- Two HS hosts with integrated High Speed Inter-Chip (HS-IC) USB PHY

- Expansion PCI Express port (PCIe) v2.0 one lane

- PCI Express (Gen 2.0) dual mode complex, supporting Root complex operations and Endpoint operations. Uses x1 PHY configuration.

- Miscellaneous IPs and interfaces:

- SSI block capable of supporting audio sample frequencies up to 192 kHz stereo inputs and outputs with I<sup>2</sup>S mode

- ESAI is capable of supporting audio sample frequencies up to 260 kHz in I2S mode with 7.1 multi channel outputs

- Five UARTs, up to 5.0 Mbps each:

- Providing RS232 interface

- Supporting 9-bit RS485 multidrop mode

- One of the five UARTs (UART1) supports 8-wire while the other four support 4-wire. This is due to the SoC IOMUX limitation, because all UART IPs are identical.

- Five eCSPI (Enhanced CSPI)

- Three I2C, supporting 400 kbps

- Gigabit Ethernet Controller (IEEE1588 compliant), 10/100/1000<sup>1</sup> Mbps

- Four Pulse Width Modulators (PWM)

- System JTAG Controller (SJC)

- GPIO with interrupt capabilities

- 8x8 Key Pad Port (KPP)

- Sony Philips Digital Interconnect Format (SPDIF), Rx and Tx

- Two Controller Area Network (FlexCAN), 1 Mbps each

- Two Watchdog timers (WDOG)

- Audio MUX (AUDMUX)

- MLB (MediaLB) provides interface to MOST Networks (150 Mbps) with the option of DTCP cipher accelerator

1. The theoretical maximum performance of 1 Gbps ENET is limited to 470 Mbps (total for Tx and Rx) due to internal bus throughput limitations. The actual measured performance in optimized environment is up to 400 Mbps. For details, see the ERR004512 erratum in the i.MX 6Dual/6Quad errata document (IMX6DQCE).

# 3 Modules List

The i.MX 6Dual/6Quad processors contain a variety of digital and analog modules. Table 2 describes these modules in alphabetical order.

| Block<br>Mnemonic   | Block Name                                                                          | Subsystem                               | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------|-------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 512 x 8 Fuse<br>Box | Electrical Fuse Array                                                               | Security                                | Electrical Fuse Array. Enables to setup Boot Modes, Security Levels,<br>Security Keys, and many other system parameters.<br>The i.MX 6Dual/6Quad processors consist of 512x8-bit fuse box<br>accessible through OCOTP_CTRL interface.                                                                                                                                                                                                                                                                                                                                                |

| APBH-DMA            | NAND Flash and<br>BCH ECC DMA<br>Controller                                         | System<br>Control<br>Peripherals        | DMA controller used for GPMI2 operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ARM                 | ARM Platform                                                                        | ARM                                     | The ARM Cortex-A9 platform consists of 4x (four) Cortex-A9 cores version r2p10 and associated sub-blocks, including Level 2 Cache Controller, SCU (Snoop Control Unit), GIC (General Interrupt Controller), private timers, Watchdog, and CoreSight debug modules.                                                                                                                                                                                                                                                                                                                   |

| ASRC                | Asynchronous<br>Sample Rate<br>Converter                                            | Multimedia<br>Peripherals               | The Asynchronous Sample Rate Converter (ASRC) converts the sampling rate of a signal associated to an input clock into a signal associated to a different output clock. The ASRC supports concurrent sample rate conversion of up to 10 channels of about -120dB THD+N. The sample rate conversion of each channel is associated to a pair of incoming and outgoing sampling rates. The ASRC supports up to three sampling rate pairs.                                                                                                                                               |

| AUDMUX              | Digital Audio Mux                                                                   | Multimedia<br>Peripherals               | The AUDMUX is a programmable interconnect for voice, audio, and<br>synchronous data routing between host serial interfaces (for example,<br>SSI1, SSI2, and SSI3) and peripheral serial interfaces (audio and voice<br>codecs). The AUDMUX has seven ports with identical functionality and<br>programming models. A desired connectivity is achieved by configuring<br>two or more AUDMUX ports.                                                                                                                                                                                    |

| BCH40               | Binary-BCH ECC<br>Processor                                                         | System<br>Control<br>Peripherals        | The BCH40 module provides up to 40-bit ECC error correction for NAND Flash controller (GPMI).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CAAM                | Cryptographic<br>Accelerator and<br>Assurance Module                                | Security                                | CAAM is a cryptographic accelerator and assurance module. CAAM<br>implements several encryption and hashing functions, a run-time integrity<br>checker, and a Pseudo Random Number Generator (PRNG). The pseudo<br>random number generator is certified by Cryptographic Algorithm<br>Validation Program (CAVP) of National Institute of Standards and<br>Technology (NIST). Its DRBG validation number is 94 and its SHS<br>validation number is 1455.<br>CAAM also implements a Secure Memory mechanism. In i.MX<br>6Dual/6Quad processors, the security memory provided is 16 KB. |

| CCM<br>GPC<br>SRC   | Clock Control<br>Module, General<br>Power Controller,<br>System Reset<br>Controller | Clocks,<br>Resets, and<br>Power Control | These modules are responsible for clock and reset distribution in the system, and also for the system power management.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Table 2. i.M | IX 6Dual/6Quad | I Modules List |

|--------------|----------------|----------------|

|--------------|----------------|----------------|

| Table 2. i.MX 6Dual/6Quad Modules List (d | continued) |

|-------------------------------------------|------------|

|-------------------------------------------|------------|

| Block<br>Mnemonic                | Block Name                    | Subsystem                                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------|-------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LDB                              | LVDS Display Bridge           | Connectivity<br>Peripherals                 | <ul> <li>LVDS Display Bridge is used to connect the IPU (Image Processing Unit) to External LVDS Display Interface. LDB supports two channels; each channel has following signals:</li> <li>One clock pair</li> <li>Four data pairs</li> <li>Each signal pair contains LVDS special differential pad (PadP, PadM).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MLB150                           | MediaLB                       | Connectivity /<br>Multimedia<br>Peripherals | The MLB interface module provides a link to a MOST <sup>®</sup> data network, using the standardized MediaLB protocol (up to 150 Mbps). The module is backward compatible to MLB-50.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MMDC                             | Multi-Mode DDR<br>Controller  | Connectivity<br>Peripherals                 | <ul> <li>DDR Controller has the following features:</li> <li>Supports 16/32/64-bit DDR3 / DDR3L or LPDDR2</li> <li>Supports both dual x32 for LPDDR2 and x64 DDR3 / LPDDR2 configurations (including 2x32 interleaved mode)</li> <li>Supports up to 4 GByte DDR memory space</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OCOTP_CTRL                       | OTP Controller                | Security                                    | The On-Chip OTP controller (OCOTP_CTRL) provides an interface for reading, programming, and/or overriding identification and control information stored in on-chip fuse elements. The module supports electrically-programmable poly fuses (eFUSEs). The OCOTP_CTRL also provides a set of volatile software-accessible signals that can be used for software control of hardware elements, not requiring non-volatility. The OCOTP_CTRL provides the primary user-visible mechanism for interfacing with on-chip fuse elements. Among the uses for the fuses are unique chip identifiers, mask revision numbers, cryptographic keys, JTAG secure mode, boot characteristics, and various control signals, requiring permanent non-volatility. |

| OCRAM                            | On-Chip Memory<br>Controller  | Data Path                                   | The On-Chip Memory controller (OCRAM) module is designed as an interface between system's AXI bus and internal (on-chip) SRAM memory module.<br>In i.MX 6Dual/6Quad processors, the OCRAM is used for controlling the 256 KB multimedia RAM through a 64-bit AXI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| OSC 32 kHz                       | OSC 32 kHz                    | Clocking                                    | Generates 32.768 kHz clock from an external crystal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PCle                             | PCI Express 2.0               | Connectivity<br>Peripherals                 | The PCIe IP provides PCI Express Gen 2.0 functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PMU                              | Power-Management<br>Functions | Data Path                                   | Integrated power management unit. Used to provide power to various SoC domains.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PWM-1<br>PWM-2<br>PWM-3<br>PWM-4 | Pulse Width<br>Modulation     | Connectivity<br>Peripherals                 | The pulse-width modulator (PWM) has a 16-bit counter and is optimized to generate sound from stored sample audio images and it can also generate tones. It uses 16-bit resolution and a 4x16 data FIFO to generate sound.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RAM<br>16 KB                     | Secure/non-secure<br>RAM      | Secured<br>Internal<br>Memory               | Secure/non-secure Internal RAM, interfaced through the CAAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RAM<br>256 KB                    | Internal RAM                  | Internal<br>Memory                          | Internal RAM, which is accessed through OCRAM memory controllers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Table 2. i.MX 6Dual/6Quad Modules List (continued) |

|----------------------------------------------------|

|----------------------------------------------------|

| Block<br>Mnemonic                              | Block Name                                   | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------|----------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSI-1<br>SSI-2<br>SSI-3                        | I2S/SSI/AC97<br>Interface                    | Connectivity<br>Peripherals      | The SSI is a full-duplex synchronous interface, which is used on the processor to provide connectivity with off-chip audio peripherals. The SSI supports a wide variety of protocols (SSI normal, SSI network, I2S, and AC-97), bit depths (up to 24 bits per word), and clock / frame sync options. The SSI has two pairs of 8x24 FIFOs and hardware support for an external DMA controller to minimize its impact on system performance. The second pair of FIFOs provides hardware interleaving of a second audio stream that reduces CPU overhead in use cases where two time slots are being used simultaneously. |

| TEMPMON                                        | Temperature Monitor                          | System<br>Control<br>Peripherals | The temperature monitor/sensor IP module for detecting high temperature conditions. The temperature read out does not reflect case or ambient temperature. It reflects the temperature in proximity of the sensor location on the die. Temperature distribution may not be uniformly distributed; therefore, the read out value may not be the reflection of the temperature value for the entire die.                                                                                                                                                                                                                 |

| TZASC                                          | Trust-Zone Address<br>Space Controller       | Security                         | The TZASC (TZC-380 by ARM) provides security address region control functions required for intended application. It is used on the path to the DRAM controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| UART-1<br>UART-2<br>UART-3<br>UART-4<br>UART-5 | UART Interface                               | Connectivity<br>Peripherals      | <ul> <li>Each of the UARTv2 modules support the following serial data transmit/receive protocols and configurations:</li> <li>7- or 8-bit data words, 1 or 2 stop bits, programmable parity (even, odd or none)</li> <li>Programmable baud rates up to 5 MHz</li> <li>32-byte FIFO on Tx and 32 half-word FIFO on Rx supporting auto-baud</li> <li>IrDA 1.0 support (up to SIR speed of 115200 bps)</li> <li>Option to operate as 8-pins full UART, DCE, or DTE</li> </ul>                                                                                                                                             |

| USBOH3A                                        | USB 2.0 High Speed<br>OTG and 3x HS<br>Hosts | Connectivity<br>Peripherals      | <ul> <li>USBOH3 contains:</li> <li>One high-speed OTG module with integrated HS USB PHY</li> <li>One high-speed Host module with integrated HS USB PHY</li> <li>Two identical high-speed Host modules connected to HSIC USB ports.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                          |

| Table 8. Maximum Supply Currents ( | (continued) |

|------------------------------------|-------------|

|------------------------------------|-------------|

| Power Supply | Conditions              | Maximum C                                                                                                                                          | Unit     |      |  |

|--------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|--|

|              | Power Supply Conditions |                                                                                                                                                    | CoreMark | Onit |  |

| NVCC_LVDS2P5 | _                       | NVCC_LVDS2P5 is connected to<br>VDD_HIGH_CAP at the board<br>level. VDD_HIGH_CAP is capable<br>of handing the current required by<br>NVCC_LVDS2P5. |          |      |  |

| MISC         |                         |                                                                                                                                                    |          |      |  |

| DRAM_VREF    | _                       | 1                                                                                                                                                  |          | mA   |  |

<sup>1</sup> The actual maximum current drawn from VDD\_HIGH\_IN will be as shown plus any additional current drawn from the VDD\_HIGH\_CAP outputs, depending upon actual application configuration (for example, NVCC\_LVDS\_2P5, NVCC\_MIPI, or HDMI, PCIe, and SATA VPH supplies).

- <sup>2</sup> Under normal operating conditions, the maximum current on VDD\_SNVS\_IN is shown Table 8. The maximum VDD\_SNVS\_IN current may be higher depending on specific operating configurations, such as BOOT\_MODE[1:0] not equal to 00, or use of the Tamper feature. During initial power on, VDD\_SNVS\_IN can draw up to 1 mA if the supply is capable of sourcing that current. If less than 1 mA is available, the VDD\_SNVS\_CAP charge time will increase.

- <sup>3</sup> This is the maximum current per active USB physical interface.

- <sup>4</sup> The DRAM power consumption is dependent on several factors such as external signal termination. DRAM power calculators are typically available from memory vendors which take into account factors such as signal termination. See the *i.MX 6Dual/6Quad Power Consumption Measurement Application Note* (AN4509) for examples of DRAM power consumption during specific use case scenarios.

- <sup>5</sup> General equation for estimated, maximum power consumption of an IO power supply: Imax = N x C x V x (0.5 x F)

- Where:

N-Number of IO pins supplied by the power line

C-Equivalent external capacitive load

V—IO voltage

(0.5 xF)—Data change rate. Up to 0.5 of the clock rate (F)

In this equation, Imax is in Amps, C in Farads, V in Volts, and F in Hertz.

# 4.1.6 Low Power Mode Supply Currents

Table 9 shows the current core consumption (not including I/O) of the i.MX 6Dual/6Quad processors in selected low power modes.

| Mode | Test Conditions                                                                                                                                                                                   | Supply              | Typical <sup>1</sup> | Unit |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------|------|

| WAIT | <ul> <li>ARM, SoC, and PU LDOs are set to 1.225 V</li> <li>HIGH LDO set to 2.5 V</li> <li>Clocks are gated</li> <li>DDR is in self refresh</li> <li>PLLs are active in bypass (24 MHz)</li> </ul> | VDD_ARM_IN (1.4 V)  | 6                    | mA   |

|      |                                                                                                                                                                                                   | VDD_SOC_IN (1.4 V)  | 23                   | mA   |

|      |                                                                                                                                                                                                   | VDD_HIGH_IN (3.0 V) | 3.7                  | mA   |

|      | Supply voltages remain ON                                                                                                                                                                         | Total               | 52                   | mW   |

| Table 9 | . Stop Mode | Current and | Power | Consumption |

|---------|-------------|-------------|-------|-------------|

|---------|-------------|-------------|-------|-------------|

# 4.1.7 USB PHY Current Consumption

## 4.1.7.1 Power Down Mode

In power down mode, everything is powered down, including the VBUS valid detectors, typical condition. Table 10 shows the USB interface current consumption in power down mode.

#### Table 10. USB PHY Current Consumption in Power Down Mode

|         | VDD_USB_CAP (3.0 V) | VDD_HIGH_CAP (2.5 V) | NVCC_PLL_OUT (1.1 V) |

|---------|---------------------|----------------------|----------------------|

| Current | 5.1 μA              | 1.7 μA               | <0.5 μA              |

### NOTE

The currents on the VDD\_HIGH\_CAP and VDD\_USB\_CAP were identified to be the voltage divider circuits in the USB-specific level shifters.

# 4.1.8 SATA Typical Power Consumption

Table 11 provides SATA PHY currents for certain Tx operating modes.

### NOTE

Tx power consumption values are provided for a single transceiver. If T = single transceiver power and C = Clock module power, the total power required for N lanes = N x T + C.

| Table 11. | SATA  | PHY | Current | Drain |

|-----------|-------|-----|---------|-------|

|           | ••••• |     |         |       |

| Mode                              | Test Conditions    | Supply   | Typical Current | Unit |

|-----------------------------------|--------------------|----------|-----------------|------|

| P0: Full-power state <sup>1</sup> | Single Transceiver | SATA_VP  | 11              | mA   |

|                                   |                    | SATA_VPH | 13              |      |

|                                   | Clock Module       | SATA_VP  | 6.9             |      |

|                                   |                    | SATA_VPH | 6.2             |      |

| P0: Mobile <sup>2</sup>           | Single Transceiver | SATA_VP  | 11              | mA   |

|                                   |                    | SATA_VPH | 11              |      |

|                                   | Clock Module       | SATA_VP  | 6.9             |      |

|                                   |                    | SATA_VPH | 6.2             |      |

| P0s: Transmitter idle             | Single Transceiver | SATA_VP  | 9.4             | mA   |

|                                   |                    | SATA_VPH | 2.9             |      |

|                                   | Clock Module       | SATA_VP  | 6.9             |      |

|                                   |                    | SATA_VPH | 6.2             | 1    |

# 4.2 **Power Supplies Requirements and Restrictions**

The system design must comply with power-up sequence, power-down sequence, and steady state guidelines as described in this section to ensure the reliable operation of the device. Any deviation from these sequences may result in the following situations:

- Excessive current during power-up phase

- Prevention of the device from booting

- Irreversible damage to the processor

# 4.2.1 Power-Up Sequence

For power-up sequence, the restrictions are as follows:

- VDD\_SNVS\_IN supply must be turned ON before any other power supply. It may be connected (shorted) with VDD\_HIGH\_IN supply.

- If a coin cell is used to power VDD\_SNVS\_IN, then ensure that it is connected before any other supply is switched on.

- The SRC\_POR\_B signal controls the processor POR and must be immediately asserted at power-up and remain asserted until the VDD\_ARM\_CAP, VDD\_SOC\_CAP, and VDD\_PU\_CAP supplies are stable. VDD\_ARM\_IN and VDD\_SOC\_IN may be applied in either order with no restrictions.

Ensure that there is no back voltage (leakage) from any supply on the board towards the 3.3 V supply (for example, from the external components that use both the 1.8 V and 3.3 V supplies).

### NOTE

USB\_OTG\_VBUS and USB\_H1\_VBUS are not part of the power supply sequence and can be powered at any time.

# 4.2.2 Power-Down Sequence

There are no special restrictions for i.MX 6Dual/6Quad SoC.

# 4.2.3 Power Supplies Usage

- All I/O pins must not be externally driven while the I/O power supply for the pin (NVCC\_xxx) is OFF. This can cause internal latch-up and malfunctions due to reverse current flows. For information about I/O power supply of each pin, see the "Power Group" column of Table 96, "21 x 21 mm Functional Contact Assignments".

- When the SATA interface is not used, the SATA\_VP and SATA\_VPH supplies should be grounded. The input and output supplies for rest of the ports (SATA\_REXT, SATA\_PHY\_RX\_N, SATA\_PHY\_RX\_P, and SATA\_PHY\_TX\_N) can remain unconnected. It is recommended not to turn OFF the SATA\_VPH supply while the SATA\_VP supply is ON, as it may lead to excessive power consumption. If boundary scan test is used, SATA\_VP and SATA\_VPH must remain powered.

# CAUTION

The internal RTC oscillator does not provide an accurate frequency and is affected by process, voltage, and temperature variations. NXP strongly recommends using an external crystal as the RTC\_XTALI reference. If the internal oscillator is used instead, careful consideration must be given to the timing implications on all of the SoC modules dependent on this clock.

The OSC32k runs from VDD\_SNVS\_CAP, which comes from the VDD\_HIGH\_IN/VDD\_SNVS\_IN power mux.

| Parameter           | Min | Тур        | Max    | Comments                                                                                                                                                                                                                                                                                                                                                       |

|---------------------|-----|------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fosc                | _   | 32.768 kHz |        | This frequency is nominal and determined mainly by the crystal selected. 32.0 K would work as well.                                                                                                                                                                                                                                                            |

| Current consumption | _   | 4 μΑ       | _      | The typical value shown is only for the oscillator, driven by an external crystal. If the internal ring oscillator is used instead of an external crystal, then approximately 25 $\mu$ A must be added to this value.                                                                                                                                          |

| Bias resistor       | _   | 14 MΩ      | _      | This the integrated bias resistor that sets the amplifier into a high gain state. Any leakage through the ESD network, external board leakage, or even a scope probe that is significant relative to this value will debias the amplifier. The debiasing will result in low gain, and will impact the circuit's ability to start up and maintain oscillations. |

|                     |     |            |        | Target Crystal Properties                                                                                                                                                                                                                                                                                                                                      |

| Cload               | _   | 10 pF      |        | Usually crystals can be purchased tuned for different Cloads. This Cload value is typically 1/2 of the capacitances realized on the PCB on either side of the quartz. A higher Cload will decrease oscillation margin, but increases current oscillating through the crystal.                                                                                  |

| ESR                 | _   | 50 kΩ      | 100 kΩ | Equivalent series resistance of the crystal. Choosing a crystal with a higher value will decrease the oscillating margin.                                                                                                                                                                                                                                      |

#### Table 20. OSC32K Main Characteristics

# 4.6 I/O DC Parameters

This section includes the DC parameters of the following I/O types:

- General Purpose I/O (GPIO)

- Double Data Rate I/O (DDR) for LPDDR2 and DDR3/DDR3L modes

- LVDS I/O

- MLB I/O

### NOTE

The term 'OVDD' in this section refers to the associated supply rail of an input or output.

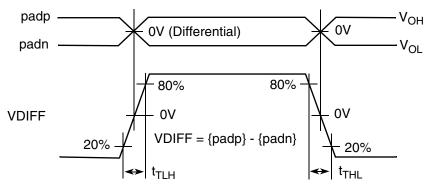

Figure 7. Differential MLB Driver Transition Time Waveform

A 4-stage pipeline is used in the MLB 6-pin implementation to facilitate design, maximize throughput, and allow for reasonable PCB trace lengths. Each cycle is one ipp\_clk\_in\* (internal clock from MLB PLL) clock period. Cycles 2, 3, and 4 are MLB PHY related. Cycle 2 includes clock-to-output delay of Signal/Data sampling flip-flop and Transmitter, Cycle 3 includes clock-to-output delay of Signal/Data clocked receiver, Cycle 4 includes clock-to-output delay of Signal/Data sampling flip-flop.

MLB 6-pin pipeline diagram is shown in Figure 8.

Figure 8. MLB 6-Pin Pipeline Diagram

Table 33 shows the AC parameters for MLB I/O.

| Parameter                                | Symbol           | Test Condition      | Min | Тур | Max   | Unit |

|------------------------------------------|------------------|---------------------|-----|-----|-------|------|

| Differential pulse skew <sup>1</sup>     | t <sub>SKD</sub> | Rload = 50 $\Omega$ | _   | _   | 0.1   |      |

| Transition Low to High Time <sup>2</sup> | t <sub>TLH</sub> | between padP        | _   | —   | 1     | ns   |

| Transition High to Low Time              | t <sub>THL</sub> | and padN            | _   | —   | 1     |      |

| MLB external clock Operating Frequency   | fclk_ext         | —                   | _   | —   | 102.4 | MHz  |

| MLB PLL clock Operating Frequency        | fclk_pll         | —                   | _   | —   | 307.2 | MHz  |

<sup>1</sup> t<sub>SKD</sub> = I t<sub>PHLD</sub> - t<sub>PLHD</sub> I, is the magnitude difference in differential propagation delay time between the positive going edge and the negative going edge of the same channel.

<sup>2</sup> Measurement levels are 20-80% from output voltage.

# 4.8 Output Buffer Impedance Parameters

This section defines the I/O impedance parameters of the i.MX 6Dual/6Quad processors for the following I/O types:

- General Purpose I/O (GPIO)

- Double Data Rate I/O (DDR) for LPDDR2, and DDR3 modes

- LVDS I/O

- MLB I/O

### NOTE

GPIO and DDR I/O output driver impedance is measured with "long" transmission line of impedance Ztl attached to I/O pad and incident wave launched into transmission line. Rpu/Rpd and Ztl form a voltage divider that defines specific voltage of incident wave relative to OVDD. Output driver impedance is calculated from this voltage divider (see Figure 9).

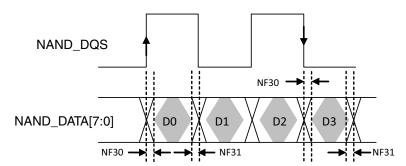

Figure 32. NAND\_DQS/NAND\_DQ Read Valid Window

| ID   | Parameter                                      | Symbol | Timin<br>T = GPMI Clo                     | Unit                     |    |

|------|------------------------------------------------|--------|-------------------------------------------|--------------------------|----|

|      |                                                |        | Min                                       | Max                      |    |

| NF18 | NAND_CEx_B access time                         | tCE    | $CE_DELAY \times T$ -                     | 0.79 [see <sup>2</sup> ] | ns |

| NF19 | NAND_CEx_B hold time                           | tCH    | 0.5 × tCK - 0.6                           | 63 [see <sup>2</sup> ]   | ns |

| NF20 | Command/address NAND_DATAxx setup time         | tCAS   | 0.5 	imes tCK ·                           | 0.05                     | ns |

| NF21 | Command/address NAND_DATAxx hold time          | tCAH   | 0.5 × tCK - 1.23                          |                          | ns |

| NF22 | clock period                                   | tCK    | —                                         |                          | ns |

| NF23 | preamble delay                                 | tPRE   | PRE_DELAY × T - 0.29 [see <sup>2</sup> ]  |                          | ns |

| NF24 | postamble delay                                | tPOST  | POST_DELAY × T - 0.78 [see <sup>2</sup> ] |                          | ns |

| NF25 | NAND_CLE and NAND_ALE setup time               | tCALS  | 0.5 	imes tCK ·                           | 0.86                     | ns |

| NF26 | NAND_CLE and NAND_ALE hold time                | tCALH  | 0.5 	imes tCK ·                           | 0.37                     | ns |

| NF27 | NAND_CLK to first NAND_DQS latching transition | tDQSS  | T - 0.41 [s                               | ee <sup>2</sup> ]        | ns |

| NF28 | Data write setup                               | tDS    | 0.25 × tCK - 0.35                         |                          | —  |

| NF29 | Data write hold                                | tDH    | 0.25 × tCK - 0.85                         |                          | —  |

| NF30 | NAND_DQS/NAND_DQ read setup skew               | tDQSQ  | — 2.06                                    |                          | —  |

| NF31 | NAND_DQS/NAND_DQ read hold skew                | tQHS   |                                           | 1.95                     | —  |

Table 45. Source Synchronous Mode Timing Parameters<sup>1</sup>

<sup>1</sup> The GPMI source synchronous mode output timing can be controlled by the module's internal registers GPMI\_TIMING2\_CE\_DELAY, GPMI\_TIMING\_PREAMBLE\_DELAY, GPMI\_TIMING2\_POST\_DELAY. This AC timing depends on these registers settings. In the table, CE\_DELAY/PRE\_DELAY/POST\_DELAY represents each of these settings.

<sup>2</sup> T = tCK (GPMI clock period) -0.075ns (half of maximum p-p jitter).

Figure 32 shows the timing diagram of NAND\_DQS/NAND\_DATAxx read valid window. For Source Synchronous mode, the typical value of tDQSQ is 0.85 ns (max) and 1 ns (max) for tQHS at 200MB/s. GPMI will sample NAND\_DATA[7:0] at both rising and falling edge of a delayed NAND\_DQS signal, which can be provided by an internal DPLL. The delay value can be controlled by GPMI register GPMI\_READ\_DDR\_DLL\_CTRL.SLV\_DLY\_TARGET (see the GPMI chapter of the i.MX 6Dual/6Quad reference manual (IMX6DQRM)). Generally, the typical delay value of this register is equal to 0x7 which means 1/4 clock cycle delay expected. However, if the board delay is large enough and cannot be ignored, the delay value should be made larger to compensate the board delay.

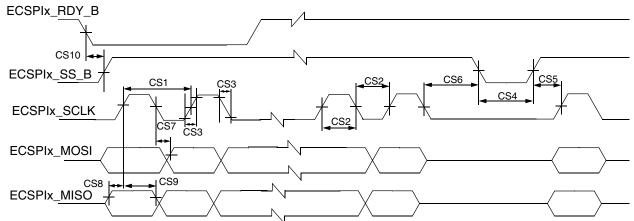

# 4.12.2.1 ECSPI Master Mode Timing

Figure 35 depicts the timing of ECSPI in master mode and Table 47 lists the ECSPI master mode timing characteristics.

Note: ECSPIx\_MOSI is always driven (not tri-stated) between actual data transmissions. This limits the ECSPI to be connected between a single master and a single slave.

#### Figure 35. ECSPI Master Mode Timing Diagram

| ID   | Parameter                                                 | Symbol                 | Min                         | Max | Unit |

|------|-----------------------------------------------------------|------------------------|-----------------------------|-----|------|

| CS1  | ECSPIx_SCLK Cycle Time-Read                               | t <sub>clk</sub>       |                             | —   | ns   |

|      | • Slow group <sup>1</sup>                                 |                        | 55                          |     |      |

|      | • Fast group <sup>2</sup>                                 |                        | 40                          |     |      |

|      | ECSPIx_SCLK Cycle Time–Write                              |                        | 15                          |     |      |

| CS2  | ECSPIx_SCLK High or Low Time-Read                         | t <sub>SW</sub>        |                             | —   | ns   |

|      | • Slow group <sup>1</sup>                                 |                        | 26                          |     |      |

|      | • Fast group <sup>2</sup>                                 |                        | 20                          |     |      |

|      | ECSPIx_SCLK High or Low Time-Write                        |                        | 7                           |     |      |

| CS3  | ECSPIx_SCLK Rise or Fall <sup>3</sup>                     | t <sub>RISE/FALL</sub> | _                           | —   | ns   |

| CS4  | ECSPIx_SSx pulse width                                    | t <sub>CSLH</sub>      | Half ECSPIx_SCLK period     | —   | ns   |

| CS5  | ECSPIx_SSx Lead Time (CS setup time)                      | t <sub>SCS</sub>       | Half ECSPIx_SCLK period - 4 | —   | ns   |

| CS6  | ECSPIx_SSx Lag Time (CS hold time)                        | t <sub>HCS</sub>       | Half ECSPIx_SCLK period - 2 | —   | ns   |

| CS7  | ECSPIx_MOSI Propagation Delay (C <sub>LOAD</sub> = 20 pF) | t <sub>PDmosi</sub>    | -1                          | 1   | ns   |

| CS8  | ECSPIx_MISO Setup Time                                    | t <sub>Smiso</sub>     |                             | —   | ns   |

|      | • Slow group <sup>1</sup>                                 |                        | 21.5                        |     |      |

|      | • Fast group <sup>2</sup>                                 |                        | 16                          |     |      |

| CS9  | ECSPIx_MISO Hold Time                                     | t <sub>Hmiso</sub>     | 0                           | —   | ns   |

| CS10 | ECSPIx_RDY to ECSPIx_SSx Time <sup>4</sup>                | t <sub>SDRY</sub>      | 5                           | —   | ns   |

#### Table 47. ECSPI Master Mode Timing Parameters

<sup>1</sup> ECSPI slow includes:

ECSPI1/DISP0\_DAT22, ECSPI1/KEY\_COL1, ECSPI1/CSI0\_DAT6, ECSPI2/EIM\_OE, ECSPI2/ECSPI2/CSI0\_DAT10, ECSPI3/DISP0\_DAT2

<sup>2</sup> ECSPI fast includes:

ECSPI1/EIM\_D17, ECSPI4/EIM\_D22, ECSPI5/SD2\_DAT0, ECSPI5/SD1\_DAT0

<sup>3</sup> See specific I/O AC parameters Section 4.7, "I/O AC Parameters."

<sup>4</sup> ECSPI\_RDY is sampled internally by ipg\_clk and is asynchronous to all other CSPI signals.

| ID | Parameter <sup>1,2</sup>                                                             | Symbol | Expression <sup>2</sup> | Min         | Мах          | Condition <sup>3</sup> | Unit |  |  |

|----|--------------------------------------------------------------------------------------|--------|-------------------------|-------------|--------------|------------------------|------|--|--|

| 81 | ESAI_TX_CLK rising edge to ESAI_TX_FS out (wr) low <sup>5</sup>                      |        | _                       |             | 22.0<br>12.0 | x ck<br>i ck           | ns   |  |  |

| 82 | ESAI_TX_CLK rising edge to ESAI_TX_FS out (wI) high                                  |        | _                       |             | 19.0<br>9.0  | x ck<br>i ck           | ns   |  |  |

| 83 | ESAI_TX_CLK rising edge to ESAI_TX_FS out (wl) low                                   |        | _                       |             | 20.0<br>10.0 | x ck<br>i ck           | ns   |  |  |

| 84 | ESAI_TX_CLK rising edge to data out enable from high impedance                       |        | _                       |             | 22.0<br>17.0 | x ck<br>i ck           | ns   |  |  |

| 86 | ESAI_TX_CLK rising edge to data out valid                                            |        |                         |             | 19.0<br>13.0 | x ck<br>i ck           | ns   |  |  |

| 87 | ESAI_TX_CLK rising edge to data out high impedance <sup>67</sup>                     |        | _                       |             | 21.0<br>16.0 | x ck<br>i ck           | ns   |  |  |

| 89 | ESAI_TX_FS input (bl, wr) setup time before<br>ESAI_TX_CLK falling edge <sup>5</sup> |        | _                       | 2.0<br>18.0 | _            | x ck<br>i ck           | ns   |  |  |

| 90 | ESAI_TX_FS input (wI) setup time before ESAI_TX_CLK falling edge                     |        |                         | 2.0<br>18.0 | _            | x ck<br>i ck           | ns   |  |  |

| 91 | ESAI_TX_FS input hold time after ESAI_TX_CLK falling edge                            |        |                         | 4.0<br>5.0  |              | x ck<br>i ck           | ns   |  |  |

| 95 | ESAI_RX_HF_CLK/ESAI_TX_HF_CLK clock cycle                                            |        | 2 x T <sub>C</sub>      | 15          | —            |                        | ns   |  |  |

| 96 | ESAI_TX_HF_CLK input rising edge to ESAI_TX_CLK output                               | _      | —                       |             | 18.0         | _                      | ns   |  |  |

| 97 | ESAI_RX_HF_CLK input rising edge to ESAI_RX_CLK output                               | —      | _                       | _           | 18.0         | _                      | ns   |  |  |

| 1  |                                                                                      |        |                         |             |              |                        |      |  |  |

#### Table 49. Enhanced Serial Audio Interface (ESAI) Timing (continued)

<sup>1</sup> i ck = internal clock

x ck = external clock

i ck a = internal clock, asynchronous mode

(asynchronous implies that ESAI\_TX\_CLK and ESAI\_RX\_CLK are two different clocks)

i ck s = internal clock, synchronous mode

(synchronous implies that ESAI\_TX\_CLK and ESAI\_RX\_CLK are the same clock)

<sup>2</sup> bl = bit length

- wl = word length

- wr = word length relative

- <sup>3</sup> ESAI\_TX\_CLK(ESAI\_TX\_CLK pin) = transmit clock

ESAI\_RX\_CLK(ESAI\_RX\_CLK pin) = receive clock

ESAI\_TX\_FS(ESAI\_TX\_FS pin) = transmit frame sync

ESAI\_RX\_FS(ESAI\_RX\_FS pin) = receive frame sync

ESAI\_TX\_HF\_CLK(ESAI\_TX\_HF\_CLK pin) = transmit high frequency clock

ESAI\_RX\_HF\_CLK(ESAI\_RX\_HF\_CLK pin) = receive high frequency clock

<sup>4</sup> For the internal clock, the external clock cycle is defined by lcyc and the ESAI control register.

<sup>5</sup> The word-relative frame sync signal waveform relative to the clock operates in the same manner as the bit-length frame sync signal waveform, but it spreads from one serial clock before the first bit clock (like the bit length frame sync signal), until the second-to-last bit clock of the first word in the frame.

<sup>6</sup> Periodically sampled and not 100% tested.

# 4.12.5.2 RMII Mode Timing

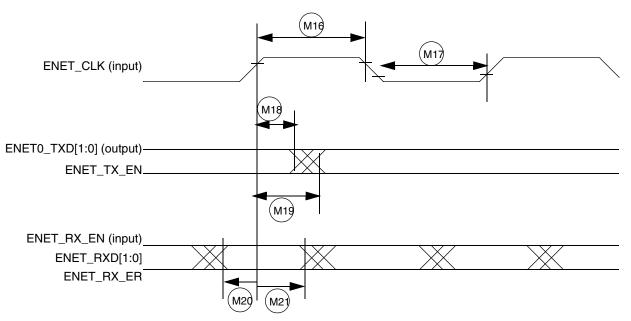

In RMII mode, ENET\_CLK is used as the REF\_CLK, which is a 50 MHz  $\pm$  50 ppm continuous reference clock. ENET\_RX\_EN is used as the ENET\_RX\_EN in RMII. Other signals under RMII mode include ENET\_TX\_EN, ENET0\_TXD[1:0], ENET\_RXD[1:0] and ENET\_RX\_ER.

Figure 46 shows RMII mode timings. Table 57 describes the timing parameters (M16–M21) shown in the figure.

Figure 46. RMII Mode Signal Timing Diagram

| Tabla | 57  | DMII | Signal | Timing  |

|-------|-----|------|--------|---------|

| Table | 57. |      | Signal | rinning |

| ID  | Characteristic                                                      | Min | Max  | Unit            |

|-----|---------------------------------------------------------------------|-----|------|-----------------|

| M16 | ENET_CLK pulse width high                                           | 35% | 65%  | ENET_CLK period |

| M17 | ENET_CLK pulse width low                                            | 35% | 65%  | ENET_CLK period |

| M18 | ENET_CLK to ENET0_TXD[1:0], ENET_TX_EN invalid                      | 4   | —    | ns              |

| M19 | ENET_CLK to ENET0_TXD[1:0], ENET_TX_EN valid                        | —   | 13.5 | ns              |

| M20 | ENET_RXD[1:0], ENET_RX_EN(ENET_RX_EN), ENET_RX_ER to ENET_CLK setup | 4   | _    | ns              |

| M21 | ENET_CLK to ENET_RXD[1:0], ENET_RX_EN, ENET_RX_ER hold              | 2   | —    | ns              |

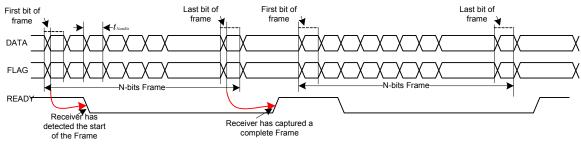

# 4.12.13.3 Receiver Real-Time Data Flow

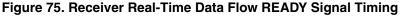

Figure 76. Synchronized Data Flow Transmission with WAKE

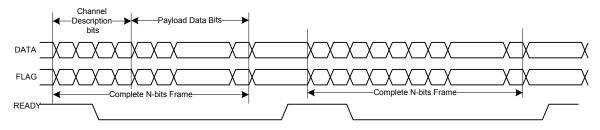

# 4.12.13.5 Stream Transmission Mode Frame Transfer

# 4.12.20 SSI Timing Parameters

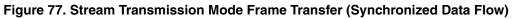

This section describes the timing parameters of the SSI module. The connectivity of the serial synchronous interfaces are summarized in Table 81.

| Port          | Signal Nomenclature | Type and Access                            |

|---------------|---------------------|--------------------------------------------|

| AUDMUX port 1 | SSI 1               | Internal                                   |

| AUDMUX port 2 | SSI 2               | Internal                                   |

| AUDMUX port 3 | AUD3                | External – AUD3 I/O                        |

| AUDMUX port 4 | AUD4                | External – EIM or CSPI1 I/O through IOMUXC |

| AUDMUX port 5 | AUD5                | External – EIM or SD1 I/O through IOMUXC   |

| AUDMUX port 6 | AUD6                | External – EIM or DISP2 through IOMUXC     |

| AUDMUX port 7 | SSI 3               | Internal                                   |

Table 81. AUDMUX Port Allocation

### NOTE

The terms WL and BL used in the timing diagrams and tables refer to Word Length (WL) and Bit Length (BL).

# 4.12.20.1 SSI Transmitter Timing with Internal Clock

Figure 90 depicts the SSI transmitter internal clock timing and Table 82 lists the timing parameters for the SSI transmitter internal clock.

Figure 90. SSI Transmitter Internal Clock Timing Diagram

#### Package Information and Contact Assignments

|                           |      |               |           | Out of Reset Condition <sup>1</sup> |                                   |              |                    |  |  |

|---------------------------|------|---------------|-----------|-------------------------------------|-----------------------------------|--------------|--------------------|--|--|

| Ball Name                 | Ball | Power Group   | Ball Type | Default<br>Mode<br>(Reset<br>Mode)  | Default Function<br>(Signal Name) | Input/Output | Value <sup>2</sup> |  |  |

| EIM_DA6                   | K25  | NVCC_EIM2     | GPIO      | ALT0                                | EIM_AD06                          | Input        | PU (100K)          |  |  |

| EIM_DA7                   | L25  | NVCC_EIM2     | GPIO      | ALT0                                | EIM_AD07                          | Input        | PU (100K)          |  |  |

| EIM_DA8                   | L24  | NVCC_EIM2     | GPIO      | ALT0                                | EIM_AD08                          | Input        | PU (100K)          |  |  |

| EIM_DA9                   | M21  | NVCC_EIM2     | GPIO      | ALT0                                | EIM_AD09                          | Input        | PU (100K)          |  |  |

| EIM_DA10                  | M22  | NVCC_EIM2     | GPIO      | ALT0                                | EIM_AD10                          | Input        | PU (100K)          |  |  |

| EIM_DA11                  | M20  | NVCC_EIM2     | GPIO      | ALT0                                | EIM_AD11                          | Input        | PU (100K)          |  |  |

| EIM_DA12                  | M24  | NVCC_EIM2     | GPIO      | ALT0                                | EIM_AD12                          | Input        | PU (100K)          |  |  |

| EIM_DA13                  | M23  | NVCC_EIM2     | GPIO      | ALT0                                | EIM_AD13                          | Input        | PU (100K)          |  |  |

| EIM_DA14                  | N23  | NVCC_EIM2     | GPIO      | ALT0                                | EIM_AD14                          | Input        | PU (100K)          |  |  |

| EIM_DA15                  | N24  | NVCC_EIM2     | GPIO      | ALT0                                | EIM_AD15                          | Input        | PU (100K)          |  |  |

| EIM_EB0                   | K21  | NVCC_EIM2     | GPIO      | ALT0                                | EIM_EB0_B                         | Output       | 1                  |  |  |

| EIM_EB1                   | K23  | NVCC_EIM2     | GPIO      | ALT0                                | EIM_EB1_B                         | Output       | 1                  |  |  |

| EIM_EB2                   | E22  | NVCC_EIM0     | GPIO      | ALT5                                | GPIO2_IO30                        | Input        | PU (100K)          |  |  |

| EIM_EB3                   | F23  | NVCC_EIM0     | GPIO      | ALT5                                | GPIO2_IO31                        | Input        | PU (100K)          |  |  |

| EIM_LBA                   | K22  | NVCC_EIM1     | GPIO      | ALT0                                | EIM_LBA_B                         | Output       | 1                  |  |  |

| EIM_OE                    | J24  | NVCC_EIM1     | GPIO      | ALT0                                | EIM_OE                            | Output       | 1                  |  |  |

| EIM_RW                    | K20  | NVCC_EIM1     | GPIO      | ALT0                                | EIM_RW                            | Output       | 1                  |  |  |

| EIM_WAIT                  | M25  | NVCC_EIM2     | GPIO      | ALT0                                | EIM_WAIT                          | Input        | PU (100K)          |  |  |

| ENET_CRS_DV               | U21  | NVCC_ENET     | GPIO      | ALT5                                | GPIO1_IO25                        | Input        | PU (100K)          |  |  |

| ENET_MDC                  | V20  | NVCC_ENET     | GPIO      | ALT5                                | GPIO1_IO31                        | Input        | PU (100K)          |  |  |

| ENET_MDIO                 | V23  | NVCC_ENET     | GPIO      | ALT5                                | GPIO1_IO22                        | Input        | PU (100K)          |  |  |

| ENET_REF_CLK <sup>3</sup> | V22  | NVCC_ENET     | GPIO      | ALT5                                | GPIO1_IO23                        | Input        | PU (100K)          |  |  |

| ENET_RX_ER                | W23  | NVCC_ENET     | GPIO      | ALT5                                | GPIO1_IO24                        | Input        | PU (100K)          |  |  |

| ENET_RXD0                 | W21  | NVCC_ENET     | GPIO      | ALT5                                | GPIO1_IO27                        | Input        | PU (100K)          |  |  |

| ENET_RXD1                 | W22  | NVCC_ENET     | GPIO      | ALT5                                | GPIO1_IO26                        | Input        | PU (100K)          |  |  |

| ENET_TX_EN                | V21  | NVCC_ENET     | GPIO      | ALT5                                | GPIO1_IO28                        | Input        | PU (100K)          |  |  |

| ENET_TXD0                 | U20  | NVCC_ENET     | GPIO      | ALT5                                | GPIO1_IO30                        | Input        | PU (100K)          |  |  |

| ENET_TXD1                 | W20  | NVCC_ENET     | GPIO      | ALT5                                | GPIO1_IO29                        | Input        | PU (100K)          |  |  |

| GPIO_0                    | T5   | NVCC_GPIO     | GPIO      | ALT5                                | GPIO1_IO00                        | Input        | PD (100K)          |  |  |

| GPIO_1                    | T4   | NVCC_GPIO     | GPIO      | ALT5                                | GPIO1_IO01                        | Input        | PU (100K)          |  |  |

| GPIO_16                   | R2   | NVCC_GPIO     | GPIO      | ALT5                                | GPIO7_IO11                        | Input        | PU (100K)          |  |  |

| <br>GPIO_17               | R1   | <br>NVCC_GPIO | GPIO      | ALT5                                | <br>GPI07_I012                    | Input        | PU (100K)          |  |  |

| <br>GPIO_18               | P6   | <br>NVCC_GPIO | GPIO      | ALT5                                | <br>GPIO7_IO13                    | Input        | PU (100K)          |  |  |

| GPIO_19                   | P5   | NVCC_GPIO     | GPIO      | ALT5                                | GPIO4_IO05                        | Input        | PU (100K)          |  |  |

| GPIO_2                    | T1   | NVCC_GPIO     | GPIO      | ALT5                                | GPIO1_IO02                        | Input        | PU (100K)          |  |  |

| GPIO_3                    | R7   | NVCC_GPIO     | GPIO      | ALT5                                | GPIO1_IO03                        | Input        | PU (100K)          |  |  |

Table 96. 21 x 21 mm Functional Contact Assignments (continued)

# 7 Revision History

Table 99 provides a revision history for the i.MX 6Dual/6Quad data sheet.

#### Table 99. i.MX 6Dual/6Quad Data Sheet Document Revision History

| Rev.<br>Number Date | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5 09/2017           | <ul> <li>Rev. 5 changes include the following:</li> <li>Changed throughout:</li> <li>Changed terminology from 'floating' to 'not connected''.</li> <li>Removed VADC feature from 19mm x 19mm package. Contact NXP sales and marketing with enablement options.</li> <li>Section 1.2, 'Features' on page 1: Corrected A9 core speed from 1 GHz to 1.2 GHz.</li> <li>Section 1.2, 'Features' on page 5: Changed Internal/external peripheral item from 'LVDS serial ports-One port up to 165 MPike/sec'to: 'One port up to 176 MPike/sec''.</li> <li>Table 1, "Example Orderable Part Numbers": Added part numbers for 1.2 GHz extended commercial parts and silicon revision 1.4 with suffix "E".</li> <li>Section 1.3, 'Signal Naming Convention' on page 8' and Section 6.1, 'Signal Naming Convention': changed wording from <i>updated</i> or <i>changed signal naming</i>, to <i>standard signal naming</i>.</li> <li>Table 2, "I/MX 6Dua/6Ouad Modules List,' on page 11: - Added DUET module.</li> <li>Section 4, 'Electrical Characteristics' on page 20: Changed several references from JESD and JEDEC standards to cross references to the Section 4.10, "Multi-Mode DDR Controller (MMDC).</li> <li>Table 4, "Absolute Maximum Ratings" on page 21: Multiple changes: - Core supply voltages: Separated rows by LDO enabled and LDO bypass. For LDO enabled, changed maximum value from 1.5 to 1.6V.</li> <li>Renamed Internal supply voltage to Core supply output voltage (LDO enabled) and changed maximum value from 1.5 to 1.6V.</li> <li>Rendred VDD_HIGH_IN row and changed maximum value from 3.6 to 3.7V.</li> <li>DDR I/O supply voltage: Added symbols. Changed maximum value from 3.6 to 3.7V.</li> <li>Resequenced: HDM, PCIe, and SATA PHY high (VPH) supply voltage to precede low (VP)</li> <li>Added row: RGMI I/O supply voltage: Added symbols. Changed maximum value from 3.6 to 3.7V.</li> <li>Resequenced: HDM, PCIe, and SATA PHY high (VPH) supply voltage to precede low (VP)</li> <li>Added row: RGMI I/O supply voltage: Added symbols. Changed maximum value from 1.275 V for operation up t</li></ul> |

#### **Revision History**