# E·XFL

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                            |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Not For New Designs                                                                                                 |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 4 Core, 32-Bit                                                                                                      |

| Speed                              | 1.2GHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON <sup>™</sup> SIMD                                                                                  |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | SATA 3Gbps (1)                                                                                                      |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | -20°C ~ 105°C (TJ)                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-LFBGA, FCBGA                                                                                                    |

| Supplier Device Package            | 624-FCPBGA (21x21)                                                                                                  |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6q5eym12ac                                             |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Introduction

| Part Number     | Quad/Dual CPU | Options                   | Speed <sup>1</sup><br>Grade | Temperature<br>Grade   | Package                                             |

|-----------------|---------------|---------------------------|-----------------------------|------------------------|-----------------------------------------------------|

| SCIMX6Q5EYM12CE | i.MX 6Quad    | Includes VPU, GPU,<br>HCP | 1.2 GHz                     | Extended<br>Commercial | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (non-lidded) |

| MCIMX6D5EYM12AC | i.MX 6Dual    | Includes VPU, GPU         | 1.2 GHz                     | Extended<br>Commercial | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (non-lidded) |

| MCIMX6D5EYM12AD | i.MX 6Dual    | Includes VPU, GPU         | 1.2 GHz                     | Extended<br>Commercial | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (non-lidded) |

| MCIMX6D5EYM12AE | i.MX 6Dual    | Includes VPU, GPU         | 1.2 GHz                     | Extended<br>Commercial | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (non-lidded) |

| SCIMX6D5EYM12CC | i.MX 6Dual    | Includes VPU, GPU,<br>HCP | 1.2 GHz                     | Extended<br>Commercial | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (non-lidded) |

| SCIMX6D5EYM12CD | i.MX 6Dual    | Includes VPU, GPU,<br>HCP | 1.2 GHz                     | Extended<br>Commercial | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (non-lidded) |

| SCIMX6D5EYM12CE | i.MX 6Dual    | Includes VPU, GPU,<br>HCP | 1.2 GHz                     | Extended<br>Commercial | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (non-lidded) |

Table 1. Example Orderable Part Numbers (continued)

<sup>1</sup> If a 24 MHz input clock is used (required for USB), the maximum SoC speed is limited to 996 MHz.

Figure 1 describes the part number nomenclature to identify the characteristics of the specific part number you have (for example, cores, frequency, temperature grade, fuse options, silicon revision). Figure 1 applies to the i.MX 6Dual/6Quad.

The two characteristics that identify which data sheet a specific part applies to are the part number series field and the temperature grade (junction) field:

- The i.MX 6Dual/6Quad Automotive and Infotainment Applications Processors data sheet (IMX6DQAEC) covers parts listed with "A (Automotive temp)"

- The i.MX 6Dual/6Quad Applications Processors for Consumer Products data sheet (IMX6DQCEC) covers parts listed with "D (Commercial temp)" or "E (Extended Commercial temp)"

- The i.MX 6Dual/6Quad Applications Processors for Industrial Products data sheet (IMX6DQIEC) covers parts listed with "C (Industrial temp)"

The Ensure that you have the right data sheet for your specific part by checking the temperature grade (junction) field and matching it to the right data sheet. If you have questions, see nxp.com/imx6series or contact your NXP representative.

- 1-bit or 4-bit transfer mode specifications for SD and SDIO cards up to UHS-I SDR-104 mode (104 MB/s max)

- 1-bit, 4-bit, or 8-bit transfer mode specifications for MMC cards up to 52 MHz in both SDR and DDR modes (104 MB/s max)

- USB:

- One High Speed (HS) USB 2.0 OTG (Up to 480 Mbps), with integrated HS USB PHY

- Three USB 2.0 (480 Mbps) hosts:

- One HS host with integrated High Speed PHY

- Two HS hosts with integrated High Speed Inter-Chip (HS-IC) USB PHY

- Expansion PCI Express port (PCIe) v2.0 one lane

- PCI Express (Gen 2.0) dual mode complex, supporting Root complex operations and Endpoint operations. Uses x1 PHY configuration.

- Miscellaneous IPs and interfaces:

- SSI block capable of supporting audio sample frequencies up to 192 kHz stereo inputs and outputs with I<sup>2</sup>S mode

- ESAI is capable of supporting audio sample frequencies up to 260 kHz in I2S mode with 7.1 multi channel outputs

- Five UARTs, up to 5.0 Mbps each:

- Providing RS232 interface

- Supporting 9-bit RS485 multidrop mode

- One of the five UARTs (UART1) supports 8-wire while the other four support 4-wire. This is due to the SoC IOMUX limitation, because all UART IPs are identical.

- Five eCSPI (Enhanced CSPI)

- Three I2C, supporting 400 kbps

- Gigabit Ethernet Controller (IEEE1588 compliant),  $10/100/1000^1$  Mbps

- Four Pulse Width Modulators (PWM)

- System JTAG Controller (SJC)

- GPIO with interrupt capabilities

- 8x8 Key Pad Port (KPP)

- Sony Philips Digital Interconnect Format (SPDIF), Rx and Tx

- Two Controller Area Network (FlexCAN), 1 Mbps each

- Two Watchdog timers (WDOG)

- Audio MUX (AUDMUX)

- MLB (MediaLB) provides interface to MOST Networks (150 Mbps) with the option of DTCP cipher accelerator

1. The theoretical maximum performance of 1 Gbps ENET is limited to 470 Mbps (total for Tx and Rx) due to internal bus throughput limitations. The actual measured performance in optimized environment is up to 400 Mbps. For details, see the ERR004512 erratum in the i.MX 6Dual/6Quad errata document (IMX6DQCE).

Architectural Overview

# 2 Architectural Overview

The following subsections provide an architectural overview of the i.MX 6Dual/6Quad processor system.

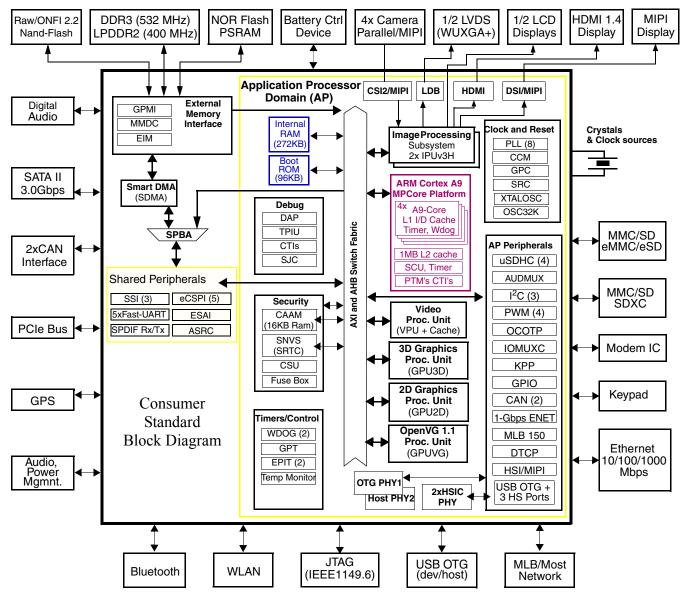

# 2.1 Block Diagram

Figure 2 shows the functional modules in the i.MX 6Dual/6Quad processor system.

Figure 2. i.MX 6Dual/6Quad Consumer Grade System Block Diagram

NOTE

The numbers in brackets indicate number of module instances. For example, PWM (4) indicates four separate PWM peripherals.

| Table 2. i.MX 6Dual/6Quad Modules List (d | continued) |

|-------------------------------------------|------------|

|-------------------------------------------|------------|

| Block<br>Mnemonic                | Block Name                    | Subsystem                                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|----------------------------------|-------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LDB                              | LVDS Display Bridge           | Connectivity<br>Peripherals                 | <ul> <li>LVDS Display Bridge is used to connect the IPU (Image Processing Unit to External LVDS Display Interface. LDB supports two channels; each channel has following signals:</li> <li>One clock pair</li> <li>Four data pairs</li> <li>Each signal pair contains LVDS special differential pad (PadP, PadM).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| MLB150                           | MediaLB                       | Connectivity /<br>Multimedia<br>Peripherals | The MLB interface module provides a link to a MOST <sup>®</sup> data network, using the standardized MediaLB protocol (up to 150 Mbps). The module is backward compatible to MLB-50.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| MMDC                             | Multi-Mode DDR<br>Controller  | Connectivity<br>Peripherals                 | <ul> <li>DDR Controller has the following features:</li> <li>Supports 16/32/64-bit DDR3 / DDR3L or LPDDR2</li> <li>Supports both dual x32 for LPDDR2 and x64 DDR3 / LPDDR2 configurations (including 2x32 interleaved mode)</li> <li>Supports up to 4 GByte DDR memory space</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| OCOTP_CTRL                       | OTP Controller                | Security                                    | The On-Chip OTP controller (OCOTP_CTRL) provides an interface for reading, programming, and/or overriding identification and control information stored in on-chip fuse elements. The module supports electrically-programmable poly fuses (eFUSEs). The OCOTP_CTRL also provides a set of volatile software-accessible signals that can be used for software control of hardware elements, not requiring non-volatility. The OCOTP_CTRL provides the primary user-visible mechanism for interfacing with on-chip fuse elements. Among the uses for the fuses are unique chip identifiers, mask revision numbers, cryptographic keys, JTAG secure mode, boot characteristics, and various control signals, requiring permanent non-volatility. |  |

| OCRAM                            | On-Chip Memory<br>Controller  | Data Path                                   | The On-Chip Memory controller (OCRAM) module is designed as an interface between system's AXI bus and internal (on-chip) SRAM memory module.<br>In i.MX 6Dual/6Quad processors, the OCRAM is used for controlling the 256 KB multimedia RAM through a 64-bit AXI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| OSC 32 kHz                       | OSC 32 kHz                    | Clocking                                    | Generates 32.768 kHz clock from an external crystal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| PCle                             | PCI Express 2.0               | Connectivity<br>Peripherals                 | The PCIe IP provides PCI Express Gen 2.0 functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| PMU                              | Power-Management<br>Functions | Data Path                                   | Integrated power management unit. Used to provide power to various SoC domains.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| PWM-1<br>PWM-2<br>PWM-3<br>PWM-4 | Pulse Width<br>Modulation     | Connectivity<br>Peripherals                 | The pulse-width modulator (PWM) has a 16-bit counter and is optimized to generate sound from stored sample audio images and it can also generate tones. It uses 16-bit resolution and a 4x16 data FIFO to generate sound.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| RAM<br>16 KB                     | Secure/non-secure<br>RAM      | Secured<br>Internal<br>Memory               | Secure/non-secure Internal RAM, interfaced through the CAAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| RAM<br>256 KB                    | Internal RAM                  | Internal<br>Memory                          | Internal RAM, which is accessed through OCRAM memory controllers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Table 2. i.MX 6Dual/6Quad Modules List (continued) |

|----------------------------------------------------|

|----------------------------------------------------|

| Block<br>Mnemonic                              | Block Name                                   | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------|----------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSI-1<br>SSI-2<br>SSI-3                        | I2S/SSI/AC97<br>Interface                    | Connectivity<br>Peripherals      | The SSI is a full-duplex synchronous interface, which is used on the processor to provide connectivity with off-chip audio peripherals. The SSI supports a wide variety of protocols (SSI normal, SSI network, I2S, and AC-97), bit depths (up to 24 bits per word), and clock / frame sync options. The SSI has two pairs of 8x24 FIFOs and hardware support for an external DMA controller to minimize its impact on system performance. The second pair of FIFOs provides hardware interleaving of a second audio stream that reduces CPU overhead in use cases where two time slots are being used simultaneously. |

| TEMPMON                                        | Temperature Monitor                          | System<br>Control<br>Peripherals | The temperature monitor/sensor IP module for detecting high temperature conditions. The temperature read out does not reflect case or ambient temperature. It reflects the temperature in proximity of the sensor location on the die. Temperature distribution may not be uniformly distributed; therefore, the read out value may not be the reflection of the temperature value for the entire die.                                                                                                                                                                                                                 |

| TZASC                                          | Trust-Zone Address<br>Space Controller       | Security                         | The TZASC (TZC-380 by ARM) provides security address region control functions required for intended application. It is used on the path to the DRAM controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| UART-1<br>UART-2<br>UART-3<br>UART-4<br>UART-5 | UART Interface                               | Connectivity<br>Peripherals      | <ul> <li>Each of the UARTv2 modules support the following serial data transmit/receive protocols and configurations:</li> <li>7- or 8-bit data words, 1 or 2 stop bits, programmable parity (even, odd or none)</li> <li>Programmable baud rates up to 5 MHz</li> <li>32-byte FIFO on Tx and 32 half-word FIFO on Rx supporting auto-baud</li> <li>IrDA 1.0 support (up to SIR speed of 115200 bps)</li> <li>Option to operate as 8-pins full UART, DCE, or DTE</li> </ul>                                                                                                                                             |

| USBOH3A                                        | USB 2.0 High Speed<br>OTG and 3x HS<br>Hosts | Connectivity<br>Peripherals      | <ul> <li>USBOH3 contains:</li> <li>One high-speed OTG module with integrated HS USB PHY</li> <li>One high-speed Host module with integrated HS USB PHY</li> <li>Two identical high-speed Host modules connected to HSIC USB ports.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                          |

system to determine when the load capability of the regulator is being exceeded to take the necessary steps. Current-limiting can be enabled to allow for in-rush current requirements during start-up, if needed. Active-pull-down can also be enabled for systems requiring this feature.

For information on external capacitor requirements for this regulator, see the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG).

For additional information, see the i.MX 6Dual/6Quad reference manual (IMX6DQRM).

# 4.3.2.2 LDO\_2P5

The LDO\_2P5 module implements a programmable linear-regulator function from VDD\_HIGH\_IN (see Table 6 for min and max input requirements). Typical Programming Operating Range is 2.25 V to 2.75 V with the nominal default setting as 2.5 V. The LDO\_2P5 supplies the SATA PHY, USB PHY, LVDS PHY, HDMI PHY, MIPI PHY, E-fuse module and PLLs. A programmable brown-out detector is included in the regulator that can be used by the system to determine when the load capability of the regulator is being exceeded, to take the necessary steps. Current-limiting can be enabled to allow for in-rush current requirements during start-up, if needed. Active-pull-down can also be enabled for systems requiring this feature. An alternate self-biased low-precision weak-regulator is included that can be enabled for applications needing to keep the output voltage alive during low-power modes where the main regulator driver and its associated global bandgap reference module are disabled. The output of the weak-regulator is not programmable and is a function of the input supply as well as the load current. Typically, with a 3 V input supply the weak-regulator output is 2.525 V and its output impedance is approximately  $40 \, \Omega$ .

For information on external capacitor requirements for this regulator, see the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG).

For additional information, see the i.MX 6Dual/6Quad reference manual (IMX6DQRM).

# 4.3.2.3 LDO\_USB

The LDO\_USB module implements a programmable linear-regulator function from the USB\_OTG\_VBUS and USB\_H1\_VBUS voltages (4.4 V–5.25 V) to produce a nominal 3.0 V output voltage. A programmable brown-out detector is included in the regulator that can be used by the system to determine when the load capability of the regulator is being exceeded, to take the necessary steps. This regulator has a built in power-mux that allows the user to select to run the regulator from either VBUS supply, when both are present. If only one of the VBUS voltages is present, then the regulator automatically selects this supply. Current limit is also included to help the system meet in-rush current targets. If no VBUS voltage is present, then the VBUSVALID threshold setting will prevent the regulator from being enabled.

For information on external capacitor requirements for this regulator, see the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG).

For additional information, see the i.MX 6Dual/6Quad reference manual (IMX6DQRM).

# 4.8.1 GPIO Output Buffer Impedance

Table 34 shows the GPIO output buffer impedance (OVDD 1.8 V).

#### Table 34. GPIO Output Buffer Average Impedance (OVDD 1.8 V)

| Parameter                  | Symbol | Drive Strength (DSE) | Typ Value | Unit |

|----------------------------|--------|----------------------|-----------|------|

|                            |        | 001                  | 260       |      |

|                            | Rdrv   | 010                  | 130       |      |

|                            |        | 011                  | 90        |      |

| Output Driver<br>Impedance |        | 100                  | 60        | Ω    |

|                            |        | 101                  | 50        |      |

|                            |        | 110                  | 40        |      |

|                            |        | 111                  | 33        |      |

Table 35 shows the GPIO output buffer impedance (OVDD 3.3 V).

#### Table 35. GPIO Output Buffer Average Impedance (OVDD 3.3 V)

| Parameter     | Symbol | Drive Strength (DSE) | Typ Value | Unit |

|---------------|--------|----------------------|-----------|------|

|               |        | 001                  | 150       |      |

|               | Rdrv   | 010                  | 75        |      |

|               |        | 011                  | 50        |      |

| Output Driver |        | 100                  | 37        | Ω    |

| Impedance     |        | 101                  | 30        |      |

|               |        | 110                  | 25        |      |

|               |        | 111                  | 20        |      |

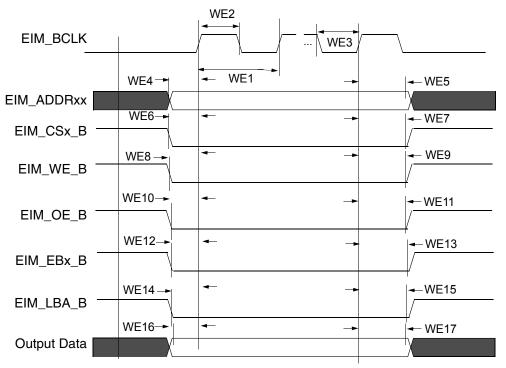

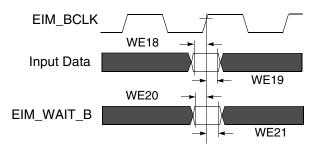

# 4.9.3.2 General EIM Timing-Synchronous Mode

Figure 12, Figure 13, and Table 41 specify the timings related to the EIM module. All EIM output control signals may be asserted and deasserted by an internal clock synchronized to the EIM\_BCLK rising edge according to corresponding assertion/negation control fields.

Figure 12. EIM Output Timing Diagram

Figure 13. EIM Input Timing Diagram

# 4.9.3.3 Examples of EIM Synchronous Accesses

Table 41. EIM Bus Timing Parameters

| ID  | Parameter                        | Min <sup>1</sup>            | Max <sup>1</sup> | Unit |

|-----|----------------------------------|-----------------------------|------------------|------|

| WE1 | EIM_BCLK cycle time <sup>2</sup> | t × (k+1)                   | —                | ns   |

| WE2 | EIM_BCLK high level width        | $0.4 \times t \times (k+1)$ | —                | ns   |

| WE3 | EIM_BCLK low level width         | $0.4 \times t \times (k+1)$ | —                | ns   |

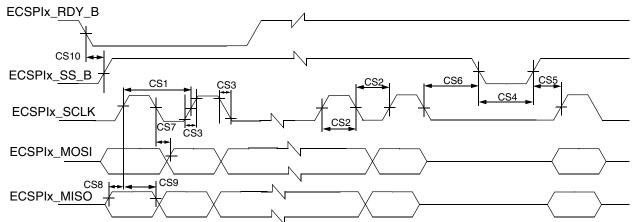

# 4.12.2.1 ECSPI Master Mode Timing

Figure 35 depicts the timing of ECSPI in master mode and Table 47 lists the ECSPI master mode timing characteristics.

Note: ECSPIx\_MOSI is always driven (not tri-stated) between actual data transmissions. This limits the ECSPI to be connected between a single master and a single slave.

#### Figure 35. ECSPI Master Mode Timing Diagram

| ID   | Parameter                                                 | Symbol                 | Min                         | Max | Unit |

|------|-----------------------------------------------------------|------------------------|-----------------------------|-----|------|

| CS1  | ECSPIx_SCLK Cycle Time-Read                               | t <sub>clk</sub>       |                             | —   | ns   |

|      | • Slow group <sup>1</sup>                                 |                        | 55                          |     |      |

|      | • Fast group <sup>2</sup>                                 |                        | 40                          |     |      |

|      | ECSPIx_SCLK Cycle Time–Write                              |                        | 15                          |     |      |

| CS2  | ECSPIx_SCLK High or Low Time-Read                         | t <sub>SW</sub>        |                             | —   | ns   |

|      | • Slow group <sup>1</sup>                                 |                        | 26                          |     |      |

|      | • Fast group <sup>2</sup>                                 |                        | 20                          |     |      |

|      | ECSPIx_SCLK High or Low Time-Write                        |                        | 7                           |     |      |

| CS3  | ECSPIx_SCLK Rise or Fall <sup>3</sup>                     | t <sub>RISE/FALL</sub> | _                           | —   | ns   |

| CS4  | ECSPIx_SSx pulse width                                    | t <sub>CSLH</sub>      | Half ECSPIx_SCLK period     | —   | ns   |

| CS5  | ECSPIx_SSx Lead Time (CS setup time)                      | t <sub>SCS</sub>       | Half ECSPIx_SCLK period - 4 | —   | ns   |

| CS6  | ECSPIx_SSx Lag Time (CS hold time)                        | t <sub>HCS</sub>       | Half ECSPIx_SCLK period - 2 | —   | ns   |

| CS7  | ECSPIx_MOSI Propagation Delay (C <sub>LOAD</sub> = 20 pF) | t <sub>PDmosi</sub>    | -1                          | 1   | ns   |

| CS8  | ECSPIx_MISO Setup Time                                    | t <sub>Smiso</sub>     |                             | —   | ns   |

|      | • Slow group <sup>1</sup>                                 |                        | 21.5                        |     |      |

|      | • Fast group <sup>2</sup>                                 |                        | 16                          |     |      |

| CS9  | ECSPIx_MISO Hold Time                                     | t <sub>Hmiso</sub>     | 0                           | —   | ns   |

| CS10 | ECSPIx_RDY to ECSPIx_SSx Time <sup>4</sup>                | t <sub>SDRY</sub>      | 5                           | —   | ns   |

#### Table 47. ECSPI Master Mode Timing Parameters

<sup>1</sup> ECSPI slow includes:

ECSPI1/DISP0\_DAT22, ECSPI1/KEY\_COL1, ECSPI1/CSI0\_DAT6, ECSPI2/EIM\_OE, ECSPI2/ECSPI2/CSI0\_DAT10, ECSPI3/DISP0\_DAT2

<sup>2</sup> ECSPI fast includes:

ECSPI1/EIM\_D17, ECSPI4/EIM\_D22, ECSPI5/SD2\_DAT0, ECSPI5/SD1\_DAT0

<sup>3</sup> See specific I/O AC parameters Section 4.7, "I/O AC Parameters."

<sup>4</sup> ECSPI\_RDY is sampled internally by ipg\_clk and is asynchronous to all other CSPI signals.

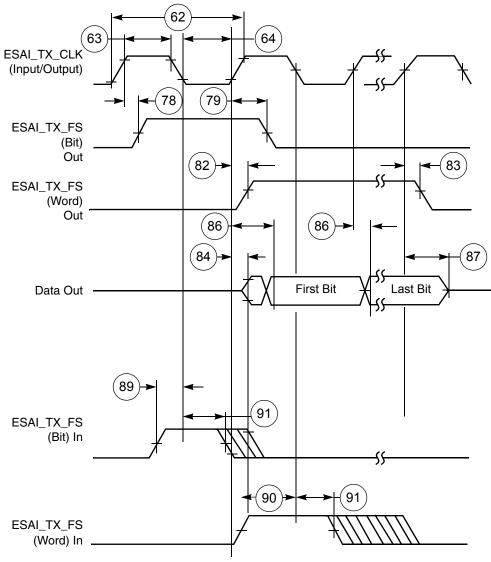

Figure 37. ESAI Transmitter Timing

| Table 55. MII Asynchronous | Inputs | Signal 7 | Гiming |

|----------------------------|--------|----------|--------|

|----------------------------|--------|----------|--------|

| ID              | Characteristic                           | Min | Max | Unit               |

|-----------------|------------------------------------------|-----|-----|--------------------|

| M9 <sup>1</sup> | ENET_CRS to ENET_COL minimum pulse width | 1.5 |     | ENET_TX_CLK period |

<sup>1</sup> ENET\_COL has the same timing in 10-Mbit 7-wire interface mode.

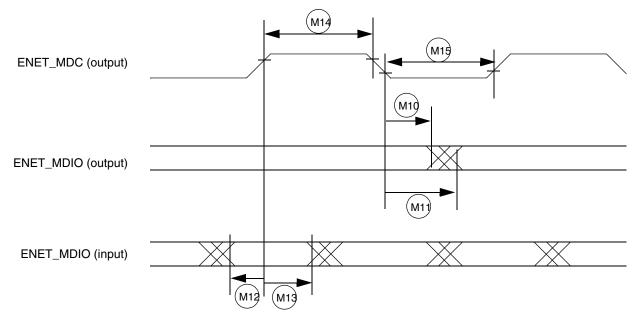

### 4.12.5.1.4 MII Serial Management Channel Timing (ENET\_MDIO and ENET\_MDC)

The MDC frequency is designed to be equal to or less than 2.5 MHz to be compatible with the IEEE 802.3 MII specification. However the ENET can function correctly with a maximum MDC frequency of 15 MHz.

Figure 45 shows MII asynchronous input timings. Table 56 describes the timing parameters (M10–M15) shown in the figure.

Figure 45. MII Serial Management Channel Timing Diagram

| Table 56. MII Serial Management Cha | nnel Timing |

|-------------------------------------|-------------|

|-------------------------------------|-------------|

| ID  | Characteristic                                                                | Min | Max | Unit            |

|-----|-------------------------------------------------------------------------------|-----|-----|-----------------|

| M10 | ENET_MDC falling edge to ENET_MDIO output invalid (minimum propagation delay) | 0   | _   | ns              |

| M11 | ENET_MDC falling edge to ENET_MDIO output valid (maximum propagation delay)   | _   | 5   | ns              |

| M12 | ENET_MDIO (input) to ENET_MDC rising edge setup                               | 18  | —   | ns              |

| M13 | ENET_MDIO (input) to ENET_MDC rising edge hold                                | 0   | —   | ns              |

| M14 | ENET_MDC pulse width high                                                     | 40% | 60% | ENET_MDC period |

| M15 | ENET_MDC pulse width low                                                      | 40% | 60% | ENET_MDC period |

| Symbol                  | Parameter                                 | Conditions                                   | Min | Тур | Max    | Unit |  |

|-------------------------|-------------------------------------------|----------------------------------------------|-----|-----|--------|------|--|

| t <sub>F</sub>          | Differential output signal fall time      | 20–80%<br>RL = 50 Ω<br>See Figure 57.        | 75  |     | 0.4 UI | ps   |  |

| _                       | Differential signal overshoot             | Referred to 2x V <sub>SWING</sub>            | _   | —   | 15     | %    |  |

| _                       | Differential signal undershoot            | Referred to 2x V <sub>SWING</sub>            | _   |     | 25     | %    |  |

|                         | Data and Control Interface Specifications |                                              |     |     |        |      |  |

| t <sub>Power-up</sub> 2 | HDMI 3D Tx PHY power-up time              | From power-down to<br>HSI_TX_READY assertion | —   | _   | 3.35   | ms   |  |

#### Table 60. Switching Characteristics (continued)

<sup>1</sup> Relative to ideal recovery clock, as specified in the HDMI specification, version 1.4a, section 4.2.3.

<sup>2</sup> For information about latencies and associated timings, see Section 4.12.7.1, "Latencies and Timing Information."

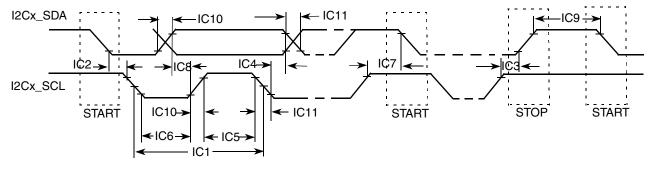

# 4.12.9 I<sup>2</sup>C Module Timing Parameters

This section describes the timing parameters of the  $I^2C$  module. Figure 58 depicts the timing of  $I^2C$  module, and Table 61 lists the  $I^2C$  module timing characteristics.

Figure 58. I<sup>2</sup>C Bus Timing

# Table 61. I<sup>2</sup>C Module Timing Parameters

| ID  | Parameter                                  | Standa         | ard Mode          | Fast Mode        |                  | Unit |

|-----|--------------------------------------------|----------------|-------------------|------------------|------------------|------|

|     |                                            | Min            | Max               | Min              | Max              | Omt  |

| IC1 | I2Cx_SCL cycle time                        | 10             | -                 | 2.5              | —                | μs   |

| IC2 | Hold time (repeated) START condition       | 4.0            | _                 | 0.6              | —                | μs   |

| IC3 | Set-up time for STOP condition             | 4.0            | _                 | 0.6              | —                | μs   |

| IC4 | Data hold time                             | 0 <sup>1</sup> | 3.45 <sup>2</sup> | 0 <sup>1</sup>   | 0.9 <sup>2</sup> | μs   |

| IC5 | HIGH Period of I2Cx_SCL Clock              | 4.0            | _                 | 0.6              | —                | μs   |

| IC6 | LOW Period of the I2Cx_SCL Clock           | 4.7            | _                 | 1.3              | —                | μs   |

| IC7 | Set-up time for a repeated START condition | 4.7            | _                 | 0.6              | —                | μs   |

| IC8 | Data set-up time                           | 250            | _                 | 100 <sup>3</sup> | _                | ns   |

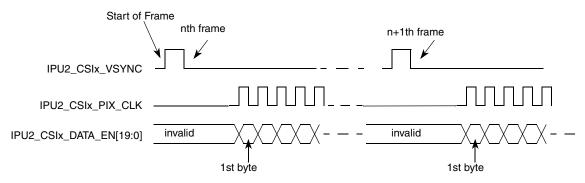

stops receiving data from the stream. For the next line, the IPU2\_CSIx\_HSYNC timing repeats. For the next frame, the IPU2\_CSIx\_VSYNC timing repeats.

### 4.12.10.2.3 Non-Gated Clock Mode

The timing is the same as the gated-clock mode (described in Section 4.12.10.2.2, "Gated Clock Mode,") except for the IPU2\_CSIx\_HSYNC signal, which is not used (see Figure 60). All incoming pixel clocks are valid and cause data to be latched into the input FIFO. The IPU2\_CSIx\_PIX\_CLK signal is inactive (states low) until valid data is going to be transmitted over the bus.

Figure 60. Non-Gated Clock Mode Timing Diagram

The timing described in Figure 60 is that of a typical sensor. Some other sensors may have a slightly different timing. The CSI can be programmed to support rising/falling-edge triggered IPU2\_CSIx\_VSYNC; active-high/low IPU2\_CSIx\_HSYNC; and rising/falling-edge triggered IPU2\_CSIx\_PIX\_CLK.

There are special physical outputs to provide synchronous controls:

- The ipp\_disp\_clk is a dedicated base synchronous signal that is used to generate a base display (component, pixel) clock for a display.

- The ipp\_pin\_1- ipp\_pin\_7 are general purpose synchronous pins, that can be used to provide HSYNC, VSYNC, DRDY or any else independent signal to a display.

The IPU has a system of internal binding counters for internal events (such as, HSYNC/VSYNC) calculation. The internal event (local start point) is synchronized with internal DI\_CLK. A suitable control starts from the local start point with predefined UP and DOWN values to calculate control's changing points with half DI\_CLK resolution. A full description of the counter system can be found in the IPU chapter of the i.MX 6Dual/6Quad reference manual (IMX6DQRM).

### 4.12.10.5.2 Asynchronous Controls

The asynchronous control is a data-oriented signal that changes its value with an output data according to additional internal flags coming with the data.

There are special physical outputs to provide asynchronous controls, as follows:

- The ipp\_d0\_cs and ipp\_d1\_cs pins are dedicated to provide chip select signals to two displays.

- The ipp\_pin\_11- ipp\_pin\_17 are general purpose asynchronous pins, that can be used to provide WR. RD, RS or any other data-oriented signal to display.

#### NOTE

The IPU has independent signal generators for asynchronous signals toggling. When a DI decides to put a new asynchronous data on the bus, a new internal start (local start point) is generated. The signal generators calculate predefined UP and DOWN values to change pins states with half DI\_CLK resolution.

# 4.12.10.6 Synchronous Interfaces to Standard Active Matrix TFT LCD Panels

### 4.12.10.6.1 IPU Display Operating Signals

The IPU uses four control signals and data to operate a standard synchronous interface:

- IPP\_DISP\_CLK—Clock to display

- HSYNC—Horizontal synchronization

- VSYNC—Vertical synchronization

- DRDY—Active data

All synchronous display controls are generated on the base of an internally generated "local start point". The synchronous display controls can be placed on time axis with DI's offset, up and down parameters. The display access can be whole number of DI clock (Tdiclk) only. The IPP\_DATA can not be moved relative to the local start point. The data bus of the synchronous interface is output direction only.

| Symbol                                     | Parameters                         | Min | Тур | Max | Unit |    |  |  |

|--------------------------------------------|------------------------------------|-----|-----|-----|------|----|--|--|

|                                            | LP Line Receiver DC Specifications |     |     |     |      |    |  |  |

| V <sub>IL</sub>                            | Input low voltage                  | _   | —   | —   | 550  | mV |  |  |

| V <sub>IH</sub>                            | Input high voltage                 | _   | 920 | _   | _    | mV |  |  |

| V <sub>HYST</sub>                          | Input hysteresis                   | _   | 25  | _   | _    | mV |  |  |

| Contention Line Receiver DC Specifications |                                    |     |     |     |      |    |  |  |

| V <sub>ILF</sub>                           | Input low fault threshold          | _   | 200 | _   | 450  | mV |  |  |

#### Table 68. Electrical and Timing Information (continued)

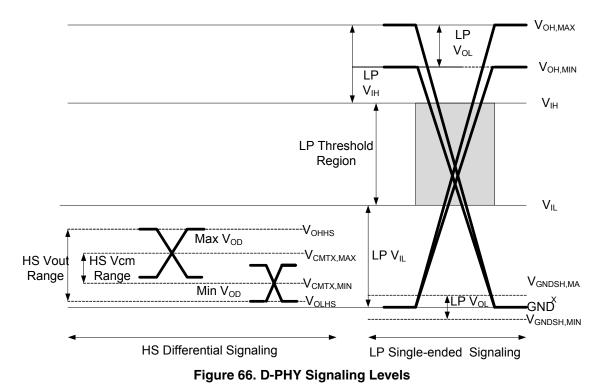

### 4.12.12.2 D-PHY Signaling Levels

The signal levels are different for differential HS mode and single-ended LP mode. Figure 66 shows both the HS and LP signal levels on the left and right sides, respectively. The HS signalling levels are below the LP low-level input threshold such that LP receiver always detects low on HS signals.

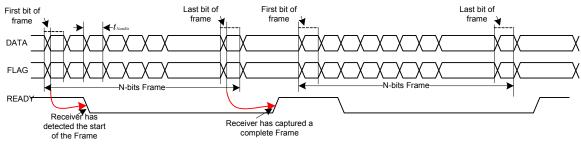

# 4.12.13.3 Receiver Real-Time Data Flow

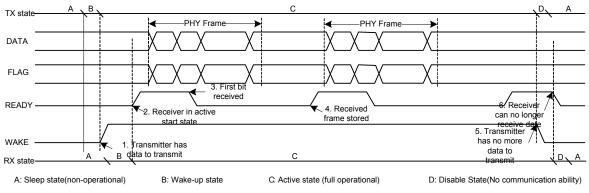

Figure 76. Synchronized Data Flow Transmission with WAKE

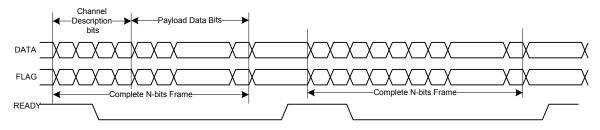

# 4.12.13.5 Stream Transmission Mode Frame Transfer

| ID   | Parameter                      | Min   | Мах | Unit |

|------|--------------------------------|-------|-----|------|

|      | Oversampling Clock Oper        | ation |     |      |

| SS47 | Oversampling clock period      | 15.04 | —   | ns   |

| SS48 | Oversampling clock high period | 6.0   | _   | ns   |

| SS49 | Oversampling clock rise time   | _     | 3.0 | ns   |

| SS50 | Oversampling clock low period  | 6.0   | _   | ns   |

| SS51 | Oversampling clock fall time   | —     | 3.0 | ns   |

#### Table 83. SSI Receiver Timing with Internal Clock (continued)

#### NOTE

- All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal AUDx\_TXC/AUDx\_RXC and/or the frame sync AUDx\_TXFS/AUDx\_RXFS shown in the tables and in the figures.

- All timings are on Audiomux Pads when SSI is being used for data transfer.

- AUDx\_TXC and AUDx\_RXC refer to the Transmit and Receive sections of the SSI.

- The terms, WL and BL, refer to Word Length (WL) and Bit Length (BL).

- For internal Frame Sync operation using external clock, the frame sync timing is same as that of transmit data (for example, during AC97 mode of operation).

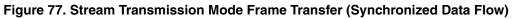

# 4.12.20.3 SSI Transmitter Timing with External Clock

Figure 92 depicts the SSI transmitter external clock timing and Table 84 lists the timing parameters for the transmitter timing with the external clock.

Figure 92. SSI Transmitter External Clock Timing Diagram

| ID   | Parameter                                           | Min   | Мах  | Unit |  |  |  |

|------|-----------------------------------------------------|-------|------|------|--|--|--|

|      | External Clock Operation                            |       |      |      |  |  |  |

| SS22 | AUDx_TXC/AUDx_RXC clock period                      | 81.4  | —    | ns   |  |  |  |

| SS23 | AUDx_TXC/AUDx_RXC clock high period                 | 36.0  | _    | ns   |  |  |  |

| SS24 | AUDx_TXC/AUDx_RXC clock rise time                   | —     | 6.0  | ns   |  |  |  |

| SS25 | AUDx_TXC/AUDx_RXC clock low period                  | 36.0  | _    | ns   |  |  |  |

| SS26 | AUDx_TXC/AUDx_RXC clock fall time                   | —     | 6.0  | ns   |  |  |  |

| SS27 | AUDx_TXC high to AUDx_TXFS (bl) high                | -10.0 | 15.0 | ns   |  |  |  |

| SS29 | AUDx_TXC high to AUDx_TXFS (bl) low                 | 10.0  | _    | ns   |  |  |  |

| SS31 | AUDx_TXC high to AUDx_TXFS (wl) high                | -10.0 | 15.0 | ns   |  |  |  |

| SS33 | AUDx_TXC high to AUDx_TXFS (wl) low                 | 10.0  | _    | ns   |  |  |  |

| SS37 | AUDx_TXC high to AUDx_TXD valid from high impedance | —     | 15.0 | ns   |  |  |  |

| SS38 | AUDx_TXC high to AUDx_TXD high/low                  | —     | 15.0 | ns   |  |  |  |

| SS39 | AUDx_TXC high to AUDx_TXD high impedance            | —     | 15.0 | ns   |  |  |  |

# 4.12.23 USB PHY Parameters

This section describes the USB-OTG PHY and the USB Host port PHY parameters.

The USB PHY meets the electrical compliance requirements defined in the Universal Serial Bus Revision 2.0 OTG, USB Host with the amendments below (On-The-Go and Embedded Host Supplement to the USB Revision 2.0 Specification is not applicable to Host port).

- USB ENGINEERING CHANGE NOTICE

- Title: 5V Short Circuit Withstand Requirement Change

- Applies to: Universal Serial Bus Specification, Revision 2.0

- Errata for USB Revision 2.0 April 27, 2000 as of 12/7/2000

- USB ENGINEERING CHANGE NOTICE

- Title: Pull-up/Pull-down resistors

- Applies to: Universal Serial Bus Specification, Revision 2.0

- USB ENGINEERING CHANGE NOTICE

- Title: Suspend Current Limit Changes

- Applies to: Universal Serial Bus Specification, Revision 2.0

- USB ENGINEERING CHANGE NOTICE

- Title: USB 2.0 Phase Locked SOFs

- Applies to: Universal Serial Bus Specification, Revision 2.0

- On-The-Go and Embedded Host Supplement to the USB Revision 2.0 Specification

- Revision 2.0 plus errata and ecn June 4, 2010

- Battery Charging Specification (available from USB-IF)

- Revision 1.2, December 7, 2010

- Portable device only

#### Package Information and Contact Assignments

|               |      |              |           | Out of Reset Condition <sup>1</sup> |                                   |              |                                 |

|---------------|------|--------------|-----------|-------------------------------------|-----------------------------------|--------------|---------------------------------|

| Ball Name     | Ball | Power Group  | Ball Type | Default<br>Mode<br>(Reset<br>Mode)  | Default Function<br>(Signal Name) | Input/Output | Value <sup>2</sup>              |

| NANDF_WP_B    | E15  | NVCC_NANDF   | GPIO      | ALT5                                | GPIO6_IO09                        | Input        | PU (100K)                       |

| ONOFF         | D12  | VDD_SNVS_IN  | GPIO      | _                                   | SRC_ONOFF                         | Input        | PU (100K)                       |

| PCIE_RXM      | B1   | PCIE_VPH     | —         | _                                   | PCIE_RX_N                         | —            | —                               |

| PCIE_RXP      | B2   | PCIE_VPH     | —         | _                                   | PCIE_RX_P                         | —            | _                               |

| PCIE_TXM      | A3   | PCIE_VPH     | —         | _                                   | PCIE_TX_N                         | —            | —                               |

| PCIE_TXP      | B3   | PCIE_VPH     | _         | _                                   | PCIE_TX_P                         | —            | _                               |

| PMIC_ON_REQ   | D11  | VDD_SNVS_IN  | GPIO      | ALT0                                | SNVS_PMIC_ON_REQ                  | Output       | Open<br>Drain with<br>PU (100K) |

| PMIC_STBY_REQ | F11  | VDD_SNVS_IN  | GPIO      | ALT0                                | CCM_PMIC_STBY_REQ                 | Output       | 0                               |

| POR_B         | C11  | VDD_SNVS_IN  | GPIO      | ALT0                                | SRC_POR_B                         | Input        | PU (100K)                       |

| RGMII_RD0     | C24  | NVCC_RGMII   | DDR       | ALT5                                | GPIO6_IO25                        | Input        | PU (100K)                       |

| RGMII_RD1     | B23  | NVCC_RGMII   | DDR       | ALT5                                | GPIO6_IO27                        | Input        | PU (100K)                       |

| RGMII_RD2     | B24  | NVCC_RGMII   | DDR       | ALT5                                | GPIO6_IO28                        | Input        | PU (100K)                       |

| RGMII_RD3     | D23  | NVCC_RGMII   | DDR       | ALT5                                | GPIO6_IO29                        | Input        | PU (100K)                       |

| RGMII_RX_CTL  | D22  | NVCC_RGMII   | DDR       | ALT5                                | GPIO6_IO24                        | Input        | PD (100K)                       |

| RGMII_RXC     | B25  | NVCC_RGMII   | DDR       | ALT5                                | GPIO6_IO30                        | Input        | PD (100K)                       |

| RGMII_TD0     | C22  | NVCC_RGMII   | DDR       | ALT5                                | GPIO6_IO20                        | Input        | PU (100K)                       |

| RGMII_TD1     | F20  | NVCC_RGMII   | DDR       | ALT5                                | GPIO6_IO21                        | Input        | PU (100K)                       |

| RGMII_TD2     | E21  | NVCC_RGMII   | DDR       | ALT5                                | GPIO6_IO22                        | Input        | PU (100K)                       |

| RGMII_TD3     | A24  | NVCC_RGMII   | DDR       | ALT5                                | GPIO6_IO23                        | Input        | PU (100K)                       |

| RGMII_TX_CTL  | C23  | NVCC_RGMII   | DDR       | ALT5                                | GPIO6_IO26                        | Input        | PD (100K)                       |

| RGMII_TXC     | D21  | NVCC_RGMII   | DDR       | ALT5                                | GPIO6_IO19                        | Input        | PD (100K)                       |

| RTC_XTALI     | D9   | VDD_SNVS_CAP | —         | —                                   | RTC_XTALI                         | —            | —                               |

| RTC_XTALO     | C9   | VDD_SNVS_CAP | —         | _                                   | RTC_XTALO                         | —            | —                               |

| SATA_RXM      | A14  | SATA_VPH     | —         | _                                   | SATA_PHY_RX_N                     | —            | —                               |

| SATA_RXP      | B14  | SATA_VPH     | _         | _                                   | SATA_PHY_RX_P                     | —            |                                 |

| SATA_TXM      | B12  | SATA_VPH     | _         | _                                   | SATA_PHY_TX_N                     | —            |                                 |

| SATA_TXP      | A12  | SATA_VPH     | —         | _                                   | SATA_PHY_TX_P                     | -            | —                               |

| SD1_CLK       | D20  | NVCC_SD1     | GPIO      | ALT5                                | GPIO1_IO20                        | Input        | PU (100K)                       |

| SD1_CMD       | B21  | NVCC_SD1     | GPIO      | ALT5                                | GPIO1_IO18                        | Input        | PU (100K)                       |

| SD1_DAT0      | A21  | NVCC_SD1     | GPIO      | ALT5                                | GPIO1_IO16                        | Input        | PU (100K)                       |

| SD1_DAT1      | C20  | NVCC_SD1     | GPIO      | ALT5                                | GPIO1_IO17                        | Input        | PU (100K)                       |

| SD1_DAT2      | E19  | NVCC_SD1     | GPIO      | ALT5                                | GPIO1_IO19                        | Input        | PU (100K)                       |

| SD1_DAT3      | F18  | NVCC_SD1     | GPIO      | ALT5                                | GPIO1_IO21                        | Input        | PU (100K)                       |

| SD2_CLK       | C21  | NVCC_SD2     | GPIO      | ALT5                                | GPIO1_IO10                        | Input        | PU (100K)                       |

| SD2_CMD       | F19  | NVCC_SD2     | GPIO      | ALT5                                | GPIO1_IO11                        | Input        | PU (100K)                       |