Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Core Processore200z2, e200z4Core Size32-Bit Dual-CoreSpeed80MHz/120MHzConnectivityCANbus, Ethernet, I²C, LINbus, SAI, SPI, USB, USB, OTGPeripheralsDMA, LVD, POR, WDTNumber of I/O178Program Memory Size4MB (4M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size512K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 80x10b, 64x12bOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case256-LBGASurface MAPPBGA (17x17)Surface Mount Batter |                            |                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------------|

| Core Size32-Bit Dual-CoreSpeed80MHz/120MHzConnectivityCANbus, Ethernet, IPC, LINbus, SAI, SPI, USB, USB OTGPeripheralsDMA, LVD, POR, WDTNumber of I/O178Program Memory Size4MB (4M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size512K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 80x10b, 64x12bOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case256-LBGAConserter Package256-MAPPBGA (17x17)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Product Status             | Active                                                                 |

| Speed80MHz/120MHzConnectivityCANbus, Ethernet, I²C, LINbus, SAI, SPI, USB, USB OTGPeripheralsDMA, LVD, POR, WDTNumber of I/O178Program Memory Size4MB (4M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size512K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 80x10b, 64x12bOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case256-LBGASupplier Device Package256-MAPPBGA (17x17)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core Processor             | e200z2, e200z4                                                         |

| ConnectivityCANbus, Ethernet, I²C, LINbus, SAI, SPI, USB, USB OTGPeripheralsDMA, LVD, POR, WDTNumber of I/O178Program Memory Size4MB (4M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size512K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 80x10b, 64x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case256-LBGASupplier Device Package256-MAPPBGA (17x17)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Core Size                  | 32-Bit Dual-Core                                                       |

| PeripheralsDMA, LVD, POR, WDTNumber of I/O178Program Memory Size4MB (4M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size512K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 80x10b, 64x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case256-LBGASupplier Device Package256-MAPPBGA (17x17)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Speed                      | 80MHz/120MHz                                                           |

| Number of I/O178Program Memory Size4MB (4M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size512K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 80x10b, 64x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case256-LBGASupplier Device Package256-MAPPBGA (17x17)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, LINbus, SAI, SPI, USB, USB OTG     |

| Program Memory Size4MB (4M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size512K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 80x10b, 64x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case256-LBGASupplier Device Package256-MAPPBGA (17x17)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Peripherals                | DMA, LVD, POR, WDT                                                     |

| Program Memory TypeFLASHEEPROM Size-RAM Size512K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 80x10b, 64x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case256-LBGASupplier Device Package256-MAPPBGA (17x17)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Number of I/O              | 178                                                                    |

| EEPROM Size-RAM Size512K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 80x10b, 64x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case256-LBGASupplier Device Package256-MAPPBGA (17x17)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Program Memory Size        | 4MB (4M x 8)                                                           |

| RAM Size512K × 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 80x10b, 64x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case256-LBGASupplier Device Package256-MAPPBGA (17x17)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Program Memory Type        | FLASH                                                                  |

| Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 80x10b, 64x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case256-LBGASupplier Device Package256-MAPPBGA (17x17)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | EEPROM Size                | -                                                                      |

| Data ConvertersA/D 80x10b, 64x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case256-LBGASupplier Device Package256-MAPPBGA (17x17)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RAM Size                   | 512K x 8                                                               |

| Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case256-LBGASupplier Device Package256-MAPPBGA (17x17)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                              |

| Operating Temperature     -40°C ~ 85°C (TA)       Mounting Type     Surface Mount       Package / Case     256-LBGA       Supplier Device Package     256-MAPPBGA (17x17)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Data Converters            | A/D 80x10b, 64x12b                                                     |

| Mounting Type     Surface Mount       Package / Case     256-LBGA       Supplier Device Package     256-MAPPBGA (17x17)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Oscillator Type            | Internal                                                               |

| Package / Case 256-LBGA<br>Supplier Device Package 256-MAPPBGA (17x17)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Supplier Device Package 256-MAPPBGA (17x17)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Mounting Type              | Surface Mount                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Package / Case             | 256-LBGA                                                               |

| Purchase URL https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5747ck1cmj2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Supplier Device Package    | 256-MAPPBGA (17x17)                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5747ck1cmj2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Table 1. MPC5748G Family Comparison1 (continued)

| Feature                                                   | MPC5747C | MPC5748C   | MPC5746G              | MPC5747G  | MPC5748G |  |  |  |  |  |

|-----------------------------------------------------------|----------|------------|-----------------------|-----------|----------|--|--|--|--|--|

| l <sup>2</sup> C                                          |          |            | 4                     |           |          |  |  |  |  |  |

| SAI/I <sup>2</sup> S                                      | 3        |            |                       |           |          |  |  |  |  |  |

| FXOSC                                                     |          | 8 - 40 MHz |                       |           |          |  |  |  |  |  |

| SXOSC                                                     |          |            | 32 KHz                |           |          |  |  |  |  |  |

| FIRC                                                      |          |            | 16 MHz                |           |          |  |  |  |  |  |

| SIRC                                                      |          |            | 128 KHz               |           |          |  |  |  |  |  |

| FMPLL                                                     |          |            | Yes                   |           |          |  |  |  |  |  |

| LPU                                                       |          |            | Yes                   |           |          |  |  |  |  |  |

| FlexRay 2.1 (dual channel)                                |          |            | Yes, 128 MB           |           |          |  |  |  |  |  |

| MLB150                                                    | (        | )          |                       | 1         |          |  |  |  |  |  |

| USB 2.0 SPH                                               | (        | )          |                       | 1         |          |  |  |  |  |  |

| USB 2.0 OTG                                               | (        | )          |                       | 1         |          |  |  |  |  |  |

| SDHC                                                      |          |            | 1                     |           |          |  |  |  |  |  |

| Ethernet (RMII, MII<br>+ 1588, Muti queue<br>AVB support) |          |            | Up to 2               |           |          |  |  |  |  |  |

| 3 Port L2 Ethernet<br>Switch                              |          |            | Optional              |           |          |  |  |  |  |  |

| CRC                                                       |          |            | 1                     |           |          |  |  |  |  |  |

| MEMU                                                      |          |            | 2                     |           |          |  |  |  |  |  |

| STCU                                                      |          |            | 1                     |           |          |  |  |  |  |  |

| HSM-v2 (security)                                         |          |            | Optional              |           |          |  |  |  |  |  |

| Censorship                                                |          |            | Yes                   |           |          |  |  |  |  |  |

| FCCU                                                      |          |            | 1                     |           |          |  |  |  |  |  |

| Safety level                                              |          | Specifi    | c functions ASIL-B ce | rtifiable |          |  |  |  |  |  |

| User MBIST                                                |          |            | Yes                   |           |          |  |  |  |  |  |

| User LBIST                                                |          |            | Yes                   |           |          |  |  |  |  |  |

| I/O Retention in<br>Standby                               |          |            | Yes                   |           |          |  |  |  |  |  |

| GPIO <sup>5</sup>                                         |          | Up to 2    | 264 GPI and up to 246 | 6 GPIO    |          |  |  |  |  |  |

| Debug                                                     |          |            | JTAGC,                |           |          |  |  |  |  |  |

|                                                           |          |            | cJTAG                 |           |          |  |  |  |  |  |

| Nexus                                                     |          |            | Z4 N3+                |           |          |  |  |  |  |  |

|                                                           |          |            | Z2 N3+                |           |          |  |  |  |  |  |

| Packages                                                  |          |            | 176 LQFP-EP           |           |          |  |  |  |  |  |

|                                                           |          |            | 256 BGA, 324 BGA      |           |          |  |  |  |  |  |

1. Feature set dependent on selected peripheral multiplexing, table shows example. Peripheral availability is package dependent.

2. Based on 125°C ambient operating temperature and subject to full device characterisation.

- 3. Additional SWT included when HSM option selected

- 4. Refer device datasheet and reference manual for information on to timer channel configuration and functions.

Stress beyond the listed maximum values may affect device reliability or cause permanent damage to the device.

| Symbol                                                                        | Parameter                                                                                 | Conditions <sup>1</sup>                                                                 | Min         | Max                                                                                            | Unit |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------|------------------------------------------------------------------------------------------------|------|

| $\begin{array}{c} V_{DD\_HV\_A},V_{DD\_HV\_B},\\ V_{DD\_HV\_C}^2 \end{array}$ |                                                                                           |                                                                                         | -0.3        | 6.0                                                                                            | V    |

| V <sub>DD_HV_FLA</sub> <sup>3, 4</sup>                                        | from an external source in bypass mode)                                                   |                                                                                         | -0.3        | 3.63                                                                                           | V    |

| V <sub>DD_LP_DEC</sub> <sup>5</sup>                                           | Decoupling pin for low power regulators <sup>6</sup>                                      | —                                                                                       | -0.3        | 1.32                                                                                           | V    |

| V <sub>DD_HV_ADC1_REF</sub> <sup>7</sup>                                      | 3.3 V / 5.0 V ADC1 high reference voltage                                                 | _                                                                                       | -0.3        | 6                                                                                              | V    |

| V <sub>DD_HV_ADC0</sub>                                                       | 3.3 V to 5.5V ADC supply voltage                                                          | _                                                                                       | -0.3        | 6.0                                                                                            | V    |

| V <sub>DD_HV_ADC1</sub>                                                       |                                                                                           |                                                                                         |             |                                                                                                |      |

| V <sub>SS_HV_ADC0</sub>                                                       | 3.3V to 5.5V ADC supply ground                                                            | _                                                                                       | -0.1        | 0.1                                                                                            | V    |

| $V_{SS_HV_ADC1}$                                                              |                                                                                           |                                                                                         |             |                                                                                                |      |

| V <sub>DD_LV</sub>                                                            | Core logic supply voltage                                                                 | _                                                                                       | -0.3        | 1.32                                                                                           | V    |

| V <sub>INA</sub>                                                              | Voltage on analog pin with respect to ground (V $_{\rm SS\_HV}$ )                         | _                                                                                       | -0.3        | Min (V <sub>DD_HV_x</sub> ,<br>V <sub>DD_HV_ADCx</sub> ,<br>V <sub>DD_ADCx_REF</sub> )<br>+0.3 | V    |

| V <sub>IN</sub>                                                               | Voltage on any digital pin with respect to ground (V_{SS_HV})                             | Relative to<br>V <sub>DD_HV_A</sub> ,<br>V <sub>DD_HV_B</sub> ,<br>V <sub>DD_HV_C</sub> | -0.3        | V <sub>DD_HV_x</sub> + 0.3                                                                     | V    |

| I <sub>INJPAD</sub>                                                           | Injected input current on any pin during overload condition                               | Always                                                                                  | -5          | 5                                                                                              | mA   |

| I <sub>INJSUM</sub>                                                           | I <sub>INJSUM</sub> Absolute sum of all injected input currents during overload condition |                                                                                         | -50         | 50                                                                                             | mA   |

| T <sub>ramp</sub>                                                             | Supply ramp rate                                                                          | _                                                                                       | 0.5 V / min | 100V/ms                                                                                        | _    |

| T <sub>A</sub> <sup>8</sup>                                                   | Ambient temperature                                                                       | _                                                                                       | -40         | 125                                                                                            | °C   |

| T <sub>STG</sub>                                                              | Storage temperature                                                                       | _                                                                                       | -55         | 165                                                                                            | °C   |

Table 5. Absolute maximum ratings

1. All voltages are referred to VSS\_HV unless otherwise specified

- 2. VDD\_HV\_B and VDD\_HV\_C are common together on the 176 LQFP-EP package.

- 3. VDD\_HV\_FLA must be connected to VDD\_HV\_A when VDD\_HV\_A = 3.3V

- 4. VDD\_HV\_FLA must be disconnected from ANY power sources when VDD\_HV\_A = 5V

- 5. This pin should be decoupled with low ESR 1  $\mu F$  capacitor.

- 6. Not available for input voltage, only for decoupling internal regulators

- 7. 10-bit ADC does not have dedicated reference and its reference is double bonded to 10-bit ADC supply(VDD\_HV\_ADC0).

- 8. T<sub>J</sub>=150°C. Assumes T<sub>A</sub>=125°C

- Assumes maximum θJA. SeeThermal attributes

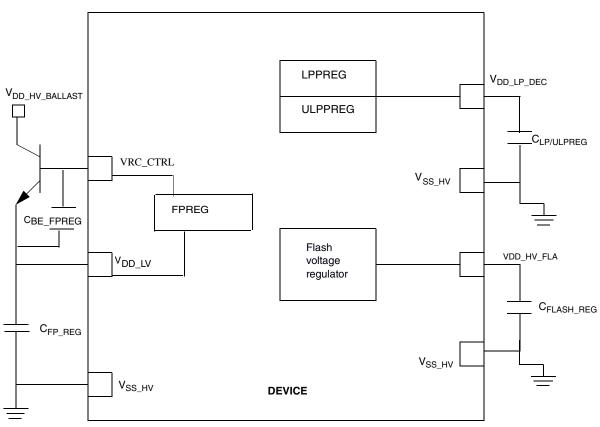

## Figure 2. Voltage regulator capacitance connection

| Table 8. | Voltage regulator | electrical | specifications |

|----------|-------------------|------------|----------------|

|----------|-------------------|------------|----------------|

| Symbol                              | Parameter                                                                         | Conditions                                                                                                       | Min   | Тур              | Max  | Unit |

|-------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------|------------------|------|------|

| C <sub>fp_reg</sub> 1               | External decoupling / stability capacitor                                         | Min, max values shall be granted<br>with respect to tolerance, voltage,<br>temperature, and aging<br>variations. | 1.32  | 2.2 <sup>2</sup> | 3    | μF   |

|                                     | Combined ESR of external capacitor                                                | —                                                                                                                | 0.001 | _                | 0.03 | Ohm  |

| C <sub>lp/ulp_reg</sub>             | External decoupling / stability<br>capacitor for internal low power<br>regulators | Min, max values shall be granted<br>with respect to tolerance, voltage,<br>temperature, and aging<br>variations. | 0.8   | 1                | 1.4  | μF   |

|                                     | Combined ESR of external capacitor                                                | —                                                                                                                | 0.001 | —                | 0.1  | Ohm  |

| C <sub>be_fpreg</sub> <sup>3</sup>  | Capacitor in parallel to base-                                                    | BCP68 and BCP56                                                                                                  |       | 3.3              |      | nF   |

|                                     | emitter                                                                           | MJD31                                                                                                            |       | 4.7              |      |      |

| C <sub>flash_reg</sub> <sup>4</sup> | External decoupling / stability<br>capacitor for internal Flash<br>regulators     | Min, max values shall be granted<br>with respect to tolerance, voltage,<br>temperature, and aging<br>variations. | 1.32  | 2.2              | 3    | μF   |

|                                     | Combined ESR of external capacitor                                                | —                                                                                                                | 0.001 | _                | 0.03 | Ohm  |

Table continues on the next page...

#### General

- 7. In external ballast configuration the following must be ensured during power-up and power-down (Note: If V<sub>DD\_HV\_BALLAST</sub> is supplied from the same source as VDD\_HV\_A this condition is implicitly met):

- During power-up, V<sub>DD\_HV\_BALLAST</sub> must have met the min spec of 2.25V before VDD\_HV\_A reaches the POR\_HV\_RISE min of 2.75V.

- During power-down,  $V_{DD_HV_BALLAST}$  must not drop below the min spec of 2.25V until VDD\_HV\_A is below POR\_HV\_FALL min of 2.7V.

### NOTE

For a typical configuration using an external ballast transistor with separate supply for VDD\_HV\_A and the ballast collector, a bulk storage capacitor (as defined in Table 8) is required on VDD\_HV\_A close to the device pins to ensure a stable supply voltage.

Extra care must be taken if the VDD\_HV\_A supply is also being used to power the external ballast transistor or the device is running in internal regulation mode. In these modes, the inrush current on device Power Up or on exit from Low Power Modes is significant and may cause the VDD\_HV\_A voltage to drop resulting in an LVD reset event. To avoid this, the board layout should be optimized to reduce common trace resistance or additional capacitance at the ballast transistor collector (or VDD\_HV\_A pins in the case of internal regulation mode) is required. NXP recommends that customers simulate the external voltage supply circuitry.

In all circumstances, the voltage on VDD\_HV\_A must be maintained within the specified operating range (see Recommended operating conditions) to prevent LVD events.

## 4.4 Voltage monitor electrical characteristics

| Symbol              | Parameter | State          | Conditions | Configuration             |                 |            | Threshold |       |       | Unit |

|---------------------|-----------|----------------|------------|---------------------------|-----------------|------------|-----------|-------|-------|------|

|                     |           |                |            | Powe<br>r Up <sup>1</sup> | Mas<br>k<br>Opt | Reset Type | Min       | Тур   | Max   | v    |

| V <sub>POR_LV</sub> | LV supply | Fall           | Untrimmed  | Yes                       | No              | Powerup    | 0.930     | 0.979 | 1.028 | V    |

|                     | power on  | reset detector | Trimmed    |                           |                 |            | 0.959     | 0.979 | 0.999 | V    |

|                     |           |                | Untrimmed  |                           |                 |            | 0.980     | 1.029 | 1.078 | V    |

|                     |           |                | Trimmed    |                           |                 |            | 1.009     | 1.029 | 1.049 | V    |

Table 9. Voltage monitor electrical characteristics

Table continues on the next page...

| Symbol                                | Parameter                  | Conditions <sup>1</sup>       | Min | Тур  | Max | Unit |

|---------------------------------------|----------------------------|-------------------------------|-----|------|-----|------|

|                                       |                            | T <sub>a</sub> = 105 °C       | —   | 114  | 206 | mA   |

|                                       |                            | $T_{a} = 125 \ ^{\circ}C^{4}$ | _   | 131  | 277 | mA   |

| I <sub>DD_STOP</sub>                  | STOP mode                  | T <sub>a</sub> = 25 °C        | —   | 11   | _   | mA   |

|                                       | Operating current          | $V_{DD_{LV}} = 1.25 V$        |     |      |     |      |

|                                       |                            | T <sub>a</sub> = 85 °C        | —   | 19.8 | 105 |      |

|                                       |                            | V <sub>DD_LV</sub> = 1.25 V   |     |      |     |      |

|                                       |                            | T <sub>a</sub> = 105 °C       |     | 29   | 145 |      |

|                                       |                            | V <sub>DD_LV</sub> = 1.25 V   |     |      |     |      |

|                                       |                            | $T_a = 125 \text{ °C}^4$      | —   | 45   | 160 |      |

|                                       |                            | $V_{DD_{LV}} = 1.25 V$        |     |      |     |      |

| IDD_HV_ADC_REF <sup>11, 12</sup>      | ADC REF                    | $T_a = 25 \ ^{\circ}C$        | —   | 200  | 400 | μA   |

|                                       | Operating current          | 2 ADCs operating at 80 MHz    |     |      |     |      |

|                                       |                            | $V_{DD_HV_ADC_REF} = 3.6 V$   |     |      |     |      |

|                                       |                            | $T_a = 125 \text{ °C }^4$     | —   | 200  | 400 |      |

|                                       |                            | 2 ADCs operating at 80 MHz    |     |      |     |      |

|                                       |                            | $V_{DD_HV_ADC_REF} = 5.5 V$   |     |      |     |      |

| I <sub>DD_HV_ADCx</sub> <sup>12</sup> | ADC HV                     | T <sub>a</sub> = 25 °C        | _   | 1    | 2   | mA   |

|                                       | Operating current          | ADC operating at 80 MHz       |     |      |     |      |

|                                       |                            | $V_{DD_HV_ADC} = 3.6 V$       |     |      |     |      |

|                                       |                            | $T_{a} = 125 \ ^{\circ}C^{4}$ | _   | 1.2  | 2   |      |

|                                       |                            | ADC operating at 80 MHz       |     |      |     |      |

|                                       |                            | $V_{DD_HV_ADC} = 5.5 V$       |     |      |     |      |

| I <sub>DD_HV_FLASH</sub>              | Flash Operating            | $T_{a} = 125 \ ^{\circ}C^{4}$ | —   | 40   | 45  | mA   |

|                                       | current during read access | 3.3 V supplies                |     |      |     |      |

|                                       |                            | x MHz frequency               |     |      |     |      |

### Table 10. Current consumption characteristics (continued)

- 1. The content of the Conditions column identifies the components that draw the specific current.

- 2. ALL Modules enabled at maximum frequency: 2 x e200Z4 @ 160 MHz, e200Z2 at 80 MHz, Platform @ 160MHz, DMA (SRAM to SRAM), all SRAMs accessed in parallel, Flash access(prefetch is disabled while buffers are enabled), HSM reading from flash at regular intervals (500 pll clock cycles), ENET0 transmitting, MLB transmitting, FlexRay transmitting, USB-SPH transmitting (USB-OTG only clocked), 2 x I2C transmitting (rest clocked), 1 x SAI transmitting (rest clocked), ADC0 converting using BCTU triggers triggered through PIT (other ADC clocked), RTC running, 3 x STM running, 2 x DSPI transmitting (rest clocked), 2 x SPI transmitting (rest clocked), 4 x CAN state machines working(rest clocked), 9 x LINFlexD transmitting (rest clocked), 1 x eMIOS clocked (used OPWFMB mode) (Others clock gated), SDHC,3 x CMP only clocked, FIRC, SIRC, FXOSC, SXOSC, PLL running. All others modules clock gated if not specifically mentioned. I/O supply current excluded.

- 3. Recommended Transistors:MJD31 @ 85°C, 105°C and 125°C.

- 4. Tj=150°C. Assumes Ta=125°C

- Assumes maximum θJA. SeeThermal attributes

- 5. Enabled Modules in Gateway mode: 2 x e200Z4 @160 MHz (Instruction and Data cache enabled), Platform @160MHz, e200Z2 at 80 MHz(Instruction cache enabled), all SRAMs accessed in parallel, Flash access(prefetch is disabled while buffers are enabled), HSM reading from flash at regular intervals(500 pll clock cycles), ENET0 transmitting, MLB transmitting, FlexRay transmitting, USB-SPH Transmitting, USB-OTG clocked, 2 x I2C transmitting, (2 x I2C clock gated), 1 x SAI transmitting (2 x SAI clock gated), ADC0 converting in continuous mode (ADC1 clock gated), PIT clocked, RTC clocked, 3 x STM clocked, 2 x DSPI transmitting(Other DSPS clock gated), 2 x SPI transmitting(Other SPIs clock gated), 4

#### I/O parameters

| lat  | ble 15. | DC electrical specifications @ 3.3 | 3V Range (continued) |

|------|---------|------------------------------------|----------------------|

| abal |         | Baramatar                          | Value                |

| Symbol | Parameter                                              | Va   | Unit          |    |

|--------|--------------------------------------------------------|------|---------------|----|

|        |                                                        | Min  | Мах           |    |

|        | Output Low Voltage <sup>8</sup>                        |      | 0.1 *VDD_HV_x |    |

| loh_f  | Full drive loh <sup>9</sup> (SIUL2_MSCRn[SRC 1:0]= 11) | 18   | 70            | mA |

| lol_f  | Full drive Iol <sup>9</sup> (SIUL2_MSCRn[SRC 1:0]= 11) | 21   | 120           | mA |

| loh_h  | Half drive loh <sup>9</sup> (SIUL2_MSCRn[SRC 1:0]= 10) | 9    | 35            | mA |

| lol_h  | Half drive Iol <sup>9</sup> (SIUL2_MSCRn[SRC 1:0]= 10) | 10.5 | 60            | mA |

- 1. Max power supply ramp rate is 500 V / ms

- 2. Measured when pad=0.69\*VDD\_HV\_x

- 3. Measured when pad=0.49\*VDD\_HV\_x

- 4. Measured when pad = 0 V

- 5. Measured when  $pad = VDD_HV_x$

- 6. Measured when pad is sourcing 2 mA  $\,$

- 7. Measured when pad is sinking 2 mA

- 8. Measured when pad is sinking 1.5 mA

- 9. Ioh/IoI is derived from spice simulations. These values are NOT guaranteed by test.

# 5.3 AC specifications @ 5 V Range

### Table 16. Functional Pad AC Specifications @ 5 V Range

| Symbol                 | Prop. Delay (ns) <sup>1</sup><br>L>H/H>L |           | Rise/Fall Edge (ns) |         | Drive Load (pF) | SIUL2_MSCRn[SRC 1:0] |

|------------------------|------------------------------------------|-----------|---------------------|---------|-----------------|----------------------|

|                        | Min                                      | Max       | Min                 | Max     | 1 +             | MSB,LSB              |

| pad_sr_hv              |                                          | 4.5/4.5   |                     | 1.3/1.2 | 25              | 11                   |

| (output)               |                                          | 6/6       |                     | 2.5/2   | 50              |                      |

| (output)               |                                          | 13/13     |                     | 9/9     | 200             |                      |

|                        |                                          | 5.25/5.25 |                     | 3/2     | 25              | 10                   |

|                        |                                          | 9/8       |                     | 5/4     | 50              |                      |

|                        |                                          | 22/22     |                     | 18/16   | 200             |                      |

|                        |                                          | 27/27     |                     | 13/13   | 50              | 01 <sup>2</sup>      |

|                        |                                          | 40/40     |                     | 24/24   | 200             |                      |

|                        |                                          | 40/40     |                     | 24/24   | 50              | 00 <sup>2</sup>      |

|                        |                                          | 65/65     |                     | 40/40   | 200             |                      |

| pad_i_hv/<br>pad_sr_hv |                                          | 1.5/1.5   |                     | 0.5/0.5 | 0.5             | NA                   |

| (input)                |                                          |           |                     |         |                 |                      |

1. As measured from 50% of core side input to Voh/Vol of the output

2. Slew rate control modes

#### I/O parameters

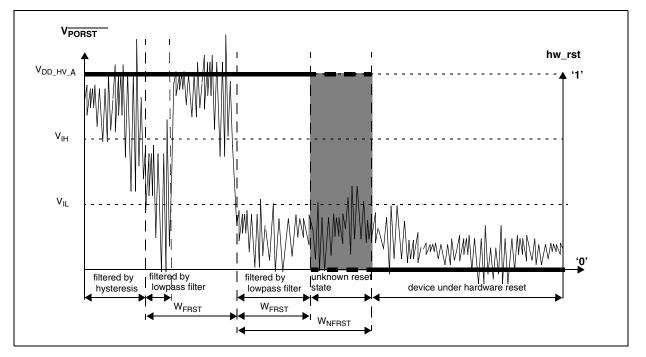

Figure 4. Noise filtering on reset signal

| Symbol              | Parameter                                      | Conditions                                                                                 | Value |     |                              | Unit |

|---------------------|------------------------------------------------|--------------------------------------------------------------------------------------------|-------|-----|------------------------------|------|

|                     |                                                |                                                                                            | Min   | Тур | Max                          | 7    |

| V <sub>IH</sub>     | Input high level TTL (Schmitt Trigger)         | -                                                                                          | 2.0   | —   | V <sub>DD_HV_A</sub><br>+0.4 | V    |

| V <sub>IL</sub>     | Input low level TTL (Schmitt Trigger)          | —                                                                                          | -0.4  | —   | 0.8                          | V    |

| V <sub>HYS</sub>    | Input hysteresis TTL (Schmitt Trigger)         | —                                                                                          | 300   | _   | _                            | mV   |

| V <sub>DD_POR</sub> | Minimum supply for strong pull-down activation | -                                                                                          | —     | _   | 1.2                          | V    |

| I <sub>OL_R</sub>   | Strong pull-down current <sup>1</sup>          | Device under power-on reset<br>$V_{DD_HV_A} = V_{DD_POR}$<br>$V_{OL} = 0.35^*V_{DD_HV_A}$  | 0.2   |     |                              | mA   |

|                     |                                                | Device under power-on reset<br>$V_{DD_HV_A} = V_{DD_POR}$<br>$V_{OL} = 0.35^*V_{DD_HV_IO}$ | 11    | _   |                              | mA   |

| W <sub>FRST</sub>   | RESET input filtered pulse                     | -                                                                                          | —     | —   | 500                          | ns   |

| W <sub>NFRST</sub>  | RESET input not filtered pulse                 | —                                                                                          | 2000  | —   | —                            | ns   |

| ll <sub>WPU</sub> l | Weak pull-up current absolute value            | RESET pin V <sub>IN</sub> = V <sub>DD</sub>                                                | 23    | _   | 82                           | μA   |

1. Strong pull-down is active on PHASE0, PHASE1, PHASE2, and the beginning of PHASE3 for RESET.

# 5.6 PORST electrical specifications

## Table 19. PORST electrical specifications

| Symbol               | Parameter                      |      | Value                       |     |    |

|----------------------|--------------------------------|------|-----------------------------|-----|----|

|                      |                                | Min  | Тур                         | Max |    |

| W <sub>FPORST</sub>  | PORST input filtered pulse     | —    | _                           | 200 | ns |

| W <sub>NFPORST</sub> | PORST input not filtered pulse | 1000 |                             | —   | ns |

| V <sub>IH</sub>      | Input high level               | —    | 0.65 x V <sub>DD_HV_A</sub> | —   | V  |

| V <sub>IL</sub>      | Input low level                | _    | 0.35 x V <sub>DD_HV_A</sub> |     | V  |

# 6 Peripheral operating requirements and behaviours

# 6.1 Analog

## 6.1.1 ADC electrical specifications

The device provides a 12-bit Successive Approximation Register (SAR) Analog-to-Digital Converter.

| Symbol                           | Parameter                                                                             | Conditions                            | Min | Typ <sup>1</sup> | Мах  | Unit |

|----------------------------------|---------------------------------------------------------------------------------------|---------------------------------------|-----|------------------|------|------|

| t <sub>conv</sub>                | Conversion time <sup>4</sup>                                                          | 80 MHz                                | 550 | —                |      | ns   |

| t <sub>total_conv</sub>          | Total Conversion time t <sub>sample</sub> + t <sub>conv</sub> (for standard channels) | 80 MHz                                | 1   | —                | _    | μs   |

|                                  | Total Conversion time t <sub>sample</sub> + t <sub>conv</sub> (for extended channels) |                                       | 1.5 | _                | —    |      |

| C <sub>S</sub>                   | ADC input sampling capacitance                                                        | —                                     | —   | 3                | 5    | pF   |

| C <sub>P1</sub> <sup>5</sup>     | ADC input pin capacitance 1                                                           | —                                     | _   | —                | 5    | pF   |

| C <sub>P2</sub> <sup>5</sup>     | ADC input pin capacitance 2                                                           | —                                     | _   | —                | 0.8  | pF   |

| R <sub>SW1</sub> <sup>5</sup>    | Internal resistance of analog                                                         | V <sub>REF</sub> range = 4.5 to 5.5 V | _   | —                | 0.3  | kΩ   |

|                                  | source                                                                                | $V_{REF}$ range = 3.15 to 3.6 V       | _   | —                | 875  | Ω    |

| R <sub>AD</sub> <sup>5</sup>     | Internal resistance of analog source                                                  | _                                     | —   | —                | 825  | Ω    |

| INL                              | Integral non-linearity                                                                | —                                     | -2  | —                | 2    | LSB  |

| DNL                              | Differential non-linearity                                                            | —                                     | -1  | _                | 1    | LSB  |

| OFS                              | Offset error                                                                          | —                                     | -4  | —                | 4    | LSB  |

| GNE                              | Gain error                                                                            | —                                     | -4  | —                | 4    | LSB  |

| ADC Analog Pad                   | Max leakage (standard channel)                                                        | 150 °C                                | —   | —                | 2500 | nA   |

| (pad going to one<br>ADC)        | Max leakage (standard channel)                                                        | 105 °C <sub>TA</sub>                  | —   | 5                | 250  | nA   |

| ADO)                             | Max positive/negative injection                                                       |                                       | -5  | —                | 5    | mA   |

| TUE <sub>standard/extended</sub> | Total unadjusted error for standard                                                   | Without current injection             | -4  | +/-3             | 4    | LSB  |

| channels                         | channels                                                                              | With current injection <sup>6</sup>   |     | +/-4             |      | LSB  |

| t <sub>recovery</sub>            | STOP mode to Run mode recovery time                                                   |                                       |     |                  | < 1  | μs   |

#### Table 21. ADC conversion characteristics (for 10-bit) (continued)

- Active ADC Input, VinA < [min(ADC\_ADV, IO\_Supply\_A,B,C)]. Violation of this condition would lead to degradation of ADC performance. Please refer to Table: 'Absolute maximum ratings' to avoid damage. Refer to Table: 'Recommended operating conditions' for required relation between IO\_supply\_A, B, C and ADC\_Supply.

- 2. The internally generated clock (known as AD\_clk or ADCK) could be same as the peripheral clock or half of the peripheral clock based on register configuration in the ADC.

- During the sample time the input capacitance C<sub>S</sub> can be charged/discharged by the external source. The internal

resistance of the analog source must allow the capacitance to reach its final voltage level within t<sub>sample</sub>. After the end of the

sample time t<sub>sample</sub>, changes of the analog input voltage have no effect on the conversion result. Values for the sample

clock t<sub>sample</sub> depend on programming.

- 4. This parameter does not include the sample time t<sub>sample</sub>, but only the time for determining the digital result and the time to load the result register with the conversion result.

- 5. See Figure 2

- 6. Current injection condition for ADC channels is defined for an inactive ADC channel (on which conversion is NOT being performed), and this occurs when voltage on the ADC pin exceeds the I/O supply or ground. However, absolute maximum voltage spec on pad input (VINA, see Table: 'Absolute maximum ratings') must be honored to meet TUE spec quoted here

## NOTE

The ADC input pins sit across all three I/O segments, VDD\_HV\_A, VDD\_HV\_B and VDD\_HV\_C.

# 6.2 Clocks and PLL interfaces modules

## 6.2.1 Main oscillator electrical characteristics

This device provides a driver for oscillator in pierce configuration with amplitude control. Controlling the amplitude allows a more sinusoidal oscillation, reducing in this way the EMI. Other benefits arises by reducing the power consumption. This Loop Controlled Pierce (LCP mode) requires good practices to reduce the stray capacitance of traces between crystal and MCU.

An operation in Full Swing Pierce (FSP mode), implemented by an inverter is also available in case of parasitic capacitances and cannot be reduced by using crystal with high equivalent series resistance. For this mode, a special care needs to be taken regarding the serial resistance used to avoid the crystal overdrive.

Other two modes called External (EXT Wave) and disable (OFF mode) are provided. For EXT Wave, the drive is disabled and an external source of clock within CMOS level based in analog oscillator supply can be used. When OFF, EXTAL is pulled down by 240 Kohms resistor and the feedback resistor remains active connecting XTAL through EXTAL by 1M resistor.

## 6.2.4 128 KHz Internal RC oscillator Electrical specifications Table 26. 128 KHz Internal RC oscillator electrical specifications

| Symbol                         | Parameter                 | Condition     | Min | Тур | Max   | Unit  |

|--------------------------------|---------------------------|---------------|-----|-----|-------|-------|

| F <sub>oscu</sub> <sup>1</sup> | Oscillator<br>frequency   | Calibrated    | 119 | 128 | 136.5 | KHz   |

|                                | Temperature<br>dependence |               |     |     | 600   | ppm/C |

|                                | Supply dependence         |               |     |     | 18    | %/V   |

|                                | Supply current            | Clock running |     |     | 2.75  | μΑ    |

|                                |                           | Clock stopped |     |     | 200   | nA    |

1. Vdd=1.2 V, 1.32V, T<sub>a</sub>=-40 C, 125 C

## 6.2.5 PLL electrical specifications

### Table 27. PLL electrical specifications

| Parameter                        | Min       | Тур | Max          | Unit | Comments                                                       |

|----------------------------------|-----------|-----|--------------|------|----------------------------------------------------------------|

| Input Frequency                  | 8         |     | 40           | MHz  |                                                                |

| VCO Frequency Range              | 600       |     | 1280         | MHz  |                                                                |

| Duty Cycle at pllclkout          | 48%       |     | 52%          |      | This specification is guaranteed at PLL IP boundary            |

| Period Jitter                    |           |     | See Table 28 | ps   | NON SSCG mode                                                  |

| TIE                              |           |     | See Table 28 |      | at 960 M Integrated over 1MHz<br>offset not valid in SSCG mode |

| Modulation Depth (Center Spread) | +/- 0.25% |     | +/- 3.0%     |      |                                                                |

| Modulation Frequency             |           |     | 32           | KHz  |                                                                |

| Lock Time                        |           |     | 60           | μs   | Calibration mode                                               |

Table 28. Jitter calculation

| Type of jitter                        | Jitter due to<br>Supply<br>Noise (ps)<br>J <sub>SN</sub> <sup>1</sup> | Jitter due to<br>Fractional Mode<br>(ps) J <sub>SDM</sub> <sup>2</sup> | Jitter due to<br>Fractional Mode<br>J <sub>SSCG</sub> (ps) <sup>3</sup> | 1 Sigma<br>Random<br>Jitter J <sub>RJ</sub><br>(ps) <sup>4</sup> | Total Period Jitter (ps)                                                                      |