Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| C, LINbus, SAI, SPI, USB, USB OTG |

|-----------------------------------|

| т                                 |

|                                   |

|                                   |

|                                   |

|                                   |

|                                   |

|                                   |

|                                   |

|                                   |

|                                   |

|                                   |

|                                   |

| Pad                               |

| ad                                |

|                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Timer

- 16 Periodic Interrupt Timers (PITs)

- Three System Timer Module (STM)

- Four Software WatchDog Timers (SWT)

- 96 Configurable Enhanced Modular Input Output Subsystem (eMIOS) channels

- Device/board boundary Scan testing supported with per Joint Test Action Group (JTAG) of IEEE (IEEE 1149.1) and 1149.7 (cJTAG)

- Security

- Hardware Security Module (HSMv2)

- Password and Device Security (PASS and TDM) supporting advanced censorship and life-cycle management

- One Fault Collection and Control Unit (FCCU) to collect faults and issue interrupts

- Functional Safety

- ISO26262 ASIL compliance

- Multiple operating modes

- Includes enhanced low power operation

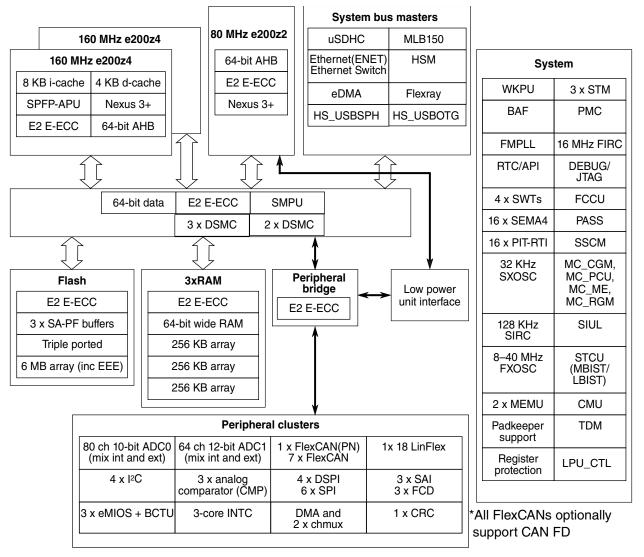

# 1 Block diagram

Figure 1. MPC5748G block diagram

# 2 Family comparison

The following table provides a summary of the different members of the MPC5748G family and their proposed features. This information is intended to provide an understanding of the range of functionality offered by this family. For full details of all of the family derivatives please contact your marketing representative.

### NOTE

All optional features (Flash memory, RAM, Peripherals) start with lowest peripheral number (for example: STM\_0) or memory address and end at the highest available peripheral number or memory address (for example: MPC574xC have 2 STM, ending with STM\_1).

| Feature                             | MPC5747C     | MPC5748C                                          | MPC5746G              | MPC5747G       | MPC5748G    |  |  |

|-------------------------------------|--------------|---------------------------------------------------|-----------------------|----------------|-------------|--|--|

| CPUs                                | e200z4       | e200z4                                            | e200z4                | e200z4         | e200z4      |  |  |

|                                     | e200z2       | e200z2                                            | e200z4                | e200z4         | e200z4      |  |  |

|                                     |              |                                                   | e200z2                | e200z2         | e200z2      |  |  |

| FPU                                 | e200z4       | e200z4                                            | e200z4                | e200z4         | e200z4      |  |  |

|                                     |              |                                                   | e200z4                | e200z4         | e200z4      |  |  |

| Maximum                             | 160MHz (z4)  | 160MHz (z4)                                       | 160MHz (z4)           | 160MHz (z4)    | 160MHz (z4) |  |  |

| Operating<br>Frequency <sup>2</sup> | 80MHz (z2)   | 80MHz (z2)                                        | 160MHz (z4)           | 160MHz (z4)    | 160MHz (z4) |  |  |

| Frequency                           |              |                                                   | 80MHz (z2)            | 80MHz (z2)     | 80MHz (z2)  |  |  |

| Flash memory                        | 4 MB         | 6 MB                                              | 3 MB                  | 4 MB           | 6 MB        |  |  |

| EEPROM support                      | 32 KB to 128 | 32 KB to 128 KB emulated 32 KB to 192 KB emulated |                       |                |             |  |  |

| RAM                                 | 512 KB       |                                                   | 768                   | KB             |             |  |  |

| ECC                                 |              | End to End                                        |                       |                |             |  |  |

| SMPU                                | 24 e         | 24 entry 32 entry                                 |                       |                |             |  |  |

| DMA                                 |              | 32 channels                                       |                       |                |             |  |  |

| 10-bit ADC                          |              |                                                   | 48 Standard channels  | 6              |             |  |  |

|                                     |              |                                                   | 32 External channels  |                |             |  |  |

| 12-bit ADC                          |              |                                                   | 16 Precision channels | 6              |             |  |  |

|                                     |              |                                                   | 16 Standard channels  | 3              |             |  |  |

|                                     |              |                                                   | 32 External channels  |                |             |  |  |

| AnalogComparator                    |              |                                                   | 3                     |                |             |  |  |

| BCTU                                |              |                                                   | 1                     |                |             |  |  |

| SWT                                 | 2            | 2                                                 |                       | 4 <sup>3</sup> |             |  |  |

| STM                                 | 2            | 2                                                 |                       | 3              |             |  |  |

| PIT-RTI                             |              |                                                   | 16 channels PIT       |                |             |  |  |

|                                     |              |                                                   | 1 channels RTI        |                |             |  |  |

| RTC/API                             |              |                                                   | Yes                   |                |             |  |  |

| Total Timer I/O <sup>4</sup>        |              |                                                   | 96 channels           |                |             |  |  |

|                                     | 16-bits      |                                                   |                       |                |             |  |  |

| LINFlexD                            | 1 M/S        | 15 M                                              |                       | 1 M/S, 17 M    |             |  |  |

| FlexCAN                             |              | 8 wit                                             | h optional CAN FD su  | ipport         |             |  |  |

| DSPI/SPI                            |              |                                                   | 4 x DSPI              |                |             |  |  |

|                                     |              |                                                   | 6 x SPI               |                |             |  |  |

### Table 1. MPC5748G Family Comparison1

Table continues on the next page...

### Table 1. MPC5748G Family Comparison1 (continued)

| Feature                                                   | MPC5747C                         | MPC5748C | MPC5746G              | MPC5747G  | MPC5748G |  |  |  |

|-----------------------------------------------------------|----------------------------------|----------|-----------------------|-----------|----------|--|--|--|

| l <sup>2</sup> C                                          |                                  |          | 4                     |           |          |  |  |  |

| SAI/I <sup>2</sup> S                                      |                                  |          | 3                     |           |          |  |  |  |

| FXOSC                                                     | 8 - 40 MHz                       |          |                       |           |          |  |  |  |

| SXOSC                                                     |                                  | 32 KHz   |                       |           |          |  |  |  |

| FIRC                                                      |                                  |          | 16 MHz                |           |          |  |  |  |

| SIRC                                                      |                                  |          | 128 KHz               |           |          |  |  |  |

| FMPLL                                                     |                                  |          | Yes                   |           |          |  |  |  |

| LPU                                                       |                                  |          | Yes                   |           |          |  |  |  |

| FlexRay 2.1 (dual channel)                                |                                  |          | Yes, 128 MB           |           |          |  |  |  |

| MLB150                                                    | (                                | )        |                       | 1         |          |  |  |  |

| USB 2.0 SPH                                               | (                                | )        |                       | 1         |          |  |  |  |

| USB 2.0 OTG                                               | (                                | )        |                       | 1         |          |  |  |  |

| SDHC                                                      |                                  |          | 1                     |           |          |  |  |  |

| Ethernet (RMII, MII<br>+ 1588, Muti queue<br>AVB support) | Up to 2                          |          |                       |           |          |  |  |  |

| 3 Port L2 Ethernet<br>Switch                              |                                  |          | Optional              |           |          |  |  |  |

| CRC                                                       |                                  |          | 1                     |           |          |  |  |  |

| MEMU                                                      |                                  |          | 2                     |           |          |  |  |  |

| STCU                                                      |                                  |          | 1                     |           |          |  |  |  |

| HSM-v2 (security)                                         |                                  |          | Optional              |           |          |  |  |  |

| Censorship                                                |                                  |          | Yes                   |           |          |  |  |  |

| FCCU                                                      |                                  |          | 1                     |           |          |  |  |  |

| Safety level                                              |                                  | Specifi  | c functions ASIL-B ce | rtifiable |          |  |  |  |

| User MBIST                                                |                                  |          | Yes                   |           |          |  |  |  |

| User LBIST                                                |                                  |          | Yes                   |           |          |  |  |  |

| I/O Retention in<br>Standby                               |                                  |          | Yes                   |           |          |  |  |  |

| GPIO <sup>5</sup>                                         | Up to 264 GPI and up to 246 GPIO |          |                       |           |          |  |  |  |

| Debug                                                     |                                  |          | JTAGC,                |           |          |  |  |  |

|                                                           |                                  |          | cJTAG                 |           |          |  |  |  |

| Nexus                                                     |                                  |          | Z4 N3+                |           |          |  |  |  |

|                                                           |                                  |          | Z2 N3+                |           |          |  |  |  |

| Packages                                                  |                                  |          | 176 LQFP-EP           |           |          |  |  |  |

|                                                           |                                  |          | 256 BGA, 324 BGA      |           |          |  |  |  |

1. Feature set dependent on selected peripheral multiplexing, table shows example. Peripheral availability is package dependent.

2. Based on 125°C ambient operating temperature and subject to full device characterisation.

- 3. Additional SWT included when HSM option selected

- 4. Refer device datasheet and reference manual for information on to timer channel configuration and functions.

| Start Address | End Address | Flash block      | RWW | MPC5747C      | MPC5746G  |

|---------------|-------------|------------------|-----|---------------|-----------|

|               |             |                  |     | MPC5748C      | MPC5747G  |

|               |             |                  |     |               | MPC5748G  |

| 0x00F90000    | 0x00F93FFF  | 16 KB data Flash | 2   | available     | available |

| 0x00F94000    | 0x00F97FFF  | 16 KB data Flash | 2   | available     | available |

| 0x00F98000    | 0x00F9BFFF  | 16 KB data Flash | 2   | available     | available |

| 0x00F9C000    | 0x00F9FFFF  | 16 KB data Flash | 2   | available     | available |

| 0x00FA0000    | 0x00FA3FFF  | 16 KB data Flash | 3   | available     | available |

| 0x00FA4000    | 0x00FA7FFF  | 16 KB data Flash | 3   | available     | available |

| 0x00FA8000    | 0x00FABFFF  | 16 KB data Flash | 3   | available     | available |

| 0x00FAC000    | 0x00FAFFFF  | 16 KB data Flash | 3   | available     | available |

| 0x00FB0000    | 0x00FB7FFF  | 32 KB data Flash | 2   | not available | available |

| 0x00FB8000    | 0x00FBFFFF  | 32 KB data flash | 3   | not available | available |

Table 3.

MPC5748G Family Comparison - NVM Memory Map 2

Table 4.

MPC5748G Family Comparison - RAM Memory Map

| Start Address | End Address | Allocated size [KB] | MPC5747C      | MPC5748C<br>MPC5746G<br>MPC5747G<br>MPC5748G |

|---------------|-------------|---------------------|---------------|----------------------------------------------|

| 0x4000000     | 0x40001FFF  | 8                   | available     | available                                    |

| 0x40002000    | 0x4000FFFF  | 56                  | available     | available                                    |

| 0x40010000    | 0x4001FFFF  | 64                  | available     | available                                    |

| 0x40020000    | 0x4003FFFF  | 128                 | available     | available                                    |

| 0x40040000    | 0x4007FFFF  | 256                 | available     | available                                    |

| 0x40080000    | 0x400BFFFF  | 256                 | not available | available                                    |

# 3 Ordering parts

# 3.1 Determining valid orderable parts

To determine the orderable part numbers for this device, go to www.nxp.com and perform a part number search for the following device number: MPC5748G.

# 4.3 Voltage regulator electrical characteristics

The voltage regulator is composed of the following blocks:

- Choice of generating supply voltage for the core area.

- Control of external NPN ballast transistor

- Connecting an external 1.25 V (nominal) supply directly without the NPN ballast

- Internal generation of the 3.3 V flash supply when device connected in 5V applications

- External bypass of the 3.3 V flash regulator when device connected in 3.3V applications

- Low voltage detector low threshold (LVD\_IO\_A\_LO) for V<sub>DD\_HV\_IO\_A supply</sub>

- Low voltage detector high threshold (LVD\_IO\_A\_Hi) for V<sub>DD\_HV\_IO\_A</sub> supply

- Various low voltage detectors (LVD\_LV\_x)

- High voltage detector (HVD\_LV\_cold) for 1.2 V digital core supply (VDD\_LV)

- Power on Reset (POR\_LV) for 1.25 V digital core supply (VDD\_LV)

- Power on Reset (POR\_HV) for 3.3 V to 5 V supply (VDD\_HV\_A)

The following bipolar transistors<sup>1</sup> are supported, depending on the device performance requirements. As a minimum the following must be considered when determining the most appropriate solution to maintain the device under its maximum power dissipation capability: current, ambient temperature, mounting pad area, duty cycle and frequency for Idd, collector voltage, etc

<sup>1.</sup> BCP56, MCP68 and MJD31are guaranteed ballasts.

| Symbol                                | Parameter                  | Conditions <sup>1</sup>       | Min | Тур  | Max | Unit |

|---------------------------------------|----------------------------|-------------------------------|-----|------|-----|------|

|                                       |                            | T <sub>a</sub> = 105 °C       | —   | 114  | 206 | mA   |

|                                       |                            | $T_{a} = 125 \ ^{\circ}C^{4}$ | _   | 131  | 277 | mA   |

| I <sub>DD_STOP</sub>                  | STOP mode                  | T <sub>a</sub> = 25 °C        | —   | 11   | _   | mA   |

|                                       | Operating current          | $V_{DD_{LV}} = 1.25 V$        |     |      |     |      |

|                                       |                            | T <sub>a</sub> = 85 °C        | —   | 19.8 | 105 |      |

|                                       |                            | V <sub>DD_LV</sub> = 1.25 V   |     |      |     |      |

|                                       |                            | T <sub>a</sub> = 105 °C       |     | 29   | 145 |      |

|                                       |                            | V <sub>DD_LV</sub> = 1.25 V   |     |      |     |      |

|                                       |                            | $T_a = 125 \text{ °C}^4$      | —   | 45   | 160 |      |

|                                       |                            | $V_{DD_{LV}} = 1.25 V$        |     |      |     |      |

| IDD_HV_ADC_REF <sup>11, 12</sup>      | ADC REF                    | $T_a = 25 \ ^{\circ}C$        | _   | 200  | 400 | μA   |

|                                       | Operating current          | 2 ADCs operating at 80 MHz    |     |      |     |      |

|                                       |                            | $V_{DD_HV_ADC_REF} = 3.6 V$   |     |      |     |      |

|                                       |                            | $T_a = 125 \text{ °C }^4$     | —   | 200  | 400 |      |

|                                       |                            | 2 ADCs operating at 80 MHz    |     |      |     |      |

|                                       |                            | $V_{DD_HV_ADC_REF} = 5.5 V$   |     |      |     |      |

| I <sub>DD_HV_ADCx</sub> <sup>12</sup> | ADC HV                     | T <sub>a</sub> = 25 °C        | _   | 1    | 2   | mA   |

|                                       | Operating current          | ADC operating at 80 MHz       |     |      |     |      |

|                                       |                            | $V_{DD_HV_ADC} = 3.6 V$       |     |      |     |      |

|                                       |                            | $T_{a} = 125 \ ^{\circ}C^{4}$ | _   | 1.2  | 2   |      |

|                                       |                            | ADC operating at 80 MHz       |     |      |     |      |

|                                       |                            | $V_{DD_HV_ADC} = 5.5 V$       |     |      |     |      |

| I <sub>DD_HV_FLASH</sub>              | Flash Operating            | $T_{a} = 125 \ ^{\circ}C^{4}$ | —   | 40   | 45  | mA   |

|                                       | current during read access | 3.3 V supplies                |     |      |     |      |

|                                       |                            | x MHz frequency               |     |      |     |      |

#### Table 10. Current consumption characteristics (continued)

- 1. The content of the Conditions column identifies the components that draw the specific current.

- 2. ALL Modules enabled at maximum frequency: 2 x e200Z4 @ 160 MHz, e200Z2 at 80 MHz, Platform @ 160MHz, DMA (SRAM to SRAM), all SRAMs accessed in parallel, Flash access(prefetch is disabled while buffers are enabled), HSM reading from flash at regular intervals (500 pll clock cycles), ENET0 transmitting, MLB transmitting, FlexRay transmitting, USB-SPH transmitting (USB-OTG only clocked), 2 x I2C transmitting (rest clocked), 1 x SAI transmitting (rest clocked), ADC0 converting using BCTU triggers triggered through PIT (other ADC clocked), RTC running, 3 x STM running, 2 x DSPI transmitting (rest clocked), 2 x SPI transmitting (rest clocked), 4 x CAN state machines working(rest clocked), 9 x LINFlexD transmitting (rest clocked), 1 x eMIOS clocked (used OPWFMB mode) (Others clock gated), SDHC,3 x CMP only clocked, FIRC, SIRC, FXOSC, SXOSC, PLL running. All others modules clock gated if not specifically mentioned. I/O supply current excluded.

- 3. Recommended Transistors:MJD31 @ 85°C, 105°C and 125°C.

- 4. Tj=150°C. Assumes Ta=125°C

- Assumes maximum θJA. SeeThermal attributes

- 5. Enabled Modules in Gateway mode: 2 x e200Z4 @160 MHz (Instruction and Data cache enabled), Platform @160MHz, e200Z2 at 80 MHz(Instruction cache enabled), all SRAMs accessed in parallel, Flash access(prefetch is disabled while buffers are enabled), HSM reading from flash at regular intervals(500 pll clock cycles), ENET0 transmitting, MLB transmitting, FlexRay transmitting, USB-SPH Transmitting, USB-OTG clocked, 2 x I2C transmitting, (2 x I2C clock gated), 1 x SAI transmitting (2 x SAI clock gated), ADC0 converting in continuous mode (ADC1 clock gated), PIT clocked, RTC clocked, 3 x STM clocked, 2 x DSPI transmitting(Other DSPS clock gated), 2 x SPI transmitting(Other SPIs clock gated), 4

# 6.2 Clocks and PLL interfaces modules

## 6.2.1 Main oscillator electrical characteristics

This device provides a driver for oscillator in pierce configuration with amplitude control. Controlling the amplitude allows a more sinusoidal oscillation, reducing in this way the EMI. Other benefits arises by reducing the power consumption. This Loop Controlled Pierce (LCP mode) requires good practices to reduce the stray capacitance of traces between crystal and MCU.

An operation in Full Swing Pierce (FSP mode), implemented by an inverter is also available in case of parasitic capacitances and cannot be reduced by using crystal with high equivalent series resistance. For this mode, a special care needs to be taken regarding the serial resistance used to avoid the crystal overdrive.

Other two modes called External (EXT Wave) and disable (OFF mode) are provided. For EXT Wave, the drive is disabled and an external source of clock within CMOS level based in analog oscillator supply can be used. When OFF, EXTAL is pulled down by 240 Kohms resistor and the feedback resistor remains active connecting XTAL through EXTAL by 1M resistor.

#### Memory interfaces

- 2. This jitter component is added when the PLL is working in the fractional mode.

- 3. This jitter component is added when the PLL is working in the Spread Spectrum Mode. Else it is 0.

- 4. The value of N is dependent on the accuracy requirement of the application. See Percentage of sample exceeding specified value of jitter table

Table 29. Percentage of sample exceeding specified value of jitter

| N | Percentage of samples exceeding specified value of jitter<br>(%) |

|---|------------------------------------------------------------------|

| 1 | 31.73                                                            |

| 2 | 4.55                                                             |

| 3 | 0.27                                                             |

| 4 | 6.30 × 1e-03                                                     |

| 5 | 5.63 × 1e-05                                                     |

| 6 | 2.00 × 1e-07                                                     |

| 7 | 2.82 × 1e-10                                                     |

### 6.3 Memory interfaces

### 6.3.1 Flash memory program and erase specifications

NOTE

All timing, voltage, and current numbers specified in this section are defined for a single embedded flash memory within an SoC, and represent average currents for given supplies and operations.

Table 30 shows the estimated Program/Erase times.

Symbol Characteristic<sup>1</sup> Typ<sup>2</sup> Factory **Field Update** Unit Programming<sup>3, 4</sup> Initial Typical Lifetime Max<sup>6</sup> Initial Max, Full End of Max Temp Life<sup>5</sup> 20°C ≤T<sub>A</sub> -40°C ≤T<sub>J</sub> ≤ 1,000 -40°C ≤T,J ≤ 250,000 ≤30°C ≤150°C ≤150°C cycles cycles 500 Doubleword (64 bits) program time 43 100 150 55 μs t<sub>dwpgm</sub> 200 300 108 500 Page (256 bits) program time 73 μs t<sub>ppgm</sub> Quad-page (1024 bits) program 268 800 1,200 396 2,000 μs t<sub>qppgm</sub> time 16 KB Block erase time 168 290 320 250 1,000 ms t<sub>16kers</sub> 40 1,000 16 KB Block program time 34 45 50 ms t<sub>16kpgm</sub>

Table 30. Flash memory program and erase specifications

Table continues on the next page...

| Symbol               | Characteristic                                                                                                                                                                                                                        | Min                                              | Typical                                        | Max                                              | Units |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------------------------|--------------------------------------------------|-------|

| t <sub>psus</sub>    | Time from setting the MCR-PSUS bit until MCR-DONE bit is set to a 1.                                                                                                                                                                  | _                                                | 9.4<br>plus four<br>system<br>clock<br>periods | 11.5<br>plus four<br>system<br>clock<br>periods  | μs    |

| t <sub>esus</sub>    | Time from setting the MCR-ESUS bit until MCR-DONE bit is set to a 1.                                                                                                                                                                  | _                                                | 16<br>plus four<br>system<br>clock<br>periods  | 20.8<br>plus four<br>system<br>clock<br>periods  | μs    |

| t <sub>res</sub>     | Time from clearing the MCR-ESUS or PSUS bit with EHV = 1 until DONE goes low.                                                                                                                                                         | _                                                | _                                              | 100                                              | ns    |

| t <sub>done</sub>    | Time from 0 to 1 transition on the MCR-EHV bit initiating a program/erase until the MCR-DONE bit is cleared.                                                                                                                          |                                                  | —                                              | 5                                                | ns    |

| t <sub>dones</sub>   | Time from 1 to 0 transition on the MCR-EHV bit aborting a program/erase until the MCR-DONE bit is set to a 1.                                                                                                                         | _                                                | 16<br>plus four<br>system<br>clock<br>periods  | 20.8<br>plus four<br>system<br>clock<br>periods  | μs    |

| t <sub>drcv</sub>    | Time to recover once exiting low power mode.                                                                                                                                                                                          | 16<br>plus seven<br>system<br>clock<br>periods.  |                                                | 45<br>plus seven<br>system<br>clock<br>periods   | μs    |

| t <sub>aistart</sub> | Time from 0 to 1 transition of UT0-AIE initiating a Margin Read<br>or Array Integrity until the UT0-AID bit is cleared. This time also<br>applies to the resuming from a suspend or breakpoint by<br>clearing AISUS or clearing NAIBP | _                                                | _                                              | 5                                                | ns    |

| t <sub>aistop</sub>  | Time from 1 to 0 transition of UT0-AIE initiating an Array<br>Integrity abort until the UT0-AID bit is set. This time also applies<br>to the UT0-AISUS to UT0-AID setting in the event of a Array<br>Integrity suspend request.       |                                                  |                                                | 80<br>plus fifteen<br>system<br>clock<br>periods | ns    |

| t <sub>mrstop</sub>  | Time from 1 to 0 transition of UT0-AIE initiating a Margin Read<br>abort until the UT0-AID bit is set. This time also applies to the<br>UT0-AISUS to UT0-AID setting in the event of a Margin Read<br>suspend request.                | 10.36<br>plus four<br>system<br>clock<br>periods |                                                | 20.42<br>plus four<br>system<br>clock<br>periods | μs    |

# 6.3.5 Flash memory AC timing specifications

Table 33. Flash memory AC timing specifications

## 6.3.6 Flash read wait state and address pipeline control settings

The following table describes the recommended RWSC and APC settings at various operating frequencies based on specified intrinsic flash access times of the flash module controller array at 125 °C.

| Flash frequency             | RWSC setting | APC setting |

|-----------------------------|--------------|-------------|

| 0 MHz < fFlash <= 33 MHz    | 0            | 0           |

| 33 MHz < fFlash <= 100 MHz  | 2            | 1           |

| 100 MHz < fFlash <= 133 MHz | 3            | 1           |

| 133 MHz < fFlash <= 160 MHz | 4            | 1           |

Table 34.

Flash Read Wait State and Address Pipeline Control Combinations

# 6.4 Communication interfaces

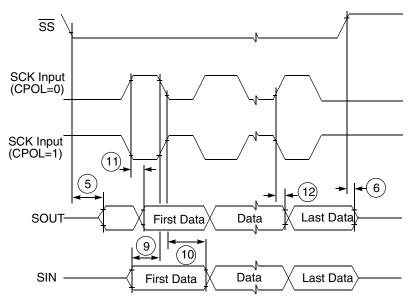

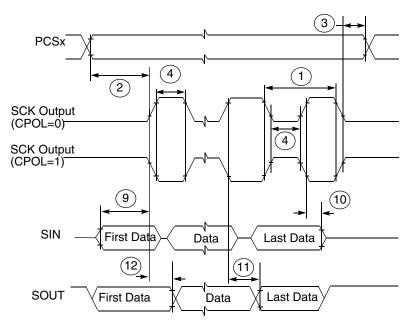

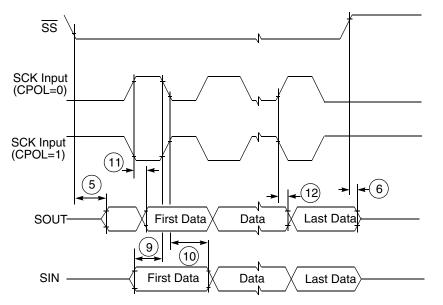

## 6.4.1 DSPI timing

Table 35. DSPI electrical specifications

| No | Symbol            | Parameter               | Conditions                                          | High Spe                 | eed Mode                 | low Spe        | ed mode | Unit |

|----|-------------------|-------------------------|-----------------------------------------------------|--------------------------|--------------------------|----------------|---------|------|

|    |                   |                         |                                                     | Min                      | Max                      | Min            | Мах     | 1    |

| 1  | t <sub>SCK</sub>  | DSPI cycle              | Master (MTFE = 0)                                   | 25                       | —                        | 50             | —       | ns   |

|    |                   | time                    | Slave (MTFE = 0)                                    | 40                       | _                        | 60             | —       | 1    |

| 2  | t <sub>csc</sub>  | PCS to SCK delay        |                                                     | 16                       |                          | _              | _       | ns   |

| 3  | t <sub>ASC</sub>  | After SCK delay         | —                                                   | 16                       |                          | _              | _       | ns   |

| 4  | t <sub>SDC</sub>  | SCK duty<br>cycle       | —                                                   | t <sub>SCK</sub> /2 - 10 | t <sub>SCK</sub> /2 + 10 | _              | _       | ns   |

| 5  | t <sub>A</sub>    | Slave access time       | SS active to SOUT valid                             | —                        | 40                       | _              | _       | ns   |

| 6  | t <sub>DIS</sub>  | Slave SOUT disable time | <sub>SS</sub> inactive to SOUT<br>High-Z or invalid | —                        | 10                       | —              | _       | ns   |

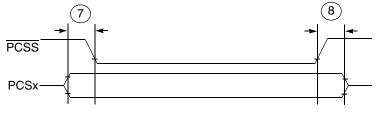

| 7  | t <sub>PCSC</sub> | PCSx to<br>PCSS time    | —                                                   | 13                       | —                        | _              | _       | ns   |

| 8  | t <sub>PASC</sub> | PCSS to<br>PCSx time    |                                                     | 13                       |                          | _              | _       | ns   |

| 9  | t <sub>SUI</sub>  | Data setup              | Master (MTFE = 0)                                   | NA                       | _                        | 20             | —       | ns   |

|    |                   | time for<br>inputs      | Slave                                               | 2                        | —                        | 2              | —       |      |

|    |                   | inputo                  | Master (MTFE = 1,<br>CPHA = 0)                      | 15                       | —                        | 8 <sup>1</sup> | —       |      |

Table continues on the next page ...

**Communication interfaces**

Figure 11. DSPI classic SPI timing — slave, CPHA = 1

Figure 12. DSPI modified transfer format timing — master, CPHA = 0

FlexRay electrical specifications

Figure 15. DSPI modified transfer format timing — slave, CPHA = 1

Figure 16. DSPI PCS strobe (PCSS) timing

## 6.4.2 FlexRay electrical specifications

### 6.4.2.1 FlexRay timing

This section provides the FlexRay Interface timing characteristics for the input and output signals. It should be noted that these are recommended numbers as per the FlexRay EPL v3.0 specification, and subject to change per the final timing analysis of the device.

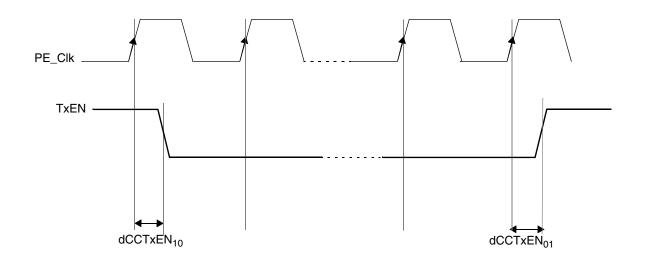

6.4.2.3 TxD

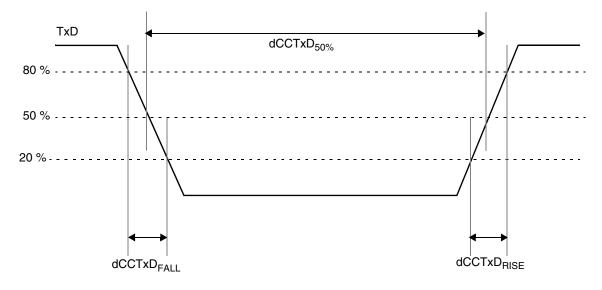

Figure 19. TxD Signal

| Name                                                   | Description <sup>1</sup>                                   | Min   | Max            | Unit |

|--------------------------------------------------------|------------------------------------------------------------|-------|----------------|------|

| dCCT <sub>xAsym</sub>                                  | Asymmetry of sending CC @ 25 pF load (=dCCTxD50% - 100 ns) | -2.45 | 2.45           | ns   |

| dCCTxD <sub>RISE25</sub> +dCCTx<br>D <sub>FALL25</sub> | Sum of Rise and Fall time of TxD signal at the output      | —     | 9 <sup>2</sup> | ns   |

Table continues on the next page...

| Name                 | Description <sup>1</sup>                                                               | Min | Max | Unit |

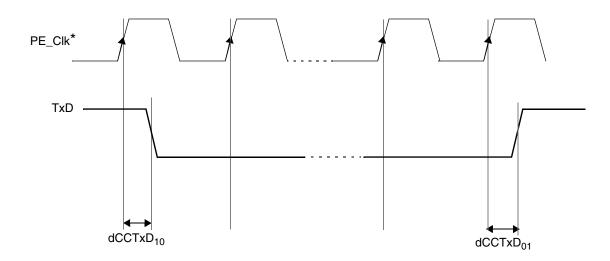

|----------------------|----------------------------------------------------------------------------------------|-----|-----|------|

| dCCTxD <sub>01</sub> | Sum of delay between Clk to Q of the last FF and the final output buffer, rising edge  | —   | 25  | ns   |

| dCCTxD <sub>10</sub> | Sum of delay between Clk to Q of the last FF and the final output buffer, falling edge | _   | 25  | ns   |

### Table 39. TxD output characteristics (continued)

1. All parameters specified for  $V_{DD_HV_IOx} = 3.3 \text{ V} - 5\%$ , +±10%, TJ = -40 °C / 150 °C, TxD pin load maximum 25 pF. 2. For 3.3 V ± 10% operation, this specification is 10 ns.

\*FlexRay Protocol Engine Clock

### Figure 20. TxD Signal propagation delays

#### 6.4.2.4 **RxD**

| Name                 | Description <sup>1</sup>                                                             | Min | Мах | Unit |

|----------------------|--------------------------------------------------------------------------------------|-----|-----|------|

| C_CCRxD              | Input capacitance on<br>RxD pin                                                      | —   | 7   | pF   |

| uCCLogic_1           | Threshold for detecting logic high                                                   | 35  | 70  | %    |

| uCCLogic_0           | Threshold for detecting<br>logic low                                                 | 30  | 65  | %    |

| dCCRxD <sub>01</sub> | Sum of delay from<br>actual input to the D<br>input of the first FF,<br>rising edge  | _   | 10  | ns   |

| dCCRxD <sub>10</sub> | Sum of delay from<br>actual input to the D<br>input of the first FF,<br>falling edge | _   | 10  | ns   |

# 6.4.4 Ethernet switching specifications

The following timing specs are defined at the chip I/O pin and must be translated appropriately to arrive at timing specs/constraints for the physical interface.

### 6.4.4.1 MII signal switching specifications

The following timing specs meet the requirements for MII style interfaces for a range of transceiver devices.

### NOTE

ENET0 supports the following xMII interfaces: MII, MII\_Lite and RMII. ENET1 supports the following xMII interfaces: MII\_Lite.

### NOTE

It is only possible to use ENET0 and ENET1 simultaneously when both are configured for MII\_Lite.

### NOTE

In certain pinout configurations ENET1 MII-Lite signals can be across multiple VDD\_HV\_A/B/C domains. If these configuration are used, VDD\_HV IO domains need to be at the same voltage (for example: 3.3V)

| Symbol | Description                           | Min. | Max. | Unit   |

|--------|---------------------------------------|------|------|--------|

| _      | RXCLK frequency                       | —    | 25   | MHz    |

| MII1   | RXCLK pulse width high                | 35%  | 65%  | RXCLK  |

|        |                                       |      |      | period |

| MII2   | RXCLK pulse width low                 | 35%  | 65%  | RXCLK  |

|        |                                       |      |      | period |

| MII3   | RXD[3:0], RXDV, RXER to RXCLK setup   | 5    | _    | ns     |

| MII4   | RXCLK to RXD[3:0], RXDV, RXER hold    | 5    | _    | ns     |

| _      | TXCLK frequency                       | —    | 25   | MHz    |

| MII5   | TXCLK pulse width high                | 35%  | 65%  | TXCLK  |

|        |                                       |      |      | period |

| MII6   | TXCLK pulse width low                 | 35%  | 65%  | TXCLK  |

|        |                                       |      |      | period |

| MII7   | TXCLK to TXD[3:0], TXEN, TXER invalid | 2    | _    | ns     |

| MII8   | TXCLK to TXD[3:0], TXEN, TXER valid   | _    | 25   | ns     |

### Table 42. MII signal switching specifications

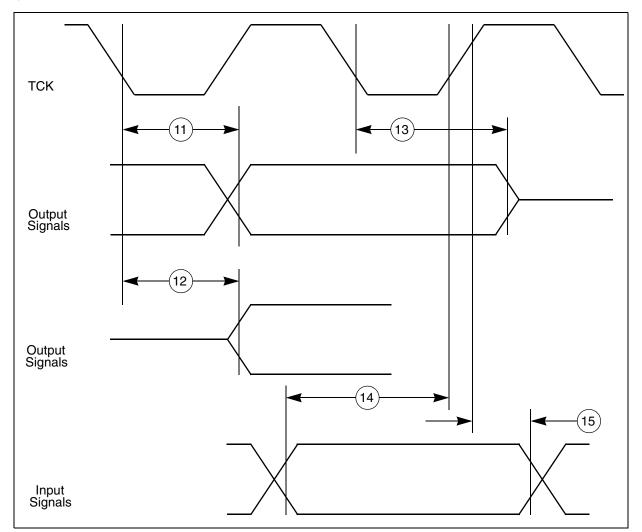

Figure 30. JTAG boundary scan timing

# 6.5.2 Nexus timing

### Table 51. Nexus debug port timing <sup>1</sup>

| No. | Symbol                                     | Parameter                                           | Condition | Min  | Max  | Unit  |

|-----|--------------------------------------------|-----------------------------------------------------|-----------|------|------|-------|

|     |                                            |                                                     | S         |      |      |       |

| 1   | t <sub>MCYC</sub>                          | MCKO Cycle Time                                     | —         | 15.6 | —    | ns    |

| 2   | t <sub>MDC</sub>                           | MCKO Duty Cycle                                     | _         | 40   | 60   | %     |

| 3   | t <sub>MDOV</sub>                          | MCKO Low to MDO, MSEO, EVTO Data Valid <sup>2</sup> | —         | -0.1 | 0.25 | tMCYC |

| 4   | t <sub>EVTIPW</sub>                        | EVTI Pulse Width                                    | —         | 4    | —    | tTCYC |

| 5   | t <sub>EVTOPW</sub>                        | EVTO Pulse Width                                    | _         | 1    | _    | tMCYC |

| 6   | t <sub>TCYC</sub>                          | TCK Cycle Time <sup>3</sup>                         | —         | 62.5 | —    | ns    |

| 7   | t <sub>TDC</sub>                           | TCK Duty Cycle                                      | —         | 40   | 60   | %     |

| 8   | t <sub>NTDIS</sub> ,<br>t <sub>NTMSS</sub> | TDI, TMS Data Setup Time                            |           | 8    |      | ns    |

Table continues on the next page...

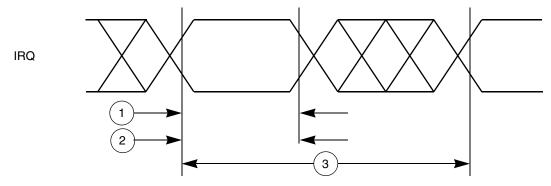

### 6.5.4 External interrupt timing (IRQ pin) Table 53. External interrupt timing specifications

| No. | Symbol            | Parameter             | Conditions | Min | Max | Unit             |

|-----|-------------------|-----------------------|------------|-----|-----|------------------|

| 1   | t <sub>IPWL</sub> | IRQ pulse width low   | —          | 3   | —   | t <sub>CYC</sub> |

| 2   | t <sub>IPWH</sub> | IRQ pulse width high  |            | 3   | _   | t <sub>CYC</sub> |

| 3   | t <sub>ICYC</sub> | IRQ edge to edge time | _          | 6   |     | t <sub>CYC</sub> |

These values applies when IRQ pins are configured for rising edge or falling edge events, but not both.

Figure 34. External interrupt timing

# 7 Thermal attributes

# 7.1 Thermal attributes

| Board<br>type        | Symbol                  | Description                                                      | 176LQFP | Unit | Notes   |

|----------------------|-------------------------|------------------------------------------------------------------|---------|------|---------|

| Single-layer<br>(1s) | R <sub>θJA</sub>        | Thermal resistance, junction to ambient (natural convection)     | 45.5    | °C/W | 1, 2    |

| Four-layer<br>(2s2p) | R <sub>θJA</sub>        | Thermal resistance, junction to ambient (natural convection)     | 23.1    | °C/W | 1, 2, 3 |

| Single-layer<br>(1s) | R <sub>θJMA</sub>       | Thermal resistance, junction to ambient (200 ft./min. air speed) | 34.8    | °C/W | 1,3     |

| Four-layer<br>(2s2p) | R <sub>θJMA</sub>       | Thermal resistance, junction to ambient (200 ft./min. air speed) | 16      | °C/W | 1,3     |

|                      | R <sub>θJB</sub>        | Thermal resistance, junction to board                            | 9.4     | °C/W | 4       |

|                      | R <sub>0JCtop</sub>     | Thermal resistance, junction to case top                         | 9.5     | °C/W | 5       |

|                      | R <sub>0JCbotttom</sub> | Thermal resistance, junction to case bottom                      | 0.2     | °C/W | 6       |

Table continues on the next page ...

# 9 Pinouts

# 9.1 Package pinouts and signal descriptions

For package pinouts and signal descriptions, refer to the Reference Manual.

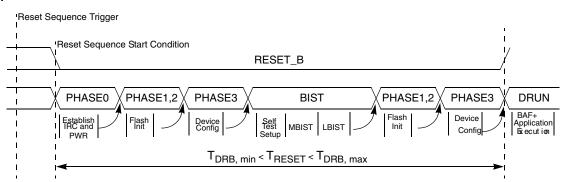

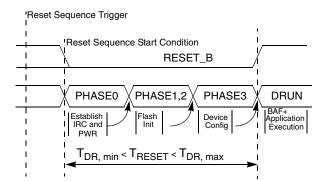

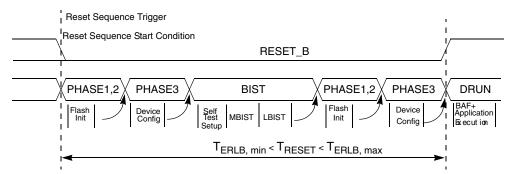

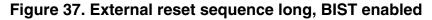

# 10 Reset sequence

This section describes different reset sequences and details the duration for which the device remains in reset condition in each of those conditions.

# 10.1 Reset sequence duration

Table 54 specifies the minimum and the maximum reset sequence duration for the five different reset sequences described in Reset sequence description.

| No. | Symbol            | Parameter                                      | T <sub>Reset</sub> |                  | Unit |    |

|-----|-------------------|------------------------------------------------|--------------------|------------------|------|----|

|     |                   |                                                | Min                | Typ <sup>1</sup> | Max  |    |

| 1   | T <sub>DRB</sub>  | Destructive Reset Sequence, BIST enabled       | 5.730              | 7.796            |      | ms |

| 2   | T <sub>DR</sub>   | Destructive Reset Sequence, BIST disabled      | 0.111              | 0.182            |      | ms |

| 3   | T <sub>ERLB</sub> | External Reset Sequence Long, Unsecure Boot    | 5.729              | 7.793            |      | ms |

| 4   | T <sub>FRL</sub>  | Functional Reset Sequence Long, Unsecure Boot  | 0.110              | 0.179            |      | ms |

| 5   | T <sub>FRS</sub>  | Functional Reset Sequence Short, Unsecure Boot | 0.007              | 0.009            |      | ms |

Table 54. RESET sequences

1. The Typ value is applicable only if the reset sequence duration is not prolonged by an extended assertion of RESET\_B by an external reset generator.

#### **Reset sequence**

Figure 38. Functional reset sequence long