Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Flouder Status             | Active                                                                 |

| Core Processor             | e200z2, e200z4                                                         |

| Core Size                  | 32-Bit Dual-Core                                                       |

| Speed                      | 80MHz/160MHz                                                           |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, LINbus, SAI, SPI, USB, USB OTG     |

| Peripherals                | DMA, LVD, POR, WDT                                                     |

| Number of I/O              | 178                                                                    |

| Program Memory Size        | 4MB (4M × 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 512K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                              |

| Data Converters            | A/D 80x10b, 64x12b                                                     |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 256-LBGA                                                               |

| Supplier Device Package    | 256-MAPPBGA (17x17)                                                    |

|                            | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5747ck1vmj6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

5. Estimated I/O count for largest proposed packages based on multiplexing with peripherals.

## Table 2. MPC5748G Family Comparison - NVM Memory Map 1

| Start Address | End Address | Flash block                   | RWW | MPC5746       | MPC5747       | MPC5748   |

|---------------|-------------|-------------------------------|-----|---------------|---------------|-----------|

| 0x01000000    | 0x0103FFFF  | 256 KB code<br>Flash block 0  | 6   | available     | available     | available |

| 0x01040000    | 0x0107FFFF  | 256 KB code<br>Flash block 1  | 6   | available     | available     | available |

| 0x01080000    | 0x010BFFFF  | 256 KB code<br>Flash block 2  | 6   | available     | available     | available |

| 0x010C0000    | 0x010FFFFF  | 256 KB code<br>Flash block3   | 6   | available     | available     | available |

| 0x01100000    | 0x0113FFFF  | 256 KB code<br>Flash block 4  | 6   | available     | available     | available |

| 0x01140000    | 0x0117FFFF  | 256 KB code<br>Flash block 5  | 6   | available     | available     | available |

| 0x01180000    | 0x011BFFFF  | 256 KB code<br>Flash block 6  | 6   | available     | available     | available |

| 0x011C0000    | 0x011FFFFF  | 256 KB code<br>Flash block 7  | 6   | available     | available     | available |

| 0x01200000    | 0x0123FFFF  | 256 KB code<br>Flash block 8  | 7   | available     | available     | available |

| 0x01240000    | 0x0127FFFF  | 256 KB code<br>Flash block 9  | 7   | available     | available     | available |

| 0x01280000    | 0x012BFFFF  | 256 KB code<br>Flash block 10 | 7   | not available | available     | available |

| 0x012C0000    | 0x012FFFFF  | 256 KB code<br>flash block 11 | 7   | not available | available     | available |

| 0x01300000    | 0x0133FFFF  | 256 KB code<br>flash block 12 | 7   | not available | available     | available |

| 0x01340000    | 0x0137FFFF  | 256 KB code<br>flash block 13 | 7   | not available | available     | available |

| 0x01380000    | 0x013BFFFF  | 256 KB code<br>flash block 14 | 7   | not available | not available | available |

| 0x013C0000    | 0x013FFFFF  | 256 KB code<br>flash block 15 | 7   | not available | not available | available |

| 0x01400000    | 0x0143FFFF  | 256 KB code<br>flash block 16 | 8   | not available | not available | available |

| 0x01440000    | 0x0147FFFF  | 256 KB code<br>flash block 17 | 8   | not available | not available | available |

| 0x01480000    | 0x014BFFFF  | 256 KB code<br>flash block 18 | 8   | not available | not available | available |

| 0x14C0000     | 0x014FFFFF  | 256 KB code<br>flash block 19 | 9   | not available | not available | available |

| 0x01500000    | 0x0153FFFF  | 256 KB code<br>flash block 20 | 9   | not available | not available | available |

| 0x01540000    | 0x0157FFFF  | 256 KB code<br>flash block 21 | 9   | not available | not available | available |

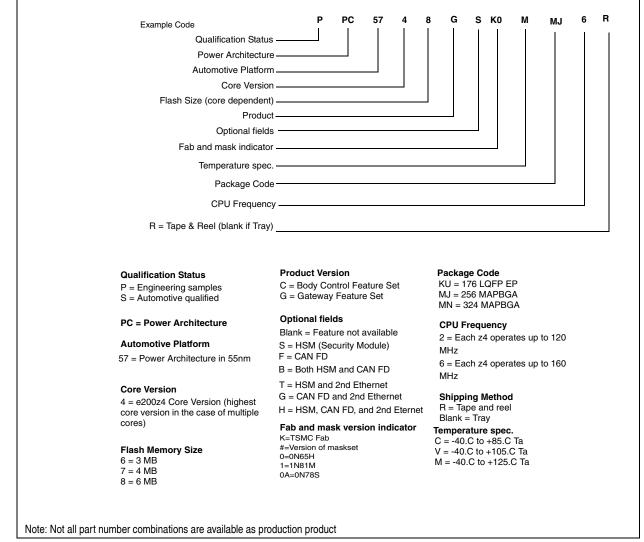

# 3.2 Ordering Information

# 4 General

## 4.1 Absolute maximum ratings

## NOTE

Functional operating conditions appear in the DC electrical characteristics. Absolute maximum ratings are stress ratings only, and functional operation at the maximum values is not guaranteed. See footnotes in Table 5 for specific conditions

# 4.3 Voltage regulator electrical characteristics

The voltage regulator is composed of the following blocks:

- Choice of generating supply voltage for the core area.

- Control of external NPN ballast transistor

- Connecting an external 1.25 V (nominal) supply directly without the NPN ballast

- Internal generation of the 3.3 V flash supply when device connected in 5V applications

- External bypass of the 3.3 V flash regulator when device connected in 3.3V applications

- Low voltage detector low threshold (LVD\_IO\_A\_LO) for V<sub>DD\_HV\_IO\_A supply</sub>

- Low voltage detector high threshold (LVD\_IO\_A\_Hi) for V<sub>DD\_HV\_IO\_A</sub> supply

- Various low voltage detectors (LVD\_LV\_x)

- High voltage detector (HVD\_LV\_cold) for 1.2 V digital core supply (VDD\_LV)

- Power on Reset (POR\_LV) for 1.25 V digital core supply (VDD\_LV)

- Power on Reset (POR\_HV) for 3.3 V to 5 V supply (VDD\_HV\_A)

The following bipolar transistors<sup>1</sup> are supported, depending on the device performance requirements. As a minimum the following must be considered when determining the most appropriate solution to maintain the device under its maximum power dissipation capability: current, ambient temperature, mounting pad area, duty cycle and frequency for Idd, collector voltage, etc

<sup>1.</sup> BCP56, MCP68 and MJD31are guaranteed ballasts.

| Symbol                                       | Parameter                                           | Conditions                                                                                                                                                                                                              | Min  | Тур | Max | Unit |

|----------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| C <sub>HV_VDD_A</sub>                        | VDD_HV_A supply capacitor                           | Min, max values shall be granted<br>with respect to tolerance, voltage,<br>temperature, and aging<br>variations.                                                                                                        | 1    | _   | —   | μF   |

| C <sub>HV_VDD_B</sub>                        | VDD_HV_B supply capacitor <sup>5</sup>              | Min, max values shall be granted<br>with respect to tolerance, voltage,<br>temperature, and aging<br>variations.                                                                                                        | 1    | _   | _   | μF   |

| C <sub>HV_VDD_C</sub>                        | VDD_HV_C supply capacitor <sup>5</sup>              | Min, max values shall be granted<br>with respect to tolerance, voltage,<br>temperature, and aging<br>variations.                                                                                                        | 1    | —   | —   | μF   |

| C <sub>HV_ADC0</sub><br>C <sub>HV_ADC1</sub> | HV ADC supply decoupling<br>capacitances            | Min, max values shall be granted<br>with respect to tolerance, voltage,<br>temperature, and aging<br>variations.                                                                                                        | 1    |     | _   | μF   |

| C <sub>HV_ADR</sub> <sup>6</sup>             | HV ADC SAR reference supply decoupling capacitances | Min, max values shall be granted<br>with respect to tolerance, voltage,<br>temperature, and aging<br>variations.                                                                                                        | 0.47 |     | _   | μF   |

| V <sub>DD_HV_BALL</sub><br>AST <sup>7</sup>  | FPREG Ballast collector supply voltage              | When collector of NPN ballast is<br>directly supplied by an on board<br>supply source (not shared with<br>VDD_HV_A supply pin) without<br>any series resistance, that is,<br>R <sub>C_BALLAST</sub> less than 0.01 Ohm. | 2.25 | _   | 5.5 | V    |

| R <sub>C_BALLAST</sub>                       | Series resistor on collector of FPREG ballast       | When VDD_HV_BALLAST is<br>shorted to VDD_HV_A on the<br>board                                                                                                                                                           | —    | _   | 0.1 | Ohm  |

| t <sub>SU</sub>                              | Start-up time after main supply stabilization       | Cfp_reg = 3 µF                                                                                                                                                                                                          | _    | 74  | _   | μs   |

| t <sub>ramp</sub>                            | Load current transient                              | lload from 15% to 55% $C_{\rm fp_{reg}} = 3 \ \mu F$                                                                                                                                                                    |      | 1.0 |     | μs   |

Table 8. Voltage regulator electrical specifications (continued)

- 1. Split capacitance on each pair VDD\_LV pin should sum up to a total value of  $C_{fp\_reg}$

- 2. Typical values will vary over temperature, voltage, tolerance, drift, but total variation must not exceed minimum and maximum values.

- 3. Ceramic X7R or X5R type with capacitance-temperature characteristics +/-15% of -55 degC to +125degC is recommended. The tolerance +/-20% is acceptable.

- 4. It is required to minimize the board parasitic inductance from decoupling capacitor to VDD\_HV\_FLA pin and the routing inductance should be less than 1nH.

- 5. 1. For VDD\_HV\_A, VDD\_HV\_B, and VDD\_HV\_C, 1µf on each side of the chip

- a. 0.1 µf close to each VDD/VSS pin pair.

- b. 10 µf near for each power supply source

- c. For VDD\_LV, 0.1uf close to each VDD/VSS pin pair is required. Depending on the the selected regulation mode, this amount of capacitance will need to be subtracted from the total capacitance required by the regulator for e.g., as specified by CFP\_REG parameter.

- For VDD\_LV, 0.1uf close to each VDD/VSS pin pair is required. Depending on the the selected regulation mode, this

amount of capacitance will need to be subtracted from the total capacitance required by the regulator for e.g., as

specified by CFP\_REG parameter

- 6. Only applicable to ADC1

#### General

- 7. In external ballast configuration the following must be ensured during power-up and power-down (Note: If V<sub>DD\_HV\_BALLAST</sub> is supplied from the same source as VDD\_HV\_A this condition is implicitly met):

- During power-up, V<sub>DD\_HV\_BALLAST</sub> must have met the min spec of 2.25V before VDD\_HV\_A reaches the POR\_HV\_RISE min of 2.75V.

- During power-down,  $V_{DD_HV_BALLAST}$  must not drop below the min spec of 2.25V until VDD\_HV\_A is below POR\_HV\_FALL min of 2.7V.

## NOTE

For a typical configuration using an external ballast transistor with separate supply for VDD\_HV\_A and the ballast collector, a bulk storage capacitor (as defined in Table 8) is required on VDD\_HV\_A close to the device pins to ensure a stable supply voltage.

Extra care must be taken if the VDD\_HV\_A supply is also being used to power the external ballast transistor or the device is running in internal regulation mode. In these modes, the inrush current on device Power Up or on exit from Low Power Modes is significant and may cause the VDD\_HV\_A voltage to drop resulting in an LVD reset event. To avoid this, the board layout should be optimized to reduce common trace resistance or additional capacitance at the ballast transistor collector (or VDD\_HV\_A pins in the case of internal regulation mode) is required. NXP recommends that customers simulate the external voltage supply circuitry.

In all circumstances, the voltage on VDD\_HV\_A must be maintained within the specified operating range (see Recommended operating conditions) to prevent LVD events.

## 4.4 Voltage monitor electrical characteristics

| Symbol              | Parameter                  | State | Conditions |                           | Configuration   |            |       | Threshold |       |   |

|---------------------|----------------------------|-------|------------|---------------------------|-----------------|------------|-------|-----------|-------|---|

|                     |                            |       |            | Powe<br>r Up <sup>1</sup> | Mas<br>k<br>Opt | Reset Type | Min   | Тур       | Max   | v |

| V <sub>POR_LV</sub> | LV supply                  | Fall  | Untrimmed  | Yes                       | No              | Powerup    | 0.930 | 0.979     | 1.028 | V |

|                     | power on<br>reset detector | -     | Trimmed    |                           |                 |            | 0.959 | 0.979     | 0.999 | V |

|                     |                            | Rise  | Untrimmed  |                           |                 |            | 0.980 | 1.029     | 1.078 | V |

|                     |                            |       | Trimmed    |                           |                 |            | 1.009 | 1.029     | 1.049 | V |

Table 9. Voltage monitor electrical characteristics

Table continues on the next page...

| Symbol                                                                               | Parameter                   | State   | Conditions |                           | Conf            | iguration  | 1                                        | Thresho           | ld    | Unit |  |

|--------------------------------------------------------------------------------------|-----------------------------|---------|------------|---------------------------|-----------------|------------|------------------------------------------|-------------------|-------|------|--|

|                                                                                      |                             |         |            | Powe<br>r Up <sup>1</sup> | Mas<br>k<br>Opt | Reset Type | Min                                      | Тур               | Max   | V    |  |

| V <sub>HVD_LV_cold</sub>                                                             | LV supply high              | Fall    | Untrimmed  | ed No Yes I               |                 | Functional | Disable                                  | Disabled at Start |       |      |  |

|                                                                                      | voltage monitoring,         |         | Trimmed    |                           |                 |            | 1.325                                    | 1.345             | 1.375 | V    |  |

|                                                                                      | detecting at                | Rise    | Untrimmed  |                           |                 |            | Disable                                  | ed at Sta         | irt   |      |  |

|                                                                                      | the device pin              |         | Trimmed    |                           |                 |            | 1.345                                    | 1.365             | 1.395 | V    |  |

| V <sub>LVD_LV_PD2_hot</sub>                                                          | LV supply low               | Fall    | Untrimmed  | Yes                       | Yes No          | Powerup    | 1.080                                    | 1.120             | 1.160 | V    |  |

|                                                                                      | voltage monitoring,         |         | Trimmed    | ]                         |                 |            | 1.125                                    | 1.143             | 1.160 | V    |  |

|                                                                                      | detecting in                | Rise    | Untrimmed  |                           |                 |            | 1.100                                    | 1.140             | 1.180 | V    |  |

| (hot) area                                                                           | the PD2 core (hot) area     |         | Trimmed    |                           |                 |            | 1.145                                    | 1.163             | 1.180 | V    |  |

| V <sub>LVD_LV_PD1_hot</sub>                                                          | LV supply low               | Fall    | Untrimmed  | Yes                       | No              | Powerup    | 1.080                                    | 1.120             | 1.160 | V    |  |

|                                                                                      | voltage monitoring,         |         | Trimmed    |                           |                 |            | 1.114                                    | 1.137             | 1.160 | V    |  |

|                                                                                      | detecting in                | Rise    | Untrimmed  |                           |                 |            | 1.100                                    | 1.140             | 1.180 | V    |  |

|                                                                                      | the PD1 core<br>(hot) area  |         | Trimmed    |                           |                 |            | 1.134                                    | 1.157             | 1.180 | V    |  |

| V <sub>LVD_LV_PD0_hot</sub><br>V <sub>LVD_LV_PD0_hot</sub><br>voltage<br>monitoring, | LV supply low               | Fall    | Untrimmed  | Yes                       | No              | Powerup    | 1.080                                    | 1.120             | 1.160 | V    |  |

|                                                                                      |                             | Trimmed | ]          |                           |                 | 1.114      | 1.137                                    | 1.160             | V     |      |  |

|                                                                                      | detecting in                | Rise    | Untrimmed  | ]                         |                 |            | 1.100                                    | 1.140             | 1.180 | V    |  |

|                                                                                      | the PD0 core<br>(hot) area  |         | Trimmed    |                           |                 |            | 1.134                                    | 1.157             | 1.180 | V    |  |

| V <sub>POR_HV</sub>                                                                  | HV supply                   | Fall    | Untrimmed  | Yes                       | No              | Powerup    | 2.700                                    | 2.850             | 3.000 | V    |  |

|                                                                                      | power on<br>reset detector  | Rise    | Untrimmed  |                           |                 |            | 2.750                                    | 2.900             | 3.050 | V    |  |

| V <sub>LVD_IO_A_LO</sub> , <sup>2</sup>                                              | HV IO_A                     | Fall    | Untrimmed  | Yes                       | No              | Powerup    | 2.750                                    | 2.923             | 3.095 | V    |  |

|                                                                                      | supply low voltage          |         | Trimmed    |                           |                 |            | 2.978                                    | 3.039             | 3.100 | V    |  |

|                                                                                      | monitoring -                | Rise    | Untrimmed  |                           |                 |            | 2.780                                    | 2.953             | 3.125 | V    |  |

|                                                                                      | low range                   |         | Trimmed    |                           |                 |            | 3.008                                    | 3.069             | 3.130 | V    |  |

| V <sub>LVD_IO_A_HI<sup>2</sup></sub>                                                 | HV IO_A<br>supply low       | Fall    | Trimmed    | No                        | Yes             | Functional |                                          | ed at Sta         |       | V    |  |

|                                                                                      | voltage                     | Rise    | Trimmed    | -                         |                 |            | 4.060 4.151 4.240 V<br>Disabled at Start |                   |       |      |  |

|                                                                                      | monitoring -<br>high range  | nise    | Thinned    |                           |                 | 4.115      | 4.201                                    | 4.3               | V     |      |  |

| V <sub>LVD_LV_PD2_cold</sub>                                                         | LV supply low               | Fall    | Untrimmed  | No                        | Yes             | Functional | Disable                                  | ed at Sta         | ırt   | 1    |  |

|                                                                                      | voltage                     |         | Trimmed    | 1                         |                 |            | 1.14                                     | 1.158             | 1.175 | V    |  |

|                                                                                      | monitoring,<br>detecting at | Rise    | Untrimmed  | 1                         |                 |            | Disable                                  | ed at Sta         | ırt   | 1    |  |

|                                                                                      | the device pin              |         | Trimmed    | 1                         |                 |            | 1.16                                     | 1.178             | 1.195 | V    |  |

Table 9. Voltage monitor electrical characteristics (continued)

All monitors that are active at power-up will gate the power up recovery and prevent exit from POWERUP phase until the minimum level is crossed. These monitors can in some cases be masked during normal device operation, but when active will always generate a destructive reset.

2. There is no voltage monitoring on the  $V_{DD_HV_ADC0}$ ,  $V_{DD_HV_ADC1}$ ,  $V_{DD_HV_B}$  and  $V_{DD_HV_C}$  I/O segments. For applications requiring monitoring of these segments, either connect these to  $V_{DD_HV_A}$  at the PCB level or monitor externally.

#### General

x FlexCAN state machines clocked(other FLEXCAN clock gated), 4 x LINFlexD transmitting (Other clock gated), 1x eMIOS clocked(used OPWFMB mode) (Others clock gated), FIRC, SIRC, FXOSC, SXOSC, PLL running, BCTU, DMAMUX, ACMP clock gated. All others modules clock gated if not specifically mentioned. I/O supply current excluded

- 6. Recommended Transistors:MJD31@85°C, 105°C and 125°C.

- 7. Enabled Modules in Body mode enabled at maximum frequency: 2 x e200Z4 @ 120Mhz(Instruction and Data cache enabled),Platform@120MHz, SRAMs accessed in parallel, Flash access(prefetch is disabled while buffers are enabled), HSM reading from flash at regular intervals(500 pll clock cycles), DMA (SRAM to SRAM), ADC0 converting using BCTU triggers which are triggered through PIT(ADC1 clocked), RTC clocked, 3 x STM clocked, 2 x DSPI transmitting(others DSPIs clocked), 2 x SPI transmitting(others clocked), 4 x FlexCAN state machines working(others clocked), 9xLINFlexD transmitting (others clocked), 1xeMIOS operational (used OPWFMB mode) (others clocked), FIRC, SIRC, FXOSC, SXOSC, PLL running, MEMU, FCCU, SIUL, SDHC,CMP clocked, e200Z2, ENET, MLB, SAI, I2C, FlexRay, USB clock gated. All others modules clock gated if not specifically mentioned I/O supply current excluded

- 8. Recommended Transistors: BCP56, BCP68 or MJD31@85°C, BCP56, BCP68 or MJD31@105°C and MJD31@125°C.

- 9. Enabled Modules in Body mode enabled at maximum frequency:2 x e200Z4 @80Mhz(Instruction and Data cache enabled),Platform@80MHz, SRAMs accessed in parallel, Flash access(prefetch is disabled while buffers are enabled), HSM reading from flash at regular intervals(500 pll clock cycles), DMA (SRAM to SRAM), ADC0 converting using BCTU triggers which are triggered through PIT(ADC1 clocked), RTC clocked, 3 x STM clocked, 2 x DSPI transmitting(others DSPIs clocked), 2 x SPI transmitting(others clocked), 4 x FlexCAN state machines working(others clocked), 9xLINFlexD transmitting (others clocked), 1xeMIOS operational (used OPWFMB mode) (others clocked), FIRC, SIRC, FXOSC, SXOSC, PLL running, MEMU, FCCU, SIUL, SDHC,CMP clocked, e200Z2, ENET, MLB, SAI, I2C, FlexRay, USB clock gated. All others modules clock gated if not specifically mentioned I/O supply current excluded

- 10. Recommended Transistors:BCP56, BCP68 or MJD31@85°C, 105°C and 125°C

- Internal structures hold the input voltage less than V<sub>DD\_HV\_ADC\_REF</sub> + 1.0 V on all pads powered by V<sub>DDA</sub> supplies, if the maximum injection current specification is met (3 mA for all pins) and V<sub>DDA</sub> is within the operating voltage specifications.

This value is the total support for two ADCs Fach ADC might compute on A structure.

- 12. This value is the total current for two ADCs.Each ADC might consume upto 2mA at max.

| Symbol   | Parameter                       | Conditions <sup>1</sup>                        | Min | Тур   | Max  | Unit |

|----------|---------------------------------|------------------------------------------------|-----|-------|------|------|

| LPU_RUN  | with 256K RAM,                  | T <sub>a</sub> = 25 °C                         | _   | 8.9   |      | mA   |

|          | but only one RAM being accessed | SYS_CLK = 16MHz                                |     |       |      |      |

|          | ling and the                    | ADC0 = OFF, SPI0 = OFF, LIN0 = OFF, CAN0 = OFF |     |       |      |      |

|          |                                 | T <sub>a</sub> = 25 °C                         |     | 10.2  |      |      |

|          |                                 | SYS_CLK = 16MHz                                |     |       |      |      |

|          |                                 | ADC0 = ON, SPI0 = ON, LIN0 = ON, CAN0 = ON     |     |       |      |      |

|          |                                 | T <sub>a</sub> = 85 °C                         | —   | 12.5  | 22   |      |

|          |                                 | $T_a = 105 \ ^{\circ}C$                        | —   | 14.5  | 24   |      |

|          |                                 | T <sub>a</sub> = 125 °C <sup>, 2</sup>         | —   | 16    | 26   |      |

|          |                                 | SYS_CLK = 16MHz                                |     |       |      |      |

|          |                                 | ADC0 = ON, SPI0 = ON, LIN0 = ON, CAN0 = ON     |     |       |      |      |

| LPU_STOP | with 256K RAM                   | T <sub>a</sub> = 25 °C                         | —   | 0.535 |      | mA   |

|          |                                 | T <sub>a</sub> = 85 °C                         | —   | 0.72  | 6    |      |

|          |                                 | $T_a = 105 \text{ °C}$                         | _   | 1     | 8    |      |

|          |                                 | $T_a = 125 \ ^{\circ}C^2$                      | —   | 1.6   | 10.6 |      |

### Table 11. Low Power Unit (LPU) Current consumption characteristics

1. The content of the Conditions column identifies the components that draw the specific current.

Assuming Ta=Tj, as the device is in static (fully clock gated) mode. Assumes maximum θJA of 2s2p board. SeeThermal attributes

| Symbol   | Parameter    | Conditions <sup>1</sup> | Min | Тур | Max  | Unit |

|----------|--------------|-------------------------|-----|-----|------|------|

| STANDBY0 | STANDBY with | T <sub>a</sub> = 25 °C  |     | 71  | _    | μA   |

|          | 8K RAM       | T <sub>a</sub> = 85 °C  | _   | 175 | 800  |      |

|          |              | T <sub>a</sub> = 105 °C | _   | 338 | 1725 | 1    |

|          |              | T <sub>a</sub> = 125 °C | _   | 750 | 2775 |      |

| STANDBY1 | STANDBY with | T <sub>a</sub> = 25 °C  |     | 72  |      | μA   |

|          | 64K RAM      | T <sub>a</sub> = 85 °C  | —   | 176 | 815  | 1    |

|          |              | T <sub>a</sub> = 105 °C |     | 350 | 1775 | 1    |

|          |              | T <sub>a</sub> = 125 °C | _   | 825 | 3000 | 1    |

| STANDBY2 | STANDBY with | T <sub>a</sub> = 25 °C  | —   | 75  |      | μA   |

|          | 128K RAM     | T <sub>a</sub> = 85 °C  | _   | 182 | 830  |      |

|          |              | T <sub>a</sub> = 105 °C | _   | 366 | 1825 | 1    |

|          |              | T <sub>a</sub> = 125 °C | _   | 900 | 3250 | 1    |

| STANDBY3 | STANDBY with | T <sub>a</sub> = 25 °C  | _   | 80  |      | μA   |

|          | 256K RAM     | T <sub>a</sub> = 85 °C  | _   | 197 | 860  |      |

|          |              | T <sub>a</sub> = 105 °C | —   | 400 | 1875 | 1    |

|          |              | T <sub>a</sub> = 125 °C | —   | 975 | 3500 | 1    |

| STANDBY3 | FIRC ON      | T <sub>a</sub> = 25 °C  | _   | 500 | _    | μA   |

Table 12. STANDBY Current consumption characteristics

1. The content of the Conditions column identifies the components that draw the specific current.

# 4.6 Electrostatic discharge (ESD) characteristics

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n + 1) supply pin). This test conforms to the AEC-Q100-002/-003/-011 standard.

## NOTE

A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device specification requirements. Complete DC parametric and functional testing shall be performed per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

Table 13. ESD ratings

| Symbol                | Parameter               | Conditions <sup>1</sup> | Class | Max value <sup>2</sup> | Unit |

|-----------------------|-------------------------|-------------------------|-------|------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge | T <sub>A</sub> = 25 °C  | H1C   | 2000                   | V    |

|                       | (Human Body Model)      |                         |       |                        |      |

Table continues on the next page ...

#### I/O parameters

| Table 17. | DC electrical s | specifications @ \$ | 5 V Range | (continued) |

|-----------|-----------------|---------------------|-----------|-------------|

|-----------|-----------------|---------------------|-----------|-------------|

| Symbol | Parameter                                              | Va  | lue | Unit |

|--------|--------------------------------------------------------|-----|-----|------|

|        |                                                        | Min | Мах |      |

| loh_f  | Full drive loh <sup>9</sup> (SIUL2_MSCRn[SRC 1:0]= 11) | 38  | 132 | mA   |

| lol_f  | Full drive Iol <sup>9</sup> (SIUL2_MSCRn[SRC 1:0]= 11) | 48  | 220 | mA   |

| loh_h  | Half drive loh <sup>9</sup> (SIUL2_MSCRn[SRC 1:0]= 10) | 19  | 66  | mA   |

| lol_h  | Half drive Iol <sup>9</sup> (SIUL2_MSCRn[SRC 1:0]= 10) | 24  | 110 | mA   |

- 1. Max power supply ramp rate is 500 V / ms

- 2. Measured when pad=0.69\*VDD\_HV\_x

- 3. Measured when pad=0.49\*VDD\_HV\_x

- 4. Measured when pad = 0 V

- 5. Measured when pad =  $VDD_HV_x$

- 6. Measured when pad is sourcing 2 mA

- 7. Measured when pad is sinking 2 mA

- 8. Measured when pad is sinking 1.5 mA

- 9. Ioh/IoI is derived from spice simulations. These values are NOT guaranteed by test.

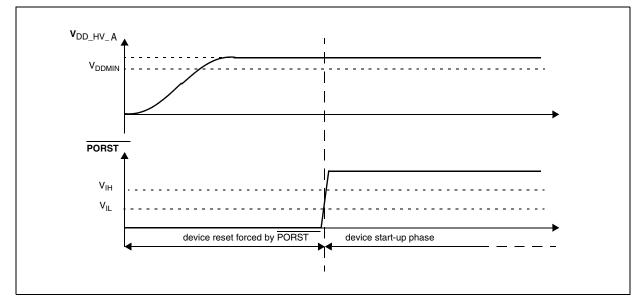

## 5.5 Reset pad electrical characteristics

The device implements a dedicated bidirectional RESET pin.

Figure 3. Start-up reset requirements

| Symbol                           | Parameter                                                                             | Conditions                            | Min | Typ <sup>1</sup> | Мах  | Unit |

|----------------------------------|---------------------------------------------------------------------------------------|---------------------------------------|-----|------------------|------|------|

| t <sub>conv</sub>                | Conversion time <sup>4</sup>                                                          | 80 MHz                                | 550 | —                |      | ns   |

| t <sub>total_conv</sub>          | Total Conversion time t <sub>sample</sub> + t <sub>conv</sub> (for standard channels) | 80 MHz                                | 1   | —                | _    | μs   |

|                                  | Total Conversion time t <sub>sample</sub> + t <sub>conv</sub> (for extended channels) |                                       | 1.5 | _                | —    |      |

| C <sub>S</sub>                   | ADC input sampling capacitance                                                        | —                                     | —   | 3                | 5    | pF   |

| C <sub>P1</sub> <sup>5</sup>     | ADC input pin capacitance 1                                                           | —                                     | _   | —                | 5    | pF   |

| C <sub>P2</sub> <sup>5</sup>     | ADC input pin capacitance 2                                                           | —                                     | _   | —                | 0.8  | pF   |

| R <sub>SW1</sub> <sup>5</sup>    | Internal resistance of analog                                                         | V <sub>REF</sub> range = 4.5 to 5.5 V | —   | —                | 0.3  | kΩ   |

|                                  | source                                                                                | $V_{REF}$ range = 3.15 to 3.6 V       | _   | —                | 875  | Ω    |

| R <sub>AD</sub> <sup>5</sup>     | Internal resistance of analog source                                                  | _                                     | —   | —                | 825  | Ω    |

| INL                              | Integral non-linearity                                                                | —                                     | -2  | —                | 2    | LSB  |

| DNL                              | Differential non-linearity                                                            | —                                     | -1  | _                | 1    | LSB  |

| OFS                              | Offset error                                                                          | —                                     | -4  | —                | 4    | LSB  |

| GNE                              | Gain error                                                                            | —                                     | -4  | —                | 4    | LSB  |

| ADC Analog Pad                   | Max leakage (standard channel)                                                        | 150 °C                                | _   | —                | 2500 | nA   |

| (pad going to one ADC)           | Max leakage (standard channel)                                                        | 105 °C <sub>TA</sub>                  | —   | 5                | 250  | nA   |

| ADO)                             | Max positive/negative injection                                                       |                                       | -5  | —                | 5    | mA   |

| TUE <sub>standard/extended</sub> | Total unadjusted error for standard                                                   | Without current injection             | -4  | +/-3             | 4    | LSB  |

| channels                         | channels                                                                              | With current injection <sup>6</sup>   |     | +/-4             |      | LSB  |

| t <sub>recovery</sub>            | STOP mode to Run mode recovery time                                                   |                                       |     |                  | < 1  | μs   |

### Table 21. ADC conversion characteristics (for 10-bit) (continued)

- Active ADC Input, VinA < [min(ADC\_ADV, IO\_Supply\_A,B,C)]. Violation of this condition would lead to degradation of ADC performance. Please refer to Table: 'Absolute maximum ratings' to avoid damage. Refer to Table: 'Recommended operating conditions' for required relation between IO\_supply\_A, B, C and ADC\_Supply.

- 2. The internally generated clock (known as AD\_clk or ADCK) could be same as the peripheral clock or half of the peripheral clock based on register configuration in the ADC.

- During the sample time the input capacitance C<sub>S</sub> can be charged/discharged by the external source. The internal

resistance of the analog source must allow the capacitance to reach its final voltage level within t<sub>sample</sub>. After the end of the

sample time t<sub>sample</sub>, changes of the analog input voltage have no effect on the conversion result. Values for the sample

clock t<sub>sample</sub> depend on programming.

- 4. This parameter does not include the sample time t<sub>sample</sub>, but only the time for determining the digital result and the time to load the result register with the conversion result.

- 5. See Figure 2

- 6. Current injection condition for ADC channels is defined for an inactive ADC channel (on which conversion is NOT being performed), and this occurs when voltage on the ADC pin exceeds the I/O supply or ground. However, absolute maximum voltage spec on pad input (VINA, see Table: 'Absolute maximum ratings') must be honored to meet TUE spec quoted here

## NOTE

The ADC input pins sit across all three I/O segments, VDD\_HV\_A, VDD\_HV\_B and VDD\_HV\_C.

## 6.1.2 Analog Comparator (CMP) electrical specifications Table 22. Comparator and 6-bit DAC electrical specifications

| Symbol             | Description                                                          | Min.            | Тур. | Max.                         | Unit             |

|--------------------|----------------------------------------------------------------------|-----------------|------|------------------------------|------------------|

| I <sub>DDHS</sub>  | Supply current, High-speed mode (EN=1, PMODE=1)                      | _               | —    | 250                          | μA               |

| I <sub>DDLS</sub>  | Supply current, low-speed mode (EN=1, PMODE=0)                       |                 | 5    | 11                           | μA               |

| V <sub>AIN</sub>   | Analog input voltage                                                 | V <sub>SS</sub> | _    | V <sub>IN1_CMP_RE</sub><br>F | V                |

| V <sub>AIO</sub>   | Analog input offset voltage <sup>1</sup>                             | -42             | _    | 42                           | mV               |

| V <sub>H</sub>     | Analog comparator hysteresis <sup>2</sup>                            | _               | 1    | 25                           | mV               |

|                    | • CR0[HYSTCTR] = 00                                                  | _               | 20   | 50                           | mV               |

|                    | • CR0[HYSTCTR] = 01                                                  | _               | 40   | 70                           | mV               |

|                    | • CR0[HYSTCTR] = 10                                                  | _               | 60   | 105                          | mV               |

|                    | <ul> <li>CR0[HYSTCTR] = 11</li> </ul>                                |                 |      |                              |                  |

| t <sub>DHS</sub>   | Propagation Delay, High Speed Mode (Full Swing) <sup>1, 3</sup>      |                 | _    | 250                          | ns               |

| t <sub>DLS</sub>   | Propagation Delay, Low power Mode (Full Swing) <sup>1, 3</sup>       |                 | 5    | 21                           | μs               |

|                    | Analog comparator initialization delay, High speed mode <sup>4</sup> | _               | 4    |                              | μs               |

|                    | Analog comparator initialization delay, Low speed mode <sup>4</sup>  | _               | 100  |                              | μs               |

| I <sub>DAC6b</sub> | 6-bit DAC current adder (when enabled)                               |                 |      |                              |                  |

|                    | 3.3V Reference Voltage                                               | _               | 6    | 9                            | μA               |

|                    | 5V Reference Voltage                                                 | _               | 10   | 16                           | μA               |

| INL                | 6-bit DAC integral non-linearity                                     | -0.5            | —    | 0.5                          | LSB <sup>5</sup> |

| DNL                | 6-bit DAC differential non-linearity                                 | -0.8            | _    | 0.8                          | LSB              |

1. Measured with hysteresis mode of 00

2. Typical hysteresis is measured with input voltage range limited to 0.6 to  $V_{DD_HV_A}$ -0.6V

3. Full swing = VIH, VIL

4. Comparator initialization delay is defined as the time between software writes to change control inputs (Writes to DACEN, VRSEL, PSEL, MSEL, VOSEL) and the comparator output settling to a stable level.

5. 1 LSB =  $V_{reference}/64$

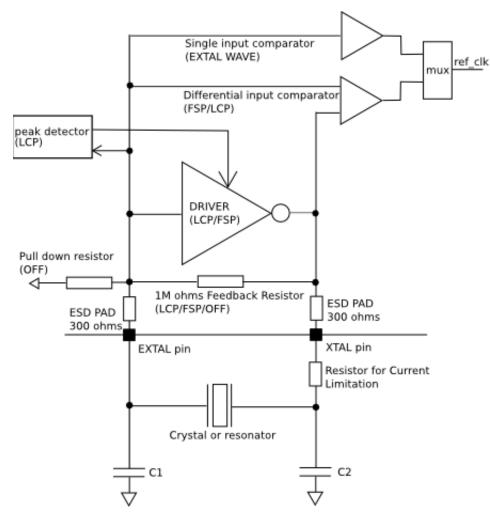

| Table 23. | Main oscillator | electrical | characteristics |

|-----------|-----------------|------------|-----------------|

|-----------|-----------------|------------|-----------------|

| Symbol                      | Parameter                | Mode    | Conditions | Min | Тур | Max | Unit            |

|-----------------------------|--------------------------|---------|------------|-----|-----|-----|-----------------|

| f <sub>xoschs</sub>         | Oscillator<br>frequency  | FSP/LCP |            | 8   |     | 40  | MHz             |

| <b>g</b> <sub>mXOSCHS</sub> | Driver                   | LCP     |            |     | 23  |     | mA/V            |

|                             | Transconduct ance        | FSP     |            |     | 33  |     |                 |

| V <sub>XOSCHS</sub>         | Oscillation<br>Amplitude | LCP     | 8 MHz      |     | 1.0 |     | V <sub>PP</sub> |

|                             |                          |         | 16 MHz     | 1   | 1.0 |     |                 |

|                             |                          |         | 40 MHz     |     | 0.8 |     |                 |

| T <sub>XOSCHSSU</sub>       | Startup time             | FSP/LCP | 8 MHz      |     | 2   |     | ms              |

|                             |                          |         | 16 MHz     |     | 1   |     |                 |

|                             |                          |         | 40 MHz     |     | 0.5 |     |                 |

|                             | Oscillator               | FSP     | 8 MHz      |     | 2.2 |     | mA              |

|                             | Analog Circuit           | current | 16 MHz     | 1   | 2.2 |     |                 |

|                             | supply current           |         | 40 MHz     | -   | 3.2 |     |                 |

Table continues on the next page...

| Spec | Characteristics     | Pad Drive/Load | Value  |       |  |

|------|---------------------|----------------|--------|-------|--|

|      |                     |                | Min    | Мах   |  |

| tSCK | SCK cycle timing    | strong/50 pF   | 100 ns | -     |  |

| -    | PCS valid after SCK | strong/50 pF   | -      | 15 ns |  |

| -    | PCS valid after SCK | strong/50 pF   | -4 ns  | -     |  |

Table 36.

Continuous SCK timing

## Table 37. DSPI high speed mode I/Os

| DSPI  | High speed SCK | High speed SIN | High speed SOUT |

|-------|----------------|----------------|-----------------|

| DSPI2 | GPIO[78]       | GPIO[76]       | GPIO[77]        |

| DSPI3 | GPIO[100]      | GPIO[101]      | GPIO[98]        |

| SPI1  | GPIO[173]      | GPIO[175]      | GPIO[176]       |

| SPI2  | GPIO[79]       | GPIO[110]      | GPIO[111]       |

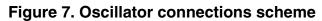

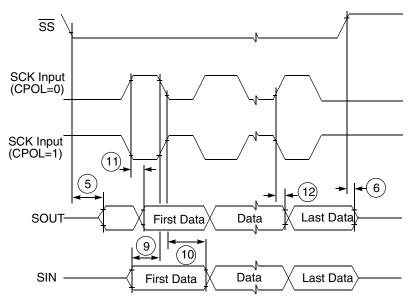

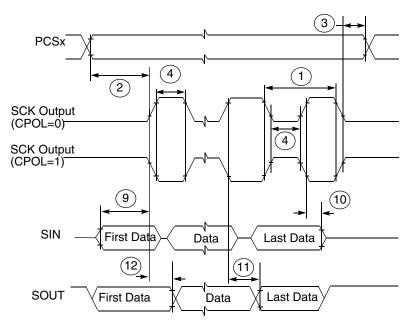

Figure 8. DSPI classic SPI timing — master, CPHA = 0

Figure 9. DSPI classic SPI timing — master, CPHA = 1

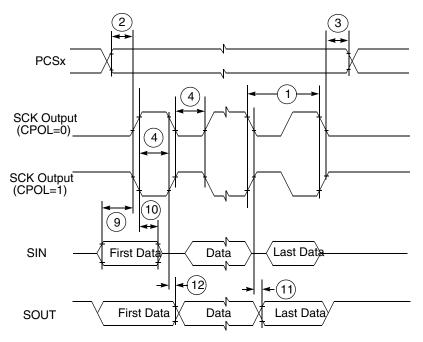

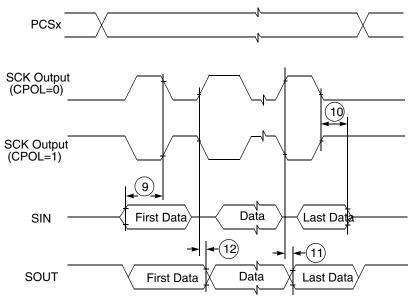

Figure 10. DSPI classic SPI timing — slave, CPHA = 0

**Communication interfaces**

Figure 11. DSPI classic SPI timing — slave, CPHA = 1

Figure 12. DSPI modified transfer format timing — master, CPHA = 0

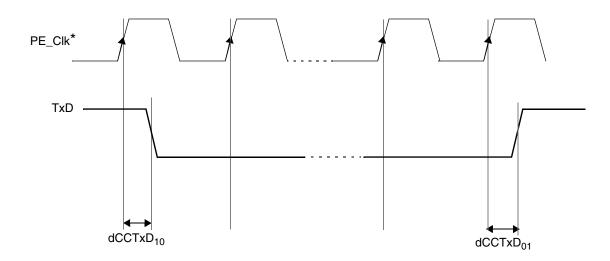

| Name                 | Description <sup>1</sup>                                                               | Min | Max | Unit |

|----------------------|----------------------------------------------------------------------------------------|-----|-----|------|

| dCCTxD <sub>01</sub> | Sum of delay between Clk to Q of the last FF and the final output buffer, rising edge  | —   | 25  | ns   |

| dCCTxD <sub>10</sub> | Sum of delay between Clk to Q of the last FF and the final output buffer, falling edge | _   | 25  | ns   |

## Table 39. TxD output characteristics (continued)

1. All parameters specified for  $V_{DD_HV_IOx} = 3.3 \text{ V} - 5\%$ , +±10%, TJ = -40 °C / 150 °C, TxD pin load maximum 25 pF. 2. For 3.3 V ± 10% operation, this specification is 10 ns.

\*FlexRay Protocol Engine Clock

### Figure 20. TxD Signal propagation delays

#### 6.4.2.4 **RxD**

| Name                 | Description <sup>1</sup>                                                             | Min | Мах | Unit |

|----------------------|--------------------------------------------------------------------------------------|-----|-----|------|

| C_CCRxD              | Input capacitance on<br>RxD pin                                                      | —   | 7   | pF   |

| uCCLogic_1           | Threshold for detecting logic high                                                   | 35  | 70  | %    |

| uCCLogic_0           | Threshold for detecting<br>logic low                                                 | 30  | 65  | %    |

| dCCRxD <sub>01</sub> | Sum of delay from<br>actual input to the D<br>input of the first FF,<br>rising edge  | _   | 10  | ns   |

| dCCRxD <sub>10</sub> | Sum of delay from<br>actual input to the D<br>input of the first FF,<br>falling edge | _   | 10  | ns   |

1. All parameters specified for VDD\_HV\_IOx =  $3.3 \text{ V} \cdot 5\%$ , +±10%, TJ = -40 oC / 150 oC.

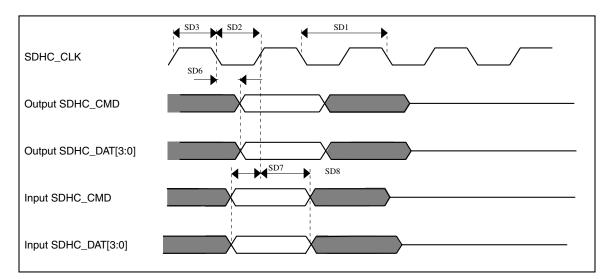

# 6.4.3 uSDHC specifications

### Table 41. uSDHC switching specifications

| Num | Symbol           | Description                                   | Min.          | Max.      | Unit |

|-----|------------------|-----------------------------------------------|---------------|-----------|------|

|     |                  | Card input clock                              |               |           |      |

| SD1 | fpp              | Clock frequency (Identification mode)         | 0             | 400       | kHz  |

|     | fpp              | Clock frequency (SD\SDIO full speed)          | 0             | 25        | MHz  |

|     | fpp              | Clock frequency (SD\SDIO high speed)          | 0             | 40        | MHz  |

|     | fpp              | Clock frequency (MMC full speed)              | 0             | 20        | MHz  |

|     | f <sub>OD</sub>  | Clock frequency (MMC full speed)              | 0             | 40        | MHz  |

| SD2 | t <sub>WL</sub>  | Clock low time                                | 7             | —         | ns   |

| SD3 | t <sub>WH</sub>  | Clock high time                               | 7             | —         | ns   |

| SD4 | t <sub>TLH</sub> | Clock rise time                               | _             | 3         | ns   |

| SD5 | t <sub>THL</sub> | Clock fall time                               | _             | 3         | ns   |

|     |                  | SDHC output / card inputs SDHC_CMD, SDHC_DAT  | (reference to | SDHC_CLK) |      |

| SD6 | t <sub>OD</sub>  | SDHC output delay (output valid)              | -5            | 6.5       | ns   |

|     |                  | SDHC input / card inputs SDHC_CMD, SDHC_DAT ( | reference to  | SDHC_CLK) |      |

| SD7 | t <sub>ISU</sub> | SDHC input setup time                         | 5             | —         | ns   |

| SD8 | t <sub>IH</sub>  | SDHC input hold time                          | 0             | —         | ns   |

Figure 21. uSDHC timing

#### FlexRay electrical specifications

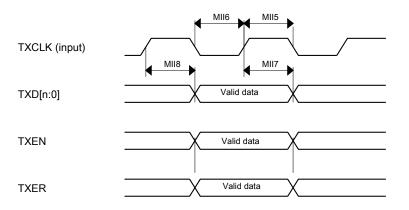

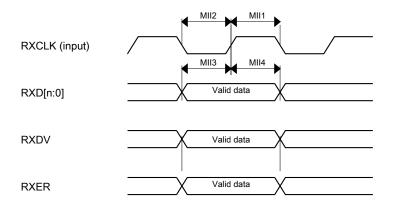

Figure 23. RMII/MII receive signal timing diagram

## 6.4.4.2 RMII signal switching specifications

The following timing specs meet the requirements for RMII style interfaces for a range of transceiver devices.

| Num   | Description                                 | Min. | Max. | Unit               |

|-------|---------------------------------------------|------|------|--------------------|

| —     | EXTAL frequency (RMII input clock RMII_CLK) | —    | 50   | MHz                |

| RMII1 | RMII_CLK pulse width high                   | 35%  | 65%  | RMII_CLK<br>period |

| RMII2 | RMII_CLK pulse width low                    | 35%  | 65%  | RMII_CLK<br>period |

| RMII3 | RXD[1:0], CRS_DV, RXER to RMII_CLK setup    | 4    | _    | ns                 |

| RMII4 | RMII_CLK to RXD[1:0], CRS_DV, RXER hold     | 2    | —    | ns                 |

| RMII7 | RMII_CLK to TXD[1:0], TXEN invalid          | 4    | _    | ns                 |

| RMII8 | RMII_CLK to TXD[1:0], TXEN valid            | —    | 15   | ns                 |

Table 43. RMII signal switching specifications

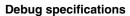

Figure 30. JTAG boundary scan timing

# 6.5.2 Nexus timing

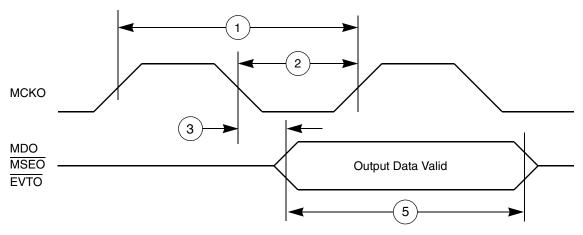

## Table 51. Nexus debug port timing <sup>1</sup>

| No. | Symbol                                     | Parameter                                           | Condition | Min  | Max  | Unit  |

|-----|--------------------------------------------|-----------------------------------------------------|-----------|------|------|-------|

|     |                                            |                                                     | S         |      |      |       |

| 1   | t <sub>MCYC</sub>                          | MCKO Cycle Time                                     | —         | 15.6 | —    | ns    |

| 2   | t <sub>MDC</sub>                           | MCKO Duty Cycle                                     | _         | 40   | 60   | %     |

| 3   | t <sub>MDOV</sub>                          | MCKO Low to MDO, MSEO, EVTO Data Valid <sup>2</sup> | —         | -0.1 | 0.25 | tMCYC |

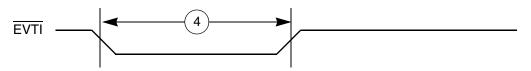

| 4   | t <sub>EVTIPW</sub>                        | EVTI Pulse Width                                    | —         | 4    | —    | tTCYC |

| 5   | t <sub>EVTOPW</sub>                        | EVTO Pulse Width                                    | _         | 1    | _    | tMCYC |

| 6   | t <sub>TCYC</sub>                          | TCK Cycle Time <sup>3</sup>                         | —         | 62.5 | —    | ns    |

| 7   | t <sub>TDC</sub>                           | TCK Duty Cycle                                      | —         | 40   | 60   | %     |

| 8   | t <sub>NTDIS</sub> ,<br>t <sub>NTMSS</sub> | TDI, TMS Data Setup Time                            |           | 8    |      | ns    |

Table continues on the next page...

## Table 51. Nexus debug port timing <sup>1</sup> (continued)

| No. | Symbol                                     | Parameter                     | Condition<br>s | Min | Max | Unit |

|-----|--------------------------------------------|-------------------------------|----------------|-----|-----|------|

| 9   | t <sub>NTDIH</sub> ,<br>t <sub>NTMSH</sub> | TDI, TMS Data Hold Time       | _              | 5   | —   | ns   |

| 10  | t <sub>JOV</sub>                           | TCK Low to TDO/RDY Data Valid | —              | 0   | 25  | ns   |

1. JTAG specifications in this table apply when used for debug functionality. All Nexus timing relative to MCKO is measured from 50% of MCKO and 50% of the respective signal.

- 2. For all Nexus modes except DDR mode, MDO, MSEO, and EVTO data is held valid until next MCKO low cycle.

- 3. The system clock frequency needs to be four times faster than the TCK frequency.

Figure 31. Nexus output timing

Figure 32. Nexus EVTI Input Pulse Width