Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | e200z2, e200z4, e200z4                                                 |

| Core Size                  | 32-Bit Tri-Core                                                        |

| Speed                      | 80MHz/160MHz                                                           |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, LINbus, SAI, SPI, USB, USB OTG     |

| Peripherals                | DMA, LVD, POR, WDT                                                     |

| Number of I/O              | 129                                                                    |

| Program Memory Size        | 4MB (4M × 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 768K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                              |

| Data Converters            | A/D 80x10b, 64x12b                                                     |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 176-LQFP Exposed Pad                                                   |

| Supplier Device Package    | 176-LQFP (24x24)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5747gk1mku6 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

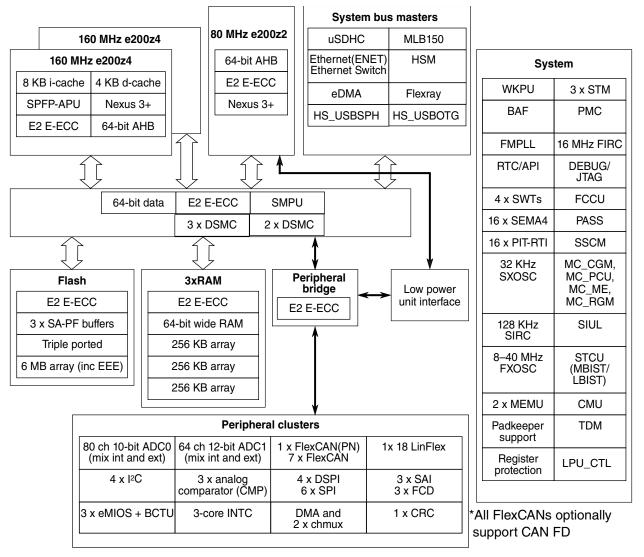

## 1 Block diagram

Figure 1. MPC5748G block diagram

## 2 Family comparison

The following table provides a summary of the different members of the MPC5748G family and their proposed features. This information is intended to provide an understanding of the range of functionality offered by this family. For full details of all of the family derivatives please contact your marketing representative.

| Start Address | End Address | Flash block      | RWW | MPC5747C      | MPC5746G  |

|---------------|-------------|------------------|-----|---------------|-----------|

|               |             |                  |     | MPC5748C      | MPC5747G  |

|               |             |                  |     |               | MPC5748G  |

| 0x00F90000    | 0x00F93FFF  | 16 KB data Flash | 2   | available     | available |

| 0x00F94000    | 0x00F97FFF  | 16 KB data Flash | 2   | available     | available |

| 0x00F98000    | 0x00F9BFFF  | 16 KB data Flash | 2   | available     | available |

| 0x00F9C000    | 0x00F9FFFF  | 16 KB data Flash | 2   | available     | available |

| 0x00FA0000    | 0x00FA3FFF  | 16 KB data Flash | 3   | available     | available |

| 0x00FA4000    | 0x00FA7FFF  | 16 KB data Flash | 3   | available     | available |

| 0x00FA8000    | 0x00FABFFF  | 16 KB data Flash | 3   | available     | available |

| 0x00FAC000    | 0x00FAFFFF  | 16 KB data Flash | 3   | available     | available |

| 0x00FB0000    | 0x00FB7FFF  | 32 KB data Flash | 2   | not available | available |

| 0x00FB8000    | 0x00FBFFFF  | 32 KB data flash | 3   | not available | available |

Table 3.

MPC5748G Family Comparison - NVM Memory Map 2

Table 4.

MPC5748G Family Comparison - RAM Memory Map

| Start Address | End Address | Allocated size [KB] | MPC5747C      | MPC5748C<br>MPC5746G<br>MPC5747G<br>MPC5748G |

|---------------|-------------|---------------------|---------------|----------------------------------------------|

| 0x4000000     | 0x40001FFF  | 8                   | available     | available                                    |

| 0x40002000    | 0x4000FFFF  | 56                  | available     | available                                    |

| 0x40010000    | 0x4001FFFF  | 64                  | available     | available                                    |

| 0x40020000    | 0x4003FFFF  | 128                 | available     | available                                    |

| 0x40040000    | 0x4007FFFF  | 256                 | available     | available                                    |

| 0x40080000    | 0x400BFFFF  | 256                 | not available | available                                    |

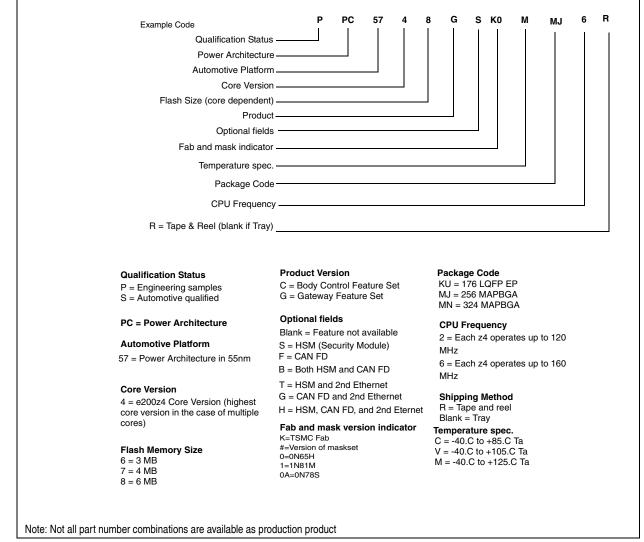

## 3 Ordering parts

## 3.1 Determining valid orderable parts

To determine the orderable part numbers for this device, go to www.nxp.com and perform a part number search for the following device number: MPC5748G.

## 3.2 Ordering Information

## 4 General

### 4.1 Absolute maximum ratings

### NOTE

Functional operating conditions appear in the DC electrical characteristics. Absolute maximum ratings are stress ratings only, and functional operation at the maximum values is not guaranteed. See footnotes in Table 5 for specific conditions

Stress beyond the listed maximum values may affect device reliability or cause permanent damage to the device.

| Symbol                                                                        | Parameter                                                                          | Conditions <sup>1</sup>                                                                 | Min         | Max                                                                                            | Unit |

|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------|------------------------------------------------------------------------------------------------|------|

| $\begin{array}{c} V_{DD\_HV\_A},V_{DD\_HV\_B},\\ V_{DD\_HV\_C}^2 \end{array}$ | 3.3 V - 5. 5V input/output supply voltage                                          |                                                                                         | -0.3        | 6.0                                                                                            | V    |

| V <sub>DD_HV_FLA</sub> <sup>3, 4</sup>                                        | 3.3 V flash supply voltage (when supplying from an external source in bypass mode) |                                                                                         | -0.3        | 3.63                                                                                           | V    |

| V <sub>DD_LP_DEC</sub> <sup>5</sup>                                           | Decoupling pin for low power regulators <sup>6</sup>                               | —                                                                                       | -0.3        | 1.32                                                                                           | V    |

| V <sub>DD_HV_ADC1_REF</sub> <sup>7</sup>                                      | 3.3 V / 5.0 V ADC1 high reference voltage                                          | _                                                                                       | -0.3        | 6                                                                                              | V    |

| V <sub>DD_HV_ADC0</sub>                                                       | 3.3 V to 5.5V ADC supply voltage                                                   | _                                                                                       | -0.3        | 6.0                                                                                            | V    |

| V <sub>DD_HV_ADC1</sub>                                                       |                                                                                    |                                                                                         |             |                                                                                                |      |

| V <sub>SS_HV_ADC0</sub>                                                       | 3.3V to 5.5V ADC supply ground                                                     | _                                                                                       | -0.1        | 0.1                                                                                            | V    |

| $V_{SS_HV_ADC1}$                                                              |                                                                                    |                                                                                         |             |                                                                                                |      |

| V <sub>DD_LV</sub>                                                            | Core logic supply voltage                                                          | _                                                                                       | -0.3        | 1.32                                                                                           | V    |

| V <sub>INA</sub>                                                              | Voltage on analog pin with respect to ground (V $_{\rm SS\_HV}$ )                  | _                                                                                       | -0.3        | Min (V <sub>DD_HV_x</sub> ,<br>V <sub>DD_HV_ADCx</sub> ,<br>V <sub>DD_ADCx_REF</sub> )<br>+0.3 | V    |

| V <sub>IN</sub>                                                               | Voltage on any digital pin with respect to ground (V_{SS_HV})                      | Relative to<br>V <sub>DD_HV_A</sub> ,<br>V <sub>DD_HV_B</sub> ,<br>V <sub>DD_HV_C</sub> | -0.3        | V <sub>DD_HV_x</sub> + 0.3                                                                     | V    |

| I <sub>INJPAD</sub>                                                           | Injected input current on any pin during overload condition                        | Always                                                                                  | -5          | 5                                                                                              | mA   |

| I <sub>INJSUM</sub>                                                           | Absolute sum of all injected input currents during overload condition              | _                                                                                       | -50         | 50                                                                                             | mA   |

| T <sub>ramp</sub>                                                             | Supply ramp rate                                                                   | _                                                                                       | 0.5 V / min | 100V/ms                                                                                        | _    |

| T <sub>A</sub> <sup>8</sup>                                                   | Ambient temperature                                                                | _                                                                                       | -40         | 125                                                                                            | °C   |

| T <sub>STG</sub>                                                              | Storage temperature                                                                | _                                                                                       | -55         | 165                                                                                            | °C   |

Table 5. Absolute maximum ratings

1. All voltages are referred to VSS\_HV unless otherwise specified

- 2. VDD\_HV\_B and VDD\_HV\_C are common together on the 176 LQFP-EP package.

- 3. VDD\_HV\_FLA must be connected to VDD\_HV\_A when VDD\_HV\_A = 3.3V

- 4. VDD\_HV\_FLA must be disconnected from ANY power sources when VDD\_HV\_A = 5V

- 5. This pin should be decoupled with low ESR 1  $\mu F$  capacitor.

- 6. Not available for input voltage, only for decoupling internal regulators

- 7. 10-bit ADC does not have dedicated reference and its reference is double bonded to 10-bit ADC supply(VDD\_HV\_ADC0).

- 8. T<sub>J</sub>=150°C. Assumes T<sub>A</sub>=125°C

- Assumes maximum θJA. SeeThermal attributes

## 4.3 Voltage regulator electrical characteristics

The voltage regulator is composed of the following blocks:

- Choice of generating supply voltage for the core area.

- Control of external NPN ballast transistor

- Connecting an external 1.25 V (nominal) supply directly without the NPN ballast

- Internal generation of the 3.3 V flash supply when device connected in 5V applications

- External bypass of the 3.3 V flash regulator when device connected in 3.3V applications

- Low voltage detector low threshold (LVD\_IO\_A\_LO) for V<sub>DD\_HV\_IO\_A supply</sub>

- Low voltage detector high threshold (LVD\_IO\_A\_Hi) for V<sub>DD\_HV\_IO\_A</sub> supply

- Various low voltage detectors (LVD\_LV\_x)

- High voltage detector (HVD\_LV\_cold) for 1.2 V digital core supply (VDD\_LV)

- Power on Reset (POR\_LV) for 1.25 V digital core supply (VDD\_LV)

- Power on Reset (POR\_HV) for 3.3 V to 5 V supply (VDD\_HV\_A)

The following bipolar transistors<sup>1</sup> are supported, depending on the device performance requirements. As a minimum the following must be considered when determining the most appropriate solution to maintain the device under its maximum power dissipation capability: current, ambient temperature, mounting pad area, duty cycle and frequency for Idd, collector voltage, etc

#### MPC5748G Microcontroller Data Sheet, Rev. 5, 07/2017

<sup>1.</sup> BCP56, MCP68 and MJD31are guaranteed ballasts.

### NOTE

The above specification is based on simulation data into an ideal lumped capacitor. Customer should use IBIS models for their specific board/loading conditions to simulate the expected signal integrity and edge rates of their system.

### NOTE

The above specification is measured between 20% / 80%.

## 5.4 DC electrical specifications @ 5 V Range

# Table 17. DC electrical specifications @ 5 V Range

| Symbol                | Parameter                                                          | Va                 | lue                               | Unit |  |

|-----------------------|--------------------------------------------------------------------|--------------------|-----------------------------------|------|--|

|                       |                                                                    | Min                | Max                               |      |  |

| VDD_LV                | LV (core) Supply Voltage                                           | 1.08               | 1.32                              | V    |  |

| VDD_HV_x <sup>1</sup> | I/O Supply Voltage                                                 | 4.5                | 5.5                               | V    |  |

| Vih (pad_i_hv)        | pad_i_hv Input Buffer High Voltage                                 | 0.7*VDD_HV_x       | VDD_HV_x +<br>0.3                 | V    |  |

| Vil (pad_i_hv)        | pad_i_hv Input Buffer Low Voltage                                  | VSS_LV- 0.3        | 0.45*VDD_HV_<br>x                 | V    |  |

| Vhys (pad_i_hv)       | pad_i_hv Input Buffer Hysteresis                                   | 0.09*VDD_HV_<br>x  |                                   | V    |  |

| Vih                   | CMOS Input Buffer High Voltage (with hysteresis disabled)          | 0.55 *<br>VDD_HV_x | VDD_HV_x +<br>0.3                 | V    |  |

| Vil                   | CMOS Input Buffer Low Voltage (with hysteresis disabled)           | VSS_LV - 0.3       | 0.4 *<br>VDD_HV_x                 | V    |  |

| Vhys                  | CMOS Input Buffer Hysteresis                                       | 0.09 *<br>VDD_HV_x |                                   | V    |  |

| Vih_hys               | CMOS Input Buffer High Voltage (with hysteresis enabled)           | 0.65*<br>VDD_HV_x  | VDD_HV_x +<br>0.3                 | V    |  |

| Vil_hys               | CMOS Input Buffer Low Voltage (with hysteresis enabled)            | VSS_LV - 0.3       | 0.35*VDD_HV_<br>x                 | V    |  |

| Pull_IIH (pad_i_hv)   | Weak Pullup Current Low                                            | 23                 |                                   | μA   |  |

| Pull_IIH (pad_i_hv)   | Weak Pullup Current High                                           |                    | 82                                | μA   |  |

| Pull_IIL (pad_i_hv)   | Weak Pulldown Current <sup>3</sup> Low                             | 40                 |                                   | μA   |  |

| Pull_IIL (pad_i_hv)   | Weak Pulldown Current <sup>2</sup> High                            |                    | 130                               | μA   |  |

| Pull_loh              | Weak Pullup Current <sup>4</sup>                                   | 30                 | 80                                | μA   |  |

| Pull_lol              | Weak Pulldown Current <sup>5</sup>                                 | 30                 | 80                                | μA   |  |

| linact_d              | Digital Pad Input Leakage Current (weak pull inactive)             | -2.5               | 2.5                               | μA   |  |

| Voh                   | Output High Voltage <sup>6</sup>                                   | 0.8 *<br>VDD_HV_x  | —                                 | V    |  |

| Vol                   | Output Low Voltage <sup>7</sup><br>Output Low Voltage <sup>8</sup> | _                  | 0.2 *<br>VDD_HV_x<br>0.1*VDD_HV_x | V    |  |

Table continues on the next page...

## 5.6 PORST electrical specifications

### Table 19. PORST electrical specifications

| Symbol               | Parameter                      |      | Value                       |     |    |

|----------------------|--------------------------------|------|-----------------------------|-----|----|

|                      |                                | Min  | Тур                         | Max |    |

| W <sub>FPORST</sub>  | PORST input filtered pulse     | —    | _                           | 200 | ns |

| W <sub>NFPORST</sub> | PORST input not filtered pulse | 1000 |                             | —   | ns |

| V <sub>IH</sub>      | Input high level               | —    | 0.65 x V <sub>DD_HV_A</sub> | —   | V  |

| V <sub>IL</sub>      | Input low level                | _    | 0.35 x V <sub>DD_HV_A</sub> |     | V  |

## 6 Peripheral operating requirements and behaviours

## 6.1 Analog

### 6.1.1 ADC electrical specifications

The device provides a 12-bit Successive Approximation Register (SAR) Analog-to-Digital Converter.

| Symbol               | Characteristic <sup>1</sup> | Typ <sup>2</sup> | Factory F<br>Programming <sup>3, 4</sup> |                                 | Field Update                           |                   |                     |    |

|----------------------|-----------------------------|------------------|------------------------------------------|---------------------------------|----------------------------------------|-------------------|---------------------|----|

|                      |                             |                  | Initial<br>Max                           | Initial<br>Max, Full<br>Temp    | Typical<br>End of<br>Life <sup>5</sup> | Lifeti            | me Max <sup>6</sup> |    |

|                      |                             |                  | 20°C ≤T <sub>A</sub><br>≤30°C            | -40°C ≤T <sub>J</sub><br>≤150°C | -40°C ≤T <sub>J</sub><br>≤150°C        | ≤ 1,000<br>cycles | ≤ 250,000<br>cycles |    |

| t <sub>32kers</sub>  | 32 KB Block erase time      | 217              | 360                                      | 390                             | 310                                    | 1,200             |                     | ms |

| t <sub>32kpgm</sub>  | 32 KB Block program time    | 69               | 100                                      | 110                             | 90                                     | 1,200             |                     | ms |

| t <sub>64kers</sub>  | 64 KB Block erase time      | 315              | 490                                      | 590                             | 420                                    | 1,600             |                     | ms |

| t <sub>64kpgm</sub>  | 64 KB Block program time    | 138              | 180                                      | 210                             | 170                                    | 1,600             |                     | ms |

| t <sub>256kers</sub> | 256 KB Block erase time     | 884              | 1,520                                    | 2,030                           | 1,080                                  | 4,000             |                     | ms |

| t <sub>256kpgm</sub> | 256 KB Block program time   | 552              | 720                                      | 880                             | 650                                    | 4,000             |                     | ms |

#### Table 30. Flash memory program and erase specifications (continued)

1. Program times are actual hardware programming times and do not include software overhead. Block program times assume quad-page programming.

2. Typical program and erase times represent the median performance and assume nominal supply values and operation at 25 °C. Typical program and erase times may be used for throughput calculations.

- 3. Conditions:  $\leq$  150 cycles, nominal voltage.

- 4. Plant Programing times provide guidance for timeout limits used in the factory.

5. Typical End of Life program and erase times represent the median performance and assume nominal supply values. Typical End of Life program and erase values may be used for throughput calculations.

6. Conditions:  $-40^{\circ}C \le T_J \le 150^{\circ}C$ , full spec voltage.

### 6.3.2 Flash memory Array Integrity and Margin Read specifications Table 31. Flash memory Array Integrity and Margin Read specifications

| Symbol                 | Characteristic                                                | Min    | Typical | Max                          | Units |

|------------------------|---------------------------------------------------------------|--------|---------|------------------------------|-------|

| t <sub>ai16kseq</sub>  | Array Integrity time for sequential sequence on 16 KB block.  | -      | _       | 512 x<br>Tperiod x<br>Nread  | _     |

| t <sub>ai32kseq</sub>  | Array Integrity time for sequential sequence on 32 KB block.  | -      | _       | 1024 x<br>Tperiod x<br>Nread | _     |

| t <sub>ai64kseq</sub>  | Array Integrity time for sequential sequence on 64 KB block.  | _      | _       | 2048 x<br>Tperiod x<br>Nread | _     |

| tai256kseq             | Array Integrity time for sequential sequence on 256 KB block. | -      | _       | 8192 x<br>Tperiod x<br>Nread | _     |

| t <sub>mr16kseq</sub>  | Margin Read time for sequential sequence on 16 KB block.      | 73.81  | —       | 110.7                        | μs    |

| t <sub>mr32kseq</sub>  | Margin Read time for sequential sequence on 32 KB block.      | 128.43 | —       | 192.6                        | μs    |

| t <sub>mr64kseq</sub>  | Margin Read time for sequential sequence on 64 KB block.      | 237.65 |         | 356.5                        | μs    |

| t <sub>mr256kseq</sub> | Margin Read time for sequential sequence on 256 KB block.     | 893.01 | _       | 1,339.5                      | μs    |

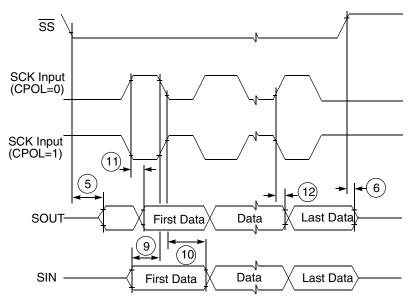

**Communication interfaces**

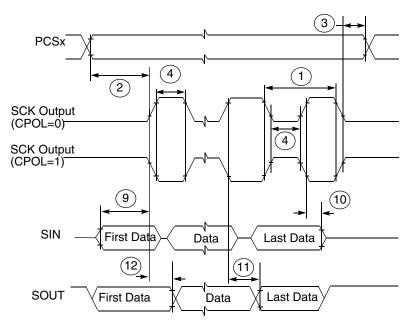

Figure 11. DSPI classic SPI timing — slave, CPHA = 1

Figure 12. DSPI modified transfer format timing — master, CPHA = 0

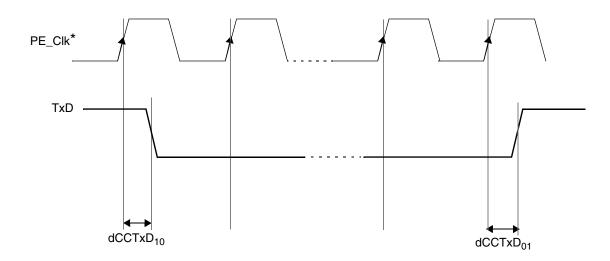

| Name                 | Description <sup>1</sup>                                                               | Min | Max | Unit |

|----------------------|----------------------------------------------------------------------------------------|-----|-----|------|

| dCCTxD <sub>01</sub> | Sum of delay between Clk to Q of the last FF and the final output buffer, rising edge  | —   | 25  | ns   |

| dCCTxD <sub>10</sub> | Sum of delay between Clk to Q of the last FF and the final output buffer, falling edge | —   | 25  | ns   |

### Table 39. TxD output characteristics (continued)

1. All parameters specified for  $V_{DD_HV_IOx} = 3.3 \text{ V} - 5\%$ , +±10%, TJ = -40 °C / 150 °C, TxD pin load maximum 25 pF. 2. For 3.3 V ± 10% operation, this specification is 10 ns.

\*FlexRay Protocol Engine Clock

### Figure 20. TxD Signal propagation delays

#### 6.4.2.4 **RxD**

| Name                 | Description <sup>1</sup>                                                             | Min | Max | Unit |

|----------------------|--------------------------------------------------------------------------------------|-----|-----|------|

| C_CCRxD              | Input capacitance on<br>RxD pin                                                      | —   | 7   | pF   |

| uCCLogic_1           | Threshold for detecting logic high                                                   | 35  | 70  | %    |

| uCCLogic_0           | Threshold for detecting<br>logic low                                                 | 30  | 65  | %    |

| dCCRxD <sub>01</sub> | Sum of delay from<br>actual input to the D<br>input of the first FF,<br>rising edge  | _   | 10  | ns   |

| dCCRxD <sub>10</sub> | Sum of delay from<br>actual input to the D<br>input of the first FF,<br>falling edge | _   | 10  | ns   |

#### MPC5748G Microcontroller Data Sheet, Rev. 5, 07/2017

## 6.4.4 Ethernet switching specifications

The following timing specs are defined at the chip I/O pin and must be translated appropriately to arrive at timing specs/constraints for the physical interface.

### 6.4.4.1 MII signal switching specifications

The following timing specs meet the requirements for MII style interfaces for a range of transceiver devices.

### NOTE

ENET0 supports the following xMII interfaces: MII, MII\_Lite and RMII. ENET1 supports the following xMII interfaces: MII\_Lite.

### NOTE

It is only possible to use ENET0 and ENET1 simultaneously when both are configured for MII\_Lite.

### NOTE

In certain pinout configurations ENET1 MII-Lite signals can be across multiple VDD\_HV\_A/B/C domains. If these configuration are used, VDD\_HV IO domains need to be at the same voltage (for example: 3.3V)

| Symbol | Description                           | Min. | Max. | Unit   |

|--------|---------------------------------------|------|------|--------|

| _      | RXCLK frequency                       | —    | 25   | MHz    |

| MII1   | RXCLK pulse width high                | 35%  | 65%  | RXCLK  |

|        |                                       |      |      | period |

| MII2   | RXCLK pulse width low                 | 35%  | 65%  | RXCLK  |

|        |                                       |      |      | period |

| MII3   | RXD[3:0], RXDV, RXER to RXCLK setup   | 5    | _    | ns     |

| MII4   | RXCLK to RXD[3:0], RXDV, RXER hold    | 5    | _    | ns     |

|        | TXCLK frequency                       | —    | 25   | MHz    |

| MII5   | TXCLK pulse width high                | 35%  | 65%  | TXCLK  |

|        |                                       |      |      | period |

| MII6   | TXCLK pulse width low                 | 35%  | 65%  | TXCLK  |

|        |                                       |      |      | period |

| MII7   | TXCLK to TXD[3:0], TXEN, TXER invalid | 2    | _    | ns     |

| MII8   | TXCLK to TXD[3:0], TXEN, TXER valid   | -    | 25   | ns     |

### Table 42. MII signal switching specifications

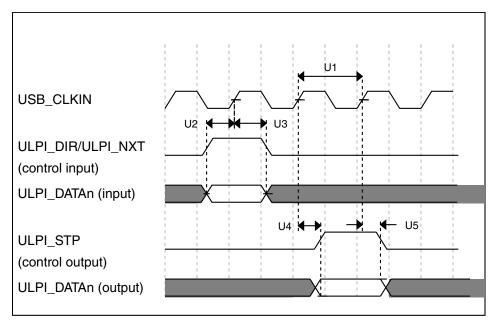

Figure 25. ULPI timing diagram

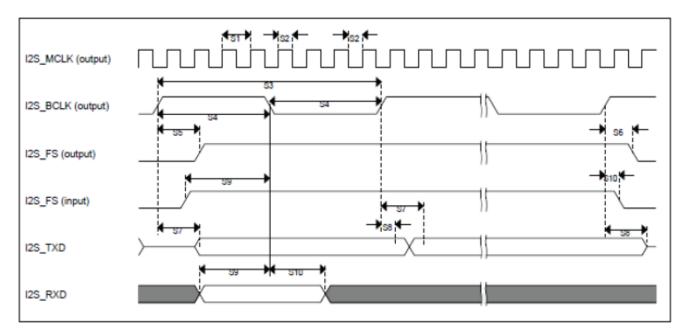

## 6.4.7 SAI electrical specifications

All timing requirements are specified relative to the clock period or to the minimum allowed clock period of a device

Table 48. Master mode SAI Timing

| no  | Parameter                                  | Va  | Unit |                |

|-----|--------------------------------------------|-----|------|----------------|

|     |                                            | Min | Мах  |                |

|     | Operating Voltage                          | 2.7 | 3.6  | V              |

| S1  | SAI_MCLK cycle time                        | 40  | -    | ns             |

| S2  | SAI_MCLK pulse width high/low              | 45% | 55%  | MCLK<br>period |

| S3  | SAI_BCLK cycle time                        | 80  | -    | BCLK<br>period |

| S4  | SAI_BCLK pulse width high/low              | 45% | 55%  | ns             |

| S5  | SAI_BCLK to SAI_FS output valid            | -   | 15   | ns             |

| S6  | SAI_BCLK to SAI_FS output invalid          | 0   | -    | ns             |

| S7  | SAI_BCLK to SAI_TXD valid                  | -   | 15   | ns             |

| S8  | SAI_BCLK to SAI_TXD invalid                | 0   | -    | ns             |

| S9  | SAI_RXD/SAI_FS input setup before SAI_BCLK | 28  | -    | ns             |

| S10 | SAI_RXD/SAI_FS input hold after SAI_BCLK   | 0   | -    | ns             |

#### **USB electrical specifications**

### Figure 26. Master mode SAI Timing

### Table 49. Slave mode SAI Timing

| No  | Parameter                                 | Value |     | Unit        |

|-----|-------------------------------------------|-------|-----|-------------|

|     |                                           | Min   | Max |             |

|     | Operating Voltage                         | 2.7   | 3.6 | V           |

| S11 | SAI_BCLK cycle time (input)               | 80    | -   | ns          |

| S12 | SAI_BCLK pulse width high/low (input)     | 45%   | 55% | BCLK period |

| S13 | SAI_FS input setup before SAI_BCLK        | 10    | -   | ns          |

| S14 | SAI_FS input hold after SAI_BCLK          | 2     | -   | ns          |

| S15 | SAI_BCLK to SAI_TXD/SAI_FS output valid   | -     | 28  | ns          |

| S16 | SAI_BCLK to SAI_TXD/SAI_FS output invalid | 0     | -   | ns          |

| S17 | SAI_RXD setup before SAI_BCLK             | 10    | -   | ns          |

| S18 | SAI_RXD hold after SAI_BCLK               | 2     | -   | ns          |

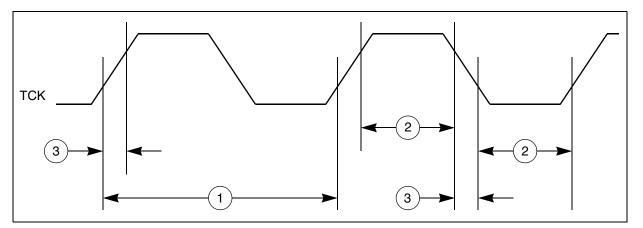

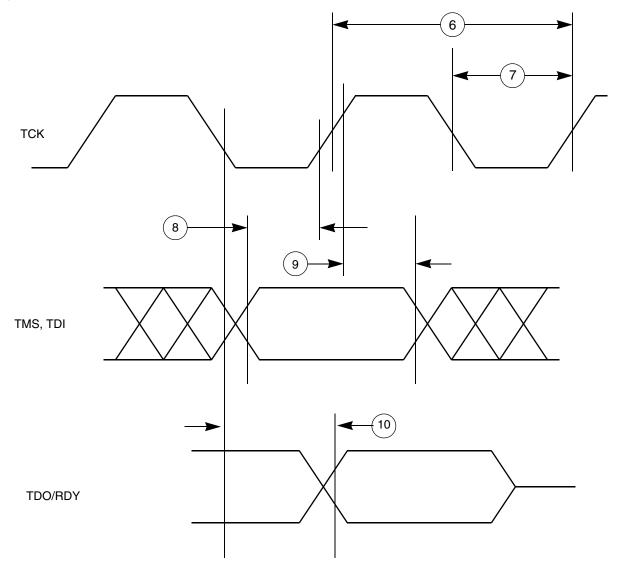

Figure 28. JTAG test clock input timing

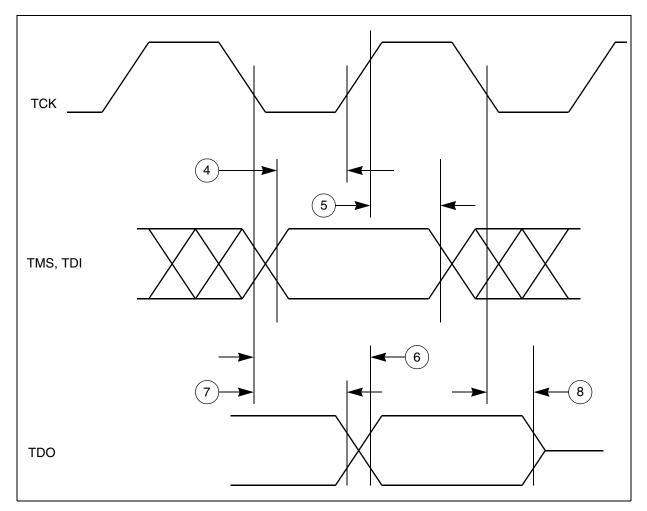

Figure 29. JTAG test access port timing

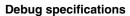

Figure 30. JTAG boundary scan timing

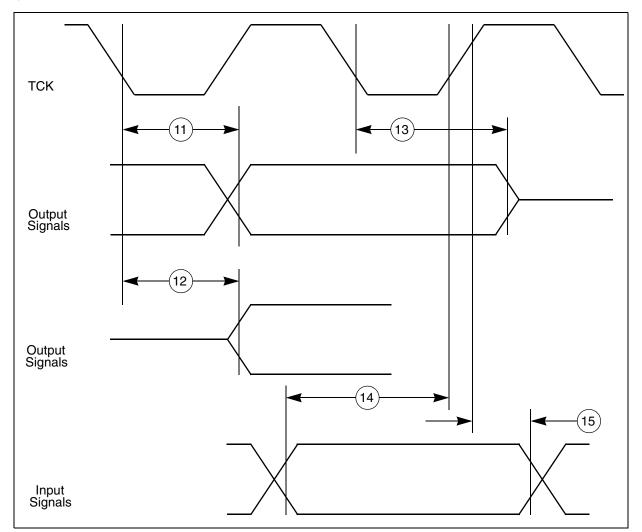

## 6.5.2 Nexus timing

### Table 51. Nexus debug port timing <sup>1</sup>

| No. | Symbol                                                              | Parameter                                                             | Condition | Min  | Max  | Unit  |

|-----|---------------------------------------------------------------------|-----------------------------------------------------------------------|-----------|------|------|-------|

|     |                                                                     |                                                                       | S         |      |      |       |

| 1   | t <sub>MCYC</sub>                                                   | MCKO Cycle Time                                                       | —         | 15.6 | —    | ns    |

| 2   | t <sub>MDC</sub>                                                    | MCKO Duty Cycle                                                       | _         | 40   | 60   | %     |

| 3   | t <sub>MDOV</sub>                                                   | t <sub>MDOV</sub> MCKO Low to MDO, MSEO, EVTO Data Valid <sup>2</sup> |           | -0.1 | 0.25 | tMCYC |

| 4   | t <sub>EVTIPW</sub>                                                 | EVTI Pulse Width                                                      | —         | 4    | —    | tTCYC |

| 5   | t <sub>EVTOPW</sub>                                                 | PW EVTO Pulse Width                                                   |           | 1    | _    | tMCYC |

| 6   | t <sub>TCYC</sub> TCK Cycle Time <sup>3</sup>                       |                                                                       | —         | 62.5 | —    | ns    |

| 7   | t <sub>TDC</sub>                                                    | TCK Duty Cycle                                                        | —         | 40   | 60   | %     |

| 8   | t <sub>NTDIS</sub> , TDI, TMS Data Setup Time<br>t <sub>NTMSS</sub> |                                                                       |           | 8    |      | ns    |

Table continues on the next page...

**Debug specifications**

Figure 33. Nexus TDI, TMS, TDO timing

## 6.5.3 WKPU/NMI timing

### Table 52. WKPU/NMI glitch filter

| No. | Symbol               | Parameter                        | Min | Тур | Max | Unit |

|-----|----------------------|----------------------------------|-----|-----|-----|------|

| 1   | W <sub>FNMI</sub>    | NMI pulse width that is rejected | _   | —   | 20  | ns   |

| 2   | W <sub>NFNMI</sub> D | NMI pulse width that is passed   | 400 |     |     | ns   |

## 9 Pinouts

## 9.1 Package pinouts and signal descriptions

For package pinouts and signal descriptions, refer to the Reference Manual.

## 10 Reset sequence

This section describes different reset sequences and details the duration for which the device remains in reset condition in each of those conditions.

## 10.1 Reset sequence duration

Table 54 specifies the minimum and the maximum reset sequence duration for the five different reset sequences described in Reset sequence description.

| No. | Symbol            | Parameter                                      | T <sub>Reset</sub> |                  | Unit |    |

|-----|-------------------|------------------------------------------------|--------------------|------------------|------|----|

|     |                   |                                                | Min                | Typ <sup>1</sup> | Max  |    |

| 1   | T <sub>DRB</sub>  | Destructive Reset Sequence, BIST enabled       | 5.730              | 7.796            |      | ms |

| 2   | T <sub>DR</sub>   | Destructive Reset Sequence, BIST disabled      | 0.111              | 0.182            |      | ms |

| 3   | T <sub>ERLB</sub> | External Reset Sequence Long, Unsecure Boot    | 5.729              | 7.793            |      | ms |

| 4   | T <sub>FRL</sub>  | Functional Reset Sequence Long, Unsecure Boot  | 0.110              | 0.179            |      | ms |

| 5   | T <sub>FRS</sub>  | Functional Reset Sequence Short, Unsecure Boot | 0.007              | 0.009            |      | ms |

Table 54. RESET sequences

1. The Typ value is applicable only if the reset sequence duration is not prolonged by an extended assertion of RESET\_B by an external reset generator.

## 10.2 BAF execution duration

Following table specifies the typical BAF execution time in case BAF boot header is present at first location (Typical) and last location (worst case). Total Boot time is the sum of reset sequence duration and BAF execution time.

| BAF execution<br>duration                                | Min | Тур | Мах | Unit |

|----------------------------------------------------------|-----|-----|-----|------|

| BAF execution time<br>(boot header at first<br>location) | -   | 200 | -   | μs   |

| BAF execution time<br>(boot header at last<br>location)  | -   | 320 | -   | μs   |

Table 55. BAF execution duration

## 10.3 Reset sequence description

The figures in this section show the internal states of the device during the five different reset sequences. The dotted lines in the figures indicate the starting point and the end point for which the duration is specified in Table 54.

With the beginning of DRUN mode, the first instruction is fetched and executed. At this point, application execution starts and the internal reset sequence is finished.

The following figures show the internal states of the device during the execution of the reset sequence and the possible states of the RESET\_B signal pin.

### NOTE

RESET\_B is a bidirectional pin. The voltage level on this pin can either be driven low by an external reset generator or by the device internal reset circuitry. A high level on this pin can only be generated by an external pullup resistor which is strong enough to overdrive the weak internal pulldown resistor. The rising edge on RESET\_B in the following figures indicates the time when the device stops driving it low. The reset sequence durations given in Table 54 are applicable only if the internal reset sequence is not prolonged by an external reset generator keeping RESET\_B asserted low beyond the last Phase3.

| Rev. No. | Date | Substantial Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |      | <ul> <li>Removed row for symbol 'V<sub>SS_LV</sub>'</li> <li>Removed footnote from 'Max' column of symbols 'V<sub>DD_HV_ADC0</sub>' and 'V<sub>DD_HV_ADC1</sub>'</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|          |      | <ul> <li>In section: Recommended operating conditions</li> <li>In table: Recommended operating conditions (V<sub>DD_HV_x</sub> = 5 V)</li> <li>Added footnote to 'Conditions' cloumn</li> <li>Updated footnote from symbols 'V<sub>DD_HV_A'</sub>, 'V<sub>DD_HV_B</sub>', and 'V<sub>DD_HV_C</sub>'</li> <li>Removed footnote from symbols 'V<sub>SS_HV</sub>'</li> <li>Updated 'Parameter' column for symbol 'V<sub>DD_HV_ADC1_REF</sub>'</li> <li>'V<sub>DD_HV_ADC1_REF</sub>', 'V<sub>DD_LV</sub>'</li> <li>Updated 'Min' columnn of symbol 'V<sub>DD_HV_ADC0</sub>' and 'V<sub>DD_HV_ADC1</sub>'</li> <li>Updated 'Parameter', 'Min' 'Max' column for symbol 'V<sub>SS_HV_ADC0</sub>' and 'V<sub>SS_HV_ADC0</sub>' and 'V<sub>SS_HV_ADC1</sub>'</li> <li>Added footnote to symbol 'V<sub>DD_LV</sub>'</li> <li>Removed row for symbol 'V<sub>DD_LV</sub>'</li> <li>Added row for symbol 'V<sub>SS_LV</sub>'</li> <li>Added row for symbol 'V<sub>SS_LV</sub>'</li> <li>Added row for symbol 'V<sub>IN1_CMP_REF</sub>' and corresponding footnotes to the symbol</li> </ul>                                                                                                                                                                                                                                                                                           |

|          |      | <ul> <li>In section: Voltage regulator electrical characteristics         <ul> <li>In table: Voltage regulator electrical specifications</li> <li>Added note to symbol 'Cbe_fpreg'</li> </ul> </li> <li>In section: Voltage monitor electrical characteristics         <ul> <li>In table: Voltage monitor electrical characteristics</li> <li>In table: Voltage monitor electrical characteristics</li> <li>Updated column 'Parameter', 'Min' and 'Max' (of fall/rise trimmed condition) for symbol 'V<sub>HVD_LV_cold</sub>' and 'V<sub>LVD_IO_A_HI'</sub></li> <li>Updated column 'Parameter', 'Min' and 'Typ' (of fall/rise trimmed condition) for symbol) 'V<sub>LVD_LV_PD2_hot</sub>', 'V<sub>LVD_LV_PD2_cold LV'</sub></li> <li>Updated column 'Parameter' for symbol 'V<sub>LVD_LV_PD0_hot</sub>'</li> <li>Updated column 'Typ' and 'Max' (of fall/rise trimmed condition) for symbol) 'V<sub>LVD_FLASH</sub>'</li> <li>Updated footnote on symbol 'V<sub>LVD_IO_A_LO</sub>' and 'V<sub>LVD_IO_A_HI'</sub></li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                 |

|          |      | <ul> <li>In section: Supply current characteristics</li> <li>In table: Current consumption characteristics</li> <li>Updated column 'Typ' for symbol 'I<sub>DD_FULL</sub>' for temperature 85, 105, 125</li> <li>Updated column 'Typ' for symbol 'I<sub>DD_GWY</sub>' for temperature 85, 105, 125 and column 'Max' for temperature 105</li> <li>Updated column 'Typ' for symbol 'I<sub>DD_BODY1</sub>' for temperature 85, 105, 125 updated column 'Typ' for symbol 'I<sub>DD_BODY2</sub>' for temperature 85, 105, 125</li> <li>Updated column 'Typ' for symbol 'I<sub>DD_BODY2</sub>' for temperature 85, 105, 125 and 'Max' for temperature 125</li> <li>Added 'Typ' value for temperature 25 for symbol 'I<sub>DD_STOP</sub>'</li> <li>Updated column 'Typ' and 'Max' for symbol 'I<sub>DD_STOP</sub>' for temperature 85, 105, 125</li> <li>In table: Low Power Unit (LPU) Current consumption characteristics</li> <li>Updated column 'Typ' for symbol 'LPU_RUN' for tempeature 25 and 125</li> <li>Added 'Typ' and 'Max' value for temperature 85 and 105 for symbol 'LPU_RUN'</li> <li>Updated column 'Typ' for symbol 'LPU_STOP' for tempeature 25 and 125</li> <li>Added 'Typ' and 'Max' value for temperature 85 and 105 for symbol 'LPU_STOP'</li> <li>In table: STANDBY Current consumption characteristics</li> <li>Updated to have one STANDBY</li> </ul> |

### Table 56. Revision History (continued)

• In section: I/O parameters

Table continues on the next page...

#### How to Reach Us:

Home Page: nxp.com

Web Support: nxp.com/support Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C-5, CodeTest, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorlQ, QorlQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. ARM, AMBA, ARM Powered, Artisan, Cortex, Jazelle, Keil, SecurCore, Thumb, TrustZone, and µVision are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. ARM7, ARM9, ARM11, big.LITTLE, CoreLink, CoreSight, DesignStart, Mali, mbed, NEON, POP, Sensinode, Socrates, ULINK and Versatile are trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© 2013–2017 NXP B.V.

Document Number MPC5748G Revision 5, 07/2017