Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | e200z2, e200z4, e200z4                                                  |

| Core Size                  | 32-Bit Tri-Core                                                         |

| Speed                      | 80MHz/160MHz                                                            |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, LINbus, SAI, SPI, USB, USB OTG      |

| Peripherals                | DMA, LVD, POR, WDT                                                      |

| Number of I/O              | 129                                                                     |

| Program Memory Size        | 4MB (4M x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 768K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                               |

| Data Converters            | A/D 80x10b, 64x12b                                                      |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 176-LQFP Exposed Pad                                                    |

| Supplier Device Package    | 176-LQFP (24x24)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5747gsk1mku6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Timer

- 16 Periodic Interrupt Timers (PITs)

- Three System Timer Module (STM)

- Four Software WatchDog Timers (SWT)

- 96 Configurable Enhanced Modular Input Output Subsystem (eMIOS) channels

- Device/board boundary Scan testing supported with per Joint Test Action Group (JTAG) of IEEE (IEEE 1149.1) and 1149.7 (cJTAG)

- Security

- Hardware Security Module (HSMv2)

- Password and Device Security (PASS and TDM) supporting advanced censorship and life-cycle management

- One Fault Collection and Control Unit (FCCU) to collect faults and issue interrupts

- Functional Safety

- ISO26262 ASIL compliance

- Multiple operating modes

- Includes enhanced low power operation

#### General

### Table 6. Recommended operating conditions ( $V_{DD_HV_x} = 3.3 V$ ) (continued)

| Symbol         | Parameter                       | Conditions <sup>1</sup>       | Min <sup>2</sup> | Max | Unit |

|----------------|---------------------------------|-------------------------------|------------------|-----|------|

| T <sub>A</sub> | Ambient temperature under bias  | f <sub>CPU</sub> ≤ 160<br>MHz | -40              | 125 | °C   |

| TJ             | Junction temperature under bias | _                             | -40              | 150 | °C   |

1. All voltages are referred to  $V_{SS\ HV}$  unless otherwise specified

- 2. Device will be functional down (and electrical specifications as per various datasheet parameters will be guaranteed) to the point where one of the LVD/HVD resets the device. When voltage drops outside range for an LVD/HVD, device is reset.

- 3. VDD\_HV\_FLA must be connected to VDD\_HV\_A when VDD\_HV\_A = 3.3V

- 4. VDD\_LV supply pins should never be grounded (through a small impedance). If these are not driven, they should only be left floating.

5. VIN1\_CMP\_REF  $\leq$  VDD\_HV\_A

6. This supply is shorted VDD\_HV\_A on lower packages.

### NOTE

If VDD\_HV\_A is in 5V range, it is necessary to use internal Flash supply 3.3V regulator. VDD\_HV\_FLA should not be supplied externally and should only have decoupling capacitor.

### Table 7. Recommended operating conditions ( $V_{DD HV x} = 5 V$ )

| Symbol                                             | Parameter                                                   | Conditions <sup>1</sup>       | Min <sup>2</sup>                                   | Max  | Unit |

|----------------------------------------------------|-------------------------------------------------------------|-------------------------------|----------------------------------------------------|------|------|

| V <sub>DD_HV_A</sub>                               | HV IO supply voltage                                        | —                             | 4.5                                                | 5.5  | V    |

| V <sub>DD_HV_B</sub>                               |                                                             |                               |                                                    |      |      |

| V <sub>DD_HV_C</sub>                               |                                                             |                               |                                                    |      |      |

| V <sub>DD_HV_FLA</sub> <sup>3</sup>                | HV flash supply voltage                                     | _                             | 3.15                                               | 3.6  | V    |

| V <sub>DD_HV_ADC1_REF</sub>                        | HV ADC1 high reference voltage                              | _                             | 3.15                                               | 5.5  | V    |

| V <sub>DD_HV_ADC0</sub><br>V <sub>DD_HV_ADC1</sub> | HV ADC supply voltage                                       | _                             | max(VDD_H<br>V_A,VDD_H<br>V_B,VDD_H<br>V_C) - 0.05 | 5.5  | V    |

| V <sub>SS_HV_ADC0</sub><br>V <sub>SS_HV_ADC1</sub> | HV ADC supply ground                                        | _                             | -0.1                                               | 0.1  | V    |

| V <sub>DD_LV</sub> <sup>4</sup>                    | Core supply voltage                                         | _                             | 1.2                                                | 1.32 | V    |

| V <sub>IN1_CMP_REF</sub> <sup>5</sup>              | Analog Comparator DAC reference voltage                     | _                             | 3.15                                               | 5.5  | V    |

| I <sub>INJPAD</sub>                                | Injected input current on any pin during overload condition | -                             | -3.0                                               | 3.0  | mA   |

| T <sub>A</sub>                                     | Ambient temperature under bias                              | f <sub>CPU</sub> ≤ 160<br>MHz | -40                                                | 125  | °C   |

| TJ                                                 | Junction temperature under bias                             | _                             | -40                                                | 150  | °C   |

1. All voltages are referred to  $V_{SS\ HV}$  unless otherwise specified

- 2. Device will be functional down (and electrical specifications as per various datasheet parameters will be guaranteed) to the point where one of the LVD/HVD resets the device. When voltage drops outside range for an LVD/HVD, device is reset.

- 3. When VDD\_HV is in 5 V range, VDD\_HV\_FLA cannot be supplied externally. This pin is decoupled with  $C_{flash\_reg}$ .

- 4. VDD\_LV supply pins should never be grounded (through a small impedance). If these are not driven, they should only be left floating

- 5. This supply is shorted VDD\_HV\_A on lower packages.

| Symbol                                | Parameter                  | Conditions <sup>1</sup>       | Min | Тур  | Max | Unit |

|---------------------------------------|----------------------------|-------------------------------|-----|------|-----|------|

|                                       |                            | T <sub>a</sub> = 105 °C       | —   | 114  | 206 | mA   |

|                                       |                            | $T_{a} = 125 \ ^{\circ}C^{4}$ | _   | 131  | 277 | mA   |

| I <sub>DD_STOP</sub>                  | STOP mode                  | T <sub>a</sub> = 25 °C        | —   | 11   | _   | mA   |

|                                       | Operating current          | $V_{DD_{LV}} = 1.25 V$        |     |      |     |      |

|                                       |                            | T <sub>a</sub> = 85 °C        | —   | 19.8 | 105 |      |

|                                       |                            | V <sub>DD_LV</sub> = 1.25 V   |     |      |     |      |

|                                       |                            | T <sub>a</sub> = 105 °C       |     | 29   | 145 |      |

|                                       |                            | V <sub>DD_LV</sub> = 1.25 V   |     |      |     |      |

|                                       |                            | $T_a = 125 \text{ °C}^4$      | —   | 45   | 160 |      |

|                                       |                            | $V_{DD_{LV}} = 1.25 V$        |     |      |     |      |

| IDD_HV_ADC_REF <sup>11, 12</sup>      | ADC REF                    | $T_a = 25 \ ^{\circ}C$        | _   | 200  | 400 | μA   |

|                                       | Operating current          | 2 ADCs operating at 80 MHz    |     |      |     |      |

|                                       |                            | $V_{DD_HV_ADC_REF} = 3.6 V$   |     |      |     |      |

|                                       |                            | $T_a = 125 \text{ °C }^4$     | —   | 200  | 400 |      |

|                                       |                            | 2 ADCs operating at 80 MHz    |     |      |     |      |

|                                       |                            | $V_{DD_HV_ADC_REF} = 5.5 V$   |     |      |     |      |

| I <sub>DD_HV_ADCx</sub> <sup>12</sup> | ADC HV                     | T <sub>a</sub> = 25 °C        | _   | 1    | 2   | mA   |

|                                       | Operating current          | ADC operating at 80 MHz       |     |      |     |      |

|                                       |                            | $V_{DD_HV_ADC} = 3.6 V$       |     |      |     |      |

|                                       |                            | $T_{a} = 125 \ ^{\circ}C^{4}$ | _   | 1.2  | 2   |      |

|                                       |                            | ADC operating at 80 MHz       |     |      |     |      |

|                                       |                            | $V_{DD_HV_ADC} = 5.5 V$       |     |      |     |      |

| I <sub>DD_HV_FLASH</sub>              | Flash Operating            | $T_{a} = 125 \ ^{\circ}C^{4}$ | —   | 40   | 45  | mA   |

|                                       | current during read access | 3.3 V supplies                |     |      |     |      |

|                                       |                            | x MHz frequency               |     |      |     |      |

#### Table 10. Current consumption characteristics (continued)

- 1. The content of the Conditions column identifies the components that draw the specific current.

- 2. ALL Modules enabled at maximum frequency: 2 x e200Z4 @ 160 MHz, e200Z2 at 80 MHz, Platform @ 160MHz, DMA (SRAM to SRAM), all SRAMs accessed in parallel, Flash access(prefetch is disabled while buffers are enabled), HSM reading from flash at regular intervals (500 pll clock cycles), ENET0 transmitting, MLB transmitting, FlexRay transmitting, USB-SPH transmitting (USB-OTG only clocked), 2 x I2C transmitting (rest clocked), 1 x SAI transmitting (rest clocked), ADC0 converting using BCTU triggers triggered through PIT (other ADC clocked), RTC running, 3 x STM running, 2 x DSPI transmitting (rest clocked), 2 x SPI transmitting (rest clocked), 4 x CAN state machines working(rest clocked), 9 x LINFlexD transmitting (rest clocked), 1 x eMIOS clocked (used OPWFMB mode) (Others clock gated), SDHC,3 x CMP only clocked, FIRC, SIRC, FXOSC, SXOSC, PLL running. All others modules clock gated if not specifically mentioned. I/O supply current excluded.

- 3. Recommended Transistors:MJD31 @ 85°C, 105°C and 125°C.

- 4. Tj=150°C. Assumes Ta=125°C

- Assumes maximum θJA. SeeThermal attributes

- 5. Enabled Modules in Gateway mode: 2 x e200Z4 @160 MHz (Instruction and Data cache enabled), Platform @160MHz, e200Z2 at 80 MHz(Instruction cache enabled), all SRAMs accessed in parallel, Flash access(prefetch is disabled while buffers are enabled), HSM reading from flash at regular intervals(500 pll clock cycles), ENET0 transmitting, MLB transmitting, FlexRay transmitting, USB-SPH Transmitting, USB-OTG clocked, 2 x I2C transmitting, (2 x I2C clock gated), 1 x SAI transmitting (2 x SAI clock gated), ADC0 converting in continuous mode (ADC1 clock gated), PIT clocked, RTC clocked, 3 x STM clocked, 2 x DSPI transmitting(Other DSPS clock gated), 2 x SPI transmitting(Other SPIs clock gated), 4

# NOTE

The above specification is based on simulation data into an ideal lumped capacitor. Customer should use IBIS models for their specific board/loading conditions to simulate the expected signal integrity and edge rates of their system.

# NOTE

The above specification is measured between 20% / 80%.

# 5.4 DC electrical specifications @ 5 V Range

# Table 17. DC electrical specifications @ 5 V Range

| Symbol                | Parameter                                                          | Va                 | lue                               | Unit |

|-----------------------|--------------------------------------------------------------------|--------------------|-----------------------------------|------|

|                       |                                                                    | Min                | Max                               |      |

| VDD_LV                | LV (core) Supply Voltage                                           | 1.08               | 1.32                              | V    |

| VDD_HV_x <sup>1</sup> | I/O Supply Voltage                                                 | 4.5                | 5.5                               | V    |

| Vih (pad_i_hv)        | pad_i_hv Input Buffer High Voltage                                 | 0.7*VDD_HV_x       | VDD_HV_x +<br>0.3                 | V    |

| Vil (pad_i_hv)        | pad_i_hv Input Buffer Low Voltage                                  | VSS_LV- 0.3        | 0.45*VDD_HV_<br>x                 | V    |

| Vhys (pad_i_hv)       | pad_i_hv Input Buffer Hysteresis                                   | 0.09*VDD_HV_<br>x  |                                   | V    |

| Vih                   | CMOS Input Buffer High Voltage (with hysteresis disabled)          | 0.55 *<br>VDD_HV_x | VDD_HV_x +<br>0.3                 | V    |

| Vil                   | CMOS Input Buffer Low Voltage (with hysteresis disabled)           | VSS_LV - 0.3       | 0.4 *<br>VDD_HV_x                 | V    |

| Vhys                  | CMOS Input Buffer Hysteresis                                       | 0.09 *<br>VDD_HV_x |                                   | V    |

| Vih_hys               | CMOS Input Buffer High Voltage (with hysteresis enabled)           | 0.65*<br>VDD_HV_x  | VDD_HV_x +<br>0.3                 | V    |

| Vil_hys               | CMOS Input Buffer Low Voltage (with hysteresis enabled)            | VSS_LV - 0.3       | 0.35*VDD_HV_<br>x                 | V    |

| Pull_IIH (pad_i_hv)   | Weak Pullup Current Low                                            | 23                 |                                   | μA   |

| Pull_IIH (pad_i_hv)   | Weak Pullup Current High                                           |                    | 82                                | μA   |

| Pull_IIL (pad_i_hv)   | Weak Pulldown Current <sup>3</sup> Low                             | 40                 |                                   | μA   |

| Pull_IIL (pad_i_hv)   | Weak Pulldown Current <sup>2</sup> High                            |                    | 130                               | μA   |

| Pull_loh              | Weak Pullup Current <sup>4</sup>                                   | 30                 | 80                                | μA   |

| Pull_lol              | Weak Pulldown Current <sup>5</sup>                                 | 30                 | 80                                | μA   |

| linact_d              | Digital Pad Input Leakage Current (weak pull inactive)             | -2.5               | 2.5                               | μA   |

| Voh                   | Output High Voltage <sup>6</sup>                                   | 0.8 *<br>VDD_HV_x  | —                                 | V    |

| Vol                   | Output Low Voltage <sup>7</sup><br>Output Low Voltage <sup>8</sup> | _                  | 0.2 *<br>VDD_HV_x<br>0.1*VDD_HV_x | V    |

Table continues on the next page...

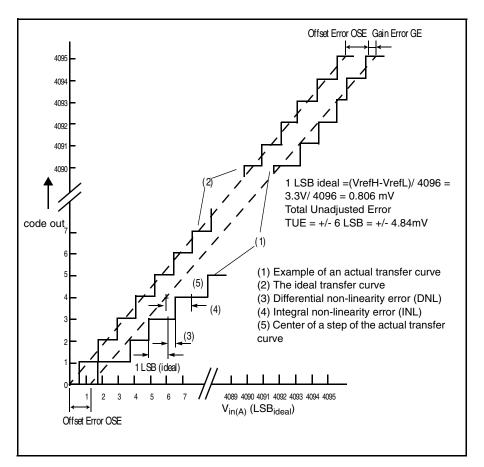

Figure 5. ADC characteristics and error definitions

| Symbol                                  | Parameter                                 | Conditions                          | Min | Typ <sup>1</sup> | Max  | Unit |

|-----------------------------------------|-------------------------------------------|-------------------------------------|-----|------------------|------|------|

| R <sub>AD</sub> <sup>6</sup>            | Internal resistance of analog source      | _                                   | -   | _                | 825  | Ω    |

| INL                                     | Integral non-linearity (precise channel)  | —                                   | -2  | _                | 2    | LSB  |

| INL                                     | Integral non-linearity (standard channel) | —                                   | -3  | —                | 3    | LSB  |

| DNL                                     | Differential non-linearity                | —                                   | -1  | —                | 1    | LSB  |

| OFS                                     | Offset error                              | —                                   | -6  | —                | 6    | LSB  |

| GNE                                     | Gain error                                | —                                   | -4  | —                | 4    | LSB  |

| ADC Analog Pad                          | Max leakage (precision channel)           | 150 °C                              | _   | _                | 250  | nA   |

| (pad going to one ADC)                  | Max leakage (standard channel)            | 150 °C                              | —   | —                | 2500 | nA   |

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | Max leakage (standard channel)            | 105 °C <sub>TA</sub>                | _   | 5                | 250  | nA   |

|                                         | Max positive/negative injection           |                                     | -5  | _                | 5    | mA   |

| TUE <sub>precision channels</sub>       | Total unadjusted error for precision      | Without current injection           | -6  | +/-4             | 6    | LSB  |

|                                         | channels                                  | With current injection              |     | +/-5             |      | LSB  |

| TUE <sub>standard/extended</sub>        | Total unadjusted error for standard/      | Without current injection           | -8  | +/-6             | 8    | LSB  |

| channels                                | extended channels                         | With current injection <sup>7</sup> |     | +/-8             |      | LSB  |

| t <sub>recovery</sub>                   | STOP mode to Run mode recovery time       |                                     |     |                  | < 1  | μs   |

#### Table 20. ADC conversion characteristics (for 12-bit) (continued)

- Active ADC input, VinA < [min(ADC\_VrefH, ADC\_ADV, VDD\_HV\_IOx)]. VDD\_HV\_IOx refers to I/O segment supply voltage. Violation of this condition would lead to degradation of ADC performance. Please refer to Table: 'Absolute maximum ratings' to avoid damage. Refer to Table: 'Recommended operating conditions (VDD\_HV\_x = 3.3 V)' for required relation between IO\_supply\_A,B,C and ADC\_Supply.</li>

- 2. The internally generated clock (known as AD\_clk or ADCK) could be same as the peripheral clock or half of the peripheral clock based on register configuration in the ADC.

- During the sample time the input capacitance C<sub>S</sub> can be charged/discharged by the external source. The internal

resistance of the analog source must allow the capacitance to reach its final voltage level within t<sub>sample</sub>. After the end of the

sample time t<sub>sample</sub>, changes of the analog input voltage have no effect on the conversion result. Values for the sample

clock t<sub>sample</sub> depend on programming.

- 4. This parameter does not include the sample time t<sub>sample</sub>, but only the time for determining the digital result and the time to load the result register with the conversion result.

- 5. Apart from tsample and tconv, few cycles are used up in ADC digital interface and hence the overall throughput from the ADC is lower.

- 6. See Figure 2.

- 7. Current injection condition for ADC channels is defined for an inactive ADC channel (on which conversion is NOT being performed), and this occurs when voltage on the ADC pin exceeds the I/O supply or ground. However, absolute maximum voltage spec on pad input (VINA, see Table: Absolute maximum ratings) must be honored to meet TUE spec quoted here

### Table 21. ADC conversion characteristics (for 10-bit)

| Symbol              | Parameter                                                                                                    | Conditions                       | Min  | Typ <sup>1</sup> | Max  | Unit |

|---------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------|------|------------------|------|------|

| f <sub>CK</sub>     | ADC Clock frequency (depends on ADC configuration) (The duty cycle depends on AD_CK <sup>2</sup> frequency.) |                                  | 15.2 | 80               | 80   | MHz  |

| f <sub>s</sub>      | Sampling frequency                                                                                           | —                                | _    | _                | 1.00 | MHz  |

| t <sub>sample</sub> | Sample time <sup>3</sup>                                                                                     | 80 MHz@ 100 ohm source impedance | 275  | _                | _    | ns   |

Table continues on the next page...

| Symbol                           | Parameter                                                                             | Conditions                            | Min | Typ <sup>1</sup> | Мах  | Unit |

|----------------------------------|---------------------------------------------------------------------------------------|---------------------------------------|-----|------------------|------|------|

| t <sub>conv</sub>                | Conversion time <sup>4</sup>                                                          | 80 MHz                                | 550 | —                |      | ns   |

| t <sub>total_conv</sub>          | Total Conversion time t <sub>sample</sub> + t <sub>conv</sub> (for standard channels) | 80 MHz                                | 1   | _                | _    | μs   |

|                                  | Total Conversion time t <sub>sample</sub> + t <sub>conv</sub> (for extended channels) |                                       | 1.5 | _                | —    |      |

| C <sub>S</sub>                   | ADC input sampling capacitance                                                        | —                                     | —   | 3                | 5    | pF   |

| C <sub>P1</sub> <sup>5</sup>     | ADC input pin capacitance 1                                                           | —                                     | _   | —                | 5    | pF   |

| C <sub>P2</sub> <sup>5</sup>     | ADC input pin capacitance 2                                                           | —                                     | _   | —                | 0.8  | pF   |

| R <sub>SW1</sub> <sup>5</sup>    | Internal resistance of analog                                                         | V <sub>REF</sub> range = 4.5 to 5.5 V | —   | —                | 0.3  | kΩ   |

|                                  | source                                                                                | $V_{REF}$ range = 3.15 to 3.6 V       | _   | —                | 875  | Ω    |

| R <sub>AD</sub> <sup>5</sup>     | Internal resistance of analog source                                                  | _                                     | —   | —                | 825  | Ω    |

| INL                              | Integral non-linearity                                                                | —                                     | -2  | —                | 2    | LSB  |

| DNL                              | Differential non-linearity                                                            | —                                     | -1  | _                | 1    | LSB  |

| OFS                              | Offset error                                                                          | —                                     | -4  | —                | 4    | LSB  |

| GNE                              | Gain error                                                                            | —                                     | -4  | —                | 4    | LSB  |

| ADC Analog Pad                   | Max leakage (standard channel)                                                        | 150 °C                                | _   | —                | 2500 | nA   |

| (pad going to one<br>ADC)        | Max leakage (standard channel)                                                        | 105 °C <sub>TA</sub>                  | —   | 5                | 250  | nA   |

| ADO)                             | Max positive/negative injection                                                       |                                       | -5  | —                | 5    | mA   |

| TUE <sub>standard/extended</sub> | Total unadjusted error for standard                                                   | Without current injection             | -4  | +/-3             | 4    | LSB  |

| channels                         | channels                                                                              | With current injection <sup>6</sup>   |     | +/-4             |      | LSB  |

| t <sub>recovery</sub>            | STOP mode to Run mode recovery time                                                   |                                       |     |                  | < 1  | μs   |

#### Table 21. ADC conversion characteristics (for 10-bit) (continued)

- Active ADC Input, VinA < [min(ADC\_ADV, IO\_Supply\_A,B,C)]. Violation of this condition would lead to degradation of ADC performance. Please refer to Table: 'Absolute maximum ratings' to avoid damage. Refer to Table: 'Recommended operating conditions' for required relation between IO\_supply\_A, B, C and ADC\_Supply.

- 2. The internally generated clock (known as AD\_clk or ADCK) could be same as the peripheral clock or half of the peripheral clock based on register configuration in the ADC.

- During the sample time the input capacitance C<sub>S</sub> can be charged/discharged by the external source. The internal

resistance of the analog source must allow the capacitance to reach its final voltage level within t<sub>sample</sub>. After the end of the

sample time t<sub>sample</sub>, changes of the analog input voltage have no effect on the conversion result. Values for the sample

clock t<sub>sample</sub> depend on programming.

- 4. This parameter does not include the sample time t<sub>sample</sub>, but only the time for determining the digital result and the time to load the result register with the conversion result.

- 5. See Figure 2

- 6. Current injection condition for ADC channels is defined for an inactive ADC channel (on which conversion is NOT being performed), and this occurs when voltage on the ADC pin exceeds the I/O supply or ground. However, absolute maximum voltage spec on pad input (VINA, see Table: 'Absolute maximum ratings') must be honored to meet TUE spec quoted here

### NOTE

The ADC input pins sit across all three I/O segments, VDD\_HV\_A, VDD\_HV\_B and VDD\_HV\_C.

# 6.1.2 Analog Comparator (CMP) electrical specifications Table 22. Comparator and 6-bit DAC electrical specifications

| Symbol             | Description                                                          | Min.            | Тур. | Max.                         | Unit             |

|--------------------|----------------------------------------------------------------------|-----------------|------|------------------------------|------------------|

| I <sub>DDHS</sub>  | Supply current, High-speed mode (EN=1, PMODE=1)                      |                 | —    | 250                          | μA               |

| I <sub>DDLS</sub>  | Supply current, low-speed mode (EN=1, PMODE=0)                       |                 | 5    | 11                           | μA               |

| V <sub>AIN</sub>   | Analog input voltage                                                 | V <sub>SS</sub> | _    | V <sub>IN1_CMP_RE</sub><br>F | V                |

| V <sub>AIO</sub>   | Analog input offset voltage <sup>1</sup>                             | -42             | _    | 42                           | mV               |

| V <sub>H</sub>     | Analog comparator hysteresis <sup>2</sup>                            | _               | 1    | 25                           | mV               |

|                    | • CR0[HYSTCTR] = 00                                                  | _               | 20   | 50                           | mV               |

|                    | • CR0[HYSTCTR] = 01                                                  | _               | 40   | 70                           | mV               |

|                    | • CR0[HYSTCTR] = 10                                                  | _               | 60   | 105                          | mV               |

|                    | <ul> <li>CR0[HYSTCTR] = 11</li> </ul>                                |                 |      |                              |                  |

| t <sub>DHS</sub>   | Propagation Delay, High Speed Mode (Full Swing) <sup>1, 3</sup>      |                 | _    | 250                          | ns               |

| t <sub>DLS</sub>   | Propagation Delay, Low power Mode (Full Swing) <sup>1, 3</sup>       |                 | 5    | 21                           | μs               |

|                    | Analog comparator initialization delay, High speed mode <sup>4</sup> | _               | 4    |                              | μs               |

|                    | Analog comparator initialization delay, Low speed mode <sup>4</sup>  | _               | 100  |                              | μs               |

| I <sub>DAC6b</sub> | 6-bit DAC current adder (when enabled)                               |                 |      |                              |                  |

|                    | 3.3V Reference Voltage                                               | _               | 6    | 9                            | μA               |

|                    | 5V Reference Voltage                                                 | _               | 10   | 16                           | μA               |

| INL                | 6-bit DAC integral non-linearity                                     | -0.5            | —    | 0.5                          | LSB <sup>5</sup> |

| DNL                | 6-bit DAC differential non-linearity                                 | -0.8            | _    | 0.8                          | LSB              |

1. Measured with hysteresis mode of 00

2. Typical hysteresis is measured with input voltage range limited to 0.6 to  $V_{DD_HV_A}$ -0.6V

3. Full swing = VIH, VIL

4. Comparator initialization delay is defined as the time between software writes to change control inputs (Writes to DACEN, VRSEL, PSEL, MSEL, VOSEL) and the comparator output settling to a stable level.

5. 1 LSB =  $V_{reference}/64$

| Symbol               | Characteristic <sup>1</sup> | Typ <sup>2</sup> | Factory<br>Programming <sup>3, 4</sup> |                                 | F                                      | Field Update      |                     | Unit |

|----------------------|-----------------------------|------------------|----------------------------------------|---------------------------------|----------------------------------------|-------------------|---------------------|------|

|                      |                             |                  | Initial<br>Max                         | Initial<br>Max, Full<br>Temp    | Typical<br>End of<br>Life <sup>5</sup> | Lifeti            | me Max <sup>6</sup> |      |

|                      |                             |                  | 20°C ≤T <sub>A</sub><br>≤30°C          | -40°C ≤T <sub>J</sub><br>≤150°C | -40°C ≤T <sub>J</sub><br>≤150°C        | ≤ 1,000<br>cycles | ≤ 250,000<br>cycles |      |

| t <sub>32kers</sub>  | 32 KB Block erase time      | 217              | 360                                    | 390                             | 310                                    | 1,200             |                     | ms   |

| t <sub>32kpgm</sub>  | 32 KB Block program time    | 69               | 100                                    | 110                             | 90                                     | 1,200             |                     | ms   |

| t <sub>64kers</sub>  | 64 KB Block erase time      | 315              | 490                                    | 590                             | 420                                    | 1,600             |                     | ms   |

| t <sub>64kpgm</sub>  | 64 KB Block program time    | 138              | 180                                    | 210                             | 170                                    | 1,600             |                     | ms   |

| t <sub>256kers</sub> | 256 KB Block erase time     | 884              | 1,520                                  | 2,030                           | 1,080                                  | 4,000             |                     | ms   |

| t <sub>256kpgm</sub> | 256 KB Block program time   | 552              | 720                                    | 880                             | 650                                    | 4,000             |                     | ms   |

#### Table 30. Flash memory program and erase specifications (continued)

1. Program times are actual hardware programming times and do not include software overhead. Block program times assume quad-page programming.

2. Typical program and erase times represent the median performance and assume nominal supply values and operation at 25 °C. Typical program and erase times may be used for throughput calculations.

- 3. Conditions:  $\leq$  150 cycles, nominal voltage.

- 4. Plant Programing times provide guidance for timeout limits used in the factory.

5. Typical End of Life program and erase times represent the median performance and assume nominal supply values. Typical End of Life program and erase values may be used for throughput calculations.

6. Conditions:  $-40^{\circ}C \le T_J \le 150^{\circ}C$ , full spec voltage.

### 6.3.2 Flash memory Array Integrity and Margin Read specifications Table 31. Flash memory Array Integrity and Margin Read specifications

| Symbol                 | Characteristic                                                | Min    | Typical | Max                          | Units |

|------------------------|---------------------------------------------------------------|--------|---------|------------------------------|-------|

| t <sub>ai16kseq</sub>  | Array Integrity time for sequential sequence on 16 KB block.  | -      | _       | 512 x<br>Tperiod x<br>Nread  | _     |

| t <sub>ai32kseq</sub>  | Array Integrity time for sequential sequence on 32 KB block.  | -      | _       | 1024 x<br>Tperiod x<br>Nread | _     |

| t <sub>ai64kseq</sub>  | Array Integrity time for sequential sequence on 64 KB block.  | _      | _       | 2048 x<br>Tperiod x<br>Nread | _     |

| tai256kseq             | Array Integrity time for sequential sequence on 256 KB block. | -      | _       | 8192 x<br>Tperiod x<br>Nread | _     |

| t <sub>mr16kseq</sub>  | Margin Read time for sequential sequence on 16 KB block.      | 73.81  | —       | 110.7                        | μs    |

| t <sub>mr32kseq</sub>  | Margin Read time for sequential sequence on 32 KB block.      | 128.43 | —       | 192.6                        | μs    |

| t <sub>mr64kseq</sub>  | Margin Read time for sequential sequence on 64 KB block.      | 237.65 |         | 356.5                        | μs    |

| t <sub>mr256kseq</sub> | Margin Read time for sequential sequence on 256 KB block.     | 893.01 | _       | 1,339.5                      | μs    |

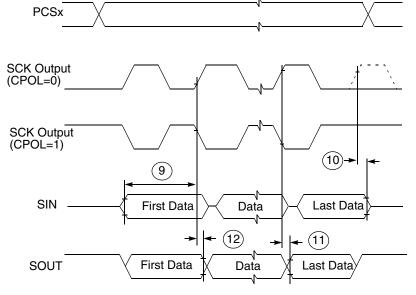

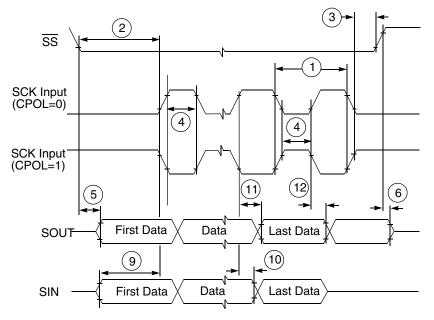

Figure 13. DSPI modified transfer format timing — master, CPHA = 1

Figure 14. DSPI modified transfer format timing – slave, CPHA = 0

1. All parameters specified for VDD\_HV\_IOx =  $3.3 \text{ V} \cdot 5\%$ , +±10%, TJ = -40 oC / 150 oC.

# 6.4.3 uSDHC specifications

### Table 41. uSDHC switching specifications

| Num | Symbol           | Description                                   | Min.          | Max.      | Unit |  |  |  |  |

|-----|------------------|-----------------------------------------------|---------------|-----------|------|--|--|--|--|

|     | Card input clock |                                               |               |           |      |  |  |  |  |

| SD1 | fpp              | Clock frequency (Identification mode)         | 0             | 400       | kHz  |  |  |  |  |

|     | fpp              | Clock frequency (SD\SDIO full speed)          | 0             | 25        | MHz  |  |  |  |  |

|     | fpp              | Clock frequency (SD\SDIO high speed)          | 0             | 40        | MHz  |  |  |  |  |

|     | fpp              | Clock frequency (MMC full speed)              | 0             | 20        | MHz  |  |  |  |  |

|     | f <sub>OD</sub>  | Clock frequency (MMC full speed)              | 0             | 40        | MHz  |  |  |  |  |

| SD2 | t <sub>WL</sub>  | Clock low time                                | 7             | —         | ns   |  |  |  |  |

| SD3 | t <sub>WH</sub>  | Clock high time                               | 7             | —         | ns   |  |  |  |  |

| SD4 | t <sub>TLH</sub> | Clock rise time                               | _             | 3         | ns   |  |  |  |  |

| SD5 | t <sub>THL</sub> | Clock fall time                               | —             | 3         | ns   |  |  |  |  |

|     |                  | SDHC output / card inputs SDHC_CMD, SDHC_DAT  | (reference to | SDHC_CLK) |      |  |  |  |  |

| SD6 | t <sub>OD</sub>  | SDHC output delay (output valid)              | -5            | 6.5       | ns   |  |  |  |  |

|     |                  | SDHC input / card inputs SDHC_CMD, SDHC_DAT ( | reference to  | SDHC_CLK) |      |  |  |  |  |

| SD7 | t <sub>ISU</sub> | SDHC input setup time                         | 5             | —         | ns   |  |  |  |  |

| SD8 | t <sub>IH</sub>  | SDHC input hold time                          | 0             | —         | ns   |  |  |  |  |

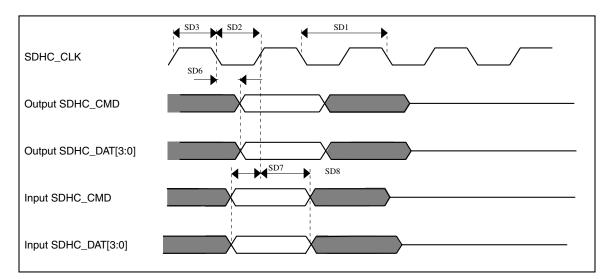

Figure 21. uSDHC timing

# 6.4.5 MediaLB (MLB) electrical specifications

## 6.4.5.1 MLB 3-pin interface DC characteristics

The section lists the MLB 3-pin interface electrical characteristics.

Table 44. MediaLB 3-Pin Interface Electrical DC Specifications

| Parameter                   | Symbol          | Test Conditions          | Min | Max | Unit |

|-----------------------------|-----------------|--------------------------|-----|-----|------|

| Maximum input voltage       | —               | —                        | -   | 3.6 | V    |

| Low level input threshold   | V <sub>IL</sub> | -                        | —   | 0.7 | V    |

| High level input threshold  | V <sub>IH</sub> | See Note <sup>1</sup>    | 1.8 | —   | V    |

| Low level output threshold  | V <sub>OL</sub> | $I_{OL} = -6 \text{ mA}$ | —   | 0.4 | V    |

| High level output threshold | V <sub>OH</sub> | I <sub>OH</sub> = –6 mA  | 2.0 | —   | V    |

| Input leakage current       | IL              | 0 < Vin < VDD            | —   | ±10 | μA   |

1. Higher  $V_{\text{IH}}$  thresholds can be used; however, the risks associated with less noise margin in the system must be evaluated and assumed by the customer.

# 6.4.5.2 MLB 3-pin interface electrical specifications

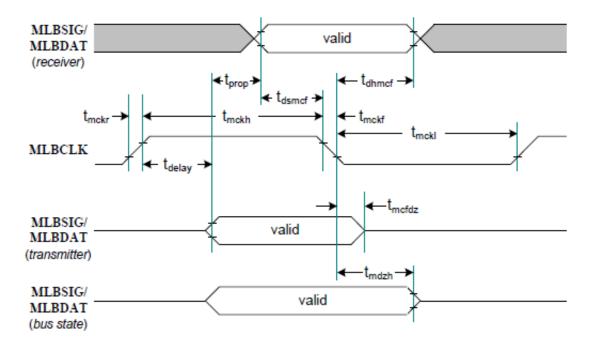

This section describes the timing electrical information of the MLB module.

#### MediaLB (MLB) electrical specifications

Ground = 0.0 V; Load Capacitance = 60 pF, input transition= 1 ns ; MediaLB speed = 256/512 Fs; Fs = 48 kHz; all timing parameters specified from the valid voltage threshold as listed below; unless otherwise noted.

| Parameter                                               | Symbol             | Min                | Max                | Unit | Comment                                   |

|---------------------------------------------------------|--------------------|--------------------|--------------------|------|-------------------------------------------|

| MLBCLK operating frequency                              | f <sub>mck</sub>   | 11.264             | 25.6               | MHz  | 256xFs at 44.0 kHz,<br>512xFs at 50.0 kHz |

| MLBCLK rise time                                        | t <sub>mck</sub> r |                    | 3                  | ns   | V <sub>IL to VIH</sub>                    |

| MLBCLK fall time                                        | t <sub>mck</sub> f |                    | 3                  | ns   | V <sub>IH to VIL</sub>                    |

| MLBCLK low time <sup>1</sup>                            | t <sub>mck</sub> l | 30                 | —                  | ns   | 256xFs                                    |

|                                                         |                    | 14                 |                    |      | 512xFs                                    |

| MLBCLK high time                                        | t <sub>mck</sub> h | 30                 | —                  | ns   | 256xFs                                    |

|                                                         |                    | 14                 |                    |      | 512xFs                                    |

| MLBSIG/MLBDAT receiver input setup to<br>MLBCLK falling | t <sub>dsmcf</sub> | 1                  | —                  | ns   | —                                         |

| MLBSIG/MLBDAT receiver input hold from MLBCLK low       | t <sub>dhmcf</sub> | t <sub>mcfdz</sub> | —                  | ns   | —                                         |

| MLBSIG/MLBDAT output valid from<br>MLBCLK low           | t <sub>mcfdz</sub> | 0                  | t <sub>mck</sub> l | ns   | 2                                         |

| Bus output hold from MLBCLK low                         | t <sub>mdzh</sub>  | 4                  | —                  | ns   | 2                                         |

Table 45. MLB 3-Pin 256/512 Fs Timing Parameters

1. MLBCLK low/high time includes the pluse width variation.

The MediaLB driver can release the MLBDAT/MLBSIG line as soon as MLBCLK is low; however, the logic state of the final driven bit on the line must remain on the bus for tmdzh. Therefore, coupling must be minimized while meeting the maximum load capacitance listed.

Ground = 0.0 V; Load Capacitance = 40 pF, input transition= 1 ns; MediaLB speed = 1024 Fs; Fs = 48 kHz; all timing parameters specified from the valid voltage threshold as listed below; unless otherwise noted.

| Parameter                                               | Symbol             | Min                | Мах               | Unit | Comment                            |

|---------------------------------------------------------|--------------------|--------------------|-------------------|------|------------------------------------|

| MLBCLK Operating Frequency <sup>1</sup>                 | f <sub>mck</sub>   | 45.056             | -                 | MHz  | 1024 x fs at 44.0 kHz              |

|                                                         |                    | -                  | 51.2              | MHz  | 1024 x fs at 50.0 kHz              |

| MLBCLK rise time                                        | f <sub>mckr</sub>  |                    | 1                 | ns   | V <sub>IL to</sub> V <sub>IH</sub> |

| MLBCLK fall time                                        | f <sub>mckf</sub>  |                    | 1                 | ns   | V <sub>IH to</sub> V <sub>IL</sub> |

| MLBCLK low time                                         | t <sub>mckl</sub>  | 6.1                | —                 | ns   | 2                                  |

| MLBCLK high time                                        | t <sub>mckh</sub>  | 9.3                | —                 | ns   | 2                                  |

| MLBSIG/MLBDAT receiver input<br>setup to MLBCLK falling | t <sub>dsmcf</sub> | 1                  | _                 | ns   |                                    |

| MLBSIG/MLBDAT receiver input hold from MLBCLK low       | t <sub>dhmcf</sub> | t <sub>mcfdz</sub> | _                 | ns   |                                    |

| MLBSIG/MLBDAT output valid from<br>MLBCLK low           | t <sub>mcfdz</sub> | 0                  | t <sub>mckl</sub> | ns   | 3                                  |

| Bus Hold from MLBCLK low                                | t <sub>mdzh</sub>  | 2                  | —                 | ns   | 3                                  |

Table 46. MLB 3-Pin 1024 Fs Timing Parameters

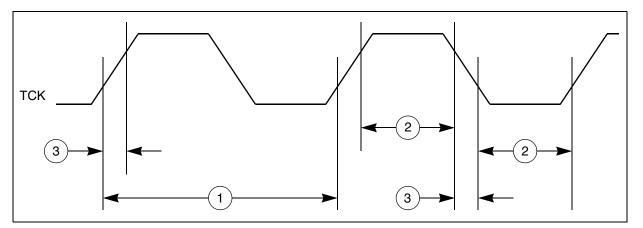

Figure 28. JTAG test clock input timing

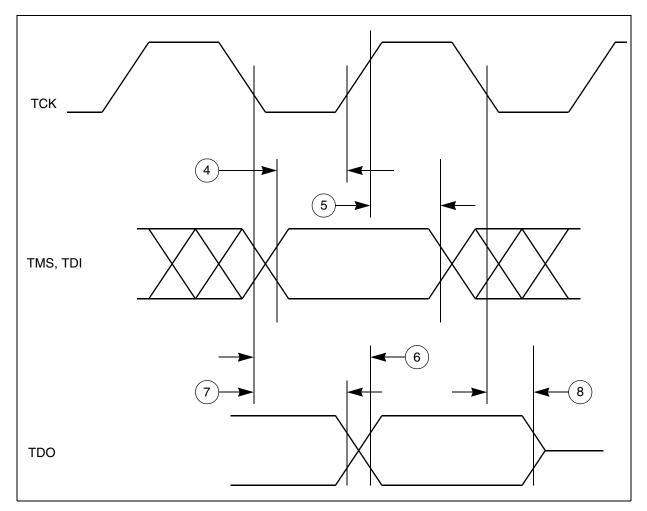

Figure 29. JTAG test access port timing

# 9 Pinouts

# 9.1 Package pinouts and signal descriptions

For package pinouts and signal descriptions, refer to the Reference Manual.

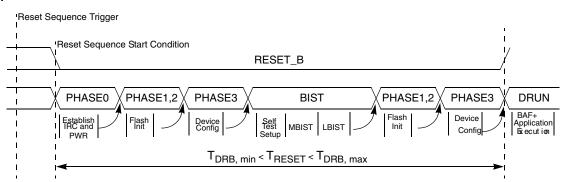

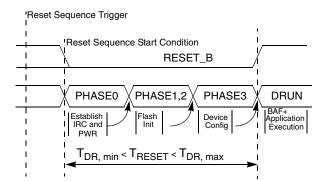

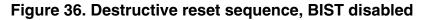

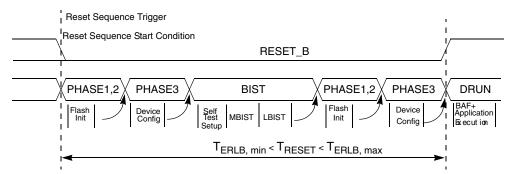

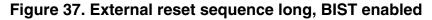

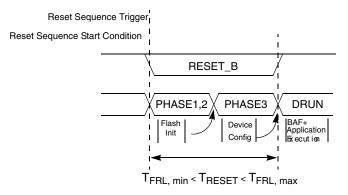

# 10 Reset sequence

This section describes different reset sequences and details the duration for which the device remains in reset condition in each of those conditions.

# 10.1 Reset sequence duration

Table 54 specifies the minimum and the maximum reset sequence duration for the five different reset sequences described in Reset sequence description.

| No. | Symbol            | Parameter T <sub>Reset</sub>                                |  |                  | Unit |    |

|-----|-------------------|-------------------------------------------------------------|--|------------------|------|----|

|     |                   |                                                             |  | Typ <sup>1</sup> | Max  |    |

| 1   | T <sub>DRB</sub>  | Destructive Reset Sequence, BIST enabled                    |  | 7.796            |      | ms |

| 2   | T <sub>DR</sub>   | Destructive Reset Sequence, BIST disabled 0.111             |  | 0.182            |      | ms |

| 3   | T <sub>ERLB</sub> | External Reset Sequence Long, Unsecure Boot 5.729 7.793     |  | 7.793            |      | ms |

| 4   | T <sub>FRL</sub>  | Functional Reset Sequence Long, Unsecure Boot         0.110 |  | 0.179            |      | ms |

| 5   | T <sub>FRS</sub>  | Functional Reset Sequence Short, Unsecure Boot         0.0  |  | 0.009            |      | ms |

Table 54. RESET sequences

1. The Typ value is applicable only if the reset sequence duration is not prolonged by an extended assertion of RESET\_B by an external reset generator.

#### **Reset sequence**

Figure 38. Functional reset sequence long

Figure 39. Functional reset sequence short

The reset sequences shown in Figure 38 and Figure 39 are triggered by functional reset events. RESET\_B is driven low during these two reset sequences only if the corresponding functional reset source (which triggered the reset sequence) was enabled to drive RESET\_B low for the duration of the internal reset sequence. See the RGM\_FBRE register in the device reference manual for more information.

# **11 Revision History**

The following table provides a revision history for this document.

| Rev. No. | Date          | Substantial Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | 14 March 2013 | Initial Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.1      | 16 May 2013   | Updated Pinouts section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2        | 22 May 2014   | <ul> <li>Removed Category (SR, CC, P, T, D, B) column from all the table of the Datasheet</li> <li>Revised the feature list.</li> <li>Revised Introduction section to remove classification information.</li> <li>Updated optional information in the ordering information figure.</li> <li>Revised Absolute maximum rating section: <ul> <li>Removed category column from table</li> <li>Added footnote at Ta</li> </ul> </li> <li>Revised Recommended operating conditions section <ul> <li>Added notes</li> <li>Updated table: Recommended operating conditions (VDD_HV_x = 3.3 V)</li> <li>Updated table: Recommended operating conditions (VDD_HV_x = 5 V)</li> </ul> </li> <li>Revised Voltage regulator electrical characteristics <ul> <li>Updated figure: Voltage regulator capacitance connection</li> <li>Updated table: Voltage regulator electrical specifications</li> <li>Removed Brownout information</li> </ul> </li> </ul> |

|          |               | <ul> <li>Revised Supply current characteristics section</li> <li>Updated table: Current consumption characteristics</li> <li>Updated table: Low Power Unit (LPU) Current consumption characteristics</li> <li>STANDBY Current consumption characteristics</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Table 56.

Revision History

Table continues on the next page ...

| Rev. No. | Date | Substantial Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |      | <ul> <li>Removed row for symbol 'V<sub>SS_LV</sub>'</li> <li>Removed footnote from 'Max' column of symbols 'V<sub>DD_HV_ADC0</sub>' and 'V<sub>DD_HV_ADC1</sub>'</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|          |      | <ul> <li>In section: Recommended operating conditions</li> <li>In table: Recommended operating conditions (V<sub>DD_HV_x</sub> = 5 V)</li> <li>Added footnote to 'Conditions' cloumn</li> <li>Updated footnote from symbols 'V<sub>DD_HV_A'</sub>, 'V<sub>DD_HV_B</sub>', and 'V<sub>DD_HV_C</sub>'</li> <li>Removed footnote from symbols 'V<sub>SS_HV</sub>'</li> <li>Updated 'Parameter' column for symbol 'V<sub>DD_HV_ADC1_REF</sub>'</li> <li>'V<sub>DD_HV_ADC1_REF</sub>', 'V<sub>DD_LV</sub>'</li> <li>Updated 'Min' columnn of symbol 'V<sub>DD_HV_ADC0</sub>' and 'V<sub>DD_HV_ADC1</sub>'</li> <li>Updated 'Parameter', 'Min' 'Max' column for symbol 'V<sub>SS_HV_ADC0</sub>' and 'V<sub>SS_HV_ADC0</sub>' and 'V<sub>SS_HV_ADC1</sub>'</li> <li>Added footnote to symbol 'V<sub>DD_LV</sub>'</li> <li>Removed row for symbol 'V<sub>DD_LV</sub>'</li> <li>Added row for symbol 'V<sub>SS_LV</sub>'</li> <li>Added row for symbol 'V<sub>SS_LV</sub>'</li> <li>Added row for symbol 'V<sub>IN1_CMP_REF</sub>' and corresponding footnotes to the symbol</li> </ul>                                                                                                                                                                                                                                                                                           |

|          |      | <ul> <li>In section: Voltage regulator electrical characteristics         <ul> <li>In table: Voltage regulator electrical specifications</li> <li>Added note to symbol 'Cbe_fpreg'</li> </ul> </li> <li>In section: Voltage monitor electrical characteristics         <ul> <li>In table: Voltage monitor electrical characteristics</li> <li>In table: Voltage monitor electrical characteristics</li> <li>Updated column 'Parameter', 'Min' and 'Max' (of fall/rise trimmed condition) for symbol 'V<sub>HVD_LV_cold</sub>' and 'V<sub>LVD_IO_A_HI'</sub></li> <li>Updated column 'Parameter', 'Min' and 'Typ' (of fall/rise trimmed condition) for symbol) 'V<sub>LVD_LV_PD2_hot</sub>', 'V<sub>LVD_LV_PD2_cold LV'</sub></li> <li>Updated column 'Parameter' for symbol 'V<sub>LVD_LV_PD0_hot</sub>'</li> <li>Updated column 'Typ' and 'Max' (of fall/rise trimmed condition) for symbol) 'V<sub>LVD_FLASH</sub>'</li> <li>Updated footnote on symbol 'V<sub>LVD_IO_A_LO</sub>' and 'V<sub>LVD_IO_A_HI'</sub></li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                 |

|          |      | <ul> <li>In section: Supply current characteristics</li> <li>In table: Current consumption characteristics</li> <li>Updated column 'Typ' for symbol 'I<sub>DD_FULL</sub>' for temperature 85, 105, 125</li> <li>Updated column 'Typ' for symbol 'I<sub>DD_GWY</sub>' for temperature 85, 105, 125 and column 'Max' for temperature 105</li> <li>Updated column 'Typ' for symbol 'I<sub>DD_BODY1</sub>' for temperature 85, 105, 125 updated column 'Typ' for symbol 'I<sub>DD_BODY2</sub>' for temperature 85, 105, 125</li> <li>Updated column 'Typ' for symbol 'I<sub>DD_BODY2</sub>' for temperature 85, 105, 125 and 'Max' for temperature 125</li> <li>Added 'Typ' value for temperature 25 for symbol 'I<sub>DD_STOP</sub>'</li> <li>Updated column 'Typ' and 'Max' for symbol 'I<sub>DD_STOP</sub>' for temperature 85, 105, 125</li> <li>In table: Low Power Unit (LPU) Current consumption characteristics</li> <li>Updated column 'Typ' for symbol 'LPU_RUN' for tempeature 25 and 125</li> <li>Added 'Typ' and 'Max' value for temperature 85 and 105 for symbol 'LPU_RUN'</li> <li>Updated column 'Typ' for symbol 'LPU_STOP' for tempeature 25 and 125</li> <li>Added 'Typ' and 'Max' value for temperature 85 and 105 for symbol 'LPU_STOP'</li> <li>In table: STANDBY Current consumption characteristics</li> <li>Updated to have one STANDBY</li> </ul> |

### Table 56. Revision History (continued)

• In section: I/O parameters

Table continues on the next page...

| Table 56. | Revision   | History | (continued) |

|-----------|------------|---------|-------------|

|           | 1101131011 | instory | (continucu) |

| Rev. No. | Date        | Substantial Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |             | <ul> <li>In table: Functional Pad AC Specifications @ 3.3 V Range</li> <li>Updated values for symbol 'pad_sr_hv (output)'</li> <li>In table: DC electrical specifications @ 3.3V Range</li> <li>Updtaed values for VDD_HV_x, Vih, Vhys</li> <li>Added Vih (pad_i_hv), Vil (pad_i_hv), Vhys (pad_i_hv), Vih_hys, Vil_hys</li> <li>In table: Functional Pad AC Specifications @ 5 V Range</li> <li>Updated values for symbol 'pad_sr_hv (output)'</li> <li>In table DC electrical specifications @ 5 V Range</li> <li>Added Vih (pad_i_hv), Vil (pad_i_hv), Vhys (pad_i_hv), Vih_hys, Vil_hys</li> </ul>                                                                                                                                                                                                                                                                                                                                                         |

|          |             | <ul> <li>In section: PORST electrical specifications</li> <li>In table: PORST electrical specifications</li> <li>Updated 'Min' value for W<sub>NFPORST</sub></li> <li>Corrected 'Unit' for V<sub>IH</sub> and V<sub>IL</sub></li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          |             | <ul> <li>In section: Peripheral operating requirements and behaviours</li> <li>Revised table: ADC conversion characteristics (for 12-bit) and ADC conversion characteristics (for 10-bit)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|          |             | <ul> <li>In section: Analogue Comparator (CMP) electrical specifications</li> <li>In table: Comparator and 6-bit DAC electrical specifications</li> <li>Updated 'Max' value of I<sub>DDLS</sub></li> <li>Updated 'Min' and 'Max' for V<sub>AIO</sub> and DNL</li> <li>Updated 'Descripton' 'Min' 'Max' od V<sub>H</sub></li> <li>Updated row for tDHS</li> <li>Added row for tDLS</li> <li>Removed row for VCMPOh and VCMPOI</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          |             | <ul> <li>In section: Clocks and PLL interfaces modules <ul> <li>Revised table: Main oscillator electrical characteristics</li> <li>In table: 16 MHz RC Oscillator electrical specifications <ul> <li>Updated 'Max' of Tstartup</li> </ul> </li> <li>In table: 128 KHz Internal RC oscillator electrical specifications <ul> <li>Removed Uncaliberated 'Condition' for Fosc</li> <li>Updated 'Min' and 'Max' of Caliberated Fosc</li> <li>Updated 'Temperature dependence' and 'Supply dependence'</li> </ul> </li> <li>In table: PLL electrical specifications <ul> <li>Removed Input Clock Low Level, Input Clock High Level, Power consumption, Regulator Maximum Output Current, Analog Supply, Digital Supply (VDD_LV), Modulation Depth (Down Spread), PLL reset assertion time, and Power Consumption</li> <li>Removed 'Typ' value of Duty Cycle at pllclkout</li> <li>Removed 'Min' from calibration mode of Lock Time</li> </ul> </li> </ul></li></ul> |

|          |             | In table: Jitter calculation     Added 1 Sigma Random Jitter value for Long term jitter      In section Flash read wait state and address pipeline control settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|          |             | <ul> <li>Revised table: Flash Read Wait State and Address Pipeline Control</li> <li>Removed section: On-chip peripherals</li> <li>Added section: 'Reset sequence'</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Rev4     | Feb 10 2017 | <ul> <li>Added VDD_HV_BALLAST footnote in Voltage regulator electrical characteristics</li> <li>Added Note to clarify In-Rush current and pin capacitance in Voltage regulator electrical characteristics</li> <li>Updated SIUL2_MSCRn[SRC 1:0]=11@25pF max value; SIUL2_MSCRn[SRC 1:0]=11@50pF min value; SIUL2_MSCRn[SRC 1:0]=10@25pF min and max values in AC specifications @ 3.3 V Range</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Table continues on the next page...

| Rev. No. | . No. Date Substantial Changes |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|----------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|