Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Core Processore200z2, e200z4Core Size32-Bit Dual-CoreSpeed80MHz/160MHzConnectivityCANbus, Ethernet, I²C, LINbus, SAI, SPI, USB, USB OTGPeripheralsDMA, LVD, POR, WDTNumber of I/O178Program Memory Size6MB (6M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size768K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 80x10b, 64x12bOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case256-LBGASurpe Converters256-LBGA |                            |                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------------|

| Core Size32-Bit Dual-CoreSpeed80MHz/160MHzConnectivityCANbus, Ethernet, I²C, LINbus, SAI, SPI, USB, USB OTGPeripheralsDMA, LVD, POR, WDTNumber of I/O178Program Memory Size6MB (6M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size768K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 80x10b, 64x12bOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case256-LBGASurface MARD Size-26-MAPPBGA (17x17)                 | Product Status             | Active                                                                 |

| Speed80MHz/160MHzConnectivityCANbus, Ethernet, I²C, LINbus, SAI, SPI, USB, USB OTGPeripheralsDMA, LVD, POR, WDTNumber of I/O178Program Memory Size6MB (6M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size768K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 80x10b, 64x12bOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case256-LBGASupplier Device Package256-MAPPBGA (17x17)                                    | Core Processor             | e200z2, e200z4                                                         |

| ConnectivityCANbus, Ethernet, I²C, LINbus, SAI, SPI, USB, USB OTGPeripheralsDMA, LVD, POR, WDTNumber of I/O178Program Memory Size6MB (6M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size768K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 80x10b, 64x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case256-LBGASupplier Device Package256-MAPPBGA (17x17)                              | Core Size                  | 32-Bit Dual-Core                                                       |

| PeripheralsDMA, LVD, POR, WDTNumber of I/O178Program Memory Size6MB (6M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size768K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 80x10b, 64x12bOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case256-LBGASupplier Device Package256-MAPPBGA (17x17)                                                                                                                      | Speed                      | 80MHz/160MHz                                                           |

| Number of I/O178Program Memory Size6MB (6M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size768K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 80x10b, 64x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case256-LBGASupplier Device Package256-MAPPBGA (17x17)                                                                                                                            | Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, LINbus, SAI, SPI, USB, USB OTG     |

| Program Memory Size6MB (6M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size768K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 80x10b, 64x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case256-LBGASupplier Device Package256-MAPPBGA (17x17)                                                                                                                                            | Peripherals                | DMA, LVD, POR, WDT                                                     |

| Program Memory TypeFLASHEEPROM Size-RAM Size768K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 80x10b, 64x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case256-LBGASupplier Device Package256-MAPPBGA (17x17)                                                                                                                                                                           | Number of I/O              | 178                                                                    |

| EEPROM Size-RAM Size768K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 80x10b, 64x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case256-LBGASupplier Device Package256-MAPPBGA (17x17)                                                                                                                                                                                                   | Program Memory Size        | 6MB (6M x 8)                                                           |

| RAM Size768K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 80x10b, 64x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case256-LBGASupplier Device Package256-MAPPBGA (17x17)                                                                                                                                                                                                               | Program Memory Type        | FLASH                                                                  |

| Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 80x10b, 64x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case256-LBGASupplier Device Package256-MAPPBGA (17x17)                                                                                                                                                                                                                               | EEPROM Size                | -                                                                      |

| Data ConvertersA/D 80x10b, 64x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case256-LBGASupplier Device Package256-MAPPBGA (17x17)                                                                                                                                                                                                                                                                  | RAM Size                   | 768K x 8                                                               |

| Oscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case256-LBGASupplier Device Package256-MAPPBGA (17x17)                                                                                                                                                                                                                                                                                                   | Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                              |

| Operating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case256-LBGASupplier Device Package256-MAPPBGA (17x17)                                                                                                                                                                                                                                                                                                                          | Data Converters            | A/D 80x10b, 64x12b                                                     |

| Mounting Type     Surface Mount       Package / Case     256-LBGA       Supplier Device Package     256-MAPPBGA (17x17)                                                                                                                                                                                                                                                                                                                                    | Oscillator Type            | Internal                                                               |

| Package / Case 256-LBGA<br>Supplier Device Package 256-MAPPBGA (17x17)                                                                                                                                                                                                                                                                                                                                                                                     | Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Supplier Device Package 256-MAPPBGA (17x17)                                                                                                                                                                                                                                                                                                                                                                                                                | Mounting Type              | Surface Mount                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Package / Case             | 256-LBGA                                                               |

| Purchase URL https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5748ck1mmj6                                                                                                                                                                                                                                                                                                                                                                        | Supplier Device Package    | 256-MAPPBGA (17x17)                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5748ck1mmj6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

5. Estimated I/O count for largest proposed packages based on multiplexing with peripherals.

#### Table 2. MPC5748G Family Comparison - NVM Memory Map 1

| Start Address | End Address | Flash block                   | RWW | MPC5746       | MPC5747       | MPC5748   |

|---------------|-------------|-------------------------------|-----|---------------|---------------|-----------|

| 0x01000000    | 0x0103FFFF  | 256 KB code<br>Flash block 0  | 6   | available     | available     | available |

| 0x01040000    | 0x0107FFFF  | 256 KB code<br>Flash block 1  | 6   | available     | available     | available |

| 0x01080000    | 0x010BFFFF  | 256 KB code<br>Flash block 2  | 6   | available     | available     | available |

| 0x010C0000    | 0x010FFFFF  | 256 KB code<br>Flash block3   | 6   | available     | available     | available |

| 0x01100000    | 0x0113FFFF  | 256 KB code<br>Flash block 4  | 6   | available     | available     | available |

| 0x01140000    | 0x0117FFFF  | 256 KB code<br>Flash block 5  | 6   | available     | available     | available |

| 0x01180000    | 0x011BFFFF  | 256 KB code<br>Flash block 6  | 6   | available     | available     | available |

| 0x011C0000    | 0x011FFFFF  | 256 KB code<br>Flash block 7  | 6   | available     | available     | available |

| 0x01200000    | 0x0123FFFF  | 256 KB code<br>Flash block 8  | 7   | available     | available     | available |

| 0x01240000    | 0x0127FFFF  | 256 KB code<br>Flash block 9  | 7   | available     | available     | available |

| 0x01280000    | 0x012BFFFF  | 256 KB code<br>Flash block 10 | 7   | not available | available     | available |

| 0x012C0000    | 0x012FFFFF  | 256 KB code<br>flash block 11 | 7   | not available | available     | available |

| 0x01300000    | 0x0133FFFF  | 256 KB code<br>flash block 12 | 7   | not available | available     | available |

| 0x01340000    | 0x0137FFFF  | 256 KB code<br>flash block 13 | 7   | not available | available     | available |

| 0x01380000    | 0x013BFFFF  | 256 KB code<br>flash block 14 | 7   | not available | not available | available |

| 0x013C0000    | 0x013FFFFF  | 256 KB code<br>flash block 15 | 7   | not available | not available | available |

| 0x01400000    | 0x0143FFFF  | 256 KB code<br>flash block 16 | 8   | not available | not available | available |

| 0x01440000    | 0x0147FFFF  | 256 KB code<br>flash block 17 | 8   | not available | not available | available |

| 0x01480000    | 0x014BFFFF  | 256 KB code<br>flash block 18 | 8   | not available | not available | available |

| 0x14C0000     | 0x014FFFFF  | 256 KB code<br>flash block 19 | 9   | not available | not available | available |

| 0x01500000    | 0x0153FFFF  | 256 KB code<br>flash block 20 | 9   | not available | not available | available |

| 0x01540000    | 0x0157FFFF  | 256 KB code<br>flash block 21 | 9   | not available | not available | available |

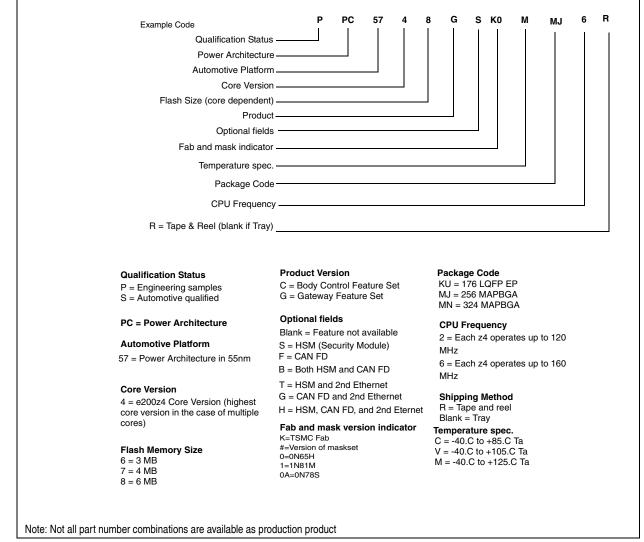

# 3.2 Ordering Information

# 4 General

# 4.1 Absolute maximum ratings

#### NOTE

Functional operating conditions appear in the DC electrical characteristics. Absolute maximum ratings are stress ratings only, and functional operation at the maximum values is not guaranteed. See footnotes in Table 5 for specific conditions

# 4.2 **Recommended operating conditions**

The following table describes the operating conditions for the device, and for which all specifications in the data sheet are valid, except where explicitly noted. The device operating conditions must not be exceeded in order to guarantee proper operation and reliability. The ranges in this table are design targets and actual data may vary in the given range.

### NOTE

- For normal device operations, all supplies must be within operating range corresponding to the range mentioned in following tables. This is required even if some of the features are not used.

- If VDD\_HV\_A is in 3.3V range, VDD\_HV\_FLA should be externally supplied using a 3.3V source. If VDD\_HV\_A is in 3.3V range, VDD\_HV\_FLA should be shorted to VDD\_HV\_A.

- VDD\_HV\_A, VDD\_HV\_B and VDD\_HV\_C are all independent supplies and can each be set to 3.3V or 5V. The following tables: 'Recommended operating conditions (VDD\_HV\_x = 3.3 V)' and table 'Recommended operating conditions (VDD\_HV\_x = 5 V)' specify their ranges when configured in 3.3V or 5V respectively.

| Symbol                                             | Parameter                                                   | Conditions <sup>1</sup> | Min <sup>2</sup>                                   | Max  | Unit |

|----------------------------------------------------|-------------------------------------------------------------|-------------------------|----------------------------------------------------|------|------|

| V <sub>DD_HV_A</sub>                               | HV IO supply voltage                                        | _                       | 3.15                                               | 3.6  | V    |

| $V_{DD_HV_B}$                                      |                                                             |                         |                                                    |      |      |

| $V_{DD_HV_C}$                                      |                                                             |                         |                                                    |      |      |

| V <sub>DD_HV_FLA</sub> <sup>3</sup>                | HV flash supply voltage                                     | _                       | 3.15                                               | 3.6  | V    |

| V <sub>DD_HV_ADC1_REF</sub>                        | HV ADC1 high reference voltage                              |                         | 3.0                                                | 5.5  | V    |

| V <sub>DD_HV_ADC0</sub><br>V <sub>DD_HV_ADC1</sub> | HV ADC supply voltage                                       | _                       | max(VDD_H<br>V_A,VDD_H<br>V_B,VDD_H<br>V_C) - 0.05 | 3.6  | V    |

| V <sub>SS_HV_ADC0</sub><br>V <sub>SS_HV_ADC1</sub> | HV ADC supply ground                                        | _                       | -0.1                                               | 0.1  | V    |

| V <sub>DD_LV</sub> <sup>4</sup>                    | Core supply voltage                                         | _                       | 1.2                                                | 1.32 | V    |

| V <sub>IN1_CMP_REF</sub> <sup>5, 6</sup>           | Analog Comparator DAC reference voltage                     | _                       | 3.15                                               | 3.6  | V    |

| I <sub>INJPAD</sub>                                | Injected input current on any pin during overload condition | —                       | -3.0                                               | 3.0  | mA   |

Table 6. Recommended operating conditions ( $V_{DD_HV_x} = 3.3 V$ )

Table continues on the next page...

#### General

#### Table 6. Recommended operating conditions ( $V_{DD_HV_x} = 3.3 V$ ) (continued)

| Symbol         | Parameter                       | Conditions <sup>1</sup>       | Min <sup>2</sup> | Max | Unit |

|----------------|---------------------------------|-------------------------------|------------------|-----|------|

| T <sub>A</sub> | Ambient temperature under bias  | f <sub>CPU</sub> ≤ 160<br>MHz | -40              | 125 | °C   |

| TJ             | Junction temperature under bias | _                             | -40              | 150 | °C   |

1. All voltages are referred to  $V_{SS\ HV}$  unless otherwise specified

- 2. Device will be functional down (and electrical specifications as per various datasheet parameters will be guaranteed) to the point where one of the LVD/HVD resets the device. When voltage drops outside range for an LVD/HVD, device is reset.

- 3. VDD\_HV\_FLA must be connected to VDD\_HV\_A when VDD\_HV\_A = 3.3V

- 4. VDD\_LV supply pins should never be grounded (through a small impedance). If these are not driven, they should only be left floating.

5. VIN1\_CMP\_REF  $\leq$  VDD\_HV\_A

6. This supply is shorted VDD\_HV\_A on lower packages.

#### NOTE

If VDD\_HV\_A is in 5V range, it is necessary to use internal Flash supply 3.3V regulator. VDD\_HV\_FLA should not be supplied externally and should only have decoupling capacitor.

#### Table 7. Recommended operating conditions ( $V_{DD HV x} = 5 V$ )

| Symbol                                             | Parameter                                     | Conditions <sup>1</sup>       | Min <sup>2</sup>                                   | Max  | Unit |  |

|----------------------------------------------------|-----------------------------------------------|-------------------------------|----------------------------------------------------|------|------|--|

| V <sub>DD_HV_A</sub>                               | HV IO supply voltage                          | —                             | 4.5                                                | 5.5  | V    |  |

| V <sub>DD_HV_B</sub>                               |                                               |                               |                                                    |      |      |  |

| V <sub>DD_HV_C</sub>                               |                                               |                               |                                                    |      |      |  |

| V <sub>DD_HV_FLA</sub> <sup>3</sup>                | HV flash supply voltage                       | _                             | 3.15                                               | 3.6  | V    |  |

| V <sub>DD_HV_ADC1_REF</sub>                        | HV ADC1 high reference voltage                | _                             | 3.15                                               | 5.5  | V    |  |

| V <sub>DD_HV_ADC0</sub><br>V <sub>DD_HV_ADC1</sub> | V <sub>DD_HV_ADC0</sub> HV ADC supply voltage |                               | max(VDD_H<br>V_A,VDD_H<br>V_B,VDD_H<br>V_C) - 0.05 | 5.5  | V    |  |

| V <sub>SS_HV_ADC0</sub><br>V <sub>SS_HV_ADC1</sub> | HV ADC supply ground                          | _                             | -0.1                                               | 0.1  | V    |  |

| V <sub>DD_LV</sub> <sup>4</sup>                    | Core supply voltage                           | _                             | 1.2                                                | 1.32 | V    |  |

| V <sub>IN1_CMP_REF</sub> <sup>5</sup>              | Analog Comparator DAC reference voltage       | _                             | 3.15                                               | 5.5  | V    |  |

| I <sub>INJPAD</sub>                                |                                               |                               | -3.0                                               | 3.0  | mA   |  |

| T <sub>A</sub>                                     | Ambient temperature under bias                | f <sub>CPU</sub> ≤ 160<br>MHz | -40                                                | 125  | °C   |  |

| TJ                                                 | Junction temperature under bias               | _                             | -40                                                | 150  | °C   |  |

1. All voltages are referred to  $V_{SS\ HV}$  unless otherwise specified

- 2. Device will be functional down (and electrical specifications as per various datasheet parameters will be guaranteed) to the point where one of the LVD/HVD resets the device. When voltage drops outside range for an LVD/HVD, device is reset.

- 3. When VDD\_HV is in 5 V range, VDD\_HV\_FLA cannot be supplied externally. This pin is decoupled with  $C_{flash\_reg}$ .

- 4. VDD\_LV supply pins should never be grounded (through a small impedance). If these are not driven, they should only be left floating

- 5. This supply is shorted VDD\_HV\_A on lower packages.

# 4.3 Voltage regulator electrical characteristics

The voltage regulator is composed of the following blocks:

- Choice of generating supply voltage for the core area.

- Control of external NPN ballast transistor

- Connecting an external 1.25 V (nominal) supply directly without the NPN ballast

- Internal generation of the 3.3 V flash supply when device connected in 5V applications

- External bypass of the 3.3 V flash regulator when device connected in 3.3V applications

- Low voltage detector low threshold (LVD\_IO\_A\_LO) for V<sub>DD\_HV\_IO\_A supply</sub>

- Low voltage detector high threshold (LVD\_IO\_A\_Hi) for V<sub>DD\_HV\_IO\_A</sub> supply

- Various low voltage detectors (LVD\_LV\_x)

- High voltage detector (HVD\_LV\_cold) for 1.2 V digital core supply (VDD\_LV)

- Power on Reset (POR\_LV) for 1.25 V digital core supply (VDD\_LV)

- Power on Reset (POR\_HV) for 3.3 V to 5 V supply (VDD\_HV\_A)

The following bipolar transistors<sup>1</sup> are supported, depending on the device performance requirements. As a minimum the following must be considered when determining the most appropriate solution to maintain the device under its maximum power dissipation capability: current, ambient temperature, mounting pad area, duty cycle and frequency for Idd, collector voltage, etc

<sup>1.</sup> BCP56, MCP68 and MJD31are guaranteed ballasts.

# 4.5 Supply current characteristics

Current consumption data is given in the following table. These specifications are design targets and are subject to change per device characterization.

#### NOTE

The ballast must be chosen in accordance with the ballast transistor supplier operating conditions and recommendations.

| Symbol                         | Parameter                          | Conditions <sup>1</sup>                                          | Min | Тур | Max | Unit |

|--------------------------------|------------------------------------|------------------------------------------------------------------|-----|-----|-----|------|

| I <sub>DD_FULL</sub>           | RUN Full Mode                      | LV supply + HV supply + HV Flash supply +                        | —   | 219 | 292 | mA   |

| 2, 3                           | Operating current                  | 2 x HV ADC supplies                                              |     |     |     |      |

|                                |                                    | $T_a = 85^{\circ}C$                                              |     |     |     |      |

|                                |                                    | V <sub>DD_LV</sub> = 1.25 V                                      |     |     |     |      |

|                                |                                    | VDD_HV_A = 5.5V                                                  |     |     |     |      |

|                                |                                    | SYS_CLK = 160MHz                                                 |     |     |     |      |

|                                |                                    | $T_a = 105^{\circ}C$                                             | —   | 230 | 328 | mA   |

|                                |                                    | T <sub>a</sub> = 125 °C                                          | —   | 249 | 400 | mA   |

| I <sub>DD_GWY</sub><br>5, 6    | RUN Gateway<br>Mode Operating      | LV supply + HV supply + HV Flash supply + 2 x HV<br>ADC supplies | _   | 183 | 260 | mA   |

| 0, 0                           | current                            | $T_a = 85^{\circ}C$                                              |     |     |     |      |

|                                |                                    | V <sub>DD_LV</sub> = 1.25 V                                      |     |     |     |      |

|                                |                                    | VDD_HV_A = 5.5V                                                  |     |     |     |      |

|                                |                                    | SYS_CLK = 160MHz                                                 |     |     |     |      |

|                                |                                    | $T_a = 105^{\circ}C$                                             | —   | 196 | 294 | mA   |

|                                |                                    | $T_a = 125^{\circ}C^4$                                           | —   | 215 | 348 | mA   |

| I <sub>DD_BODY_1</sub><br>7, 8 | RUN Body Mode<br>Profile Operating | LV supply + HV supply + HV Flash supply + 2 x HV<br>ADC supplies | -   | 149 | 223 | mA   |

| 7,0                            | current                            | T <sub>a</sub> = 85 °C                                           |     |     |     |      |

|                                |                                    | V <sub>DD_LV</sub> = 1.25 V                                      |     |     |     |      |

|                                |                                    | VDD_HV_A = 5.5V                                                  |     |     |     |      |

|                                |                                    | SYS_CLK = 120MHz                                                 |     |     |     |      |

|                                |                                    | T <sub>a</sub> = 105 °C                                          | —   | 158 | 270 | mA   |

|                                |                                    | $T_{a} = 125^{\circ}C^{4}$                                       | —   | 175 | 310 | mA   |

| IDD_BODY_2 <sup>9, 10</sup>    | RUN Body Mode<br>Profile Operating | LV supply + HV supply + HV Flash supply + 2 x HV<br>ADC supplies | _   | 105 | 174 | mA   |

|                                | current                            | T <sub>a</sub> = 85 °C                                           |     |     |     |      |

|                                |                                    | V <sub>DD_LV</sub> = 1.25 V                                      |     |     |     |      |

|                                |                                    | VDD_HV_A = 5.5V                                                  |     |     |     |      |

|                                |                                    | SYS_CLK = 80MHz                                                  |     |     |     |      |

Table 10. Current consumption characteristics

Table continues on the next page ...

| Symbol   | Parameter    | Conditions <sup>1</sup> | Min | Тур | Max  | Unit |

|----------|--------------|-------------------------|-----|-----|------|------|

| STANDBY0 | STANDBY with | T <sub>a</sub> = 25 °C  |     | 71  | _    | μA   |

|          | 8K RAM       | T <sub>a</sub> = 85 °C  |     | 175 | 800  |      |

|          |              | T <sub>a</sub> = 105 °C | _   | 338 | 1725 | 1    |

|          |              | T <sub>a</sub> = 125 °C | _   | 750 | 2775 |      |

| STANDBY1 | STANDBY with | T <sub>a</sub> = 25 °C  |     | 72  |      | μA   |

|          | 64K RAM      | T <sub>a</sub> = 85 °C  | —   | 176 | 815  | 1    |

|          | -            | T <sub>a</sub> = 105 °C |     | 350 | 1775 | 1    |

|          |              | T <sub>a</sub> = 125 °C | _   | 825 | 3000 | 1    |

| STANDBY2 | STANDBY with | T <sub>a</sub> = 25 °C  | —   | 75  |      | μA   |

|          | 128K RAM     | T <sub>a</sub> = 85 °C  | _   | 182 | 830  | 30   |

|          |              | T <sub>a</sub> = 105 °C | _   | 366 | 1825 |      |

|          |              | T <sub>a</sub> = 125 °C | _   | 900 | 3250 | 1    |

| STANDBY3 | STANDBY with | T <sub>a</sub> = 25 °C  | _   | 80  |      | μA   |

|          | 256K RAM     | T <sub>a</sub> = 85 °C  | _   | 197 | 860  | 1    |

|          |              | T <sub>a</sub> = 105 °C | —   | 400 | 1875 | 1    |

|          |              | T <sub>a</sub> = 125 °C | —   | 975 | 3500 | 1    |

| STANDBY3 | FIRC ON      | T <sub>a</sub> = 25 °C  | _   | 500 | _    | μA   |

Table 12. STANDBY Current consumption characteristics

1. The content of the Conditions column identifies the components that draw the specific current.

# 4.6 Electrostatic discharge (ESD) characteristics

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n + 1) supply pin). This test conforms to the AEC-Q100-002/-003/-011 standard.

#### NOTE

A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device specification requirements. Complete DC parametric and functional testing shall be performed per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

Table 13. ESD ratings

| Symbol                | Parameter               | Conditions <sup>1</sup> | Class | Max value <sup>2</sup> | Unit |

|-----------------------|-------------------------|-------------------------|-------|------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge | T <sub>A</sub> = 25 °C  | H1C   | 2000                   | V    |

|                       | (Human Body Model)      |                         |       |                        |      |

Table continues on the next page ...

### NOTE

The above specification is based on simulation data into an ideal lumped capacitor. Customer should use IBIS models for their specific board/loading conditions to simulate the expected signal integrity and edge rates of their system.

### NOTE

The above specification is measured between 20% / 80%.

# 5.4 DC electrical specifications @ 5 V Range

# Table 17. DC electrical specifications @ 5 V Range

| Symbol                                                       | Parameter                                                          | Va                 | lue                               | Unit |  |

|--------------------------------------------------------------|--------------------------------------------------------------------|--------------------|-----------------------------------|------|--|

|                                                              |                                                                    | Min                | Max                               |      |  |

| VDD_LV                                                       | LV (core) Supply Voltage                                           | 1.08               | 1.32                              | V    |  |

| VDD_HV_x <sup>1</sup>                                        | I/O Supply Voltage                                                 | 4.5                | 5.5                               | V    |  |

| Vih (pad_i_hv)                                               | pad_i_hv Input Buffer High Voltage                                 | 0.7*VDD_HV_x       | VDD_HV_x +<br>0.3                 | V    |  |

| Vil (pad_i_hv)                                               | pad_i_hv Input Buffer Low Voltage                                  | VSS_LV- 0.3        | 0.45*VDD_HV_<br>x                 | V    |  |

| Vhys (pad_i_hv)                                              | pad_i_hv Input Buffer Hysteresis                                   | 0.09*VDD_HV_<br>x  |                                   | V    |  |

| Vih                                                          | CMOS Input Buffer High Voltage (with hysteresis disabled)          | 0.55 *<br>VDD_HV_x | VDD_HV_x +<br>0.3                 | V    |  |

| Vil CMOS Input Buffer Low Voltage (with hysteresis disabled) |                                                                    | VSS_LV - 0.3       | 0.4 *<br>VDD_HV_x                 | V    |  |

| Vhys                                                         | Vhys CMOS Input Buffer Hysteresis                                  |                    |                                   | V    |  |

| Vih_hys                                                      | CMOS Input Buffer High Voltage (with hysteresis enabled)           | 0.65*<br>VDD_HV_x  | VDD_HV_x +<br>0.3                 | V    |  |

| Vil_hys                                                      | CMOS Input Buffer Low Voltage (with hysteresis enabled)            | VSS_LV - 0.3       | 0.35*VDD_HV_<br>x                 | V    |  |

| Pull_IIH (pad_i_hv)                                          | Weak Pullup Current Low                                            | 23                 |                                   | μA   |  |

| Pull_IIH (pad_i_hv)                                          | Weak Pullup Current High                                           |                    | 82                                | μA   |  |

| Pull_IIL (pad_i_hv)                                          | Weak Pulldown Current <sup>3</sup> Low                             | 40                 |                                   | μA   |  |

| Pull_IIL (pad_i_hv)                                          | Weak Pulldown Current <sup>2</sup> High                            |                    | 130                               | μA   |  |

| Pull_loh                                                     | Weak Pullup Current <sup>4</sup>                                   | 30                 | 80                                | μA   |  |

| Pull_lol                                                     | Weak Pulldown Current <sup>5</sup>                                 | 30                 | 80                                | μA   |  |

| linact_d                                                     | Digital Pad Input Leakage Current (weak pull inactive)             | -2.5               | 2.5                               | μA   |  |

| Voh                                                          | Output High Voltage <sup>6</sup>                                   | 0.8 *<br>VDD_HV_x  | —                                 | V    |  |

| Vol                                                          | Output Low Voltage <sup>7</sup><br>Output Low Voltage <sup>8</sup> | _                  | 0.2 *<br>VDD_HV_x<br>0.1*VDD_HV_x | V    |  |

Table continues on the next page...

# 5.6 PORST electrical specifications

#### Table 19. PORST electrical specifications

| Symbol               | Parameter                      |      | Value                       |     |    |  |  |

|----------------------|--------------------------------|------|-----------------------------|-----|----|--|--|

|                      |                                | Min  | Тур                         | Max |    |  |  |

| W <sub>FPORST</sub>  | PORST input filtered pulse     | —    | _                           | 200 | ns |  |  |

| W <sub>NFPORST</sub> | PORST input not filtered pulse | 1000 |                             | —   | ns |  |  |

| V <sub>IH</sub>      | Input high level               | —    | 0.65 x V <sub>DD_HV_A</sub> | —   | V  |  |  |

| V <sub>IL</sub>      | Input low level                | _    | 0.35 x V <sub>DD_HV_A</sub> |     | V  |  |  |

# 6 Peripheral operating requirements and behaviours

# 6.1 Analog

### 6.1.1 ADC electrical specifications

The device provides a 12-bit Successive Approximation Register (SAR) Analog-to-Digital Converter.

### 6.1.2 Analog Comparator (CMP) electrical specifications Table 22. Comparator and 6-bit DAC electrical specifications

| Symbol             | Description                                                          | Min.     | Тур. | Max.                         | Unit             |

|--------------------|----------------------------------------------------------------------|----------|------|------------------------------|------------------|

| I <sub>DDHS</sub>  | Supply current, High-speed mode (EN=1, PMODE=1)                      | _        | —    | 250                          | μA               |

| I <sub>DDLS</sub>  | Supply current, low-speed mode (EN=1, PMODE=0)                       |          | 5    | 11                           | μA               |

| V <sub>AIN</sub>   | Analog input voltage                                                 | $V_{SS}$ | _    | V <sub>IN1_CMP_RE</sub><br>F | V                |

| V <sub>AIO</sub>   | Analog input offset voltage <sup>1</sup>                             | -42      | _    | 42                           | mV               |

| V <sub>H</sub>     | Analog comparator hysteresis <sup>2</sup>                            | _        | 1    | 25                           | mV               |

|                    | • CR0[HYSTCTR] = 00                                                  | _        | 20   | 50                           | mV               |

|                    | • CR0[HYSTCTR] = 01                                                  |          | 40   | 70                           | mV               |

|                    | • CR0[HYSTCTR] = 10                                                  | _        | 60   | 105                          | mV               |

|                    | <ul> <li>CR0[HYSTCTR] = 11</li> </ul>                                |          |      |                              |                  |

| t <sub>DHS</sub>   | Propagation Delay, High Speed Mode (Full Swing) <sup>1, 3</sup>      |          | _    | 250                          | ns               |

| t <sub>DLS</sub>   | Propagation Delay, Low power Mode (Full Swing) <sup>1, 3</sup>       |          | 5    | 21                           | μs               |

|                    | Analog comparator initialization delay, High speed mode <sup>4</sup> | _        | 4    |                              | μs               |

|                    | Analog comparator initialization delay, Low speed mode <sup>4</sup>  | _        | 100  |                              | μs               |

| I <sub>DAC6b</sub> | 6-bit DAC current adder (when enabled)                               |          |      |                              |                  |

|                    | 3.3V Reference Voltage                                               | _        | 6    | 9                            | μA               |

|                    | 5V Reference Voltage                                                 | _        | 10   | 16                           | μA               |

| INL                | 6-bit DAC integral non-linearity                                     | -0.5     | —    | 0.5                          | LSB <sup>5</sup> |

| DNL                | 6-bit DAC differential non-linearity                                 | -0.8     | _    | 0.8                          | LSB              |

1. Measured with hysteresis mode of 00

2. Typical hysteresis is measured with input voltage range limited to 0.6 to  $V_{DD_HV_A}$ -0.6V

3. Full swing = VIH, VIL

4. Comparator initialization delay is defined as the time between software writes to change control inputs (Writes to DACEN, VRSEL, PSEL, MSEL, VOSEL) and the comparator output settling to a stable level.

5. 1 LSB =  $V_{reference}/64$

# 6.2 Clocks and PLL interfaces modules

# 6.2.1 Main oscillator electrical characteristics

This device provides a driver for oscillator in pierce configuration with amplitude control. Controlling the amplitude allows a more sinusoidal oscillation, reducing in this way the EMI. Other benefits arises by reducing the power consumption. This Loop Controlled Pierce (LCP mode) requires good practices to reduce the stray capacitance of traces between crystal and MCU.

An operation in Full Swing Pierce (FSP mode), implemented by an inverter is also available in case of parasitic capacitances and cannot be reduced by using crystal with high equivalent series resistance. For this mode, a special care needs to be taken regarding the serial resistance used to avoid the crystal overdrive.

Other two modes called External (EXT Wave) and disable (OFF mode) are provided. For EXT Wave, the drive is disabled and an external source of clock within CMOS level based in analog oscillator supply can be used. When OFF, EXTAL is pulled down by 240 Kohms resistor and the feedback resistor remains active connecting XTAL through EXTAL by 1M resistor.

#### 6.2.4 128 KHz Internal RC oscillator Electrical specifications Table 26. 128 KHz Internal RC oscillator electrical specifications

| Symbol                         | Parameter                 | Condition     | Min | Тур | Max   | Unit  |

|--------------------------------|---------------------------|---------------|-----|-----|-------|-------|

| F <sub>oscu</sub> <sup>1</sup> | Oscillator<br>frequency   | Calibrated    | 119 | 128 | 136.5 | KHz   |

|                                | Temperature<br>dependence |               |     |     | 600   | ppm/C |

|                                | Supply dependence         |               |     |     | 18    | %/V   |

|                                | Supply current            | Clock running |     |     | 2.75  | μA    |

|                                |                           | Clock stopped |     |     | 200   | nA    |

1. Vdd=1.2 V, 1.32V, T<sub>a</sub>=-40 C, 125 C

### 6.2.5 PLL electrical specifications

#### Table 27. PLL electrical specifications

| Parameter                        | Min       | Тур | Max          | Unit | Comments                                                       |

|----------------------------------|-----------|-----|--------------|------|----------------------------------------------------------------|

| Input Frequency                  | 8         |     | 40           | MHz  |                                                                |

| VCO Frequency Range              | 600       |     | 1280         | MHz  |                                                                |

| Duty Cycle at pllclkout          | 48%       |     | 52%          |      | This specification is guaranteed at PLL IP boundary            |

| Period Jitter                    |           |     | See Table 28 | ps   | NON SSCG mode                                                  |

| TIE                              |           |     | See Table 28 |      | at 960 M Integrated over 1MHz<br>offset not valid in SSCG mode |

| Modulation Depth (Center Spread) | +/- 0.25% |     | +/- 3.0%     |      |                                                                |

| Modulation Frequency             |           |     | 32           | KHz  |                                                                |

| Lock Time                        |           |     | 60           | μs   | Calibration mode                                               |

Table 28. Jitter calculation

| Type of jitter                        | Jitter due to<br>Supply<br>Noise (ps)<br>J <sub>SN</sub> <sup>1</sup> | Jitter due to<br>Fractional Mode<br>(ps) J <sub>SDM</sub> <sup>2</sup> | Jitter due to<br>Fractional Mode<br>J <sub>SSCG</sub> (ps) <sup>3</sup> | 1 Sigma<br>Random<br>Jitter J <sub>RJ</sub><br>(ps) <sup>4</sup> | Total Period Jitter (ps)                                                                      |

|---------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| Period Jitter                         | 60 ps                                                                 | 3% of pllclkout1,2                                                     | Modulation depth                                                        | 0.1% of<br>pllclkout1,2                                          | +/-(J <sub>SN</sub> +J <sub>SDM</sub> +J <sub>SSCG</sub> +N <sup>[4]</sup> ×J <sub>RJ</sub> ) |

| Long Term Jitter<br>(Integer Mode)    |                                                                       |                                                                        |                                                                         | 40                                                               | +/-(N x J <sub>RJ</sub> )                                                                     |

| Long Term jitter<br>(Fractional Mode) |                                                                       |                                                                        |                                                                         | 100                                                              | +/-(N x J <sub>RJ</sub> )                                                                     |

1. This jitter component is due to self noise generated due to bond wire inductances on different PLL supplies. The jitter value is valid for inductor value of 5nH or less each on VDD\_LV and VSS\_LV.

| Symbol               | Characteristic                                                                                                                                                                                                                        | Min                                              | Typical                                        | Max                                              | Units |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------------------------|--------------------------------------------------|-------|

| t <sub>psus</sub>    | Time from setting the MCR-PSUS bit until MCR-DONE bit is set to a 1.                                                                                                                                                                  | _                                                | 9.4<br>plus four<br>system<br>clock<br>periods | 11.5<br>plus four<br>system<br>clock<br>periods  | μs    |

| t <sub>esus</sub>    | Time from setting the MCR-ESUS bit until MCR-DONE bit is set to a 1.                                                                                                                                                                  | _                                                | 16<br>plus four<br>system<br>clock<br>periods  | 20.8<br>plus four<br>system<br>clock<br>periods  | μs    |

| t <sub>res</sub>     | Time from clearing the MCR-ESUS or PSUS bit with EHV = 1 until DONE goes low.                                                                                                                                                         | _                                                | _                                              | 100                                              | ns    |

| t <sub>done</sub>    | Time from 0 to 1 transition on the MCR-EHV bit initiating a program/erase until the MCR-DONE bit is cleared.                                                                                                                          | _                                                | —                                              | 5                                                | ns    |

| t <sub>dones</sub>   | Time from 1 to 0 transition on the MCR-EHV bit aborting a program/erase until the MCR-DONE bit is set to a 1.                                                                                                                         | _                                                | 16<br>plus four<br>system<br>clock<br>periods  | 20.8<br>plus four<br>system<br>clock<br>periods  | μs    |

| t <sub>drcv</sub>    | Time to recover once exiting low power mode.                                                                                                                                                                                          | 16<br>plus seven<br>system<br>clock<br>periods.  | _                                              | 45<br>plus seven<br>system<br>clock<br>periods   | μs    |

| t <sub>aistart</sub> | Time from 0 to 1 transition of UT0-AIE initiating a Margin Read<br>or Array Integrity until the UT0-AID bit is cleared. This time also<br>applies to the resuming from a suspend or breakpoint by<br>clearing AISUS or clearing NAIBP | _                                                |                                                | 5                                                | ns    |

| t <sub>aistop</sub>  | Time from 1 to 0 transition of UT0-AIE initiating an Array<br>Integrity abort until the UT0-AID bit is set. This time also applies<br>to the UT0-AISUS to UT0-AID setting in the event of a Array<br>Integrity suspend request.       |                                                  |                                                | 80<br>plus fifteen<br>system<br>clock<br>periods | ns    |

| t <sub>mrstop</sub>  | Time from 1 to 0 transition of UT0-AIE initiating a Margin Read<br>abort until the UT0-AID bit is set. This time also applies to the<br>UT0-AISUS to UT0-AID setting in the event of a Margin Read<br>suspend request.                | 10.36<br>plus four<br>system<br>clock<br>periods |                                                | 20.42<br>plus four<br>system<br>clock<br>periods | μs    |

# 6.3.5 Flash memory AC timing specifications

Table 33. Flash memory AC timing specifications

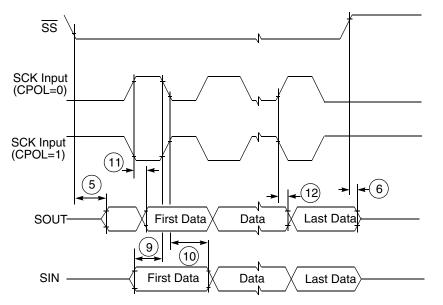

| No | Symbol           | Parameter                        | Conditions                     | High Spo | eed Mode | low Spe         | ed mode         | Unit |

|----|------------------|----------------------------------|--------------------------------|----------|----------|-----------------|-----------------|------|

|    |                  |                                  |                                | Min      | Max      | Min             | Max             |      |

|    |                  |                                  | Master (MTFE = 1,<br>CPHA = 1) | 15       | _        | 20              | _               |      |

| 10 | t <sub>HI</sub>  | Data hold                        | Master (MTFE = 0)              | NA       | —        | -5              | _               | ns   |

|    |                  | time for<br>inputs               | Slave                          | 4        | —        | 4               | _               |      |

|    |                  | inputs                           | Master (MTFE = 1,<br>CPHA = 0) | 0        | —        | 11 <sup>1</sup> | _               |      |

|    |                  |                                  | Master (MTFE = 1,<br>CPHA = 1) | 0        | _        | -5              | _               |      |

| 11 | t <sub>suo</sub> | Data valid                       | Master (MTFE = 0)              | —        | NA       | —               | 4               | ns   |

|    |                  | (after SCK<br>edge)              | Slave                          | —        | 15       | —               | 23              |      |

|    |                  | euge)                            | Master (MTFE = 1,<br>CPHA = 0) | _        | 4        | —               | 16 <sup>1</sup> |      |

|    |                  |                                  | Master (MTFE = 1,<br>CPHA = 1) | —        | 4        | _               | 4               |      |

| 12 | t <sub>HO</sub>  | Data hold<br>time for<br>outputs | Master (MTFE = 0)              | NA       | _        | -2              | _               | ns   |

|    |                  |                                  | Slave                          | 4        | _        | 6               | _               |      |

|    |                  |                                  | Master (MTFE = 1,<br>CPHA = 0) | -2       | -        | 10 <sup>1</sup> | -               |      |

|    |                  |                                  | Master (MTFE = 1,<br>CPHA = 1) | -2       | —        | -2              | —               |      |

Table 35. DSPI electrical specifications (continued)

1. SMPL\_PTR should be set to 1

#### NOTE

Restriction For High Speed modes

- DSPI2, DSPI3, SPI1 and SPI2 will support 40MHz Master mode SCK

- DSPI2, DSPI3, SPI1 and SPI2 will support 25MHz Slave SCK frequency

- Only one {SIN,SOUT and SCK} group per DSPI/SPI will support high frequency mode

- For Master mode MTFE will be 1 for high speed mode

- For high speed slaves, their master have to be in MTFE=1 mode or should be able to support 15ns tSUO delay

### NOTE

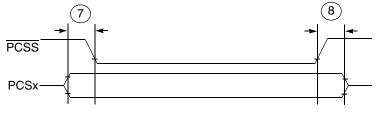

For numbers shown in the following figures, see Table 35

FlexRay electrical specifications

Figure 15. DSPI modified transfer format timing — slave, CPHA = 1

Figure 16. DSPI PCS strobe (PCSS) timing

## 6.4.2 FlexRay electrical specifications

### 6.4.2.1 FlexRay timing

This section provides the FlexRay Interface timing characteristics for the input and output signals. It should be noted that these are recommended numbers as per the FlexRay EPL v3.0 specification, and subject to change per the final timing analysis of the device.

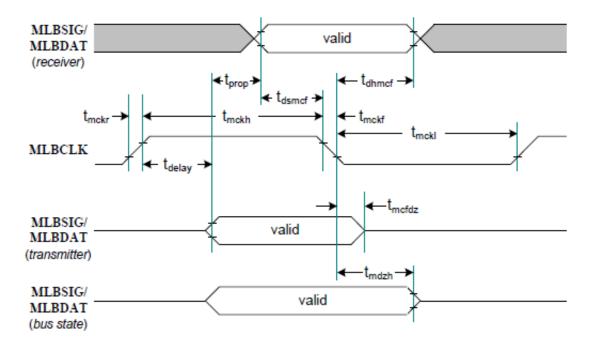

# 6.4.5 MediaLB (MLB) electrical specifications

### 6.4.5.1 MLB 3-pin interface DC characteristics

The section lists the MLB 3-pin interface electrical characteristics.

Table 44. MediaLB 3-Pin Interface Electrical DC Specifications

| Parameter                   | Symbol          | Test Conditions          | Min | Max | Unit |

|-----------------------------|-----------------|--------------------------|-----|-----|------|

| Maximum input voltage       | —               | —                        | -   | 3.6 | V    |

| Low level input threshold   | V <sub>IL</sub> | -                        | —   | 0.7 | V    |

| High level input threshold  | V <sub>IH</sub> | See Note <sup>1</sup>    | 1.8 | —   | V    |

| Low level output threshold  | V <sub>OL</sub> | $I_{OL} = -6 \text{ mA}$ | —   | 0.4 | V    |

| High level output threshold | V <sub>OH</sub> | I <sub>OH</sub> = –6 mA  | 2.0 | —   | V    |

| Input leakage current       | IL              | 0 < Vin < VDD            | —   | ±10 | μA   |

1. Higher  $V_{\text{IH}}$  thresholds can be used; however, the risks associated with less noise margin in the system must be evaluated and assumed by the customer.

### 6.4.5.2 MLB 3-pin interface electrical specifications

This section describes the timing electrical information of the MLB module.

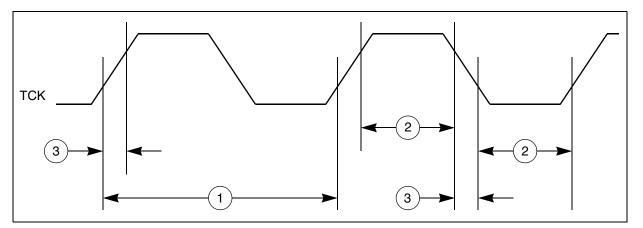

Figure 28. JTAG test clock input timing

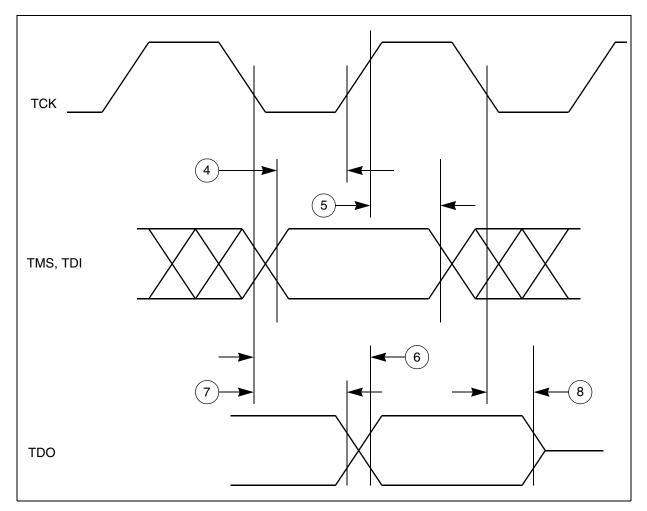

Figure 29. JTAG test access port timing

# 9 Pinouts

# 9.1 Package pinouts and signal descriptions

For package pinouts and signal descriptions, refer to the Reference Manual.

# 10 Reset sequence

This section describes different reset sequences and details the duration for which the device remains in reset condition in each of those conditions.

# 10.1 Reset sequence duration

Table 54 specifies the minimum and the maximum reset sequence duration for the five different reset sequences described in Reset sequence description.

| No. | Symbol            | Parameter                                      |       | T <sub>Reset</sub> |     |    |

|-----|-------------------|------------------------------------------------|-------|--------------------|-----|----|

|     |                   |                                                | Min   | Typ <sup>1</sup>   | Max |    |

| 1   | T <sub>DRB</sub>  | Destructive Reset Sequence, BIST enabled       | 5.730 | 7.796              |     | ms |

| 2   | T <sub>DR</sub>   | Destructive Reset Sequence, BIST disabled      |       | 0.182              |     | ms |

| 3   | T <sub>ERLB</sub> | External Reset Sequence Long, Unsecure Boot    |       | 7.793              |     | ms |

| 4   | T <sub>FRL</sub>  | Functional Reset Sequence Long, Unsecure Boot  | 0.110 | 0.179              |     | ms |

| 5   | T <sub>FRS</sub>  | Functional Reset Sequence Short, Unsecure Boot | 0.007 | 0.009              |     | ms |

Table 54. RESET sequences

1. The Typ value is applicable only if the reset sequence duration is not prolonged by an extended assertion of RESET\_B by an external reset generator.

# 10.2 BAF execution duration

Following table specifies the typical BAF execution time in case BAF boot header is present at first location (Typical) and last location (worst case). Total Boot time is the sum of reset sequence duration and BAF execution time.

| BAF execution<br>duration                                | Min | Тур | Мах | Unit |

|----------------------------------------------------------|-----|-----|-----|------|

| BAF execution time<br>(boot header at first<br>location) | -   | 200 | -   | μs   |

| BAF execution time<br>(boot header at last<br>location)  | -   | 320 | -   | μs   |

Table 55. BAF execution duration

# 10.3 Reset sequence description

The figures in this section show the internal states of the device during the five different reset sequences. The dotted lines in the figures indicate the starting point and the end point for which the duration is specified in Table 54.

With the beginning of DRUN mode, the first instruction is fetched and executed. At this point, application execution starts and the internal reset sequence is finished.

The following figures show the internal states of the device during the execution of the reset sequence and the possible states of the RESET\_B signal pin.

#### NOTE

RESET\_B is a bidirectional pin. The voltage level on this pin can either be driven low by an external reset generator or by the device internal reset circuitry. A high level on this pin can only be generated by an external pullup resistor which is strong enough to overdrive the weak internal pulldown resistor. The rising edge on RESET\_B in the following figures indicates the time when the device stops driving it low. The reset sequence durations given in Table 54 are applicable only if the internal reset sequence is not prolonged by an external reset generator keeping RESET\_B asserted low beyond the last Phase3.

| Rev. No. | Date        | Substantial Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |             | <ul> <li>Revised Electromagnetic Interference (EMI) characteristics section</li> <li>Revised DC electrical specifications @ 3.3V Range table for naming convections.</li> <li>Revised DC electrical specifications @ 5 V Range table for naming conventions</li> <li>Deleted MLB 6-pin Electrical Specifications</li> <li>Removed PORST characteristics from Functional reset pad electrical characteristics table</li> <li>Added section PORST electrical characteristics</li> <li>Revised Input impedance and ADC accuracy section to remove SNR, THD, SINAD, ENOB,</li> <li>Revised 32 kHz oscillator electrical specifications table to remove 'Vpp' row.</li> <li>Updated 16 MHz RC Oscillator electrical specifications table for statuptime, cycle to cycle jitter, and lonf term jitter</li> <li>Updated 128 KHz Internal RC oscillator electrical specifications table.</li> <li>Updated PLL electrical specifications table</li> <li>Added Jitter Calculation table</li> <li>Added Percentage of Sample exceeding specified value of jitter table</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|          |             | <ul> <li>Revised Memory interfaces section</li> <li>Revised Communication interfaces section <ul> <li>Updated note</li> <li>Added Continuous SCK timing table</li> <li>Added DSPI high speed mode I/Os table</li> </ul> </li> <li>Updated input transition value in section MLB 3-pin interface electrical specifications</li> <li>Deleted MLB 6-pin interface DC characteristics section</li> <li>Deleted MLB 6-pin interface AC characteristics section</li> <li>Updated JTAG pin AC electrical characteristics table</li> <li>Revised table under Thermal attributes section</li> <li>Updated Obtaining package dimensions section for Freescale Document numbers</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3        | 12 May 2015 | <ul> <li>Editorial updates throughout the sections</li> <li>Renamed '176 LQFP' package to '176 LQFP-EP'</li> <li>Added following sections: <ul> <li>Block diagram</li> <li>Family comparison</li> <li>Ordering Information</li> </ul> </li> <li>In table: Absolute maximum ratings as follows: <ul> <li>Removed row for symbol: 'V<sub>SS_HV</sub>'</li> <li>Added symbol: 'V<sub>DD_LV</sub>'</li> <li>Updated 'Max' column for symbol 'V<sub>INA</sub>'</li> <li>Added footnote to 'Conditions' column</li> <li>Removed footnote from 'Max' column</li> </ul> </li> <li>In section: Recommended operating conditions <ul> <li>Added note: "V<sub>DD_HV_A</sub>, V<sub>DD_HV_B</sub> and V<sub>DD_HV_C</sub> are all "</li> <li>Added footnote to 'Conditions' cloumn</li> <li>In table: Recommended operating conditions (V<sub>DD_HV_X</sub> = 3.3 V)</li> <li>Added footnote to 'Conditions' cloumn</li> <li>Updated footnote for 'Min' column</li> <li>Bemoved footnote for Symbol: 'V<sub>SS_HV</sub>'</li> <li>Updated footnote for Symbol: 'V<sub>SS_HV</sub>'</li> <li>Updated footnote for Symbols' V<sub>DD_HV_A</sub>', 'V<sub>DD_HV_B</sub> and 'V<sub>DD_HV_C</sub>'</li> <li>Removed footnote for Symbol: 'V<sub>SS_HV</sub>'</li> <li>Updated footnote for Symbol: 'V<sub>SS_HV</sub>'</li> <li>Updated footnote for Symbol: 'V<sub>SS_HV</sub>'</li> <li>Updated 'Parameter' column for symbol 'V<sub>DD_HV_A</sub>', 'V<sub>DD_HV_A</sub>DC1_REF', 'V<sub>DD_LV</sub>'</li> <li>Updated 'Parameter' Min' 'Max' column for symbol 'V<sub>SS_HV_ADC0</sub>' and 'V<sub>SS_HV_ADC0</sub>' and 'V<sub>SS_HV_ADC0</sub>'</li> <li>Removed footnote to symbol 'V<sub>DD_LV</sub>'</li> <li>Added footnote to symbol 'V<sub>DD_LV</sub>'</li> </ul> </li> </ul> |

Table 56.

Revision History (continued)

Table continues on the next page...