# E·XFL\_Toshiba Semiconductor and Storage - <u>TMPM333FYFG(C)</u> Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                               |

|----------------------------|--------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 40MHz                                                                                |

| Connectivity               | I <sup>2</sup> C, SIO, UART/USART                                                    |

| Peripherals                | POR, WDT                                                                             |

| Number of I/O              | 78                                                                                   |

| Program Memory Size        | 256KB (256K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 16K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                          |

| Data Converters            | A/D 12x10b                                                                           |

| Oscillator Type            | External                                                                             |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 100-LQFP                                                                             |

| Supplier Device Package    | 100-LQFP (14x14)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/toshiba-semiconductor-and-storage/tmpm333fyfg-c |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

8.2.2.2 Port B Register 8.2.2.3 PBDATA (Port B data register) 8.2.2.4 PBCR (Port B output control register) 8.2.2.5 PBFR1 (Port B function register 1) 8.2.2.6 PBPUP (Port B pull-up control register) 8.2.2.7 PBIE (Port B input control register) Port C Circuit Type 8231 Port C Register 8232 PCDATA (Port C data register) 8.2.3.3 PCPUP (Port C pull-up control register) 8.2.3.4 PCIE (Port C input control register) 8.2.3.5 8.2.4 Port D (PD0 to PD7).. 8241 Port D Circuit Type 8.2.4.2 Port D Register 8.2.4.3 PDDATA (Port D data register) 8.2.4.4 PDFR1 (Port D function register 1) 8245 PDPUP (Port D pull-up control register) 8.2.4.6 PDIE (Port D input control register) 8.2.5.1 Port E Circuit Type 8.2.5.2 Port E Register PEDATA (Port E data register) 8.2.5.3 8.2.5.4 PECR (Port E output control register) PEFR1(Port E function register 1) 8.2.5.5 8.2.5.6 PEFR2(Port E function register 2) PEOD (Port E open drain control register) 8.2.5.7 8258 PEPUP (Port E pull-up control register) 8.2.5.9 PEIE (Port E input control register) 8.2.6 Port F (PF0 to PF7)......126 8.2.6.1 Port F Circuit Type 8262 Port F Register PFDATA (Port F data register) 8.2.6.3 8.2.6.4 PFCR (Port F output control register) PFFR1(Port F function register 1) 8.2.6.5 PFFR2(Port F function register 2) 8.2.6.6 PFOD (Port F open drain control register) 8267 PFPUP (Port F pull-up control register) 8.2.6.8 PFIE (Port F input control register) 8.2.6.9 8.2.7.1 Port G Circuit Type 8.2.7.2 Port G Register 8.2.7.3 PGDATA (Port G data register) 8.2.7.4 PGCR (Port G output control register) 8.2.7.5 PGFR1(Port G function register 1) 8.2.7.6 PGOD (Port G open drain control register) 8.2.7.7 PGPUP (Port G pull-up control register) 8.2.7.8 PGIE (Port G input control register) Port H Circuit Type 8.2.8.1 8.2.8.2 Port H Register PHDATA (Port H data register) 8.2.8.3 8.2.8.4 PHCR (Port H output control register) 8.2.8.5 PHFR1(Port H function register 1) 8.2.8.6 PHPUP (Port H pull-up control register) 8.2.8.7 PHIE (Port H input control register) 8.2.9 Port I (PI0 to PI7)......140 Port I Circuit Type 8291 8292 Port I Register 8293 PIDATA(Port I data register) 8.2.9.4 PICR (Port I output control register) 8295 PIFR1(Port I function register 1) 8.2.9.6 PIPUP (Port I pull-up control register) 8.2.9.7 PIIE (Port I input control register) 8.2.10 Port J (PJ0 to PJ7).... 144 8.2.10.1 Port J Circuit Type 8.2.10.2 Port J Register 8.2.10.3 PJDATA (Port J data register) 8.2.10.4 PJCR (Port J output control register) 8.2.10.5 PJFR1(Port J function register 1) 8.2.10.6 PJPUP (Port J pull-up control register) 8.2.10.7 PJIE (Port J input control register) 8.2.11 Port K (PK0 to PK2).... 8.2.11.1 Port K Circuit Type

iv

Port K Register

PKDATA(Port K data register)

8.2.11.2

8.2.11.3

# Table 1-1 Pin Names and Functions Sorted by Pin (3/6)

| Туре               | Pin<br>No. | Pin Name              | Input/<br>Output | Function                                                                                           |

|--------------------|------------|-----------------------|------------------|----------------------------------------------------------------------------------------------------|

| Function           | 36         | PH3<br>TB1IN1         | I/O<br>I         | I/O port<br>Inputting the timer B capture trigger                                                  |

| Function           | 37         | PB4                   | I/O              | I/O port                                                                                           |

| Function           | 38         | PI0<br>TB0OUT         | 1/O<br>O         | I/O port<br>Timer B output                                                                         |

| Function           | 39         | PJ6<br>INT6           | I/O<br>I         | I/O port<br>External interrupt pin                                                                 |

| Function           | 40         | PI1<br>TB1OUT         | 1/O<br>O         | I/O port<br>Timer B output                                                                         |

| Function           | 41         | PB5                   | I/O              | I/O port                                                                                           |

| Function           | 42         | PI2<br>TB2OUT         | 1/O<br>O         | I/O port<br>Timer B output                                                                         |

| Function           | 43         | PB6                   | I/O              | I/O port                                                                                           |

| Function           | 44         | PF4<br>SDA1/SO1       | I/O<br>I/O       | I/O port<br>-in the I2C mode: data pin<br>-in the SIO mode: data pin                               |

| Function           | 45         | PF5<br>SCL1/SI1       | I/O<br>I/O       | I/O port<br>-in the I2C mode: clock pin<br>-in the SIO mode: data pin                              |

| Function           | 46         | PF6<br>SCK1           | 1/O<br>1/O       | I/O port<br>Inputting and outputting a clock if the serial bus interface operates in the SIO mode. |

| Function           | 47         | PB7                   | I/O              | I/O port                                                                                           |

| Function           | 48         | PI3<br>TB3OUT         | 1/O<br>O         | I/O port<br>Timer B output                                                                         |

| Function           | 49         | PJ1<br>INT1           | I/O<br>I         | I/O port<br>External interrupt pin                                                                 |

| Function           | 50         | РКО                   | I/O              | I/O port<br>(note) Nch open drain port.                                                            |

| Function           | 51         | PK1<br>SCOUT<br>ALARM | I/O<br>O<br>O    | I/O port<br>System clock output<br>Alarm output                                                    |

| Function           | 52         | PI4<br>TB4OUT         | 1/O<br>O         | I/O port<br>Timer B output                                                                         |

| Function           | 53         | PI5<br>TB5OUT         | 1/O<br>O         | I/O port<br>Timer B output                                                                         |

| Function/<br>Debug | 54         | PB0<br>TDO/SWV        | 1/O<br>O         | I/O port<br>Debug pin                                                                              |

| Function/<br>Debug | 55         | PA0<br>TMS/SWDIO      | I/O<br>I/O       | I/O port<br>Debug pin                                                                              |

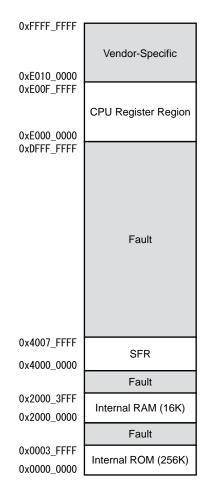

# 4.1.2 Memory Map of TMPM333FYFG

Figure 4-2 shows the memory map of the TMPM333FYFG.

# Figure 4-2 Memory Map (TMPM333FYFG)

Note: In addition to 256KB flash area, the TMPM333FYFG provides 128-word data/ password area (1 page) for Show Product Information command in the address range 0x0007\_FE00 - 0x0007\_FFFF. See the Chapter "Flash Memory Operation" for details on the single boot mode.

Do not Access to the range from 0x0004\_0000 through the password area.

# 6.6.6 Releasing the Low Power Consumption Mode

The low power consumption mode can be released by an interrupt request, Non-Maskable Interrupt (NMI) or reset. The release source that can be used is determined by the low power consumption mode selected.

Details are shown in Table 6-8.

| Table 6-8 Release So | ource in Each Mode |

|----------------------|--------------------|

|----------------------|--------------------|

|         | Low pow   | ver consumption mode     | IDLE | SLEEP | STOP |

|---------|-----------|--------------------------|------|-------|------|

|         |           | INT0 to 7 (Note1)        | 0    | 0     | 0    |

|         |           | INTRTC                   | о    | 0     | ×    |

|         |           | INTTB0 to 9              | о    | ×     | ×    |

|         | Interrupt | INTCAP00 to 60, 01 to 61 | о    | ×     | ×    |

| Release |           | INTRX0 to 2, INTTX0 to 2 | о    | ×     | ×    |

| source  |           | INTSBI0 to 2             | о    | ×     | ×    |

|         |           | INTAD/INTADHP/INTADM0, 1 | 0    | ×     | ×    |

|         | NMI (INTW | /DT)                     | 0    | ×     | ×    |

|         | NMI (NMI  | pin)                     | 0    | 0     | 0    |

|         | RESET (R  | ESET pin)                | 0    | 0     | 0    |

o: Starts the interrupt handling after the mode is released. (The reset initializes the LSI)

×: Unavailable

- Note 1: To release the low power consumption mode by using the level mode interrupt, keep the level until the interrupt handling is started. Changing the level before then will prevent the interrupt handling from starting properly.

- Note 2: For shifting to the low power consumption mode, set the CPU to prohibit all the interrupts other than the release source. If not, releasing may be executed by an unspecified interrupt.

#### • <u>Release by interrupt request</u>

To release the low power consumption mode by an interrupt, the CPU must be set in advance to detect the interrupt. In addition to the setting in the CPU, the clock generator must be set to detect the interrupt to be used to release the SLEEP and STOP modes.

• <u>Release by Non-Maskable Interrupt (NMI)</u>

There are two kinds of NMI sources: WDT interrupt (INTWDT) and NMI pin. INTWDT can only be used in the IDLE mode. The NMI pin can be used to release all the lower power consumption modes.

<u>Release by reset</u>

Any low power consumption mode can be released by reset from the  $\overline{\text{RESET}}$  pin. After that, the mode switches to the NORMAL mode and all the registers are initialized as is the case with normal reset.

Note that returning to the STOP mode by reset does not induce the automatic warm-up. Keep the reset signal valid until the oscillator operation becomes stable.

Refer to "Interrupts" for details.

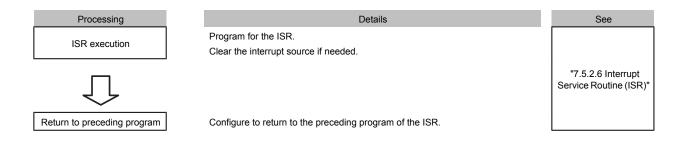

#### 7.5.2.2 Preparation

When preparing for an interrupt, you need to pay attention to the order of configuration to avoid any unexpected interrupt on the way.

Initiating an interrupt or changing its configuration must be implemented in the following order basically. Disable the interrupt by the CPU. Configure from the farthest route from the CPU. Then enable the interrupt by the CPU.

To configure the clock generator, you must follow the order indicated here not to cause any unexpected interrupt. First, configure the precondition. Secondly, clear the data related to the interrupt in the clock generator and then enable the interrupt.

The following sections are listed in the order of interrupt handling and describe how to configure them.

- 1. Disabling interrupt by CPU

- 2. CPU registers setting

- 3. Preconfiguration (1) (Interrupt from external pin)

- 4. Preconfiguration (2) (Interrupt from peripheral function)

- 5. Preconfiguration (3) (Interrupt Set-Pending Register)

- 6. Configuring the clock generator

- 7. Enabling interrupt by CPU

#### (1) Disabling interrupt by CPU

To make the CPU for not accepting any interrupt, write "1" to the corresponding bit of the PRIMASK Register. All interrupts and exceptions other than non-maskable interrupts and hard faults can be masked.

Use "MSR" instruction to set this register.

| Interrupt mask register |   |                          |  |  |  |  |

|-------------------------|---|--------------------------|--|--|--|--|

| PRIMASK                 | ← | "1" (interrupt disabled) |  |  |  |  |

Note 1: PRIMASK register cannot be modified by the user access level.

Note 2: If a fault causes when "1" is set to the PRIMASK register, it is treated as a hard fault.

#### (2) CPU registers setting

You can assign a priority level by writing to <PRI\_n> field in an Interrupt Priority Register of the NVIC register.

|             | 31               | 30                 | 29                 | 28                 | 27              | 26              | 25              | 24              |

|-------------|------------------|--------------------|--------------------|--------------------|-----------------|-----------------|-----------------|-----------------|

| bit symbol  | -                | -                  | -                  | -                  | -               | -               | -               | -               |

| After reset | 0                | 0                  | 0                  | 0                  | 0               | 0               | 0               | 0               |

|             | 23               | 22                 | 21                 | 20                 | 19              | 18              | 17              | 16              |

| bit symbol  | -                | -                  | -                  | -                  | -               | USGFAULT<br>ENA | BUSFAULT<br>ENA | MEMFAULT<br>ENA |

| After reset | 0                | 0                  | 0                  | 0                  | 0               | 0               | 0               | 0               |

|             | 15               | 14                 | 13                 | 12                 | 11              | 10              | 9               | 8               |

| bit symbol  | SVCALL<br>PENDED | BUSFAULT<br>PENDED | MEMFAULT<br>PENDED | USGFAULT<br>PENDED | SYSTICKACT      | PENDSVACT       | -               | MONITOR<br>ACT  |

| After reset | 0                | 0                  | 0                  | 0                  | 0               | 0               | 0               | 0               |

|             | 7                | 6                  | 5                  | 4                  | 3               | 2               | 1               | 0               |

| bit symbol  | SVCALLACT        | -                  | -                  | -                  | USGFAULT<br>ACT | -               | BUSFAULT<br>ACT | MEMFAULT<br>ACT |

| After reset | 0                | 0                  | 0                  | 0                  | 0               | 0               | 0               | 0               |

# 7.6.2.17 System Handler Control and State Register

| Bit   | Bit Symbol | Туре | Function          |

|-------|------------|------|-------------------|

| 31-19 | -          | R    | Read as 0.        |

| 18    | USGFAULT   | R/W  | Usage Fault       |

|       | ENA        |      | 0: Disabled       |

|       |            |      | 1: Enable         |

| 17    | BUSFAUL    | R/W  | Bus Fault         |

|       | TENA       |      | 0: Disabled       |

|       |            |      | 1: Enable         |

| 16    | MEMFAULT   | R/W  | Memory Management |

|       | ENA        |      | 0: Disabled       |

|       |            |      | 1: Enable         |

| 15    | SVCALL     | R/W  | SVCall            |

|       | PENDED     |      | 0: Not pended     |

|       |            |      | 1: Pended         |

| 14    | BUSFAULT   | R/W  | Bus Fault         |

|       | PENDED     |      | 0: Not pended     |

|       |            |      | 1: Pended         |

| 13    | MEMFAULT   | R/W  | Memory Management |

|       | PENDED     |      | 0: Not pended     |

|       |            |      | 1: Pended         |

| 12    | USGFAULT   | R/W  | Usage Fault       |

|       | PENDED     |      | 0: Not pended     |

|       |            |      | 1: Pended         |

| 11    | SYSTICKACT | R/W  | SysTick           |

|       |            |      | 0: Inactive       |

|       |            |      | 1: Active         |

| 10    | PENDSVACT  | R/W  | PendSV            |

|       |            |      | 0: Inactive       |

|       |            |      | 1: Active         |

| 9     | -          | R    | Read as 0.        |

| 8     | MONITORACT | R/W  | Debug Monitor     |

|       |            |      | 0: Inactive       |

|       |            |      | 1: Active         |

| 7     | SVCALLACT  | R/W  | SVCall            |

|       |            |      | 0: Inactive       |

|       |            |      | 1: Active         |

| 6-4   | -          | R    | Read as 0.        |

Page 89

#### 8.2 Port functions

|             | 31 | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-------------|----|-----|-----|-----|-----|-----|-----|-----|

| bit symbol  | -  | -   | -   | -   | -   | -   | -   | -   |

| After reset | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

|             | 23 | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| bit symbol  | -  | -   | -   | -   | -   | -   | -   | -   |

| After reset | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

|             | 15 | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| bit symbol  | -  | -   | -   | -   | -   | -   | -   | -   |

| After reset | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

|             | 7  | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| bit symbol  | -  | PE6 | PE5 | PE4 | PE3 | PE2 | PE1 | PE0 |

| After reset | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

# 8.2.5.3 PEDATA (Port E data register)

| Bit  | Bit Symbol | Туре | Function             |

|------|------------|------|----------------------|

| 31-7 | -          | R    | Read as 0.           |

| 6-0  | PE6-PE0    | R/W  | Port E data register |

# 8.2.5.4 PECR (Port E output control register)

|             | 31 | 30   | 29   | 28   | 27   | 26   | 25   | 24   |

|-------------|----|------|------|------|------|------|------|------|

| bit symbol  | -  | -    | -    | -    | -    | -    | -    | -    |

| After reset | 0  | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

|             | 23 | 22   | 21   | 20   | 19   | 18   | 17   | 16   |

| bit symbol  | -  | -    | -    | -    | -    | -    | -    | -    |

| After reset | 0  | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

|             | 15 | 14   | 13   | 12   | 11   | 10   | 9    | 8    |

| bit symbol  | -  | -    | -    | -    | -    | -    | -    | -    |

| After reset | 0  | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

|             | 7  | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| bit symbol  | -  | PE6C | PE5C | PE4C | PE3C | PE2C | PE1C | PE0C |

| After reset | 0  | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| Bit  | Bit Symbol | Туре | Function                          |

|------|------------|------|-----------------------------------|

| 31-7 | -          | R    | Read as 0.                        |

| 6-0  | PE6C-PE0C  | R/W  | Output<br>0: Disable<br>1: Enable |

#### 8.2 Port functions

|             | 31    | 30    | 29    | 28    | 27    | 26    | 25    | 24    |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|

| bit symbol  | -     | -     | -     | -     | -     | -     | -     | -     |

| After reset | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|             | 23    | 22    | 21    | 20    | 19    | 18    | 17    | 16    |

| bit symbol  | -     | -     | -     | -     | -     | -     | -     | -     |

| After reset | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|             | 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     |

| bit symbol  | -     | -     | -     | -     | -     | -     | -     | -     |

| After reset | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|             | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

| bit symbol  | PF7F1 | PF6F1 | PF5F1 | PF4F1 | PF3F1 | PF2F1 | PF1F1 | PF0F1 |

| After reset | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

# 8.2.6.5 PFFR1(Port F function register 1)

| Bit  | Bit Symbol | Туре | Function    |

|------|------------|------|-------------|

| 31-8 | -          | R    | Read as 0.  |

| 7    | PF7F1      | R/W  | 0: PORT     |

|      |            |      | 1: INT5     |

| 6    | PF6F1      | R/W  | 0: PORT     |

|      |            |      | 1: SCK1     |

| 5    | PF5F1      | R/W  | 0: PORT     |

|      |            |      | 1: SI1/SCL1 |

| 4    | PF4F1      | R/W  | 0: PORT     |

|      |            |      | 1: SO1/SDA1 |

| 3    | PF3F1      | R/W  | 0: PORT     |

|      |            |      | 1: Reserved |

| 2    | PF2F1      | R/W  | 0: PORT     |

|      |            |      | 1: SCLK2    |

| 1    | PF1F1      | R/W  | 0: PORT     |

|      |            |      | 1: RXD2     |

| 0    | PF0F1      | R/W  | 0: PORT     |

|      |            |      | 1: TXD2     |

# 8.3.19 Type T18

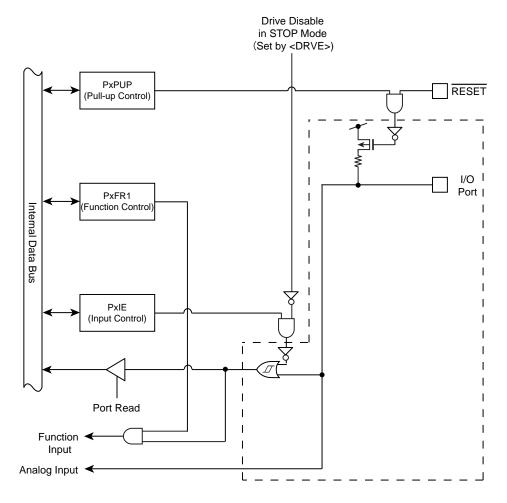

Figure 8-18 Port TypeT18

# 8.4.7 Port G Setting

| Pin | Port<br>Type | Function           | After re-<br>set | PGCR | PGFR1 | PGOD | PGPUP | PGIE |

|-----|--------------|--------------------|------------------|------|-------|------|-------|------|

|     | Input Port   |                    | 0                | 0    | х     | x    | 1     |      |

| 500 | 740          | Output Port        |                  | 1    | 0     | х    | x     | 0    |

| PG0 | T13          | SO0(Output)        |                  | 1    | 1     | x    | x     | 0    |

|     |              | SDA0(Input/Output) |                  | 1    | 1     | 1    | x     | 1    |

|     |              | Input Port         |                  | 0    | 0     | x    | x     | 1    |

| DO1 | T13          | Output Port        |                  | 1    | 0     | x    | x     | 0    |

| PG1 | 113          | SI0(Input)         |                  | 0    | 1     | x    | x     | 1    |

|     |              | SCL0(Input/Output) |                  | 1    | 1     | 1    | x     | 1    |

|     |              | Input Port         |                  | 0    | 0     | x    | x     | 1    |

| 500 |              | Output Port        |                  | 1    | 0     | x    | x     | 0    |

| PG2 | T13          | SCK0(Input)        |                  | 0    | 1     | x    | x     | 1    |

|     |              | SCK0(Output)       |                  | 1    | 1     | x    | x     | 0    |

|     |              | Input Port         |                  | 0    | 0     | x    | x     | 1    |

| PG3 | Т8           | Output Port        |                  | 1    | 0     | x    | x     | 0    |

|     |              | INT4(Input)        |                  | 0    | 1     | x    | x     | 1    |

|     |              | Input Port         |                  | 0    | 0     | x    | x     | 1    |

| 504 |              | Output Port        |                  | 1    | 0     | x    | x     | 0    |

| PG4 | T13          | SO2(Output)        |                  | 1    | 1     | x    | x     | 0    |

|     |              | SDA2(Input/Output) |                  | 1    | 1     | 1    | x     | 1    |

|     |              | Input Port         |                  | 0    | 0     | x    | x     | 1    |

| 505 |              | Output Port        |                  | 1    | 0     | x    | x     | 0    |

| PG5 | T13          | SI2(Input)         |                  | 0    | 1     | x    | x     | 1    |

|     |              | SCL2(Input/Output) |                  | 1    | 1     | 1    | x     | 1    |

|     |              | Input Port         |                  | 0    | 0     | x    | x     | 1    |

| 500 |              | Output Port        |                  | 1    | 0     | x    | x     | 0    |

| PG6 | T13          | SCK2(Input)        |                  | 0    | 1     | х    | x     | 1    |

|     |              | SCK2(Output)       |                  | 1    | 1     | х    | x     | 0    |

|     |              | Input Port         |                  | 0    | 0     | х    | x     | 1    |

| PG7 | T10          | Output Port        |                  | 1    | 0     | х    | x     | 0    |

|     |              | TB8OUT(Output)     |                  | 1    | 1     | х    | x     | 0    |

# 9.6 Description of Operations for Each Mode

# 9.6.1 16-bit Interval Timer Mode

In the case of generating constant period interrupt, set the interval time to the Timer register (TBxRG1) to generate the INTTBx interrupt.

|                                  |                            | 7    | 6 | 5 | 4 | 3 | 2     | 1      | 0      |                                                               |

|----------------------------------|----------------------------|------|---|---|---|---|-------|--------|--------|---------------------------------------------------------------|

|                                  |                            | -    | - | - |   | - | -     |        | -      |                                                               |

| TBxEN                            | ←                          | 1    | Х | Х | Х | Х | Х     | Х      | Х      | Enables TMRBx operation.                                      |

| TBxRUN                           | ←                          | Х    | х | х | Х | Х | 0     | Х      | 0      | Stops count operation.                                        |

| Interrupt Set-Enable<br>Register | ←                          | *    | * | * | * | * | *     | *      | *      | Permits INTTBx interrupt by setting corresponding bit to "1". |

| TBxFFCR                          | ←                          | Х    | Х | 0 | 0 | 0 | 0     | 1      | 1      | Disable to TBxFF0 reverse trigger                             |

| TBxMOD                           | ←                          | Х    | 0 | 1 | 0 | 0 | 1     | *      | *      | Changes to prescaler output clock as input clock. Specifies   |

|                                  |                            |      |   |   |   |   | (** = | 01, 10 | D, 11) | Capture function to disable.                                  |

| TBxRG1                           | ←                          | *    | * | * | * | * | *     | *      | *      | Specifies a time interval. (16 bits)                          |

|                                  | ←                          | *    | * | * | * | * | *     | *      | *      |                                                               |

| TBxRUN                           | ←                          | *    | * | * | * | * | 1     | Х      | 1      | Starts TMRBx.                                                 |

| Nata Ye                          | <b>D</b> = = <sup>24</sup> |      |   |   |   |   |       |        |        |                                                               |

| Note: X; I                       | Dont                       | care | • |   |   |   |       |        |        |                                                               |

-; No change

# 9.6.2 16-bit Event Counter Mode

It is possible to make it the event counter by using an input clock as an external clock (TBxIN0 pin input).

The up-counter counts up on the rising edge of TBxIN0 pin input. It is possible to read the count value by capturing value using software and reading the captured value.

|                                                               | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |                                          |

|---------------------------------------------------------------|-----|---|---|---|---|---|---|---|------------------------------------------|

| TBxEN                                                         | ← 1 | х | Х | Х | х | Х | Х | Х | Enables TMRBx operation.                 |

| TBxRUN                                                        | ← X | Х | Х | Х | Х | 0 | Х | 0 | Stops count operation.                   |

| PxIE[m]                                                       | ←   |   |   |   |   |   |   | 1 | Allocates corresponding port toTBxIN0.   |

| PxFR1[m]                                                      | ←   |   |   |   |   |   |   | 1 | Allocates corresponding port to realino. |

| TBxFFCR                                                       | ← X | х | 0 | 0 | 0 | 0 | 1 | 1 | Disables to TBxFF0 reverse trigger       |

| TBxMOD                                                        | ← X | 0 | 1 | 0 | 0 | 0 | 0 | 0 | Changes toTBxIN0 as an input clock       |

| TBxRUN                                                        | ← * | * | * | * | * | 1 | Х | 1 | Starts TMRBx.                            |

|                                                               |     |   |   |   |   |   |   |   |                                          |

| TBxMOD                                                        | ← X | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Software capture is done.                |

| Note 1: m: corresponding bit of port<br>Note 2: X; Don't care |     |   |   |   |   |   |   |   |                                          |

-; No change

10.7 Clock Control

| peripheral clock                        | Clock gear                                  | Prescaler clock se-                           | Prescaler output clock resolution |                            |                              |                               |  |  |  |

|-----------------------------------------|---------------------------------------------|-----------------------------------------------|-----------------------------------|----------------------------|------------------------------|-------------------------------|--|--|--|

| selection<br>CGSYSCR<br><fpsel></fpsel> | value<br>CGSYSCR<br><gear[2:0]></gear[2:0]> | lection<br>CGSYSCR<br><prck[2:0]></prck[2:0]> | φΤ1                               | φT4                        | φΤ16                         | φΤ64                          |  |  |  |

|                                         |                                             | 000 (fperiph/1)                               | fc/2¹ (0.05 μs)                   | fc/23 (0.2 µs)             | fc/2⁵ (0.8 µs)               | fc/2 <sup>7</sup> (3.2 µs)    |  |  |  |

|                                         |                                             | 001 (fperiph/2)                               | fc/2² (0.1 µs)                    | fc/24 (0.4 µs)             | fc/2 <sup>6</sup> (1.6 µs)   | fc/2 <sup>8</sup> (6.4 µs)    |  |  |  |

|                                         | 000 (5.)                                    | 010 (fperiph/4)                               | fc/2³ (0.2 µs)                    | fc/2⁵ (0.8 µs)             | fc/2 <sup>7</sup> (3.2 µs)   | fc/2 <sup>9</sup> (12.8 µs)   |  |  |  |

|                                         | 000 (fc)                                    | 011 (fperiph/8)                               | fc/2 <sup>4</sup> (0.4 µs)        | fc/2 <sup>6</sup> (1.6 µs) | fc/2 <sup>8</sup> (6.4 µs)   | fc/2 <sup>10</sup> (25.6 µs)  |  |  |  |

|                                         |                                             | 100 (fperiph/16)                              | fc/2⁵ (0.8 µs)                    | fc/2 <sup>7</sup> (3.2 µs) | fc/2 <sup>9</sup> (12.8 µs)  | fc/2 <sup>11</sup> (51.2 μs)  |  |  |  |

|                                         |                                             | 101 (fperiph/32)                              | fc/2 <sup>6</sup> (1.6 µs)        | fc/2 <sup>8</sup> (6.4 µs) | fc/2 <sup>10</sup> (25.6 µs) | fc/2 <sup>12</sup> (102.4 µs) |  |  |  |

|                                         |                                             | 000 (fperiph/1)                               | -                                 | fc/2³ (0.2 µs)             | fc/2⁵ (0.8 µs)               | fc/2 <sup>7</sup> (3.2 µs)    |  |  |  |

|                                         |                                             | 001 (fperiph/2)                               | fc/2² (0.1 µs)                    | fc/24 (0.4 µs)             | fc/2 <sup>6</sup> (1.6 µs)   | fc/2 <sup>8</sup> (6.4 µs)    |  |  |  |

|                                         | 100 (fc/2)                                  | 010 (fperiph/4)                               | fc/2 <sup>3</sup> (0.2 µs)        | fc/2⁵ (0.8 µs)             | fc/2 <sup>7</sup> (3.2 µs)   | fc/2 <sup>9</sup> (12.8 μs)   |  |  |  |

|                                         |                                             | 011 (fperiph/8)                               | fc/2 <sup>4</sup> (0.4 µs)        | fc/2 <sup>6</sup> (1.6 µs) | fc/2 <sup>8</sup> (6.4 µs)   | fc/2 <sup>10</sup> (25.6 µs)  |  |  |  |

|                                         |                                             | 100 (fperiph/16)                              | fc/2⁵ (0.8 µs)                    | fc/2 <sup>7</sup> (3.2 µs) | fc/2º (12.8 µs)              | fc/2 <sup>11</sup> (51.2 μs)  |  |  |  |

|                                         |                                             | 101 (fperiph/32)                              | fc/2 <sup>6</sup> (1.6 µs)        | fc/2 <sup>8</sup> (6.4 µs) | fc/2 <sup>10</sup> (25.6 µs) | fc/2 <sup>12</sup> (102.4 µs) |  |  |  |

| 1 (fc)                                  | 101 (fc/4)                                  | 000 (fperiph/1)                               | -                                 | fc/2³ (0.2 µs)             | fc/2⁵ (0.8 µs)               | fc/2 <sup>7</sup> (3.2 µs)    |  |  |  |

|                                         |                                             | 001 (fperiph/2)                               | -                                 | fc/2 <sup>4</sup> (0.4 µs) | fc/2 <sup>6</sup> (1.6 µs)   | fc/2 <sup>8</sup> (6.4 µs)    |  |  |  |

|                                         |                                             | 010 (fperiph/4)                               | fc/2³ (0.2 µs)                    | fc/2⁵ (0.8 µs)             | fc/2 <sup>7</sup> (3.2 µs)   | fc/2 <sup>9</sup> (12.8 µs)   |  |  |  |

|                                         |                                             | 011 (fperiph/8)                               | fc/24 (0.4 µs)                    | fc/2 <sup>6</sup> (1.6 µs) | fc/2 <sup>8</sup> (6.4 µs)   | fc/2 <sup>10</sup> (25.6 µs)  |  |  |  |

|                                         |                                             | 100 (fperiph/16)                              | fc/2⁵ (0.8 µs)                    | fc/2 <sup>7</sup> (3.2 µs) | fc/2 <sup>9</sup> (12.8 µs)  | fc/2 <sup>11</sup> (51.2 µs)  |  |  |  |

|                                         |                                             | 101 (fperiph/32)                              | fc/2 <sup>6</sup> (1.6 µs)        | fc/2 <sup>8</sup> (6.4 µs) | fc/2 <sup>10</sup> (25.6 µs) | fc/2 <sup>12</sup> (102.4 µs) |  |  |  |

|                                         |                                             | 000 (fperiph/1)                               | -                                 | -                          | fc/2 <sup>5</sup> (0.8 µs)   | fc/2 <sup>7</sup> (3.2 µs)    |  |  |  |

|                                         |                                             | 001 (fperiph/2)                               | -                                 | fc/24 (0.4 µs)             | fc/2 <sup>6</sup> (1.6 µs)   | fc/2 <sup>8</sup> (6.4 µs)    |  |  |  |

|                                         | 110 (5-10)                                  | 010 (fperiph/4)                               | -                                 | fc/2 <sup>5</sup> (0.8 µs) | fc/27 (3.2 µs)               | fc/2 <sup>9</sup> (12.8 μs)   |  |  |  |

|                                         | 110 (fc/8)                                  | 011 (fperiph/8)                               | fc/2 <sup>4</sup> (0.4 µs)        | fc/2 <sup>6</sup> (1.6 µs) | fc/28 (6.4 µs)               | fc/2 <sup>10</sup> (25.6 µs)  |  |  |  |

|                                         |                                             | 100 (fperiph/16)                              | fc/2 <sup>5</sup> (0.8 µs)        | fc/27 (3.2 µs)             | fc/2 <sup>9</sup> (12.8 µs)  | fc/2 <sup>11</sup> (51.2 μs)  |  |  |  |

|                                         |                                             | 101 (fperiph/32)                              | fc/2 <sup>6</sup> (1.6 μs)        | fc/2 <sup>8</sup> (6.4 µs) | fc/2 <sup>10</sup> (25.6 µs) | fc/2 <sup>12</sup> (102.4 µs) |  |  |  |

#### Table 10-4 Clock Resolution to the Baud Rate Generator fc = 40 MHz

Note 1: The prescaler output clock  $\varphi$ Tn must be selected so that the relationship " $\varphi$ Tn  $\leq$  fsys / 2" is satisfied (so that  $\varphi$ Tn is slower than fsys).

Note 2: Do not change the clock gear while SIO is operating.

Note 3: The dashes in the above table indicate that the setting is prohibited.

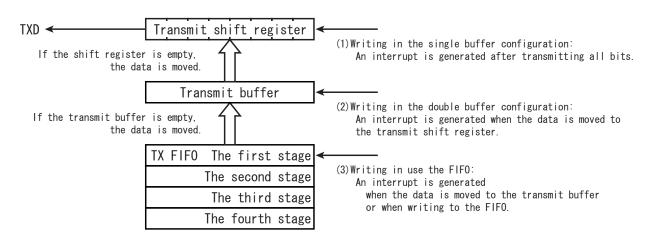

# 10.14.2 TX interrupts

Figure 10-11 shows the data flow of transmit operation and the route of read.

Figure 10-11 Transmit Buffer/FIFO Configuration Diagram

#### 10.14.2.1 Single Buffer / Double Buffer

TX interrupts are generated at the time depends on the transfer mode and the buffer configurations, which are given as follows.

| Buffer<br>Configurations | UART modes                                                                    | IO interface modes                                                                                                                         |  |  |  |  |

|--------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Single Buffer            | Just before the stop bit is sent                                              | Immediately after the raising / falling edge of the last SCLK (Rising or falling is determined according to SCxCR <sclks> setting.</sclks> |  |  |  |  |

| Double Buffer            | When a data is moved from the transmit buffet to the transmit shift register. |                                                                                                                                            |  |  |  |  |

Note: If double buffer is enabled, a interrupt is also generated when the data is moved from the buffer to the shift register by writing to the buffer.

#### 10.14.2.2 FIFO

In use of FIFO, transmit interrupt is generated on the condition that the fllowing either operation and SCxTFC<TFIS> setting are established.

- Transmittion completion of all bits of one frame.

- Writing FIFO

Interrupt conditions are decided by the SCxTFC<TFIS> settings as described in Table 10-13.

Table 10-13 Transmit Interrupt conditions in use of FIFO

| SCxTFC <tfis></tfis> | Interrupt conditions                                                                                  |

|----------------------|-------------------------------------------------------------------------------------------------------|

| "0"                  | "The fill level of FIFO" is equal to "the fill level of FIFO interruption generation."                |

| "1"                  | "The fill level of FIFO" is smaller than or equal to "the fill level of FIFO intrruption generation." |

# 11.5.11 Slave Address Match Detection Monitor

When the SBI operates as a slave device in the address recognition mode (SBIxI2CAR<ALS>="0"), SBIxSR<AAS> is set to "1" on receiving the general-call address or the slave address that matches the value specified at SBIxI2CAR.

When <ALS> is "1", <AAS> is set to "1" when the first data word has been received. <AAS> is cleared to "0" when data is written to or read from SBIxDBR.

## 11.5.12 General-call Detection Monitor

When the SBI operates as a slave device, SBIxSR<AD0> is set to "1" when it receives the general-call address; i.e., the eight bits following the start condition are all zeros.

<AD0> is cleared to "0" when the start or stop condition is detected on the bus.

## 11.5.13 Last Received Bit Monitor

SBIxSR<LRB> is set to the SDA line value that was read at the rising of the SCL line.

In the acknowledgment mode, reading SBIxSR<LRB> immediately after generation of the INTSBIx interrupt request causes ACK signal to be read.

# 11.5.14 Data Buffer Register (SBIxDBR)

Reading or writing SBIxDBR initiates reading received data or writing transmitted data.

When the SBI is acting as a master, setting a slave address and a direction bit to this register generates the start condition.

## 11.5.15 Baud Rate Register (SBIxBR0)

The SBIxBR0<I2SBI> register determines if the SBI operates or not when it enters the IDLE mode.

This register must be programmed before executing an instruction to switch to the standby mode.

## 11.5.16 Software Reset

If the serial bus interface circuit locks up due to external noise, it can be initialized by using a software reset.

Writing "10" followed by "01" to SBIxCR2<SWRST[1:0]> generates a reset signal that initializes the serial bus interface circuit. After a reset, all control registers and status flags are initialized to their reset values. When the serial bus interface is initialized, <SWRST> is automatically cleared to "0".

Note: A software reset causes the SBI operating mode to switch from the I2C mode to the port mode.

# 12.2 Configuration

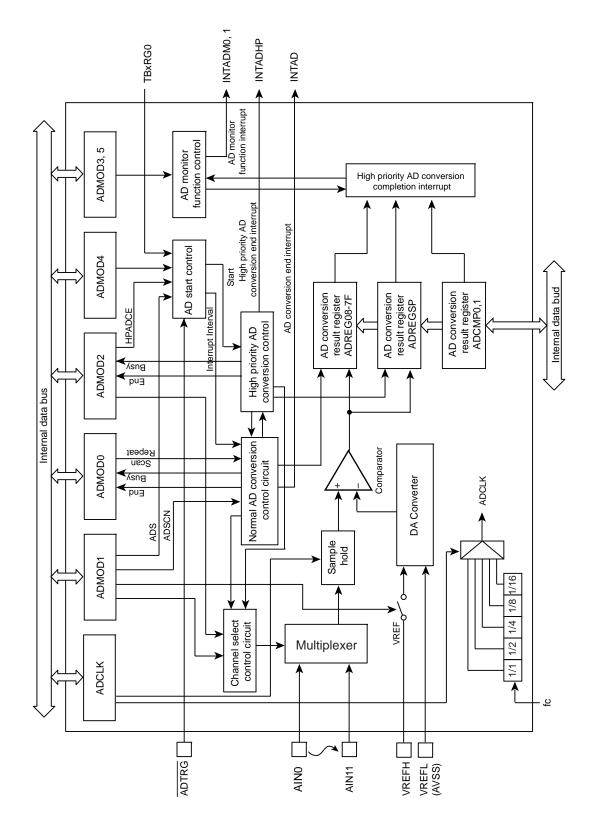

Figure 12-1 shows the block diagram of this AD converter.

Figure 12-1 AD Converter Block Diagram

|             | 31 | 30 | 29      | 28 | 27      | 26 | 25 | 24 |  |  |

|-------------|----|----|---------|----|---------|----|----|----|--|--|

| Bit symbol  | -  | -  | -       | -  | -       | -  | -  | -  |  |  |

| After reset | 0  | 0  | 0       | 0  | 0       | 0  | 0  | 0  |  |  |

|             | 23 | 22 | 21      | 20 | 19      | 18 | 17 | 16 |  |  |

| Bit symbol  | -  | -  | -       | -  | -       | -  | -  | -  |  |  |

| After reset | 0  | 0  | 0       | 0  | 0       | 0  | 0  | 0  |  |  |

|             | 15 | 14 | 13      | 12 | 11      | 10 | 9  | 8  |  |  |

| Bit symbol  | -  | -  | -       | -  | -       | -  | -  | -  |  |  |

| After reset | 0  | 0  | 0       | 0  | 0       | 0  | 0  | 0  |  |  |

|             | 7  | 6  | 5       | 4  | 3       | 2  | 1  | 0  |  |  |

| Bit symbol  | -  | -  | ADOBIC0 |    | ADREGS0 |    |    |    |  |  |

| After reset | 0  | 0  | 0       | 0  | 0       | 0  | 0  | 0  |  |  |

# 12.3.8 ADMOD3 (Mode Control Register 3)

| Bit  | Bit Symbol   | Туре | Function                                                                                                                                                                                                                                                                   |

|------|--------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-8 | -            | R    | Read as 0.                                                                                                                                                                                                                                                                 |

| 7    | -            | R/W  | Write "0".                                                                                                                                                                                                                                                                 |

| 6    | -            | R    | Read as 0.                                                                                                                                                                                                                                                                 |

| 5    | ADOBIC0      | R/W  | Set the AD monitor function interrupt 0<br>0: If the value of the conversion result is smaller than the comparison register 0, an interrupt is generated.<br>1: If the value of the conversion result is bigger than the comparison register 0, an interrupt is generated. |

| 4-1  | ADREGS0[3:0] | R/W  | Select a target conversion result register when using the AD monitor function 0 (See the below table).                                                                                                                                                                     |

| 0    | ADOBSV0      | R/W  | AD monitor function 0<br>0: Disable<br>1: Enable                                                                                                                                                                                                                           |

| <adregs0[3:0]></adregs0[3:0]> | Conversion result<br>register to be com-<br>pared | <adregs0[3:0]></adregs0[3:0]> | Conversion result<br>register to be com-<br>pared |

|-------------------------------|---------------------------------------------------|-------------------------------|---------------------------------------------------|

| 0000                          | ADREG08                                           | 0100                          | ADREG4C                                           |

| 0001                          | ADREG19                                           | 0101                          | ADREG5D                                           |

| 0010                          | ADREG2A                                           | 0110                          | ADREG6E                                           |

| 0011                          | ADREG3B                                           | 0111                          | ADREG7F                                           |

| -                             | -                                                 | 1xxx                          | ADREGSP                                           |

# 13.3 Operations

## 13.3.1 Basic Operation

The Watchdog timer is consists of the binary counters that work using the system clock (fsys) as an input. Detecting time can be selected between  $2^{15}$ ,  $2^{17}$ ,  $2^{19}$ ,  $2^{21}$ ,  $2^{23}$  and  $2^{25}$  by the WDMOD<WDTP[2:0]>. The detecting time as specified is elapsed, the watchdog timer interrupt (INTWDT) generates, and the watchdog timer out pin (WDTOUT) output "Low".

To detect malfunctions (runaways) of the CPU caused by noise or other disturbances, the binary counter of the watchdog timer should be cleared by software instruction before INTWDT interrupt generates. If the binary counter is not cleared, the non-maskable interrupt generates by INTWDT. Thus CPU detects malfunction (runway), malfunction countermeasure program is performed to return to the normal operation.

Additionally, it is possible to resolve the problem of a malfunction (runaway) of the CPU by connecting the watchdog timer out pin to reset pins of peripheral devices.

Note: This product does not include a watchdog timer out pin ( $\overline{WDTOUT}$ ).

# 13.3.2 Operation Mode and Status

The watchdog timer begins operation immediately after a reset is cleared.

If not using the watchdog timer, it should be disabled.

The watchdog timer cannot be used in the STOP mode, SLEEP mode and SLOW mode where high-speed frequency clock is stopped. Before transition to these modes, the watchdog timer should be disabled.

In IDLE mode, its operation depends on the WDMOD <12WDT> setting.

Also, the binary counter is automatically stopped during debug mode.

# 14.5.2 1Hz cycle "Low" pulse1 Hz

The RTC outputs a "Low" pulse cycle of low-speed 1Hz clock to the  $\overline{\text{ALARM}}$  pin by setting RTCPAG-ER<INTENA>="1" after setting RTCPAGER<ENAALM>= "0", RTCRESTR<DIS1HZ>= "0" and <DIS16HZ>= "1". It generates an INTRTC interrupt simultaneously.

# 14.5.3 16Hz cycle "Low" pulse16 Hz

The RTC outputs a "Low" pulse cycle of low-speed 16Hz clock to the ALARM pin by setting RTCPAG-ER<INTENA>="1" after setting RTCPAGER<ENAALM>= "0", RTCRESTR<DIS1HZ>= "1" and <DIS16HZ>= "0". It generates an INTRTC interrupt simultaneously.

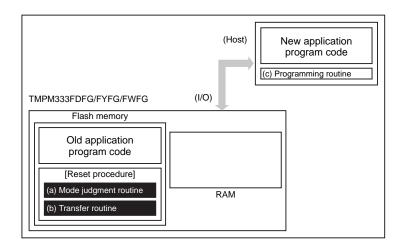

#### 15.2.2.2 (1-B) Method 2: Transferring a Programming Routine from an External Host

(1) Step-1

Determine the conditions (e.g., pin states) required for the flash memory to enter User Boot mode and the I/O bus to be used to transfer new program code. Create hardware and software accordingly. Before installing the TMPM333FDFG/FYFG/FWFG on a printed circuit board, write the following program routines into an arbitrary flash block using programming equipment.

(a) Mode judgment routine: Code to determine whether or not to switch to User Boot mode(b) Transfer routine: Code to download new program code from a host controller

Also, prepare a programming routine shown below on the host controller:

(c) Programming routine: Code to download new program code from an external host controller and re-program the flash memory

# 16.4 Writing and erasing

# 16.4.1 Protection bits

Writing and erasing protection bits are available with a single chip mode, single boot mode and writer mode.

Writing to the protection bits is done on block-by-block basis.

Erasing of the protection bits is done by two groups of the blocks: block 0 through 3 and block 4 through 5. When the settings for all the blocks are "1", erasing must be done after setting the FCSECBIT <SECBIT> bit to "0". Setting "1" at that situation erases all the protection bits. To write and erase the protection bits, command sequence is used.

See the capter "Flash" for details

# 16.4.2 Security bit

The FCSECBIT <SECBIT> bit that activates security function is set to "1" at a power-on reset right after power-on.

The bit is rewritten by the following procedure.

- 1. Write the code 0xa74a9d23 to FCSECBIT register.

- 2. Write data within 16 clocks from the above.1.

Note: The above procedure is enabled only when using 32-bit data transfer command.