Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | 78K/0R                                                                                |

| Core Size                  | 16-Bit                                                                                |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, EBI/EMI, I <sup>2</sup> C, LINbus, UART/USART                             |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                               |

| Number of I/O              | 127                                                                                   |

| Program Memory Size        | 128KB (128K x 8)                                                                      |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 8K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 16x10b; D/A 2x8b                                                                  |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 144-LQFP                                                                              |

| Supplier Device Package    | -                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f1184agj-gae-ax |

|                            |                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                | I/O Circuit Type | I/O   | Recommended Connection of Unused Pins                                                                                                                                            |

|-----------------------------------------|------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P140/PCLBUZ0/INTP6                      | 8-R              | I/O   | Input: Independently connect to EVDD0, EVDD1, EVSS0, or EVSS1                                                                                                                    |

| P141/PCLBUZ1/INTP7                      |                  |       | via a resistor.                                                                                                                                                                  |

| P142/SCK20/SCL20                        | 5-AN             |       | Output: Leave open.                                                                                                                                                              |

| P143/SI20/RxD2/SDA20                    |                  |       |                                                                                                                                                                                  |

| P144/SO20/TxD2                          | 5-AG             |       |                                                                                                                                                                                  |

| P145/TI07/TO07                          | 8-R              |       |                                                                                                                                                                                  |

| P146, P147                              | 5-AG             |       |                                                                                                                                                                                  |

| P150/ANI8 to P157/ANI15 <sup>Note</sup> | 11-G             | -     | Input: Independently connect to AV <sub>REF0</sub> or AV <sub>SS</sub> via a resistor.<br>Output: Leave open.                                                                    |

| P160/TI10/TO10 to<br>P163/TI13/TO13     | 8-R              |       | Input: Independently connect to EV <sub>DD0</sub> , EV <sub>DD1</sub> , EV <sub>SS0</sub> , or EV <sub>SS1</sub><br>via a resistor.<br>Output: Leave open.                       |

| AVREFO                                  | -                | -     | Make this pin the same potential as EV <sub>DD0</sub> , EV <sub>DD1</sub> , or V <sub>DD</sub> .<br>See <b>2.2.18 AV</b> <sub>REF0</sub> when using P20 to P27 and P150 to P157. |

| AV <sub>REF1</sub>                      | -                | -     | Make this pin the same potential as EVDD0, EVDD1, or VDD.<br>See <b>2.2.19 AVREF1</b> when using P110 and P111.                                                                  |

| AVss                                    | _                | _     | Make this pin the same potential as the EVsso, EVss1, or Vss.                                                                                                                    |

| FLMD0                                   | 2-W              | -     | Leave open or connect to $V_{\text{SS}}$ via a resistor of 100 $k\Omega$ or more.                                                                                                |

| RESET                                   | 2                | Input | Connect directly or via a resistor to EVDD0 or EVDD1.                                                                                                                            |

| REGC                                    | -                | _     | Connect to Vss via capacitor (0.47 to 1 $\mu$ F).                                                                                                                                |

# Table 2-4. Connection of Unused Pins (3/3)

**Notes** P150/ANI8 to P157/ANI15 are set in the digital input port mode after release of reset.

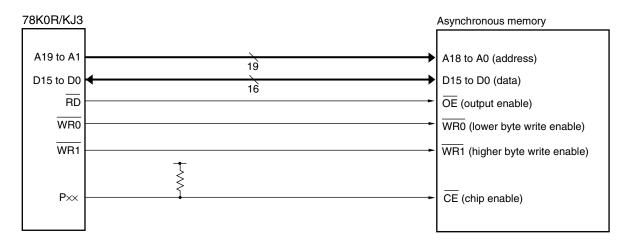

## 5.8.3 Connection of asynchronous memory

Use the separate bus mode for connecting an asynchronous memory.

| Figure 7-44. Op | peration Procedure Wher | n External Event Counter | r Function Is Used |

|-----------------|-------------------------|--------------------------|--------------------|

|-----------------|-------------------------|--------------------------|--------------------|

|                               | Software Operation                                                                                                                                                                                                         | Hardware Status                                                                                                                                                                                                                                                                                                                 |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TAU<br>default<br>setting     |                                                                                                                                                                                                                            | Power-off status<br>(Clock supply is stopped and writing to each register is<br>disabled.)                                                                                                                                                                                                                                      |

|                               | Sets the TAU0EN bit, TAU1EN bit of the PER0 register to 1                                                                                                                                                                  | <ul> <li>Power-on status. Each channel stops operating.</li> <li>(Clock supply is started and writing to each register is enabled.)</li> </ul>                                                                                                                                                                                  |

|                               | Sets the TPSm register.<br>Determines clock frequencies of CKm0 and CKm1.                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                 |

| Channel<br>default<br>setting | Sets the TMRmn register (determines operation mode of<br>channel).<br>Sets number of counts to the TDRmn register.<br>Clears the TOEmn bit of the TOEm register to 0.                                                      | Channel stops operating.<br>(Clock is supplied and some power is consumed.)                                                                                                                                                                                                                                                     |

| Operation<br>start            | Sets the TSmn bit to 1<br>The TSmn bit automatically returns to 0 because it is a<br>trigger bit.                                                                                                                          | TEmn = 1, and count operation starts.<br>Value of TDRmn is loaded to TCRmn and detection of<br>the TImn pin input edge is awaited.                                                                                                                                                                                              |

| During<br>operation           | Set value of the TDRmn register can be changed.<br>The TCRmn register can always be read.<br>The TSRmn register is not used.<br>Set values of the TMRmn register, TOMmn, TOLmn,<br>TOmn, and TOEmn bits cannot be changed. | Counter (TCRmn) counts down each time input edge of<br>the TImn pin has been detected. When count value<br>reaches 0000H, the value of TDRmn is loaded to TCRmr<br>again, and the count operation is continued. By detecting<br>TCRmn = 0000H, the INTTMmn output is generated.<br>After that, the above operation is repeated. |

| Operation<br>stop             | The TTmn bit is set to 1<br>The TTmn bit automatically returns to 0 because it is a<br>trigger bit.                                                                                                                        | TEmn = 0, and count operation stops.<br>TCRmn holds count value and stops.                                                                                                                                                                                                                                                      |

| TAU stop                      | The TAU0EN bit, TAU1EN bit of the PER0 register are cleared to 0.                                                                                                                                                          | Power-off status<br>All circuits are initialized and SFR of each channel is<br>also initialized.                                                                                                                                                                                                                                |

**Remark** m: Unit number (m = 0, 1), n: Channel number (n = 0 to 7), mn = 00 to 07, 10 to 13

Operation is resumed.

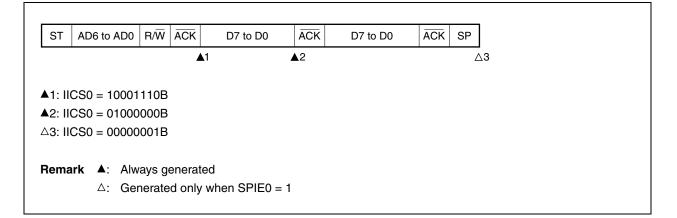

(b) When arbitration loss occurs during transmission of extension code

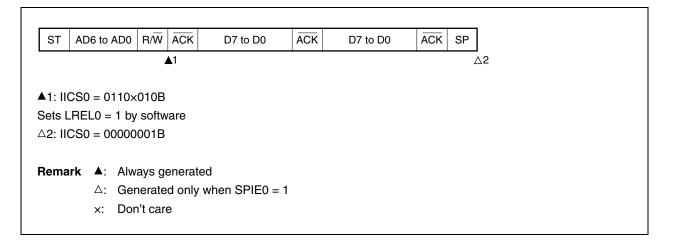

### (c) When arbitration loss occurs during transmission of data

(i) When WTIM0 = 0

| Edition     | Description                                                                                                                                                        | Chapter                        |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|

| 3rd Edition | Addition of 8.4.5 1 Hz output of real-time counter                                                                                                                 | CHAPTER 8 REAL-                |  |

|             | Addition of 8.4.6 32.768 kHz output of real-time counter                                                                                                           | TIME COUNTER<br>(continuation) |  |

|             | Addition of 8.4.7 512 Hz, 16.384 kHz output of real-time counter                                                                                                   |                                |  |

|             | Addition of 8.4.8 Example of watch error correction of real-time counter                                                                                           |                                |  |

|             | Change of Caution 3 in Table 9-4 Setting Window Open Period of Watchdog<br>Timer                                                                                   | CHAPTER 9<br>WATCHDOG TIMER    |  |

|             | Change of description in 11.2 (9) AVREF0 pin                                                                                                                       | CHAPTER 11 A/D                 |  |

|             | Change of Table 11-3 A/D Conversion Time Selection                                                                                                                 | CONVERTER                      |  |

|             | Change of Figure 11-6. A/D Converter Sampling and A/D Conversion Timing                                                                                            |                                |  |

|             | Addition of Caution 3 to Figure 11-10 Format of A/D Port Configuration Register (ADPC)                                                                             |                                |  |

|             | Addition of 11.5 Temperature Sensor Function                                                                                                                       |                                |  |

|             | Addition of 11.7 (2) Reducing current when A/D converter is stopped                                                                                                |                                |  |

|             | Addition of 12.2 (1) AVREF1 pin                                                                                                                                    | CHAPTER 12 D/A                 |  |

|             | Addition of 12.3 (4) Port mode register 11 (PM11)                                                                                                                  | CONVERTER                      |  |

|             | Change of description in 12.4.1 Operation in normal mode                                                                                                           | -                              |  |

|             | Change of description in 12.4.2 Operation in real-time output mode                                                                                                 |                                |  |

|             | Addition of Note to 13.1.3 Simplified I <sup>2</sup> C (IIC10, IIC11, IIC20 IIC21)                                                                                 | CHAPTER 13 SERIAL              |  |

|             | Change of Note 2 in Figure 13-5 Format of Serial Clock Select Register m (SPSm)                                                                                    | ARRAY UNIT                     |  |

|             | Change of Figure 13-7 Format of Serial Communication Operation Setting<br>Register mn (SCRmn)                                                                      |                                |  |

|             | Change of Figure 13-26 Procedure for Stopping Master Transmission                                                                                                  |                                |  |

|             | Change of Figure 13-28 Timing Chart of Master Transmission (in Single-<br>Transmission Mode) (Type 1: DAPmn = 0, CKPmn = 0)                                        |                                |  |

|             | Change of Figure 13-30 Timing Chart of Master Transmission (in Continuous Transmission Mode) (Type 1: DAPmn = 0, CKPmn = 0)                                        |                                |  |

|             | Modification of Figure 13-36 Timing Chart of Master Reception (in Single-<br>Reception Mode) (Type 1: DAPmn = 0, CKPmn = 0)                                        |                                |  |

|             | Change of Figure 13-40 Procedure for Stopping Master Transmission/Reception                                                                                        |                                |  |

|             | Change of Figure 13-41 Procedure for Resuming Master<br>Transmission/Reception                                                                                     |                                |  |

|             | Modification of <b>Figure 13-42 Timing Chart of Master Transmission/Reception (in</b><br><b>Single-Transmission/Reception Mode) (Type 1: DAPmn = 0, CKPmn = 0)</b> |                                |  |

|             | Modification of Figure 13-44 Timing Chart of Master Transmission/Reception (in Continuous Transmission/Reception Mode) (Type 1: DAPmn = 0, CKPmn = 0)              |                                |  |

|             | Change of transfer rate in 13.5.4 Slave transmission                                                                                                               |                                |  |

|             | Change of Figure 13-48 Procedure for Stopping Slave Transmission                                                                                                   |                                |  |

|             | Change of Figure 13-49 Procedure for Resuming Slave Transmission                                                                                                   |                                |  |

|             | Change of Figure 13-50 Timing Chart of Slave Transmission (in Single-<br>Transmission Mode) (Type 1: DAPmn = 0, CKPmn = 0)                                         |                                |  |

|             | Change of Figure 13-52 Timing Chart of Slave Transmission (in Continuous Transmission Mode) (Type 1: DAPmn = 0, CKPmn = 0)                                         |                                |  |