Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | 78K/0R                                                                                |

| Core Size                  | 16-Bit                                                                                |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, EBI/EMI, I <sup>2</sup> C, LINbus, UART/USART                             |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                               |

| Number of I/O              | 127                                                                                   |

| Program Memory Size        | 192KB (192K x 8)                                                                      |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 10K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 16x10b; D/A 2x8b                                                                  |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 144-LQFP                                                                              |

| Supplier Device Package    | ·                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f1185agj-gae-ax |

|                            |                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 9.3 Register Controlling Watchdog Timer                             |     |

|---------------------------------------------------------------------|-----|

| 9.4 Operation of Watchdog Timer                                     |     |

| 9.4.1 Controlling operation of watchdog timer                       |     |

| 9.4.2 Setting overflow time of watchdog timer                       |     |

| 9.4.3 Setting window open period of watchdog timer                  |     |

| 9.4.4 Setting watchdog timer interval interrupt                     |     |

| CHAPTER 10 CLOCK OUTPUT/BUZZER OUTPUT CONTROLLER                    |     |

| 10.1 Functions of Clock Output/Buzzer Output Controller             |     |

| 10.2 Configuration of Clock Output/Buzzer Output Controller         |     |

| 10.3 Registers Controlling Clock Output/Buzzer Output Controller    |     |

| 10.4 Operations of Clock Output/Buzzer Output Controller            |     |

| 10.4.1 Operation as output pin                                      |     |

| CHAPTER 11 A/D CONVERTER                                            |     |

| 11.1 Function of A/D Converter                                      |     |

| 11.2 Configuration of A/D Converter                                 |     |

| 11.3 Registers Used in A/D Converter                                |     |

| 11.4 A/D Converter Operations                                       |     |

| 11.4.1 Basic operations of A/D converter                            |     |

| 11.4.2 Input voltage and conversion results                         |     |

| 11.4.3 A/D converter operation mode                                 |     |

| 11.5 Temperature Sensor Function                                    |     |

| 11.5.1 Configuration of temperature sensor                          |     |

| 11.5.2 Registers used by temperature sensors                        |     |

| 11.5.3 Temperature sensor operation                                 |     |

| 11.5.4 Procedures for using temperature sensors                     |     |

| 11.6 How to Read A/D Converter Characteristics Table                |     |

|                                                                     |     |

| CHAPTER 12 D/A CONVERTER                                            | 400 |

| 12.1 Function of D/A Converter                                      | 400 |

| 12.2 Configuration of D/A Converter                                 | 400 |

| 12.3 Registers Used in D/A Converter                                | 402 |

| 12.4 Operation of D/A Converter                                     | 405 |

| 12.4.1 Operation in normal mode                                     | 405 |

| 12.4.2 Operation in real-time output mode                           |     |

| 12.4.3 Cautions                                                     | 407 |

| CHAPTER 13 SERIAL ARRAY UNIT                                        | 408 |

| 13.1 Functions of Serial Array Unit                                 |     |

| 13.1.1 3-wire serial I/O (CSI00, CSI01, CSI10, CSI11, CSI20, CSI21) |     |

| 13.1.2 UART (UART0, UART1, UART2, UART3)                            |     |

| 13.1.3 Simplified I <sup>2</sup> C (IIC10, IIC11, IIC20, IIC21)     |     |

| 13.2 Configuration of Serial Array Unit                             |     |

| 13.3 Registers Controlling Serial Array Unit                        |     |

| 13.4 Operation stop mode                                            |     |

|                                                                     |     |

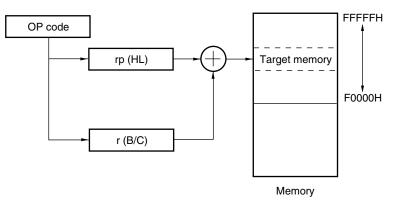

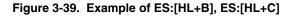

#### 3.4.8 Based indexed addressing

# [Function]

Based indexed addressing uses the contents of a register pair specified with the instruction word as the base address, and the content of the B register or C register similarly specified with the instruction word as offset address. The sum of these values is used to specify the target address.

# [Operand format]

| Identifier                                                                               | ntifier Description                                                            |  |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| <ul> <li>[HL+B], [HL+C] (only the space from F0000H to FFFFFH is specifiable)</li> </ul> |                                                                                |  |  |  |  |  |  |  |  |

| -                                                                                        | ES:[HL+B], ES:[HL+C] (higher 4-bit addresses are specified by the ES register) |  |  |  |  |  |  |  |  |

Figure 3-38. Example of [HL+B], [HL+C]

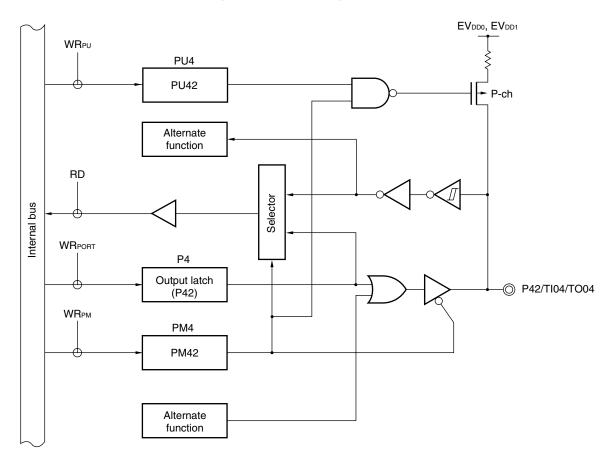

Figure 4-19. Block Diagram of P42

- P4: Port register 4

- PU4: Pull-up resistor option register 4

- PM4: Port mode register 4

- RD: Read signal

- WR××: Write signal

#### (4) Port input mode registers (PIM0, PIM4, PIM9, PIM12, PIM14)

These registers set the input buffer of P03, P04, P43, P44, P95, P96, P125, P126, P142, and P143 in 1-bit units. TTL input buffer can be selected during serial communication with an external device of the different potential. These registers can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation clears these registers to 00H.

| Symbol | 7     | 6         | 5           | 4     | 3      | 2            | 1           | 0         | Address | After reset | R/W |  |

|--------|-------|-----------|-------------|-------|--------|--------------|-------------|-----------|---------|-------------|-----|--|

| PIM0   | 0     | 0         | 0           | PIM04 | PIM03  | 0            | 0           | 0         | F0040H  | 00H         | R/W |  |

|        | -     |           |             |       |        |              |             |           |         |             |     |  |

| PIM4   | 0     | 0         | 0           | PIM44 | PIM43  | 0            | 0           | 0         | F0044H  | 00H         | R/W |  |

|        | -     |           |             |       |        |              |             |           |         |             |     |  |

| PIM9   | 0     | PIM96     | PIM95       | 0     | 0      | 0            | 0           | 0         | F0049H  | 00H         | R/W |  |

|        |       |           |             |       |        |              |             |           |         |             |     |  |

| PIM12  | 0     | PIM126    | PIM125      | 0     | 0      | 0            | 0           | 0         | F004CH  | 00H         | R/W |  |

|        | -     |           |             |       |        |              |             |           |         |             |     |  |

| PIM14  | 0     | 0         | 0           | 0     | PIM143 | PIM142       | 0           | 0         | F004EH  | 00H         | R/W |  |

|        |       |           |             |       |        |              |             |           |         |             |     |  |

|        | PIMmn |           |             |       | F      | mn pin inp   | ut buffer s | election  |         |             |     |  |

|        |       |           |             |       | (r     | n = 0, 4, 9, | 12, 14; n   | = 2 to 6) |         |             |     |  |

|        | 0     | Normal in | nput buffer |       |        |              |             |           |         |             |     |  |

|        | 1     | TTL inpu  | t buffer    |       |        |              |             |           |         |             |     |  |

#### Figure 4-56. Format of Port Input Mode Register

#### 4.4.4 Connecting to external device with different power potential (2.5 V, 3 V)

When parts of ports 0, 4, 9, 12 and 14 operate with  $V_{DD} = 4.0$  V to 5.5 V, I/O connections with an external device that operates on 2.5 V or 3 V power supply voltage are possible.

Regarding inputs, CMOS/TTL switching is possible on a bit-by-bit basis by port input mode registers (PIM0, PIM4, PIM9, PIM12, PIM14).

Moreover, regarding outputs, different power potentials can be supported by switching the output buffer to the N-ch open drain (V<sub>DD</sub> withstand voltage) by the port output mode registers (POM0, POM4, POM9, POM12, POM14).

#### (1) Setting procedure when using I/O pins of UART1, UART2, CSI01, CSI10, CSI11, CSI20 and CSI21 functions

#### (a) Use as 2.5 V or 3 V input port

- <1> After reset release, the port mode is the input mode (Hi-Z).

- <2> If pull-up is needed, externally pull up the pin to be used (on-chip pull-up resistor cannot be used).

| In case of UART1: | P03        |

|-------------------|------------|

| In case of UART2: | P143       |

| In case of CSI01: | P43, P44   |

| In case of CSI10: | P03, P04   |

| In case of CSI11: | P95, P96   |

| In case of CSI20: | P142, P143 |

| In case of CSI21: | P125, P126 |

- <3> Set the corresponding bit of the PIMn register to 1 to switch to the TTL input buffer.

- <4>  $V_{IH}/V_{IL}$  operates on 2.5 V or 3 V operating voltage.

#### (b) Use as 2.5 V or 3 V output port

- <1> After reset release, the port mode changes to the input mode (Hi-Z).

- <2> Pull up externally the pin to be used (on-chip pull-up resistor cannot be used).

| In case of UART1: | P02        |

|-------------------|------------|

| In case of UART2: | P144       |

| In case of CSI01: | P43, P45   |

| In case of CSI10: | P02, P04   |

| In case of CSI11: | P95, P97   |

| In case of CSI20: | P142, P144 |

| In case of CSI21: | P125, P127 |

- <3> Set the output latch of the corresponding port to 1.

- <4> Set the corresponding bit of the POMn register to 1 to set the N-ch open drain output (VDD withstand voltage) mode.

- <5> Set the output mode by manipulating the PMn register.

- At this time, the output data is high level, so the pin is in the Hi-Z state.

- <6> Operation is done only in the low level according to the operating status of the serial array unit.

**Remark** n = 0, 4, 9, 12, 14

#### (1) Peripheral enable register 0 (PER0)

PER0 is used to enable or disable use of each peripheral hardware macro. Clock supply to a hardware macro that is not used is stopped in order to reduce the power consumption and noise. When the timer array unit 0 is used, be sure to set bit 0 (TAU0EN) of this register to 1. When the timer array unit 1 is used, be sure to set bit 1 (TAU1EN) of this register to 1. PER0 can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation clears this register to 00H.

#### Figure 7-5. Format of Peripheral Enable Register 0 (PER0)

| Address: F00 | F0H After rea | set: 00H R/V | V     |               |        |        |        |        |

|--------------|---------------|--------------|-------|---------------|--------|--------|--------|--------|

| Symbol       | <7>           | <6>          | <5>   | <4>           | <3>    | <2>    | <1>    | <0>    |

| PER0         | RTCEN         | DACEN        | ADCEN | <b>IIC0EN</b> | SAU1EN | SAU0EN | TAU1EN | TAU0EN |

| TAUmEN | Control of timer array unit m input clock                                                                                                                           |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | <ul><li>Stops supply of input clock.</li><li>SFR used by the timer array unit m cannot be written.</li><li>The timer array unit m is in the reset status.</li></ul> |

| 1      | Supplies input clock. <ul> <li>SFR used by the timer array unit m can be read/written.</li> </ul>                                                                   |

Caution When setting the timer array unit, be sure to set TAUMEN to 1 first. If TAUMEN = 0, writing to a control register of the timer array unit is ignored, and all read values are default values (except for timer input select register m (TISm), input switch control register (ISC), noise filter enable registers 1, 2 (NFEN1, 2), port mode registers 0, 1, 3, 4, 13, 14, 16 (PM0, PM1, PM3, PM4, PM13, PM14, PM16), and port registers 0, 1, 3, 4, 13, 14, 16 (P0, P1, P3, P4, P13, P14, P16)).

#### Remark m = 0, 1

#### (2) Timer clock select register m (TPSm)

TPSm is a 16-bit register that is used to select two types of operation clocks (CKm0, CKm1) that are commonly supplied to each channel. CKm1 is selected by bits 7 to 4 of TPSm, and CKm0 is selected by bits 3 to 0. Rewriting of TPSm during timer operation is possible only in the following cases.

| Rewriting of PRSm00 to PRSm03 bits: | Possible only when all the channels set to $CKSmn = 0$ are in the                                  |

|-------------------------------------|----------------------------------------------------------------------------------------------------|

|                                     | operation stopped state (TEmn = 0)                                                                 |

| Rewriting of PRSm10 to PRSm13 bits: | Possible only when all the channels set to CKSmn = 1 are in the operation stopped state (TEmn = 0) |

TPSm can be set by a 16-bit memory manipulation instruction. The lower 8 bits of TPSm can be set with an 8-bit memory manipulation instruction with TPSmL. Reset signal generation clears this register to 0000H.

### (9) Timer output enable register m (TOEm)

TOEm is used to enable or disable timer output of each channel.

Channel n for which timer output has been enabled becomes unable to rewrite the value of the TOmn bit of the timer output register (TOm) described later by software, and the value reflecting the setting of the timer output function through the count operation is output from the timer output pin (TOmn).

TOEm can be set by a 16-bit memory manipulation instruction.

The lower 8 bits of TOEm can be set with a 1-bit or 8-bit memory manipulation instruction with TOEmL. Reset signal generation clears this register to 0000H.

#### Figure 7-18. Format of Timer Output Enable Register m (TOEm)

| Address: F01 | BAH, F | 01BBH | After | reset: ( | 0000H | R/W |   |   |           |           |           |           |           |           |           |           |

|--------------|--------|-------|-------|----------|-------|-----|---|---|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Symbol       | 15     | 14    | 13    | 12       | 11    | 10  | 9 | 8 | 7         | 6         | 5         | 4         | 3         | 2         | 1         | 0         |

| TOE0         | 0      | 0     | 0     | 0        | 0     | 0   | 0 | 0 | TOE<br>07 | TOE<br>06 | TOE<br>05 | TOE<br>04 | TOE<br>03 | TOE<br>02 | TOE<br>01 | TOE<br>00 |

#### Address: F01E2H, F01E3H After reset: 0000H R/W

| Symbol | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

|--------|----|----|----|----|----|----|---|---|---|---|---|---|-----|-----|-----|-----|

| TOE1   | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | TOE | TOE | TOE | TOE |

|        |    |    |    |    |    |    |   |   |   |   |   |   | 13  | 12  | 11  | 10  |

| TOE<br>mn | Timer output enable/disable of channel n                                                                                                                                                                                                                                                                                           |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0         | The TOmn operation stopped by count operation (timer channel output bit).<br>Writing to the TOmn bit is enabled.<br>The TOmn pin functions as data output, and it outputs the level set to the TOmn bit.<br>The output level of the TOmn pin can be manipulated by software.                                                       |

| 1         | The TOmn operation enabled by count operation (timer channel output bit).<br>Writing to the TOmn bit is disabled (writing is ignored).<br>The TOmn pin functions as timer output, and the TOEmn is set or reset depending on the timer operation.<br>The TOmn pin outputs the square-wave or PWM depending on the timer operation. |

#### Caution Be sure to clear bits 15 to 8 of TOE0 and bits 15 to 4 of TOE1 to "0".

**Remark** m: Unit number (m = 0, 1), n: Channel number (n = 0 to 7), mn = 00 to 07, 10 to 13

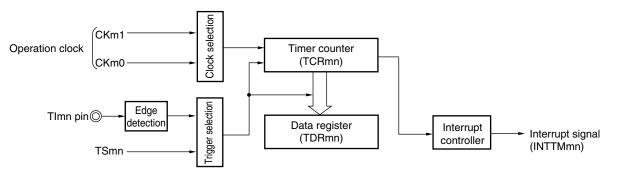

#### 7.7.4 Operation as input pulse interval measurement

The count value can be captured at the TImn valid edge and the interval of the pulse input to TImn can be measured.

The pulse interval can be calculated by the following expression.

TImn input pulse interval = Period of count clock  $\times$  ((10000H  $\times$  TSRmn: OVF) + (Capture value of TDRmn + 1))

# Caution The TImn pin input is sampled using the operating clock selected with the CKSmn bit of the TMRmn register, so an error equal to the number of operating clocks occurs.

TCRmn operates as an up counter in the capture mode.

When the channel start trigger (TSmn) is set to 1, TCRmn counts up from 0000H in synchronization with the count clock.

When the TImn pin input valid edge is detected, the count value is transferred (captured) to TDRmn and, at the same time, the counter (TCRmn) is cleared to 0000H, and the INTTMmn is output. If the counter overflows at this time, the OVF bit of the TSRmn register is set to 1. If the counter does not overflow, the OVF bit is cleared. After that, the above operation is repeated.

As soon as the count value has been captured to the TDRmn register, the OVF bit of the TSRmn register is updated depending on whether the counter overflows during the measurement period. Therefore, the overflow status of the captured value can be checked.

If the counter reaches a full count for two or more periods, it is judged to be an overflow occurrence, and the OVF bit of the TSRmn register is set to 1. However, the OVF bit is configured as a cumulative flag, the correct interval value cannot be measured if an overflow occurs more than once.

Set STSmn2 to STSmn0 of the TMRmn register to 001B to use the valid edges of TImn as a start trigger and a capture trigger.

When TEmn = 1, instead of the TImn pin input, a software operation (TSmn = 1) can be used as a capture trigger.

Figure 7-49. Block Diagram of Operation as Input Pulse Interval Measurement

**Remark** m: Unit number (m = 0, 1), n: Channel number (n = 0 to 7), mn = 00 to 07, 10 to 13

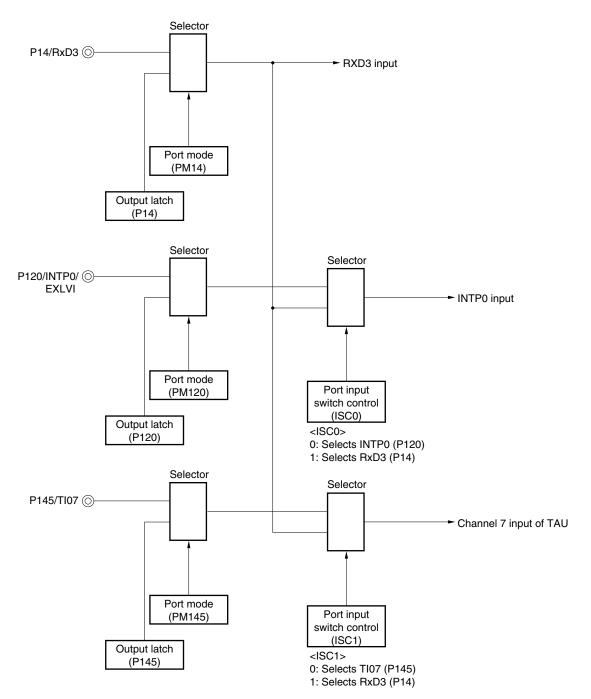

Figure 13-88 shows the configuration of a port that manipulates reception of LIN.

The wakeup signal transmitted from the master of LIN is received by detecting an edge of an external interrupt (INTP0). The length of the sync field transmitted from the master can be measured by using the external event capture operation of the timer array unit (TAU) to calculate a baud-rate error.

By controlling switch of port input (ISC0/ISC1), the input source of port input (RxD3) for reception can be input to the external interrupt pin (INTP0) and timer array unit (TAU).

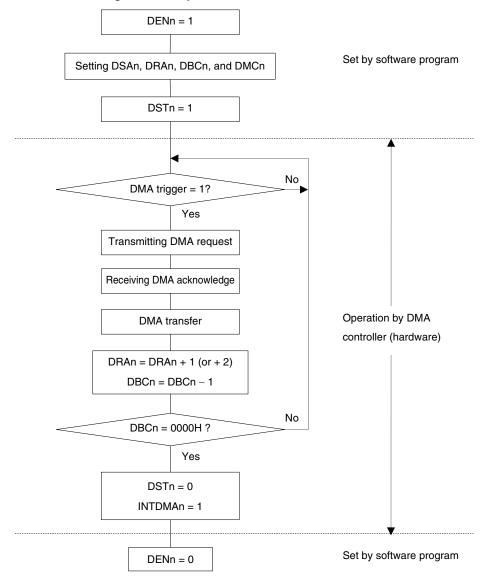

#### 16.4 Operation of DMA Controller

#### 16.4.1 Operation procedure

- <1> The DMA controller is enabled to operate when DENn = 1. Before writing the other registers, be sure to set DENn to 1. Use 80H to write with an 8-bit manipulation instruction.

- <2> Set an SFR address, a RAM address, the number of times of transfer, and a transfer mode of DMA transfer to the DSAn, DRAn, CBCn, and DMCn registers.

- <3> The DMA controller waits for a DMA trigger when DSTn = 1. Use 81H to write with an 8-bit manipulation instruction.

- <4> When a software trigger (STGn) or a start source trigger specified by IFCn3 to IFCn0 is input, a DMA transfer is started.

- <5> Transfer is completed when the number of times of transfer set by the DBCn register reaches 0, and transfer is automatically terminated by occurrence of an interrupt (INTDMAn).

- <6> Stop the operation of the DMA controller by clearing DENn to 0 when the DMA controller is not used.

Figure 16-6. Operation Procedure

**Remark** n: DMA channel number (n = 0, 1)

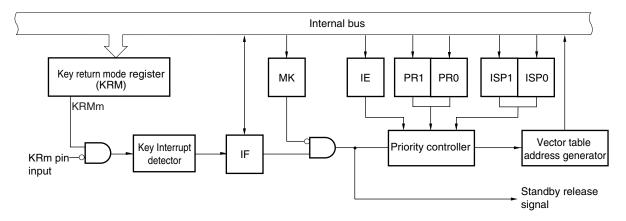

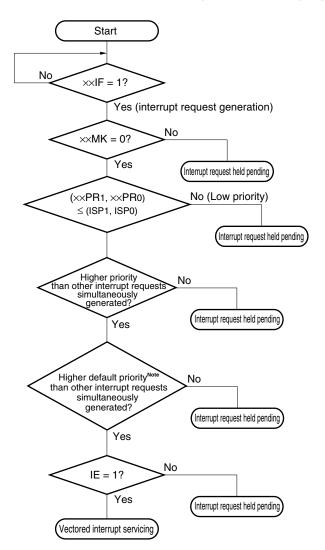

#### Figure 17-1. Basic Configuration of Interrupt Function (2/2)

# <R> (C) External maskable interrupt (INTKR)

#### (D) Software interrupt

#### Remarks 1. IF: Interrupt request flag

- IE: Interrupt enable flag

- ISP0: In-service priority flag 0

- ISP1: In-service priority flag 1

- MK: Interrupt mask flag

- PR0: Priority specification flag 0

- PR1: Priority specification flag 1

**2.** m = 0 to 7

- ××IF: Interrupt request flag

- ××MK: Interrupt mask flag

- ××PR0: Priority specification flag 0

- ××PR1: Priority specification flag 1

- IE: Flag that controls acknowledgment of maskable interrupt request (1 = Enable, 0 = Disable)

ISP0, ISP1: Flag that indicates the priority level of the interrupt currently being serviced (see Figure 17-6)

Note For the default priority, refer to Table 17-1 Interrupt Source List.

| Instruction | Mnemonic | Operands          | Bytes | Clo    | cks    | Operation                                    |   | Flag  |

|-------------|----------|-------------------|-------|--------|--------|----------------------------------------------|---|-------|

| Group       |          |                   |       | Note 1 | Note 2 |                                              | Z | AC CY |

| 8-bit data  | ХСН      | A, ES:!addr16     | 5     | 3      | -      | $A \leftarrow \rightarrow (ES, addr16)$      |   |       |

| transfer    |          | A, ES:[DE]        | 3     | 3      | _      | $A \leftarrow \rightarrow (ES, DE)$          |   |       |

|             |          | A, ES:[DE + byte] | 4     | 3      | -      | $A \leftarrow \rightarrow ((ES, DE) + byte)$ |   |       |

|             |          | A, ES:[HL]        | 3     | 3      | -      | $A \longleftrightarrow (ES, HL)$             |   |       |

|             |          | A, ES:[HL + byte] | 4     | 3      | -      | $A \leftarrow \rightarrow ((ES, HL) + byte)$ |   |       |

|             |          | A, ES:[HL + B]    | 3     | 3      | -      | $A \longleftrightarrow ((ES, HL) + B)$       |   |       |

|             |          | A, ES:[HL + C]    | 3     | 3      | -      | $A \longleftrightarrow ((ES, HL) + C)$       |   |       |

|             | ONEB     | A                 | 1     | 1      | -      | A ← 01H                                      |   |       |

|             |          | Х                 | 1     | 1      | -      | X ← 01H                                      |   |       |

|             |          | В                 | 1     | 1      | -      | B ← 01H                                      |   |       |

|             |          | С                 | 1     | 1      | -      | C ← 01H                                      |   |       |

|             |          | saddr             | 2     | 1      | -      | $(saddr) \leftarrow 01H$                     |   |       |

|             |          | !addr16           | 3     | 1      | -      | (addr16) ← 01H                               |   |       |

|             |          | ES:!addr16        | 4     | 2      | -      | (ES, addr16) ← 01H                           |   |       |

|             | CLRB     | А                 | 1     | 1      | -      | A ← 00H                                      |   |       |

|             |          | Х                 | 1     | 1      | -      | X ← 00H                                      |   |       |

|             |          | В                 | 1     | 1      | -      | B ← 00H                                      |   |       |

|             |          | С                 | 1     | 1      | -      | C ← 00H                                      |   |       |

|             |          | saddr             | 2     | 1      | -      | (saddr) ← 00H                                |   |       |

|             |          | !addr16           | 3     | 1      | -      | (addr16) ← 00H                               |   |       |

|             |          | ES:!addr16        | 4     | 2      | -      | (ES,addr16) ← 00H                            |   |       |

|             | MOVS     | [HL + byte], X    | 3     | 1      | -      | (HL + byte) ← X                              | × | ×     |

|             |          | ES:[HL + byte], X | 4     | 2      | -      | (ES, HL + byte) ← X                          | × | ×     |

| 16-bit      | MOVW     | rp, #word         | 3     | 1      | -      | $rp \leftarrow word$                         |   |       |

| data        |          | saddrp, #word     | 4     | 1      | -      | $(saddrp) \leftarrow word$                   |   |       |

| transfer    |          | sfrp, #word       | 4     | 1      | -      | $sfrp \leftarrow word$                       |   |       |

|             |          | AX, saddrp        | 2     | 1      | -      | $AX \leftarrow (saddrp)$                     |   |       |

|             |          | saddrp, AX        | 2     | 1      | -      | $(saddrp) \leftarrow AX$                     |   |       |

|             |          | AX, sfrp          | 2     | 1      | _      | $AX \leftarrow sfrp$                         |   |       |

|             |          | sfrp, AX          | 2     | 1      | -      | sfrp ← AX                                    |   |       |

|             |          | AX, rp Note 3     | 1     | 1      | _      | AX ← rp                                      |   |       |

|             |          | rp, AX Note 3     | 1     | 1      | _      | $rp \leftarrow AX$                           |   |       |

Table 28-5.

Operation List (4/17)

Notes 1. When the internal RAM area, SFR area, or extended SFR area is accessed, or for an instruction with no data access.

2. When the program memory area is accessed.

**3.** Except rp = AX

**Remarks 1.** One instruction clock cycle is one cycle of the CPU clock (fcPu) selected by the system clock control register (CKC).

**2.** This number of clocks is for when the program is in the internal ROM (flash memory) area. When fetching an instruction from the internal RAM area, the number of clocks is twice the number of clocks plus 3, maximum (except when branching to the external memory area).

3. In products where the external memory area is adjacent to the internal flash area, the number of waits is added to the number of instruction execution clocks placed in the last address (16-byte max.) in the flash memory, in order to use the external bus interface function. This should be done because, during prereading of the instruction code, an external memory wait being inserted due to an external memory area exceeding the flash space is accessed. For the number of waits, refer to 5.4 Number of Instruction Wait Clocks for Data Access.

Standard Products

| Manufacturer  | Part Number       | SMD/         | Frequency | Recommended   | Circuit Constants | Oscillation V | oltage Range |

|---------------|-------------------|--------------|-----------|---------------|-------------------|---------------|--------------|

|               |                   | Lead         | (MHz)     | C1 (pF)       | C2 (pF)           | MIN. (V)      | MAX. (V)     |

| Murata        | CSTCE12M0G55-R0   | SMD          | 12.0      | Internal (33) | Internal (33)     | 1.8           | 5.5          |

| Manufacturing | CSTCE16M0V53-R0   | SMD          | 16.0      | Internal (15) | Internal (15)     | 1.8           |              |

| Co., Ltd.     | CSTLS16M0X51-B0   | Lead         |           | Internal (5)  | Internal (5)      | 1.8           |              |

|               | CSTCE20M0V53-R0   | SMD          | 20.0      | Internal (15) | Internal (15)     | 1.9           |              |

|               | CSTCG20M0V53-R0   | Small<br>SMD |           | Internal (15) | Internal (15)     | 2.0           |              |

|               | CSTLS20M0X51-B0   | Lead         |           | Internal (5)  | Internal (5)      | 1.9           |              |

| TOKO, Inc.    | DCRHYC(P)12.00A   | Lead         | 12.0      | Internal (22) | Internal (22)     | 1.8           | 5.5          |

|               | DCRHZ(P)16.00A-15 | Lead         | 16.0      | Internal (15) | Internal (15)     |               |              |

|               | DCRHZ(P)20.00A-15 | Lead         | 20.0      | Internal (15) | Internal (15)     | 2.0           | ]            |

|               | DECRHZ20.00       | SMD          |           | Internal (10) | Internal (10)     | 1.8           |              |

#### (3) X1 oscillation: Ceramic resonator (AMPH = 1, RMC = 00H, $T_A = -40$ to +85°C)

Caution The oscillator constants shown above are reference values based on evaluation in a specific environment by the resonator manufacturer. If it is necessary to optimize the oscillator characteristics in the actual application, apply to the resonator manufacturer for evaluation on the implementation circuit.

<R>

When doing so, check the conditions for using the AMPH bit, RMC register, and whether to enter or exit the STOP mode.

The oscillation voltage and oscillation frequency only indicate the oscillator characteristic. Use the 78K0R/KJ3 so that the internal operation conditions are within the specifications of the DC and AC characteristics.

Standard Products

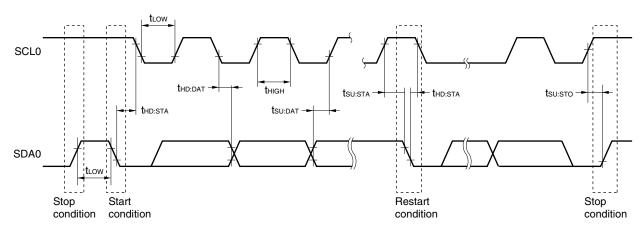

#### (4) Serial interface: IIC0

### $(T_{A} = -40 \text{ to } +85^{\circ}\text{C}, 1.8 \text{ V} \leq \text{V}_{\text{DD}} = \text{EV}_{\text{DD}} = \text{EV}_{\text{DD}} \leq 5.5 \text{ V}, \text{V}_{\text{SS}} = \text{EV}_{\text{SS}} = \text{EV}_{\text{SS}} = \text{AV}_{\text{SS}} = 0 \text{ V})$

| Parameter                                         | Symbol       | Conditions                                              | Standar | d Mode                 | Fast | Mode                   | Unit |

|---------------------------------------------------|--------------|---------------------------------------------------------|---------|------------------------|------|------------------------|------|

|                                                   |              |                                                         | MIN.    | MAX.                   | MIN. | MAX.                   |      |

| SCL0 clock frequency                              | fsc∟         | $6.7 \text{ MHz} \leq f_{CLK}$                          | 0       | 100                    | 0    | 400                    | kHz  |

|                                                   |              | $4.0 \text{ MHz} \le f_{CLK} < 6.7 \text{ MHz}$         | 0       | 100                    | 0    | 340                    | kHz  |

|                                                   |              | $3.2 \text{ MHz} \le f_{\text{CLK}} < 4.0 \text{ MHz}$  | 0       | 100                    | -    | _                      | kHz  |

|                                                   |              | $2.0 \text{ MHz} \leq f_{\text{CLK}} < 3.2 \text{ MHz}$ | 0       | 85                     | -    | -                      | kHz  |

| Setup time of restart condition <sup>Note 1</sup> | tsu:sta      |                                                         | 4.7     |                        | 0.6  |                        | μs   |

| Hold time                                         | thd:sta      |                                                         | 4.0     |                        | 0.6  |                        | μs   |

| Hold time when SCL0 = "L"                         | tLOW         |                                                         | 4.7     |                        | 1.3  |                        | μs   |

| Hold time when SCL0 = "H"                         | tніgн        |                                                         | 4.0     |                        | 0.6  |                        | μs   |

| Data setup time (reception)                       | tsu:dat      |                                                         | 250     |                        | 100  |                        | ns   |

| Data hold time (transmission) <sup>Note 2</sup>   | thd:dat      | CL00 = 1 and CL01 = 1                                   | 0       | 3.45 <sup>Note 3</sup> | 0    | 0.9 <sup>Note 4</sup>  | μs   |

|                                                   |              |                                                         |         | 5.50 <sup>Note 5</sup> |      | 1.5 Note 6             | μs   |

|                                                   |              | CL00 = 0 and CL01 = 0, or                               | 0       | 3.45                   | 0    | 0.9 <sup>Note 7</sup>  | μs   |

|                                                   |              | CL00 = 1 and CL01 = 0                                   |         |                        |      | 0.95 <sup>Note 8</sup> | μs   |

|                                                   |              | CL00 = 0 and CL01 = 1                                   | 0       | 3.45                   | 0    | 0.9                    | μs   |

| Setup time of stop condition                      | tsu:sto      |                                                         | 4.0     |                        | 0.6  |                        | μs   |

| Bus-free time                                     | <b>t</b> BUF |                                                         | 4.7     |                        | 1.3  |                        | μs   |

Notes 1. The first clock pulse is generated after this period when the start/restart condition is detected.

- 2. The maximum value (MAX.) of the during normal transfer and a wait state is inserted in the ACK (acknowledge) timing.

- 3. When 3.2 MHz  $\leq f_{CLK} \leq 4.19$  MHz.

- 4. When 6.7 MHz  $\leq$  fclk  $\leq$  8.38 MHz.

- 5. When 2.0 MHz  $\leq$  fclk < 3.2 MHz. At this time, use the SCL0 clock within 85 kHz.

- 6. When 4.0 MHz  $\leq$  f<sub>CLK</sub> < 6.7 MHz. At this time, use the SCL0 clock within 340 kHz.

- 7. When 8.0 MHz  $\leq$  folk  $\leq$  16.76 MHz.

- 8. When 7.6 MHz  $\leq$  fclk < 8.0 MHz.

Remark CL00, CL01, DFC0: Bits 0, 1, and 2 of the IIC clock select register 0 (IICCL0)

#### IIC0 serial transfer timing

# DC Characteristics (6/12) (TA = -40 to +85°C, 1.8 V $\leq$ VDD = EVDD0 = EVDD1 $\leq$ 5.5 V, 1.8 V $\leq$ AVREF0 $\leq$ VDD, 1.8 V $\leq$ AVREF1 $\leq$ VDD, VSS = EVSS0 = EVSS1 = AVSS = 0 V)

| Items                          | Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Conditio                                                                                                                                                                                                                                | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             | MIN. | TYP. | MAX.                                                                                                                                                                                                                                      | Unit     |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Input leakage<br>current, high | Цінт                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | P00 to P07, P10 to P17, P30 to<br>P37, P40 to P47, P50 to P57,<br>P60 to P67, P70 to P77, P80 to<br>P87, P90 to P97, P100 to P107,<br>P112 to P117, P120, P125 to<br>P127, P131 to P137, P140 to<br>P147, P160 to P163,<br>FLMD0, RESET | Vi = Vdd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                             |      |      | 1                                                                                                                                                                                                                                         | μA       |

|                                | Ilih2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | P20 to P27, P150 to P157                                                                                                                                                                                                                | $2.7 V \le AV$<br>VI = AVREF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | VREF0≤VDD                                   |      |      | 1     μμ       1     μμ | μA       |

|                                | Ішнз                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | P110, P111                                                                                                                                                                                                                              | 2.7 V ≤ A\                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $V_{REF1} \leq V_{DD}$                      |      |      |                                                                                                                                                                                                                                           | μA       |

|                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                             |      |      |                                                                                                                                                                                                                                           |          |

|                                | Ilih4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | P121 to P124<br>(X1, X2, XT1, XT2)                                                                                                                                                                                                      | Vi = Vdd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | In Input port<br>In resonator<br>connection |      |      |                                                                                                                                                                                                                                           | μΑ<br>μΑ |

| Input leakage<br>current, low  | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | P00 to P07, P10 to P17, P30 to<br>P37, P40 to P47, P50 to P57,<br>P60 to P67, P70 to P77, P80 to<br>P87, P90 to P97, P100 to P107,<br>P112 to P117, P120, P125 to<br>P127, P131 to P137, P140 to<br>P147, P160 to P163,                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                             |      |      | -1                                                                                                                                                                                                                                        | μA       |

|                                | $ \begin{array}{ c c c c c } \hline & \begin{array}{ c c c } \hline & 2.7 \ V \leq AV_{REF0} \leq V_{DD} \\ \hline & \hline & V_1 = AV_{REF0}, \\ \hline & AV_{REF0} = V_{DD} < 2.7 \ V \\ \hline \\ \hline \\ \hline \\ I_{LH3} \\ \hline \\ \hline \\ I_{LH4} \\ \end{array} \begin{array}{ c c } \hline & P110, P111 \\ \hline \\ & P121 \ to \ P124 \\ (X1, X2, XT1, XT2) \\ \hline \\ \hline \\ \hline \\ I_{LH4} \\ \hline \\ \hline \\ \hline \\ P121 \ to \ P124 \\ (X1, X2, XT1, XT2) \\ \hline \\ \hline \\ \hline \\ I_{I} \\ \\ I_{I} \\ I_{I} \\ I_{I} \\ \\ I_{I} \\ I_{I} \\ \\ I_{I} \\ I_{I} \\ \\ \\ I_{I} \\ \\ $ |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -1                                          | μA   |      |                                                                                                                                                                                                                                           |          |

|                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -1                                          | μA   |      |                                                                                                                                                                                                                                           |          |

|                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                         | X2, XT1, XT2)       In resonator connection       10         In resonator connection       10         to P07, P10 to P17, P30 to P57, to P67, P70 to P77, P80 to P97, P100 to P107, 2 to P117, P120, P125 to 7, P131 to P137, P140 to 7, P160 to P163, D0, RESET       -1         to P27, P150 to P157       V1 = Vss, 2.7 V ≤ AV_{REF0} ≤ V_{DD}       -1         to P27, P150 to P157       V1 = Vss, 2.7 V ≤ AV_{REF0} ≤ V_{DD}       -1         0, P111       V1 = Vss, 2.7 V ≤ AV_{REF1} ≤ V_{DD}       -1         10       V1 = Vss, 2.7 V ≤ AV_{REF1} ≤ V_{DD}       -1         10       V1 = Vss, 2.7 V ≤ AV_{REF1} ≤ V_{DD}       -1         10       V1 = Vss, 2.7 V ≤ AV_{REF1} ≤ V_{DD}       -1         110       V1 = Vss, 2.7 V       -1         110       V1 = Vss       -1         110       V1 = Vss       -1         110       V1 = Vss       -1 |                                             |      |      |                                                                                                                                                                                                                                           |          |

|                                | Ilil4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                         | $V_{I} = V_{SS}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | In Input port                               |      |      | -1                                                                                                                                                                                                                                        | μA       |

|                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | (X1, X2, XT1, XT2)                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | In resonator connection                     |      |      | -10                                                                                                                                                                                                                                       | μA       |

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of port pins.

# DC Characteristics (11/12)