Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | 78K/0R                                                                                |

| Core Size                  | 16-Bit                                                                                |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, EBI/EMI, I <sup>2</sup> C, LINbus, UART/USART                             |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                               |

| Number of I/O              | 127                                                                                   |

| Program Memory Size        | 512KB (512K x 8)                                                                      |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 30K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 16x10b; D/A 2x8b                                                                  |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 144-LQFP                                                                              |

| Supplier Device Package    | ·                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f1188agj-gae-ax |

|                            |                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

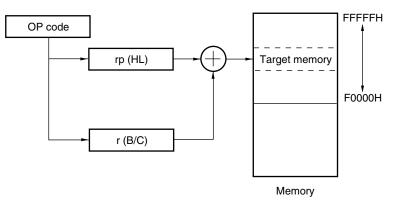

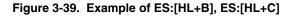

### 3.4.8 Based indexed addressing

# [Function]

Based indexed addressing uses the contents of a register pair specified with the instruction word as the base address, and the content of the B register or C register similarly specified with the instruction word as offset address. The sum of these values is used to specify the target address.

## [Operand format]

| Identifier | Description                                                                    |  |

|------------|--------------------------------------------------------------------------------|--|

| -          | [HL+B], [HL+C] (only the space from F0000H to FFFFFH is specifiable)           |  |

| -          | ES:[HL+B], ES:[HL+C] (higher 4-bit addresses are specified by the ES register) |  |

Figure 3-38. Example of [HL+B], [HL+C]

## (2) Port registers (P0 to P16)

These registers write the data that is output from the chip when data is output from a port. If the data is read in the input mode, the pin level is read. If it is read in the output mode, the output latch value is read<sup>Note</sup>.

These registers can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation clears these registers to 00H.

**Note** It is always 0 and never a pin level that is read out if a port is read during the input mode when P2 and P15 are set to function as an analog input for a A/D converter or P11 is set to function as an analog output for a D/A converter.

| (0) 10                               |                                                 |

|--------------------------------------|-------------------------------------------------|

| FFFFH                                | Special-function register (SFR)<br>256 bytes    |

| FFF00H<br>FFEFFH<br>FFEE0H<br>FFEDFH | General-purpose register<br>32 bytes            |

|                                      | RAM<br>12 KB                                    |

| FCF00H<br>FCEFFH                     | Mirror 1<br>47.75 KB 1                          |

| F1000H<br>F0FFFH                     | Reserved                                        |

| F0800H<br>F07FFH                     |                                                 |

|                                      | Special-function register (2nd SFR)<br>2 KB     |

| F0000H<br>EFFFFH                     | Reserved                                        |

| EE000H<br>EDFFFH                     |                                                 |

| ((                                   | Full-address mode<br>(when MM1, MM0 = 11)       |

| 50000H<br>4FFFFH                     | 64 KB extension mode<br>(when MM1, MM0 = 10)    |

| 41000H<br>40FFFH                     | 4 KB extension mode<br>(when MM1, MM0 = 01)     |

| 40100H<br>400FFH<br>40000H           | 256-byte extension mode<br>(when MM1, MM0 = 00) |

| 3FFFFH                               | Flash memory<br>256 KB                          |

| 00000H                               |                                                 |

(c) Memory map of μPD78F1186A

## Figure 5-1. Memory Map When Using External Bus Interface Function (2/3)

## (d) Memory map of μPD78F1187A

| FFFFH                                | Special-function register (SFR)<br>256 bytes                                                   |

|--------------------------------------|------------------------------------------------------------------------------------------------|

| FFF00H<br>FFEFFH<br>FFEE0H<br>FFEDFH | General-purpose register<br>32 bytes                                                           |

| Fredra                               | RAM<br>24 KB                                                                                   |

| F9F00H<br>F9EFFH                     | Mirror 1<br>35.75 KB                                                                           |

| F1000H<br>F0FFH<br>F0800H<br>F07FFH  | Reserved                                                                                       |

|                                      | Special-function register (2nd SFR)<br>2 KB                                                    |

| F0000H<br>EFFFFH                     | Reserved $\sim$                                                                                |

| EE000H<br>EDFFFH                     | Full-address mode                                                                              |

| 70000H<br>6FFFH                      | (when MM1, MM0 = 11) $64  KB extension mode$ $(when MM1, MM0 = 10)$                            |

| 61000H<br>60FFFH<br>60100H<br>600FFH | 4 KB extension mode<br>(when MM1, MM0 = 01)<br>256-byte extension mode<br>(when MM1, MM0 = 00) |

| 60000H<br>5FFFH                      | (when MM1, MM0 = 00)<br>Flash memory<br>384 KB                                                 |

| 00000H                               |                                                                                                |

### (7) Operation speed mode control register (OSMC)

This register is used to control the step-up circuit of the flash memory for high-speed operation.

If the microcontroller operates at a low speed with a system clock of 10 MHz or less, the power consumption can be lowered by setting this register to the default value, 00H.

OSMC can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

### Figure 6-8. Format of Operation Speed Mode Control Register (OSMC)

Address: F00F3H After reset: 00H R/W

| Symbol | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0    |

|--------|---|---|---|---|---|---|---|------|

| OSMC   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | FSEL |

| FSEL | fclk frequency selection                             |

|------|------------------------------------------------------|

| 0    | Operates at a frequency of 10 MHz or less (default). |

| 1    | Operates at a frequency higher than 10 MHz.          |

Cautions 1. OSMC can be written only once after reset release, by an 8-bit memory manipulation instruction.

- 2. Write "1" to FSEL before the following two operations.

- Changing the clock prior to dividing fcLK to a clock other than fill.

- Operating the DMA controller.

- 3. The CPU waits when "1" is written to the FSEL flag.

Interrupt requests issued during a wait will be suspended.

The wait time is 16.6  $\mu$ s to 18.5  $\mu$ s when fclk = fiH, and 33.3  $\mu$ s to 36.9  $\mu$ s when fclk = fiH/2.

However, counting the oscillation stabilization time of fx can continue even while the CPU is waiting.

4. To increase fcLk to 10 MHz or higher, set FSEL to "1", then change fcLk after two or more clocks have elapsed. Use the external bus interface two clock cycles after setting FSEL to 1.

<R>

<R>

5. Flash memory can be used at a frequency of 10 MHz or lower if FSEL is 1.

## Figure 7-40. Operation Procedure of Interval Timer/Square Wave Output Function (1/2)

|                               | Software Operation                                                                                                                                                                                                                                                       | Hardware Status                                                                                                                                                                                                                                                                                 |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TAU<br>default<br>setting     |                                                                                                                                                                                                                                                                          | Power-off status<br>(Clock supply is stopped and writing to each register is<br>disabled.)                                                                                                                                                                                                      |

|                               | Sets the TAU0EN bit, TAU1EN bit of the PER0 register to 1                                                                                                                                                                                                                | Power-on status. Each channel stops operating.<br>(Clock supply is started and writing to each register is<br>enabled.)                                                                                                                                                                         |

|                               | Sets the TPSm register.<br>Determines clock frequencies of CKm0 and CKm1.                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                 |

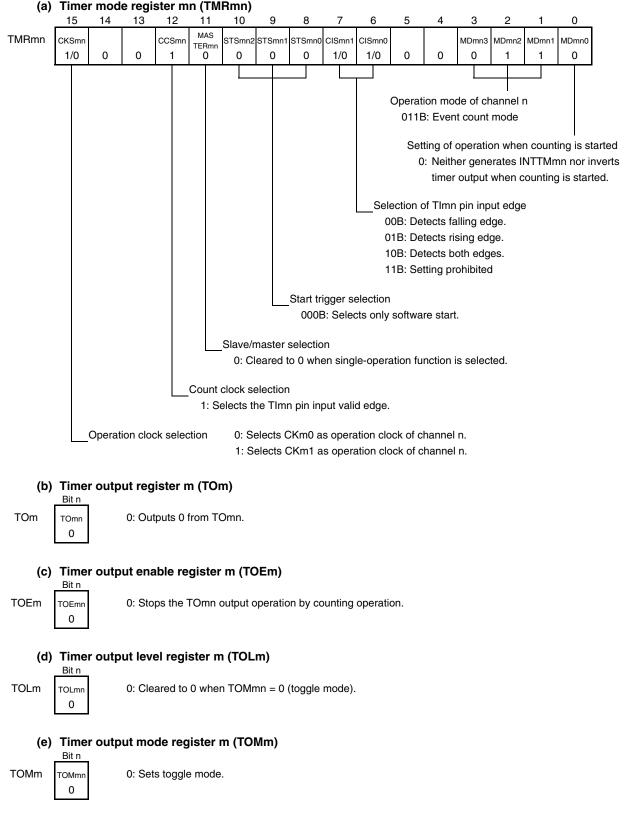

| Channel<br>default<br>setting | Sets the TMRmn register (determines operation mode of channel).<br>Sets the TISmn bit to 1 ( $f_{SUB}/4$ ) when $f_{SUB}/4$ is selected as the count clock.<br>Sets interval (period) value to the TDRmn register.                                                       | Channel stops operating.<br>(Clock is supplied and some power is consumed.)                                                                                                                                                                                                                     |

|                               | To use the TOmn output<br>Clears the TOMmn bit of the TOMm register to 0<br>(toggle mode).<br>Clears the TOLmn bit to 0.<br>Sets the TOmn bit and determines default level of the<br>TOmn output.                                                                        | The TOmn pin goes into Hi-Z output state.<br>The TOmn default setting level is output when the port mode<br>register is in the output mode and the port register is 0.                                                                                                                          |

|                               |                                                                                                                                                                                                                                                                          | TOmn does not change because channel stops operating.<br>The TOmn pin outputs the TOmn set level.                                                                                                                                                                                               |

| Operation<br>start            | Sets TOEmn to 1 (only when operation is resumed).<br>Sets the TSmn bit to 1.<br>The TSmn bit automatically returns to 0 because it is a<br>trigger bit.                                                                                                                  | TEmn = 1, and count operation starts.<br>Value of TDRmn is loaded to TCRmn at the count clock<br>input. INTTMmn is generated and TOmn performs toggle<br>operation if the MDmn0 bit of the TMRmn register is 1.                                                                                 |

| During<br>operation           | Set values of TMRmn register, TOMmn, and TOLmn bits<br>cannot be changed.<br>Set value of the TDRmn register can be changed.<br>The TCRmn register can always be read.<br>The TSRmn register is not used.<br>Set values of the TOm and TOEm registers can be<br>changed. | Counter (TCRmn) counts down. When count value reaches<br>0000H, the value of TDRmn is loaded to TCRmn again and<br>the count operation is continued. By detecting TCRmn =<br>0000H, INTTMmn is generated and TOmn performs toggle<br>operation.<br>After that, the above operation is repeated. |

| Operation<br>stop             | The TTmn bit is set to 1.<br>The TTmn bit automatically returns to 0 because it is a<br>trigger bit.                                                                                                                                                                     | TEmn = 0, and count operation stops.<br>TCRmn holds count value and stops.<br>The TOmn output is not initialized but holds current status                                                                                                                                                       |

|                               | TOEmn is cleared to 0 and value is set to TOmn bit.                                                                                                                                                                                                                      | The TOmn pin outputs the TOmn set level.                                                                                                                                                                                                                                                        |

**Remark** m: Unit number (m = 0, 1), n: Channel number (n = 0 to 7),

mn = 00 to 07, 10 to 13

**Remark** m: Unit number (m = 0, 1), n: Channel number (n = 0 to 7), mn = 00 to 07, 10 to 13

#### Figure 8-4. Format of Real-Time Counter Control Register 1 (RTCC1) (2/2)

| RIFG                                                                                                                                              | Constant-period interrupt status flag       |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--|--|

| 0                                                                                                                                                 | Constant-period interrupt is not generated. |  |  |

| 1                                                                                                                                                 | Constant-period interrupt is generated.     |  |  |

| This flag indicates the status of generation of the constant-period interrupt. When the constant-period interrupt is generated, it is set to "1". |                                             |  |  |

This flag is cleared when "0" is written to it. Writing "1" to it is invalid.

| RWST                                                              | Wait status flag of real-time counter                                                  |  |  |

|-------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|

| 0                                                                 | Counter is operating.                                                                  |  |  |

| 1                                                                 | Mode to read or write counter value                                                    |  |  |

| This status flag indicates whether the setting of RWAIT is valid. |                                                                                        |  |  |

| Before readin                                                     | Before reading or writing the counter value, confirm that the value of this flag is 1. |  |  |

| RWAIT                                                                                                           | Wait control of real-time counter                               |  |  |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--|--|

| 0                                                                                                               | Sets counter operation.                                         |  |  |

| 1                                                                                                               | Stops SEC to YEAR counters. Mode to read or write counter value |  |  |

| This bit controls the operation of the counter.                                                                 |                                                                 |  |  |

| Be sure to write "1" to it to read or write the counter value.                                                  |                                                                 |  |  |

| Because RSUBC continues operation, complete reading or writing of it in 1 second, and clear this bit back to 0. |                                                                 |  |  |

| When RWAIT = 1, it takes up to 1 clock (32.768 kHz) until the counter value can be read or written.             |                                                                 |  |  |

| If RSUBC overflows when RWAIT = 1, it counts up after RWAIT = 0. If the second count register is written,       |                                                                 |  |  |

| however, it does not count up because RSUBC is cleared.                                                         |                                                                 |  |  |

- Caution The RIFG and WAFG flags may be cleared when the RTCC1 register is written by using a 1-bit manipulation instruction. Use, therefore, an 8-bit manipulation instruction in order to write to the RTCC1 register. To prevent the RIFG and WAFG flags from being cleared during writing, disable writing by setting "1" to the corresponding bit. When the value may be rewritten because the RIFG and WAFG flags are not being used, the RTCC1 register may be written by using a 1-bit manipulation instruction.

- **Remark** Fixed-cycle interrupts and alarm match interrupts use the same interrupt source (INTRTC). When using these two types of interrupts at the same time, which interrupt occurred can be judged by checking the fixed-cycle interrupt status flag (RIFG) and the alarm detection status flag (WAFG) upon INTRTC occurrence.

### 11.4.3 A/D converter operation mode

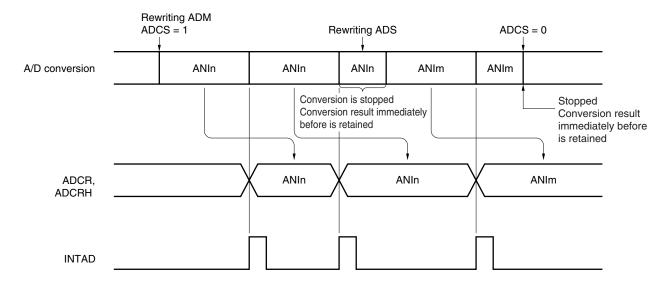

The operation mode of the A/D converter is the select mode. One channel of analog input is selected from ANI0 to ANI15 by the analog input channel specification register (ADS) and A/D conversion is executed.

### (1) A/D conversion operation

By setting bit 7 (ADCS) of the A/D converter mode register (ADM) to 1, the A/D conversion operation of the voltage, which is applied to the analog input pin specified by the analog input channel specification register (ADS), is started.

When A/D conversion has been completed, the result of the A/D conversion is stored in the A/D conversion result register (ADCR), and an interrupt request signal (INTAD) is generated. When one A/D conversion has been completed, the next A/D conversion operation is immediately started.

If ADS is rewritten during A/D conversion, the A/D conversion operation under execution is stopped and restarted from the beginning.

If 0 is written to ADCS during A/D conversion, A/D conversion is immediately stopped. At this time, the conversion result immediately before is retained.

## Figure 11-14. A/D Conversion Operation

**Remarks 1.** n = 0 to 15 **2.** m = 0 to 15

#### (2) Operation procedure

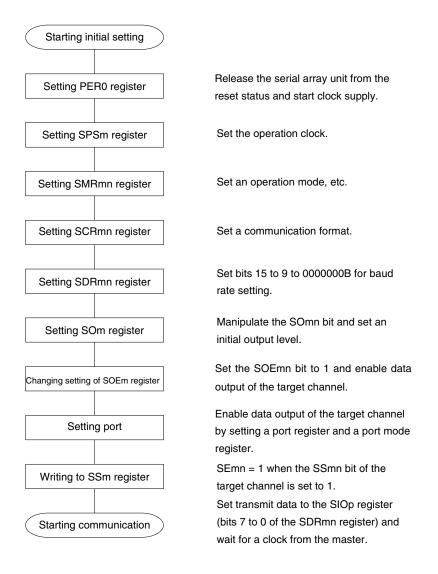

#### Figure 13-49. Initial Setting Procedure for Slave Transmission

Caution After setting the PER0 register to 1, be sure to set the SPSm register after 4 or more clocks have elapsed.

- Notes 1. The SE1 register is a read-only status register which is set using the SS1 and ST1 registers.

- 2. When channel 1 of unit 1 is set to UART2 reception, this pin becomes an RxD2 function pin. In this case, set channel 0 of unit 1 to operation stop mode or UART2 transmission (refer to **Table 13-9**). When channel 0 of unit 1 is set to CSI20 or IIC20, this pin cannot be used as an RxD2 function pin. In this case, set channel 2 of unit 1 to operation stop mode or CSI21 or IIC21.

- 3. This pin can be set as a port function pin.

- 4. This is 0 or 1, depending on the communication operation. For details, refer to 13.3 (12) Serial output register m (SOm).

- 5. When using UART2 transmission and reception in a pair, set channel 1 of unit 0 to UART2 transmission (refer to Table 13-9).

- The SMR10 register of channel 1 of unit 0 must also be set during UART2 reception. For details, refer to 13.6.2 (1) Register setting.

- **7.** Set the CKO11 bit to 1 before a start condition is generated. Clear the SO11 bit from 1 to 0 when the start condition is generated.

- **8.** Set the CKO11 bit to 1 before a stop condition is generated. Clear the SO11 bit from 0 to 1 when the stop condition is generated.

Remark X: Don't care

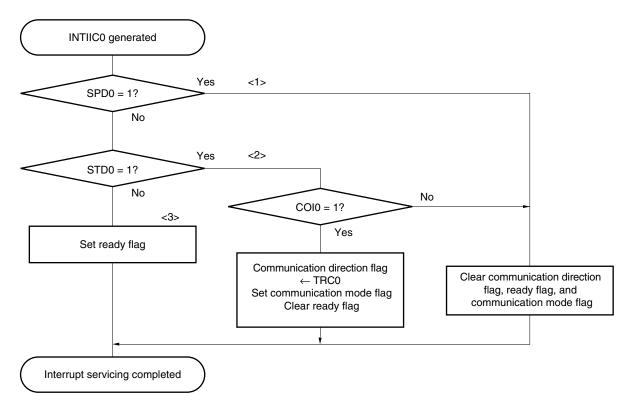

An example of the processing procedure of the slave with the INTIICO interrupt is explained below (processing is performed assuming that no extension code is used). The INTIICO interrupt checks the status, and the following operations are performed.

- <1> Communication is stopped if the stop condition is issued.

- <2> If the start condition is issued, the address is checked and communication is completed if the address does not match. If the address matches, the communication mode is set, wait is cancelled, and processing returns from the interrupt (the ready flag is cleared).

- <3> For data transmit/receive, only the ready flag is set. Processing returns from the interrupt with the I<sup>2</sup>C bus remaining in the wait state.

Remark <1> to <3> above correspond to <1> to <3> in Figure 14-27 Slave Operation Flowchart (2).

Figure 14-27. Slave Operation Flowchart (2)

#### (2) Slave device operation (slave address data reception)

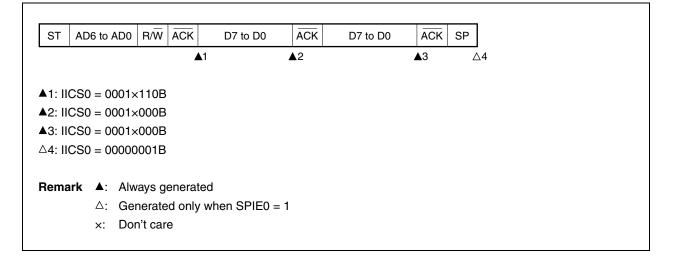

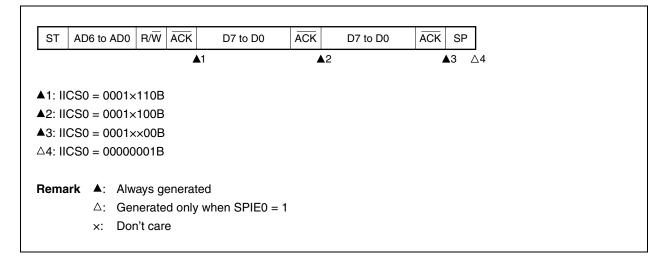

### (a) Start ~ Address ~ Data ~ Data ~ Stop

## (i) When WTIM0 = 0

(ii) When WTIM0 = 1

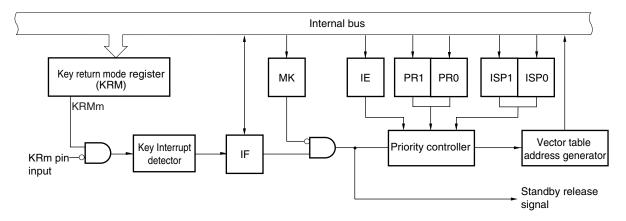

## Figure 17-1. Basic Configuration of Interrupt Function (2/2)

# <R> (C) External maskable interrupt (INTKR)

#### (D) Software interrupt

### Remarks 1. IF: Interrupt request flag

- IE: Interrupt enable flag

- ISP0: In-service priority flag 0

- ISP1: In-service priority flag 1

- MK: Interrupt mask flag

- PR0: Priority specification flag 0

- PR1: Priority specification flag 1

**2.** m = 0 to 7

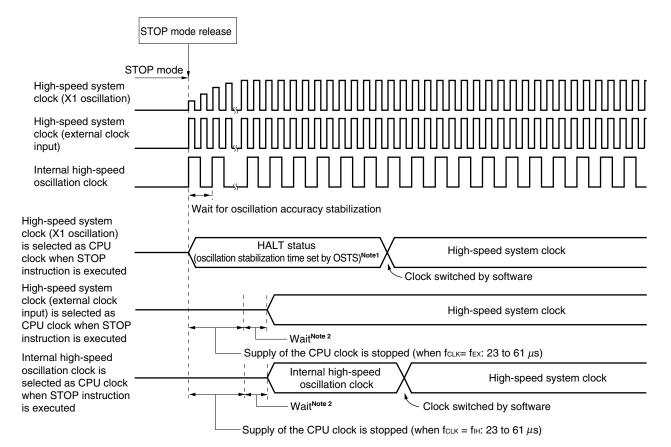

### (2) STOP mode release

## Figure 19-5. Operation Timing When STOP Mode Is Released (Release by Unmasked Interrupt Request)

- **Notes 1.** When the oscillation stabilization time set by OSTS is equal to or shorter than 61  $\mu$ s, the HALT status is retained to a maximum of "61 $\mu$ s + wait time."

- 2. The wait time is as follows:

- When vectored interrupt servicing is carried out: 10 to 12 clocks

- When vectored interrupt servicing is not carried out: 5 or 6 clocks

- Remark fex: External main system clock frequency

- fin: Internal high-speed oscillation clock frequency

- fclk: CPU/peripheral hardware clock frequency

The STOP mode can be released by the following two sources.

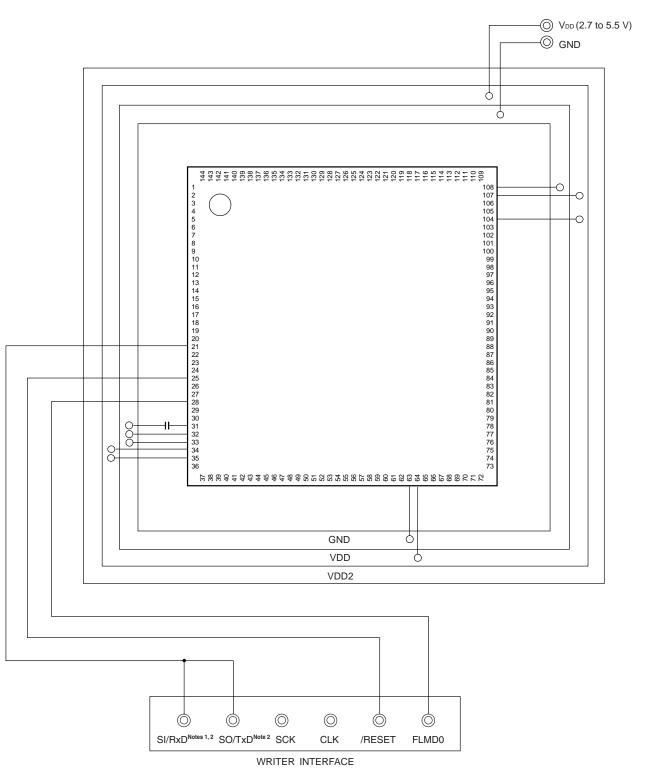

Examples of the recommended connection when using the adapter for flash memory writing are shown below.

- Notes 1. This pin is not required to be connected when using PG-FP5 or FL-PR5.

- 2. Connect SI/RxD or SO/TxD when using QB-MINI2.

#### 25.9 Flash Memory Programming by Self-Programming

The 78K0R/KJ3 supports a self-programming function that can be used to rewrite the flash memory via a user program. Because this function allows a user application to rewrite the flash memory by using the 78K0R/KJ3 self-programming library, it can be used to upgrade the program in the field.

If an interrupt occurs during self-programming, self-programming can be temporarily stopped and interrupt servicing can be executed. If an unmasked interrupt request is generated in the EI state, the request branches directly from the self-programming library to the interrupt routine. After the self-programming mode is later restored, self-programming can be resumed. However, the interrupt response time is different from that of the normal operation mode.

- **Remark** For details of the self-programming function and the 78K0R/KJ3 self-programming library, refer to **78K0R Microcontroller Self Programming Library Type01 User's Manual (U18706E)**.

- Cautions 1. The self-programming function cannot be used when the CPU operates with the subsystem clock.

- 2. In the self-programming mode, call the self-programming start library (FlashStart).

- 3. To prohibit an interrupt during self-programming, in the same way as in the normal operation mode, execute the self-programming library in the state where the IE flag is cleared (0) by the DI instruction. To enable an interrupt, clear (0) the interrupt mask flag to accept in the state where the IE flag is set (1) by the EI instruction, and then execute the self-programming library.

- 4. The self-programming function is disabled in the low consumption current mode. For details of the low consumption current mode, see CHAPTER 23 REGULATOR.

- 5. Disable DMA operation (DENn = 0) during the execution of self programming library functions.

## Standard Products

## (1) Basic operation (6/6)

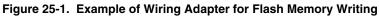

## AC Timing Test Points (Excluding External Bus Interface)

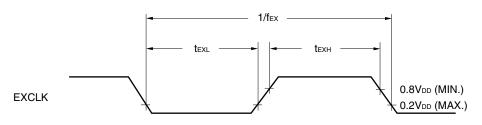

## **External Main System Clock Timing**

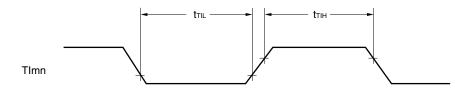

**TI Timing**

**Remark** m: Unit number (m = 0, 1), n: Channel number (n = 0 to 7), mn = 00-07, 10-13

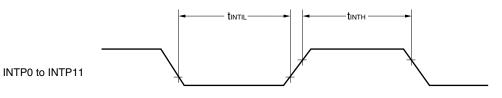

### Interrupt Request Input Timing

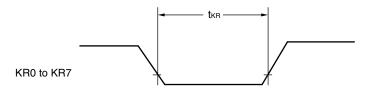

Key Interrupt Input Timing

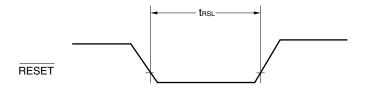

**RESET** Input Timing

Standard Products

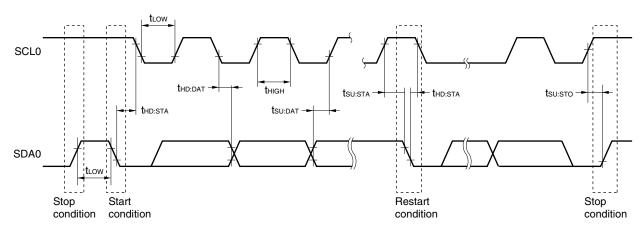

## (4) Serial interface: IIC0

## $(T_{A} = -40 \text{ to } +85^{\circ}\text{C}, 1.8 \text{ V} \leq \text{V}_{\text{DD}} = \text{EV}_{\text{DD}} = \text{EV}_{\text{DD}} \leq 5.5 \text{ V}, \text{V}_{\text{SS}} = \text{EV}_{\text{SS}} = \text{EV}_{\text{SS}} = \text{AV}_{\text{SS}} = 0 \text{ V})$

| Parameter                                         | Symbol       | Conditions                                              | Standar | Standard Mode          |      | Fast Mode              |     |

|---------------------------------------------------|--------------|---------------------------------------------------------|---------|------------------------|------|------------------------|-----|

|                                                   |              |                                                         | MIN.    | MAX.                   | MIN. | MAX.                   |     |

| SCL0 clock frequency                              | fsc∟         | $6.7 \text{ MHz} \leq f_{CLK}$                          | 0       | 100                    | 0    | 400                    | kHz |

|                                                   |              | $4.0 \text{ MHz} \le f_{CLK} < 6.7 \text{ MHz}$         | 0       | 100                    | 0    | 340                    | kHz |

|                                                   |              | $3.2 \text{ MHz} \le f_{\text{CLK}} < 4.0 \text{ MHz}$  | 0       | 100                    | 1    | _                      | kHz |

|                                                   |              | $2.0 \text{ MHz} \leq f_{\text{CLK}} < 3.2 \text{ MHz}$ | 0       | 85                     | _    | _                      | kHz |

| Setup time of restart condition <sup>Note 1</sup> | tsu:sta      |                                                         | 4.7     |                        | 0.6  |                        | μs  |

| Hold time                                         | thd:sta      |                                                         | 4.0     |                        | 0.6  |                        | μS  |

| Hold time when SCL0 = "L"                         | tLOW         |                                                         | 4.7     |                        | 1.3  |                        | μs  |

| Hold time when SCL0 = "H"                         | tніgн        |                                                         | 4.0     |                        | 0.6  |                        | μs  |

| Data setup time (reception)                       | tsu:dat      |                                                         | 250     |                        | 100  |                        | ns  |

| Data hold time (transmission) <sup>Note 2</sup>   | thd:dat      | CL00 = 1 and CL01 = 1                                   | 0       | 3.45 <sup>Note 3</sup> | 0    | 0.9 <sup>Note 4</sup>  | μS  |

|                                                   |              |                                                         |         | 5.50 <sup>Note 5</sup> |      | 1.5 Note 6             | μS  |

|                                                   |              | CL00 = 0 and CL01 = 0, or                               | 0       | 3.45                   | 0    | 0.9 <sup>Note 7</sup>  | μs  |

|                                                   |              | CL00 = 1 and CL01 = 0                                   |         |                        |      | 0.95 <sup>Note 8</sup> | μS  |

|                                                   |              | CL00 = 0 and CL01 = 1                                   | 0       | 3.45                   | 0    | 0.9                    | μS  |

| Setup time of stop condition                      | tsu:sto      |                                                         | 4.0     |                        | 0.6  |                        | μS  |

| Bus-free time                                     | <b>t</b> BUF |                                                         | 4.7     |                        | 1.3  |                        | μs  |

Notes 1. The first clock pulse is generated after this period when the start/restart condition is detected.

- 2. The maximum value (MAX.) of the during normal transfer and a wait state is inserted in the ACK (acknowledge) timing.

- 3. When 3.2 MHz  $\leq f_{CLK} \leq 4.19$  MHz.

- 4. When 6.7 MHz  $\leq$  fclk  $\leq$  8.38 MHz.

- 5. When 2.0 MHz  $\leq$  fclk < 3.2 MHz. At this time, use the SCL0 clock within 85 kHz.

- 6. When 4.0 MHz  $\leq$  f<sub>CLK</sub> < 6.7 MHz. At this time, use the SCL0 clock within 340 kHz.

- 7. When 8.0 MHz  $\leq$  folk  $\leq$  16.76 MHz.

- 8. When 7.6 MHz  $\leq$  fclk < 8.0 MHz.

Remark CL00, CL01, DFC0: Bits 0, 1, and 2 of the IIC clock select register 0 (IICCL0)

#### IIC0 serial transfer timing

## A.5 Debugging Tools (Hardware)

### A.5.1 When using in-circuit emulator QB-78K0RKX3

| QB-78K0KX3 <sup>Note</sup><br>In-circuit emulator | This in-circuit emulator serves to debug hardware and software when developing application systems using the 78K0R/Kx3. It supports to the integrated debugger (ID78K0R-QB). This emulator should be used in combination with a power supply unit and emulation probe, and the USB is used to connect this emulator to the host machine. |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QB-144-CA-01<br>Check pin adapter                 | This check pin adapter is used in waveform monitoring using the oscilloscope, etc.                                                                                                                                                                                                                                                       |

| QB-144-EP-02S<br>Emulation probe                  | This emulation probe is flexible type and used to connect the in-circuit emulator and target system.                                                                                                                                                                                                                                     |

| QB-144GJ-EA-05T<br>Exchange adapter               | This exchange adapter is used to perform pin conversion from the in-circuit emulator to target connector.                                                                                                                                                                                                                                |

| QB-144GJ-YS-01T<br>Space adapter                  | This space adapter is used to adjust the height between the target system and in-circuit emulator.                                                                                                                                                                                                                                       |

| QB-144GJ-YQ-01T<br>YQ connector                   | This YQ connector is used to connect the target connector and exchange adapter.                                                                                                                                                                                                                                                          |

| QB-144GJ-HQ-01T<br>Mount adapter                  | This mount adapter is used to mount the target device with socket.                                                                                                                                                                                                                                                                       |

| QB-144GJ-NQ-01T<br>Target connector               | This target connector is used to mount on the target system.                                                                                                                                                                                                                                                                             |

- **Remarks 1.** The QB-78K0RKX3 is supplied with a power supply unit and USB interface cable. As control software, integrated debugger ID78K0R-QB and on-chip debug emulator with programming function QB-MINI2 are supplied.

- 2. The packed contents differ depending on the part number, as follows.

| Packed Contents    | In-Circuit Emulator | Emulation Probe | Exchange Adapter | YQ Connector    | Target Connector |  |  |

|--------------------|---------------------|-----------------|------------------|-----------------|------------------|--|--|

| Part Number        |                     |                 |                  |                 |                  |  |  |

| QB-78K0RKX3-ZZZ    | QB-78K0RKX3         | None            |                  |                 |                  |  |  |

| QB-78K0RKX3-T144GJ |                     | QB-144-EP-02S   | QB-144GJ-EA-05T  | QB-144GJ-YQ-01T | QB-144GJ-NQ-01T  |  |  |

| T                  |           |                                            |                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | (28            | /35) |

|--------------------|-----------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|

| Chapter            |           |                                            |                                                                                                                                                                                                                                                                                                                            | Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Ρας            | je   |

| Chapter 22         | Hard      | Low-<br>voltage<br>detector                | Cautions for low-<br>voltage detector                                                                                                                                                                                                                                                                                      | There is some delay from the time supply voltage (V <sub>DD</sub> ) < LVI detection voltage (V <sub>LVI</sub> ) until the time LVI reset has been generated.<br>In the same way, there is also some delay from the time LVI detection voltage (V <sub>LVI</sub> ) $\leq$ supply voltage (V <sub>DD</sub> ) until the time LVI reset has been released (see Figure 22-12).<br>See the timing in Figure 21-2 (2) When LVI is ON upon power application (option byte: LVIOFF = 0) for the reset processing time until the normal operation is entered after the LVI reset is released.                                                                                                                                                                                     |                |      |

| Chapter 23<br>Soft | Regulator | RMC: Regulator<br>mode control<br>register | The RMC register can be rewritten only in the low consumption current mode (refer to Table 23-1). In other words, rewrite this register during CPU operation with the subsystem clock ( $f_{XT}$ ) while the high-speed system clock ( $f_{MX}$ ) and internal high-speed oscillation clock ( $f_{IH}$ ) are both stopped. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |      |

|                    |           |                                            |                                                                                                                                                                                                                                                                                                                            | When using the setting fixed to the low consumption current mode, the RMC register can be used in the following cases.<br><when as="" clock="" cpu="" is="" selected="" the="" x1=""><br/>fx <math>\leq</math> 5 MHz and fcLK <math>\leq</math> 5 MHz<br/><when are="" clock="" clock,="" cpu="" external="" for="" high-speed="" input="" internal="" or="" oscillation="" selected="" subsystem="" the=""><br/>fcLK <math>\leq</math> 5 MHz<br/>The self-programming function is disabled in the low consumption current mode.</when></when>                                                                                                                                                                                                                          | p.732<br>p.732 |      |

| 24                 | Soft      | Option                                     | -                                                                                                                                                                                                                                                                                                                          | Be sure to set FFH to 000C2H (000C2H/010C2H when the boot swap operation is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | p.734          |      |

| Chapter 24<br>Soft | S         | byte                                       | 000C0H/010C0H                                                                                                                                                                                                                                                                                                              | used).<br>Set the same value as 000C0H to 010C0H when the boot swap operation is used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | p.734          |      |

|                    |           |                                            | 000C1H/010C1H                                                                                                                                                                                                                                                                                                              | because 000C0H is replaced by 010C0H.<br>Set the same value as 000C1H to 010C1H when the boot swap operation is used because 000C1H is replaced by 010C1H.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | p.734          |      |

|                    |           |                                            | 000C2H/010C2H                                                                                                                                                                                                                                                                                                              | Set FFH to 010C2H when the boot swap operation is used because 000C2H is replaced by 010C2H.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | p.734          |      |

|                    |           |                                            | 000C3H/010C3H                                                                                                                                                                                                                                                                                                              | Set the same value as 000C3H to 010C3H when the boot swap operation is used because 000C3H is replaced by 010C3H.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | p.735          |      |

|                    |           | 000C0H/010C0H                              | The watchdog timer continues its operation during self-programming of the flash memory and EEPROM emulation. During processing, the interrupt acknowledge time is delayed. Set the overflow time and window size taking this delay into consideration.                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |      |

|                    |           |                                            | 000C1H/010C1H                                                                                                                                                                                                                                                                                                              | <ul> <li>Be sure to set bits 7 to 1 to "1".</li> <li>Even when the LVI default start function is used, if it is set to LVI operation prohibition by the software, it operates as follows:</li> <li>Does not perform low-voltage detection during LVION = 0.</li> <li>If a reset is generated while LVION = 0, LVION will be re-set to 1 when the CPU starts after reset release. There is a period when low-voltage detection cannot be performed normally, however, when a reset occurs due to WDT and illegal instruction execution.</li> <li>This is due to the fact that while the pulse width detected by LVI must be 200 μs max., LVION = 1 is set upon reset occurrence, and the CPU starts operating without waiting for the LVI stabilization time.</li> </ul> |                |      |

|                    |           |                                            | 000C3H/010C3H                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | p.737          |      |

|                    |           |                                            | Setting of option byte                                                                                                                                                                                                                                                                                                     | To specify the option byte by using assembly language, use OPT_BYTE as the relocation attribute name of the CSEG pseudo instruction. To specify the option byte to 010C0H to 010C3H in order to use the boot swap function, use the relocation attribute AT to specify an absolute address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |      |