Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Data Converters Oscillator Type | A/D 13x12b; D/A 2x12b<br>Internal                              |

|---------------------------------|----------------------------------------------------------------|

| Voltage - Supply (Vcc/Vdd)      | 1.65V ~ 3.6V                                                   |

| RAM Size                        | 16K x 8                                                        |

| EEPROM Size                     | -                                                              |

| Program Memory Type             | FLASH                                                          |

| Program Memory Size             | 128KB (128K x 8)                                               |

| Number of I/O                   | 36                                                             |

| Peripherals                     | DMA, I <sup>2</sup> S, POR, PWM, WDT                           |

| Connectivity                    | HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB |

| Speed                           | 48MHz                                                          |

| Core Size                       | 32-Bit Single-Core                                             |

| Core Processor                  | ARM® Cortex®-M0                                                |

| Product Status                  | Active                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Stop mode

Stop mode achieves very low power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled.

The device can be woken up from Stop mode by any of the EXTI lines. The EXTI line source can be one of the 16 external lines, RTC, I2C1, USART1, USART2, USB, COMPx,  $V_{DDIO2}$  supply comparator or the CEC.

The CEC, USART1, USART2 and I2C1 peripherals can be configured to enable the HSI RC oscillator so as to get clock for processing incoming data.

Note: The RTC, the IWDG, and the corresponding clock sources are not stopped by entering Stop mode.

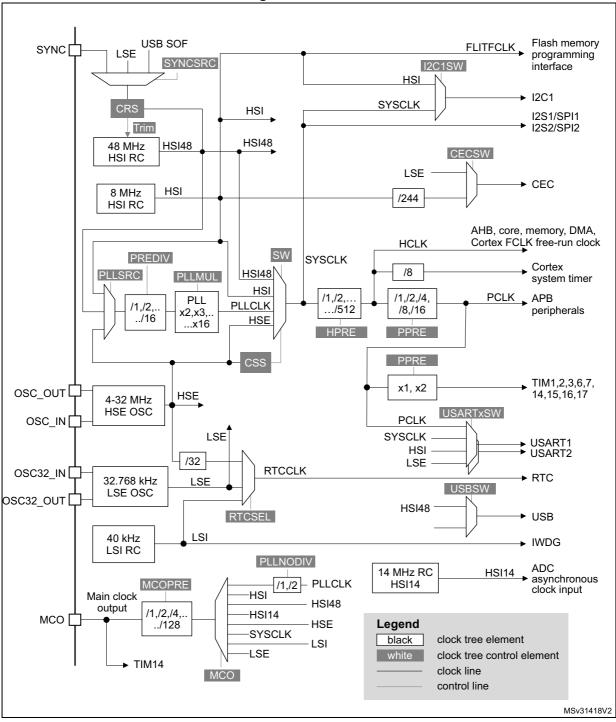

# 3.6 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-32 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example on failure of an indirectly used external crystal, resonator or oscillator).

Several prescalers allow the application to configure the frequency of the AHB and the APB domains. The maximum frequency of the AHB and the APB domains is 48 MHz.

Additionally, also the internal RC 48 MHz oscillator can be selected for system clock or PLL input source. This oscillator can be automatically fine-trimmed by the means of the CRS peripheral using the external synchronization.

Figure 2. Clock tree

# 3.7 General-purpose inputs/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions.

DocID026006 Rev 4

The I/O configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.

# 3.8 Direct memory access controller (DMA)

The 7-channel general-purpose DMAs manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers.

The DMA supports circular buffer management, removing the need for user code intervention when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with support for software trigger on each channel. Configuration is made by software and transfer sizes between source and destination are independent.

DMA can be used with the main peripherals: SPIx, I2Sx, I2Cx, USARTx, all TIMx timers (except TIM14), DAC and ADC.

# 3.9 Interrupts and events

## 3.9.1 Nested vectored interrupt controller (NVIC)

The STM32F0xx family embeds a nested vectored interrupt controller able to handle up to 32 maskable interrupt channels (not including the 16 interrupt lines of Cortex<sup>®</sup>-M0) and 4 priority levels.

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of late arriving higher priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

## 3.9.2 Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 32 edge detector lines used to generate interrupt/event requests and wake-up the system. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the internal clock period. Up to 86 GPIOs can be connected to the 16 external interrupt lines.

# 3.10 Analog-to-digital converter (ADC)

The 12-bit analog-to-digital converter has up to 16 external and 3 internal (temperature

DocID026006 Rev 4

|                                          | Number of capacitive sensing channels |             |             |  |  |  |  |  |  |

|------------------------------------------|---------------------------------------|-------------|-------------|--|--|--|--|--|--|

| Analog I/O group                         | STM32F078Vx                           | STM32F078Rx | STM32F078Cx |  |  |  |  |  |  |

| G5                                       | 3                                     | 3           | 3           |  |  |  |  |  |  |

| G6                                       | 3                                     | 3           | 3           |  |  |  |  |  |  |

| G7                                       | 3                                     | 0           | 0           |  |  |  |  |  |  |

| G8                                       | 3                                     | 0           | 0           |  |  |  |  |  |  |

| Number of capacitive<br>sensing channels | 23                                    | 17          | 16          |  |  |  |  |  |  |

Table 5. Number of capacitive sensing channels available on STM32F078CB/RB/VB devices (continued)

# 3.14 Timers and watchdogs

The STM32F078CB/RB/VB devices include up to six general-purpose timers, two basic timers and an advanced control timer.

Table 6 compares the features of the different timers.

| Timer<br>type      | Timer                                                                           | Counter resolution | Counter<br>type      | Prescaler<br>factor        | DMA<br>request<br>generation | Capture/compare<br>channels | Complementary<br>outputs |

|--------------------|---------------------------------------------------------------------------------|--------------------|----------------------|----------------------------|------------------------------|-----------------------------|--------------------------|

| Advanced control   | TIM1                                                                            | 16-bit             | Up, down,<br>up/down | integer from<br>1 to 65536 | Yes                          | 4                           | 3                        |

|                    | TIM2     32-bit     Up, down,<br>up/down     integer from<br>1 to 65536     Yes | 4                  | -                    |                            |                              |                             |                          |

|                    | TIM3                                                                            | 16-bit             | Up, down,<br>up/down | integer from<br>1 to 65536 | Yes                          | 4                           | -                        |

| General<br>purpose | TIM14                                                                           | 16-bit             | Up                   | integer from<br>1 to 65536 | No                           | 1                           | -                        |

|                    | TIM15                                                                           | 16-bit             | Up                   | integer from<br>1 to 65536 | Yes                          | 2                           | 1                        |

|                    | TIM16<br>TIM17                                                                  | 16-bit             | Up                   | integer from<br>1 to 65536 | Yes                          | 1                           | 1                        |

| Basic              | TIM6<br>TIM7                                                                    | 16-bit             | Up                   | integer from<br>1 to 65536 | Yes                          | -                           | -                        |

Table 6. Timer feature comparison

# 3.14.1 Advanced-control timer (TIM1)

The advanced-control timer (TIM1) can be seen as a three-phase PWM multiplexed on six channels. It has complementary PWM outputs with programmable inserted dead times. It

#### Table 13. Alternate functions selected through GPIOA\_AFR registers for port A Pin name AF1 AF2 AF4 AF0 AF3 AF5 AF7 AF6 USART2 CTS TIM2 CH1 ETR TSC G1 IO1 USART4 TX COMP1 OUT PA0 -EVENTOUT USART2\_RTS TIM2 CH2 TSC\_G1\_IO2 USART4 RX TIM15 CH1N PA1 \_ TIM15\_CH1 PA2 USART2\_TX TIM2\_CH3 TSC\_G1\_IO3 COMP2\_OUT ---TIM15 CH2 USART2 RX TIM2\_CH4 TSC G1 IO4 PA3 ----SPI1\_NSS, I2S1\_WS USART2\_CK TSC\_G2\_IO1 PA4 \_ TIM14\_CH1 --\_ SPI1\_SCK, I2S1\_CK CEC TIM2\_CH1\_ETR TSC\_G2\_IO2 PA5 \_ \_ USART3 CTS PA6 SPI1 MISO, I2S1 MCK TIM3 CH1 TIM1 BKIN TSC G2 103 TIM16 CH1 EVENTOUT COMP1 OUT SPI1\_MOSI, I2S1\_SD TIM3\_CH2 TIM1\_CH1N TSC\_G2\_IO4 TIM14\_CH1 TIM17 CH1 COMP2\_OUT **EVENTOUT** PA7 PA8 МСО USART1 CK TIM1\_CH1 **EVENTOUT** CRS\_SYNC \_ \_ TIM15 BKIN USART1 TX TIM1 CH2 TSC G4 IO1 PA9 ----TIM17\_BKIN USART1 RX TIM1 CH3 TSC\_G4\_IO2 PA10 ----EVENTOUT PA11 USART1\_CTS TIM1 CH4 TSC\_G4\_IO3 COMP1 OUT -\_ \_ EVENTOUT USART1\_RTS TIM1\_ETR TSC\_G4\_IO4 COMP2 OUT PA12 ---SWDIO IR\_OUT USB NOE PA13 \_ --\_ SWCLK USART2\_TX PA14 -\_ -SPI1 NSS, I2S1 WS USART2 RX TIM2 CH1 ETR **EVENTOUT** USART4 RTS

\_

-

-

DocID026006 Rev 4

PA15

39/120

STM32F078CB, STM32F078RB, STM32F078VB

| Bus  | Boundary address          | Size    | Peripheral             |

|------|---------------------------|---------|------------------------|

|      | 0x4800 1800 - 0x5FFF FFFF | ~384 MB | Reserved               |

|      | 0x4800 1400 - 0x4800 17FF | 1 KB    | GPIOF                  |

|      | 0x4800 1000 - 0x4800 13FF | 1 KB    | GPIOE                  |

|      | 0x4800 0C00 - 0x4800 0FFF | 1 KB    | GPIOD                  |

| AHB2 | 0x4800 0800 - 0x4800 0BFF | 1 KB    | GPIOC                  |

|      | 0x4800 0400 - 0x4800 07FF | 1 KB    | GPIOB                  |

|      | 0x4800 0000 - 0x4800 03FF | 1 KB    | GPIOA                  |

|      | 0x4002 4400 - 0x47FF FFFF | ~128 MB | Reserved               |

|      | 0x4002 4000 - 0x4002 43FF | 1 KB    | TSC                    |

|      | 0x4002 3400 - 0x4002 3FFF | 3 KB    | Reserved               |

|      | 0x4002 3000 - 0x4002 33FF | 1 KB    | CRC                    |

|      | 0x4002 2400 - 0x4002 2FFF | 3 KB    | Reserved               |

| AHB1 | 0x4002 2000 - 0x4002 23FF | 1 KB    | Flash memory interface |

|      | 0x4002 1400 - 0x4002 1FFF | 3 KB    | Reserved               |

|      | 0x4002 1000 - 0x4002 13FF | 1 KB    | RCC                    |

|      | 0x4002 0400 - 0x4002 0FFF | 3 KB    | Reserved               |

|      | 0x4002 0000 - 0x4002 03FF | 1 KB    | DMA                    |

|      | 0x4001 8000 - 0x4001 FFFF | 32 KB   | Reserved               |

|      | 0x4001 5C00 - 0x4001 7FFF | 9 KB    | Reserved               |

|      | 0x4001 5800 - 0x4001 5BFF | 1 KB    | DBGMCU                 |

|      | 0x4001 4C00 - 0x4001 57FF | 3 KB    | Reserved               |

|      | 0x4001 4800 - 0x4001 4BFF | 1 KB    | TIM17                  |

|      | 0x4001 4400 - 0x4001 47FF | 1 KB    | TIM16                  |

|      | 0x4001 4000 - 0x4001 43FF | 1 KB    | TIM15                  |

|      | 0x4001 3C00 - 0x4001 3FFF | 1 KB    | Reserved               |

|      | 0x4001 3800 - 0x4001 3BFF | 1 KB    | USART1                 |

|      | 0x4001 3400 - 0x4001 37FF | 1 KB    | Reserved               |

|      | 0x4001 3000 - 0x4001 33FF | 1 KB    | SPI1/I2S1              |

| APB  | 0x4001 2C00 - 0x4001 2FFF | 1 KB    | TIM1                   |

|      | 0x4001 2800 - 0x4001 2BFF | 1 KB    | Reserved               |

|      | 0x4001 2400 - 0x4001 27FF | 1 KB    | ADC                    |

|      | 0x4001 0800 - 0x4001 23FF | 7 KB    | Reserved               |

|      | 0x4001 0400 - 0x4001 07FF | 1 KB    | EXTI                   |

|      | 0x4001 0000 - 0x4001 03FF | 1 KB    | SYSCFG + COMP          |

|      | 0x4000 8000 - 0x4000 FFFF | 32 KB   | Reserved               |

# Table 19. STM32F078CB/RB/VB peripheral register boundary addresses

DocID026006 Rev 4

| Bus | Boundary address          | Size | Peripheral |

|-----|---------------------------|------|------------|

|     | 0x4000 7C00 - 0x4000 7FFF | 1 KB | Reserved   |

|     | 0x4000 7800 - 0x4000 7BFF | 1 KB | CEC        |

| -   | 0x4000 7400 - 0x4000 77FF | 1 KB | DAC        |

|     | 0x4000 7000 - 0x4000 73FF | 1 KB | PWR        |

|     | 0x4000 6C00 - 0x4000 6FFF | 1 KB | CRS        |

| -   | 0x4000 6400 - 0x4000 6BFF | 2 KB | Reserved   |

| -   | 0x4000 6000 - 0x4000 63FF | 1 KB | USB RAM    |

|     | 0x4000 5C00 - 0x4000 5FFF | 1 KB | USB        |

| -   | 0x4000 5800 - 0x4000 5BFF | 1 KB | I2C2       |

| -   | 0x4000 5400 - 0x4000 57FF | 1 KB | I2C1       |

| -   | 0x4000 5000 - 0x4000 53FF | 1 KB | Reserved   |

| -   | 0x4000 4C00 - 0x4000 4FFF | 1 KB | USART4     |

| -   | 0x4000 4800 - 0x4000 4BFF | 1 KB | USART3     |

| -   | 0x4000 4400 - 0x4000 47FF | 1 KB | USART2     |

| -   | 0x4000 3C00 - 0x4000 43FF | 2 KB | Reserved   |

| -   | 0x4000 3800 - 0x4000 3BFF | 1 KB | SPI2       |

| -   | 0x4000 3400 - 0x4000 37FF | 1 KB | Reserved   |

| APB | 0x4000 3000 - 0x4000 33FF | 1 KB | IWDG       |

| -   | 0x4000 2C00 - 0x4000 2FFF | 1 KB | WWDG       |

| -   | 0x4000 2800 - 0x4000 2BFF | 1 KB | RTC        |

| -   | 0x4000 2400 - 0x4000 27FF | 1 KB | Reserved   |

| -   | 0x4000 2000 - 0x4000 23FF | 1 KB | TIM14      |

| -   | 0x4000 1800 - 0x4000 1FFF | 2 KB | Reserved   |

| ľ   | 0x4000 1400 - 0x4000 17FF | 1 KB | TIM7       |

| ľ   | 0x4000 1000 - 0x4000 13FF | 1 KB | TIM6       |

|     | 0x4000 0800 - 0x4000 0FFF | 2 KB | Reserved   |

|     | 0x4000 0400 - 0x4000 07FF | 1 KB | TIM3       |

| ľ   | 0x4000 0000 - 0x4000 03FF | 1 KB | TIM2       |

| Table 19. STM32F078CB/RB/VB | peripheral register bounda | ry addresses (continued) |

|-----------------------------|----------------------------|--------------------------|

| Symbol            | Parameter                       | Conditions | Min | Мах | Unit |  |  |  |  |  |

|-------------------|---------------------------------|------------|-----|-----|------|--|--|--|--|--|

| t <sub>VDD</sub>  | V <sub>DD</sub> rise time rate  |            | 0   | 8   |      |  |  |  |  |  |

|                   | V <sub>DD</sub> fall time rate  | -          | 20  | 8   |      |  |  |  |  |  |

| +                 | V <sub>DDA</sub> rise time rate |            | 0   | 8   | µs/V |  |  |  |  |  |

| t <sub>VDDA</sub> | V <sub>DDA</sub> fall time rate | -          | 20  | 8   |      |  |  |  |  |  |

Table 24. Operating conditions at power-up / power-down

## 6.3.3 Embedded reference voltage

The parameters given in *Table 25* are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 23: General operating conditions*.

| Symbol                   | Parameter                                                           | Conditions                        | Min                  | Тур  | Max                | Unit   |

|--------------------------|---------------------------------------------------------------------|-----------------------------------|----------------------|------|--------------------|--------|

| V <sub>REFINT</sub>      | Internal reference voltage                                          | –40 °C < T <sub>A</sub> < +105 °C | 1.2                  | 1.23 | 1.25               | V      |

| t <sub>START</sub>       | ADC_IN17 buffer startup time                                        | -                                 | -                    | -    | 10 <sup>(1)</sup>  | μs     |

| t <sub>S_vrefint</sub>   | ADC sampling time when<br>reading the internal<br>reference voltage | -                                 | 4 <sup>(1)</sup>     | -    | -                  | μs     |

| ΔV <sub>REFINT</sub>     | Internal reference voltage<br>spread over the<br>temperature range  | V <sub>DDA</sub> = 3 V            | -                    | -    | 10 <sup>(1)</sup>  | mV     |

| T <sub>Coeff</sub>       | Temperature coefficient                                             | -                                 | - 100 <sup>(1)</sup> | -    | 100 <sup>(1)</sup> | ppm/°C |

| T <sub>VREFINT_RDY</sub> | Internal reference voltage temporization                            | -                                 | 1.5                  | 2.5  | 4.5                | ms     |

Table 25. Embedded internal reference voltage

1. Guaranteed by design, not tested in production.

Guaranteed by design, not tested in production. This parameter is the latency between the time when pin NPOR is set to 1 by the application and the time when the VREFINTRDYF status bit is set to 1 by the hardware.

## 6.3.4 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 13: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to CoreMark code.

| Symbol           | ेष्ट्र            |                       |                   |      |                    | $V_{DDA} = 3.6 V$   |                    |     |                                     |       |                    |      |     |     |     |  |

|------------------|-------------------|-----------------------|-------------------|------|--------------------|---------------------|--------------------|-----|-------------------------------------|-------|--------------------|------|-----|-----|-----|--|

|                  | Para-meter        | Conditions            | f <sub>HCLK</sub> |      | М                  | ax @ T <sub>A</sub> |                    |     | Max @ T <sub>A</sub> <sup>(2)</sup> |       |                    | Unit |     |     |     |  |

|                  | Para              |                       |                   | Тур  | 25 °C              | 85 °C               | 105 °C             | Тур | 25 °C                               | 85 °C | 105 °C             |      |     |     |     |  |

|                  |                   | HSI48                 | 48 MHz            | 309  | 325                | 328                 | 332                | 320 | 335                                 | 339   | 348                |      |     |     |     |  |

|                  |                   | HSE                   | 48 MHz            | 151  | 169 <sup>(3)</sup> | 177                 | 180 <sup>(3)</sup> | 163 | 181 <sup>(3)</sup>                  | 192   | 196 <sup>(3)</sup> |      |     |     |     |  |

|                  | Supply current in | bypass,<br>PLL on     | 32 MHz            | 103  | 119                | 124                 | 126                | 112 | 127                                 | 133   | 135                |      |     |     |     |  |

|                  | Run or            |                       | 24 MHz            | 81   | 95                 | 98                  | 100                | 87  | 100                                 | 105   | 107                |      |     |     |     |  |

|                  | Sleep<br>mode,    | HSE                   | 8 MHz             | 1.6  | 2.8                | 3.0                 | 3.3                | 2.1 | 3.2                                 | 3.4   | 3.9                |      |     |     |     |  |

| I <sub>DDA</sub> | code<br>executing | bypass,<br>PLL off    | 1 MHz             | 1.6  | 2.8                | 3.0                 | 3.3                | 2.0 | 3.2                                 | 3.4   | 3.9                | μA   |     |     |     |  |

|                  | from              | from                  | from              | from | from               |                     | 48 MHz             | 217 | 238                                 | 249   | 253                | 238  | 259 | 272 | 278 |  |

|                  | Flash<br>memory   | ,                     | 32 MHz            | 170  | 189                | 197                 | 200                | 187 | 205                                 | 214   | 218                |      |     |     |     |  |

|                  | or RAM            |                       | 24 MHz            | 146  | 164                | 170                 | 173                | 162 | 178                                 | 186   | 189                |      |     |     |     |  |

|                  |                   | HSI clock,<br>PLL off | 8 MHz             | 67   | 76                 | 79                  | 80                 | 77  | 86                                  | 89    | 90                 |      |     |     |     |  |

Table 27. Typical and maximum current consumption from the V<sub>DDA</sub> supply

Current consumption from the V<sub>DDA</sub> supply is independent of whether the digital peripherals are enabled or disabled, being in Run or Sleep mode or executing from Flash memory or RAM. Furthermore, when the PLL is off, I<sub>DDA</sub> is independent from the frequency.

2. Data based on characterization results, not tested in production unless otherwise specified.

3. Data based on characterization results and tested in production (using one common test limit for sum of IDD and IDDA).

| Symbol               |                   | Conditions                                                                       | Тур @ V <sub>BAT</sub> |       |       |       |       |       |                          |                          |                            |      |

|----------------------|-------------------|----------------------------------------------------------------------------------|------------------------|-------|-------|-------|-------|-------|--------------------------|--------------------------|----------------------------|------|

|                      | Parameter         |                                                                                  | 1.65 V                 | 1.8 V | 2.4 V | 2.7 V | 3.3 V | 3.6 V | T <sub>A</sub> =<br>25 ℃ | T <sub>A</sub> =<br>85 ℃ | T <sub>A</sub> =<br>105 °C | Unit |

| I <sub>DD_VBAT</sub> | RTC<br>domain     | LSE & RTC ON; "Xtal<br>mode": lower driving<br>capability;<br>LSEDRV[1:0] = '00' | 0.5                    | 0.6   | 0.7   | 0.8   | 1.1   | 1.2   | 1.3                      | 1.7                      | 2.3                        |      |

|                      | supply<br>current | LSE & RTC ON; "Xtal<br>mode" higher driving<br>capability;<br>LSEDRV[1:0] = '11' | 0.8                    | 0.9   | 1.1   | 1.2   | 1.4   | 1.6   | 1.7                      | 2.1                      | 2.8                        | μA   |

#### Table 28. Typical and maximum current consumption from the V<sub>BAT</sub> supply

1. Data based on characterization results, not tested in production.

| Symbol           | Parameter      | Conditions                                         | Min <sup>(1)</sup> | Unit   |  |  |  |  |

|------------------|----------------|----------------------------------------------------|--------------------|--------|--|--|--|--|

| N <sub>END</sub> | Endurance      | T <sub>A</sub> = -40 to +105 °C                    | 10                 | kcycle |  |  |  |  |

|                  | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C  | 30                 |        |  |  |  |  |

| t <sub>RET</sub> |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C | 10                 | Year   |  |  |  |  |

|                  |                | 10 kcycle <sup>(2)</sup> at T <sub>A</sub> = 55 °C | 20                 |        |  |  |  |  |

Table 44. Flash memory endurance and data retention

1. Data based on characterization results, not tested in production.

2. Cycling performed over the whole temperature range.

# 6.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- **FTB**: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 45*. They are based on the EMS levels and classes defined in application note AN1709.

| Syml              | bol | Parameter                                                                                                                         | Conditions                                                                                                        | Level/<br>Class |

|-------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FE</sub> s | SD  | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 1.8 V, LQFP100, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 48 MHz,<br>conforming to IEC 61000-4-2 | 2B              |

| V <sub>EF</sub>   | ТВ  | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD}$ = 1.8 V, LQFP100, T <sub>A</sub> = +25°C,<br>f <sub>HCLK</sub> = 48 MHz,<br>conforming to IEC 61000-4-4  | 4B              |

### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

| Symbol           | Parameter                                               | Conditions                                                                                          | Min | Тур | Max   | Unit |

|------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----|-----|-------|------|

|                  | Input leakage<br>current <sup>(2)</sup>                 | TC, FT and FTf I/O<br>TTa in digital mode<br>V <sub>SS</sub> ≤ V <sub>IN</sub> ≤ V <sub>DDIOx</sub> | -   | -   | ± 0.1 | μA   |

| l <sub>lkg</sub> |                                                         | TTa in digital mode<br>V <sub>DDIOx</sub> ≤ V <sub>IN</sub> ≤ V <sub>DDA</sub>                      | -   | -   | 1     |      |

| 5                |                                                         | TTa in analog mode<br>V <sub>SS</sub> ≤ V <sub>IN</sub> ≤ V <sub>DDA</sub>                          | -   | -   | ± 0.2 |      |

|                  |                                                         | FT and FTf I/O<br>V <sub>DDIOx</sub> ≤ V <sub>IN</sub> ≤ 5 V                                        | -   | -   | 10    |      |

| R <sub>PU</sub>  | Weak pull-up<br>equivalent resistor<br>(3)              | V <sub>IN</sub> = V <sub>SS</sub>                                                                   | 25  | 40  | 55    | kΩ   |

| R <sub>PD</sub>  | Weak pull-down<br>equivalent<br>resistor <sup>(3)</sup> | V <sub>IN</sub> = - V <sub>DDIOx</sub>                                                              | 25  | 40  | 55    | kΩ   |

| C <sub>IO</sub>  | I/O pin capacitance                                     | -                                                                                                   | -   | 5   | -     | pF   |

#### Table 50. I/O static characteristics (continued)

1. Data based on design simulation only. Not tested in production.

2. The leakage could be higher than the maximum value, if negative current is injected on adjacent pins. Refer to *Table 49: I/O current injection susceptibility*.

3. Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimal (~10% order).

All I/Os are CMOS- and TTL-compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 21* for standard I/Os, and in *Figure 22* for 5 V-tolerant I/Os. The following curves are design simulation results, not tested in production.

| Symbol                                 | Parameter                        | Conditions                                             | Min                                                                        | Тур | Max                                               | Unit                       |  |

|----------------------------------------|----------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------|-----|---------------------------------------------------|----------------------------|--|

|                                        |                                  | ADC clock = HSI14                                      | 1.5 ADC<br>cycles + 2<br>f <sub>PCLK</sub> cycles                          | -   | 1.5 ADC<br>cycles + 3<br>f <sub>PCLK</sub> cycles | -                          |  |

| W <sub>LATENCY</sub> <sup>(2)(4)</sup> | ADC_DR register ready<br>latency | ADC clock = PCLK/2                                     | -                                                                          | 4.5 | -                                                 | f <sub>PCLK</sub><br>cycle |  |

|                                        |                                  | ADC clock = PCLK/4                                     | -                                                                          | 8.5 | -                                                 | f <sub>PCLK</sub><br>cycle |  |

|                                        |                                  | $f_{ADC} = f_{PCLK}/2 = 14 \text{ MHz}$                | 0.196                                                                      |     |                                                   | μs                         |  |

|                                        | Trigger conversion latency       | $f_{ADC} = f_{PCLK}/2$                                 | 5.5                                                                        |     |                                                   | 1/f <sub>PCLK</sub>        |  |

| t <sub>latr</sub> (2)                  |                                  | f <sub>ADC</sub> = f <sub>PCLK</sub> /4 = 12 MHz 0.219 |                                                                            |     | μs                                                |                            |  |

|                                        |                                  | $f_{ADC} = f_{PCLK}/4$                                 | 10.5                                                                       |     | 1/f <sub>PCLK</sub>                               |                            |  |

|                                        |                                  | f <sub>ADC</sub> = f <sub>HSI14</sub> = 14 MHz         | 0.179                                                                      | -   | 0.250                                             | μs                         |  |

| Jitter <sub>ADC</sub>                  | ADC jitter on trigger conversion | f <sub>ADC</sub> = f <sub>HSI14</sub>                  | -                                                                          | 1   | -                                                 | 1/f <sub>HSI14</sub>       |  |

| ts <sup>(2)</sup>                      | Sampling time                    | f <sub>ADC</sub> = 14 MHz                              | 0.107                                                                      | -   | 17.1                                              | μs                         |  |

| ι <sub>S</sub> /                       | Sampling time                    | -                                                      | 1.5                                                                        | -   | 239.5                                             | 1/f <sub>ADC</sub>         |  |

| t <sub>STAB</sub> <sup>(2)</sup>       | Stabilization time               | -                                                      |                                                                            | 14  | •                                                 | 1/f <sub>ADC</sub>         |  |

| + (2)                                  | Total conversion time            | f <sub>ADC</sub> = 14 MHz,<br>12-bit resolution        | 1                                                                          | -   | 18                                                | μs                         |  |

| t <sub>CONV</sub> <sup>(2)</sup>       | (including sampling time)        | 12-bit resolution                                      | 14 to 252 (t <sub>S</sub> for sampling +12.5 for successive approximation) |     | 1/f <sub>ADC</sub>                                |                            |  |

Table 55. ADC characteristics (continued)

1. During conversion of the sampled value (12.5 x ADC clock period), an additional consumption of 100  $\mu$ A on I<sub>DD</sub> and 60  $\mu$ A on I<sub>DD</sub> should be taken into account.

2. Guaranteed by design, not tested in production.

3. Specified value includes only ADC timing. It does not include the latency of the register access.

4. This parameter specify latency for transfer of the conversion result to the ADC\_DR register. EOC flag is set at this time.

## Equation 1: R<sub>AIN</sub> max formula

$$R_{AIN} < \frac{T_{S}}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$$

The formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. Here N = 12 (from 12-bit resolution).

| T <sub>s</sub> (cycles) | t <sub>S</sub> (μs) | R <sub>AIN</sub> max (kΩ) <sup>(1)</sup> |

|-------------------------|---------------------|------------------------------------------|

| 1.5                     | 0.11                | 0.4                                      |

| 7.5                     | 0.54                | 5.9                                      |

| 13.5                    | 0.96                | 11.4                                     |

#### Table 56. R<sub>AIN</sub> max for f<sub>ADC</sub> = 14 MHz

| Symbol                               | Parameter                                                                                                                                                          | Min | Тур | Max  | Unit | Comments                                                                                                                |  |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|-------------------------------------------------------------------------------------------------------------------------|--|

| Gain error <sup>(3)</sup>            | Gain error                                                                                                                                                         | -   | -   | ±0.5 | %    | Given for the DAC in 12-bit configuration                                                                               |  |

| t <sub>SETTLING</sub> <sup>(3)</sup> | Settling time (full scale: for a<br>10-bit input code transition<br>between the lowest and the<br>highest input codes when<br>DAC_OUT reaches final<br>value ±1LSB | -   | 3   | 4    | μs   | C <sub>LOAD</sub> ≤ 50 pF, R <sub>LOAD</sub> ≥ 5 kΩ                                                                     |  |

| Update<br>rate <sup>(3)</sup>        | Max frequency for a correct<br>DAC_OUT change when<br>small variation in the input<br>code (from code i to i+1LSB)                                                 | -   | -   | 1    | MS/s | C <sub>LOAD</sub> ≤ 50 pF, R <sub>LOAD</sub> ≥ 5 kΩ                                                                     |  |

| t <sub>WAKEUP</sub> <sup>(3)</sup>   | Wakeup time from off state<br>(Setting the ENx bit in the<br>DAC Control register)                                                                                 | -   | 6.5 | 10   | μs   | $C_{LOAD} \le 50 \text{ pF}, R_{LOAD} \ge 5 \text{ k}\Omega$<br>input code between lowest and<br>highest possible ones. |  |

| PSRR+ <sup>(1)</sup>                 | Power supply rejection ratio<br>(to V <sub>DDA</sub> ) (static DC<br>measurement                                                                                   | -   | -67 | -40  | dB   | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF                                                                        |  |

Table 58. DAC characteristics (continued)

1. Guaranteed by design, not tested in production.

2. The DAC is in "quiescent mode" when it keeps the value steady on the output so no dynamic consumption is involved.

3. Data based on characterization results, not tested in production.

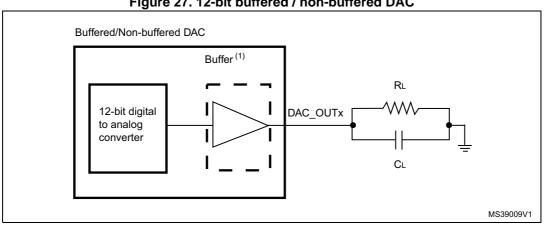

The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register. 1.

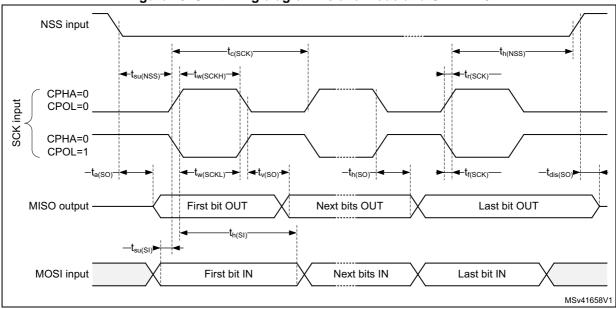

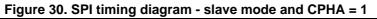

Figure 29. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are done at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}$

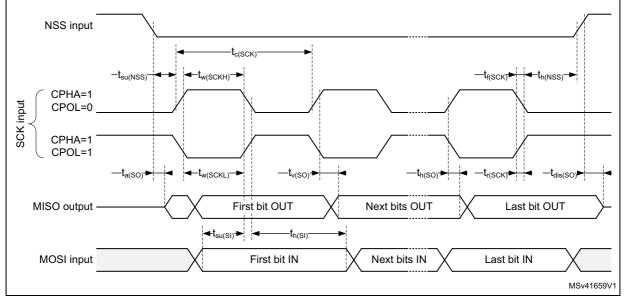

## Figure 33. I<sup>2</sup>S master timing diagram (Philips protocol)

- 1. Data based on characterization results, not tested in production.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

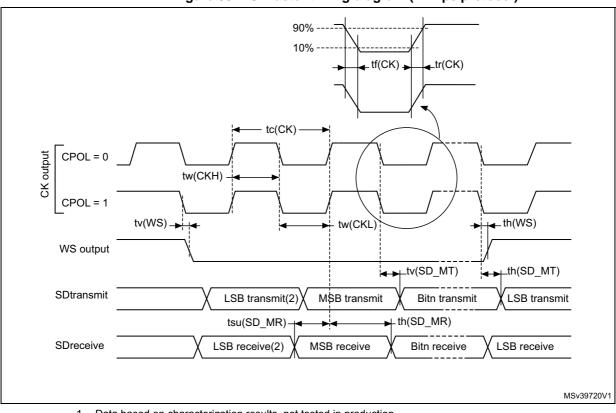

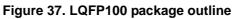

# 7.2 LQFP100 package information

LQFP100 is a100-pin, 14 x 14 mm low-profile quad flat package.

1. Drawing is not to scale.

| Symbol |        | millimeters |        | inches <sup>(1)</sup> |        |        |  |

|--------|--------|-------------|--------|-----------------------|--------|--------|--|

| Symbol | Min    | Тур         | Мах    | Min                   | Тур    | Max    |  |

| А      | -      | -           | 1.600  | -                     | -      | 0.0630 |  |

| A1     | 0.050  | -           | 0.150  | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.170  | 0.220       | 0.270  | 0.0067                | 0.0087 | 0.0106 |  |

| С      | 0.090  | -           | 0.200  | 0.0035                | -      | 0.0079 |  |

| D      | 15.800 | 16.000      | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |

| D1     | 13.800 | 14.000      | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |

| D3     | -      | 12.000      | -      | -                     | 0.4724 | -      |  |

| E      | 15.800 | 16.000      | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |

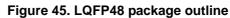

# 7.5 LQFP48 package information

LQFP48 is a 48-pin, 7 x 7 mm low-profile quad flat package.

1. Drawing is not to scale.

| Symbol |       | millimeters |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------|-------------|-------|-----------------------|--------|--------|--|

| Symbol | Min   | Тур         | Max   | Min                   | Тур    | Max    |  |

| А      | -     | -           | 1.600 | -                     | -      | 0.0630 |  |

| A1     | 0.050 | -           | 0.150 | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350 | 1.400       | 1.450 | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.170 | 0.220       | 0.270 | 0.0067                | 0.0087 | 0.0106 |  |

| с      | 0.090 | -           | 0.200 | 0.0035                | -      | 0.0079 |  |

| D      | 8.800 | 9.000       | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |

| D1     | 6.800 | 7.000       | 7.200 | 0.2677                | 0.2756 | 0.2835 |  |

| D3     | -     | 5.500       | -     | -                     | 0.2165 | -      |  |

| E      | 8.800 | 9.000       | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |

| E1     | 6.800 | 7.000       | 7.200 | 0.2677                | 0.2756 | 0.2835 |  |

| E3     | -     | 5.500       | -     | -                     | 0.2165 | -      |  |

| е      | -     | 0.500       | -     | -                     | 0.0197 | -      |  |

| L      | 0.450 | 0.600       | 0.750 | 0.0177                | 0.0236 | 0.0295 |  |

| L1     | -     | 1.000       | -     | -                     | 0.0394 | -      |  |

| k      | 0°    | 3.5°        | 7°    | 0°                    | 3.5°   | 7°     |  |

| ССС    | -     | -           | 0.080 | -                     | -      | 0.0031 |  |

| Table 74. | LQFP48 | package | mechanical | data |

|-----------|--------|---------|------------|------|

|           |        | pachage | meenamear  | uata |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

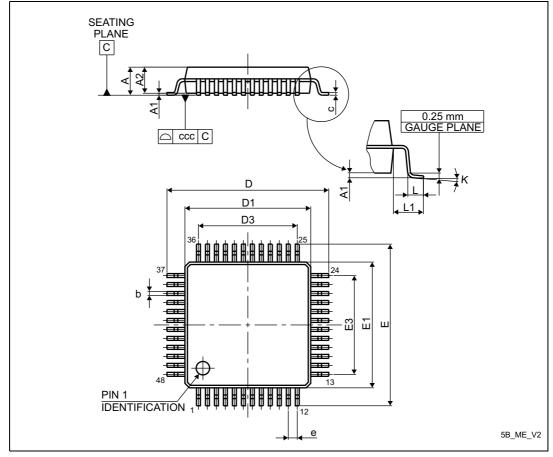

#### Figure 46. Recommended footprint for LQFP48 package

1. Dimensions are expressed in millimeters.

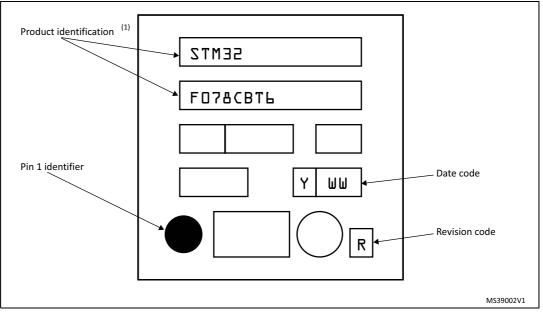

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

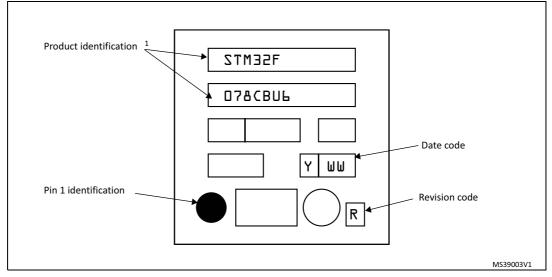

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 50. UFQFPN48 package marking example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.