Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 48MHz                                                                   |

| Connectivity               | HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                    |

| Number of I/O              | 36                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                |                                                                         |

| RAM Size                   | 16K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                            |

| Data Converters            | A/D 13x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 49-UFBGA, WLCSP                                                         |

| Supplier Device Package    | 49-WLCSP                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f078cby6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 47. | ESD absolute maximum ratings                        | 72    |

|-----------|-----------------------------------------------------|-------|

| Table 48. | Electrical sensitivities                            | 72    |

| Table 49. | I/O current injection susceptibility                | 73    |

| Table 50. | I/O static characteristics                          | 73    |

| Table 51. | Output voltage characteristics                      | 76    |

| Table 52. | I/O AC characteristics                              | 77    |

| Table 53. | NRST pin characteristics                            | 79    |

| Table 54. | NPOR pin characteristics                            | 80    |

| Table 55. | ADC characteristics                                 |       |

| Table 56. | R <sub>AIN</sub> max for f <sub>ADC</sub> = 14 MHz. | 81    |

| Table 57. | ADC accuracy                                        |       |

| Table 58. | DAC characteristics                                 | 84    |

| Table 59. | Comparator characteristics                          | 86    |

| Table 60. | TS characteristics                                  | 88    |

| Table 61. | V <sub>BAT</sub> monitoring characteristics         | 88    |

| Table 62. | TIMx characteristics                                | 88    |

| Table 63. | IWDG min/max timeout period at 40 kHz (LSI)         | 89    |

| Table 64. | WWDG min/max timeout value at 48 MHz (PCLK).        | 89    |

| Table 65. | I <sup>2</sup> C analog filter characteristics      | 90    |

| Table 66. | SPI characteristics                                 | 90    |

| Table 67. | I <sup>2</sup> S characteristics                    | 92    |

| Table 68. | USB electrical characteristics                      | 95    |

| Table 69. | UFBGA100 package mechanical data                    | 96    |

| Table 70. | UFBGA100 recommended PCB design rules.              | 97    |

| Table 71. | LQPF100 package mechanical data                     | 99    |

| Table 72. | LQFP64 package mechanical data                      | . 102 |

| Table 73. | WLCSP49 package mechanical data                     | . 106 |

| Table 74. | LQFP48 package mechanical data                      | . 109 |

| Table 75. | UFQFPN48 package mechanical data                    | . 112 |

| Table 76. | Package thermal characteristics                     | . 114 |

| Table 77. | Ordering information scheme                         |       |

| Table 78. | Document revision history                           | . 118 |

| Perip                | oheral                                | STM32F078CB                   | STM32F078RB                                                                                                            | STM32F078VB           |  |  |  |  |

|----------------------|---------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|--|

| Flash memory (Kbyte) |                                       | 128                           |                                                                                                                        |                       |  |  |  |  |

| SRAM                 | (Kbyte)                               |                               | 16                                                                                                                     |                       |  |  |  |  |

|                      | Advanced control                      |                               | 1 (16-bit)                                                                                                             |                       |  |  |  |  |

| Timers               | General<br>purpose                    |                               | 5 (16-bit)<br>1 (32-bit)                                                                                               |                       |  |  |  |  |

|                      | Basic                                 |                               | 2 (16-bit)                                                                                                             |                       |  |  |  |  |

|                      | SPI [I <sup>2</sup> S] <sup>(1)</sup> |                               | 2 [2]                                                                                                                  |                       |  |  |  |  |

|                      | l <sup>2</sup> C                      |                               | 2                                                                                                                      |                       |  |  |  |  |

| Comm.                | USART                                 |                               | 4                                                                                                                      |                       |  |  |  |  |

| interfaces           | USB                                   | 1                             |                                                                                                                        |                       |  |  |  |  |

|                      | CEC                                   | 1                             |                                                                                                                        |                       |  |  |  |  |

|                      | t ADC<br>f channels)                  | 1<br>(10 ext. + 3 int.)       |                                                                                                                        |                       |  |  |  |  |

|                      | t DAC<br>f channels)                  | 1 (2)                         |                                                                                                                        |                       |  |  |  |  |

| Analog c             | omparator                             | 2                             |                                                                                                                        |                       |  |  |  |  |

| GP                   | PIOs                                  | 36                            | 50                                                                                                                     | 86                    |  |  |  |  |

|                      | re sensing<br>nnels                   | 16                            | 17                                                                                                                     | 23                    |  |  |  |  |

| Max. CPU             | frequency                             |                               | 48 MHz                                                                                                                 |                       |  |  |  |  |

| Operatin             | ig voltage                            | V <sub>DD</sub> :             | = 1.8 V ± 8%, V <sub>DDA</sub> = from V <sub>DD</sub>                                                                  | <sub>o</sub> to 3.6 V |  |  |  |  |

| Operating t          | temperature                           |                               | Ambient operating temperature: -40°C to 85°C / -40°C to 105°C<br>Junction temperature: -40°C to 105°C / -40°C to 125°C |                       |  |  |  |  |

| Packages             |                                       | LQFP48<br>UFQFPN48<br>WLCSP49 | LQFP64                                                                                                                 | LQFP100<br>UFBGA100   |  |  |  |  |

Table 1. STM32F078CB/RB/VB family device features and peripheral counts

1. The SPI interface can be used either in SPI mode or in  $I^2S$  audio mode.

## 3.4 Cyclic redundancy check calculation unit (CRC)

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code using a configurable generator polynomial value and size.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

## 3.5 **Power management**

### 3.5.1 Power supply schemes

- $V_{DD} = V_{DDIO1} = 1.8 \text{ V} \pm 8\%$ : external power supply for I/Os ( $V_{DDIO1}$ ) and digital logic. It is provided externally through VDD pins.

- V<sub>DDA</sub> = from V<sub>DD</sub> to 3.6 V: external analog power supply for ADC, DAC, RCs and PLL (minimum voltage to be applied to V<sub>DDA</sub> is 2.4 V when the ADC or DAC are used). It is provided externally through VDDA pin. The V<sub>DDA</sub> voltage level must be always greater or equal to the V<sub>DD</sub> voltage level and must be established first.

- V<sub>DDIO2</sub> = 1.65 to 3.6 V: external power supply for marked I/Os. V<sub>DDIO2</sub> is provided externally through the VDDIO2 pin. The V<sub>DDIO2</sub> voltage level is completely independent from V<sub>DD</sub> or V<sub>DDA</sub>, but it must not be provided without a valid supply on V<sub>DD</sub>. The V<sub>DDIO2</sub> supply is monitored and compared with the internal reference voltage (V<sub>REFINT</sub>). When the V<sub>DDIO2</sub> is below this threshold, all the I/Os supplied from this rail are disabled by hardware. The output of this comparator is connected to EXTI line 31 and it can be used to generate an interrupt. Refer to the pinout diagrams or tables for concerned I/Os list.

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

For more details on how to connect power pins, refer to *Figure 12: Power supply scheme*.

### 3.5.2 Power-on reset

To guarantee a proper power-on reset, the NPOR pin must be held low until  $V_{DD}$  is stable. When  $V_{DD}$  is stable, the reset state can be exited either by:

- putting the NPOR pin in high impedance (NPOR pin has an internal pull-up), or by

- forcing the pin to high level by connecting it to V<sub>DDA</sub>

### 3.5.3 Low-power modes

The STM32F078CB/RB/VB microcontrollers support two low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

#### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

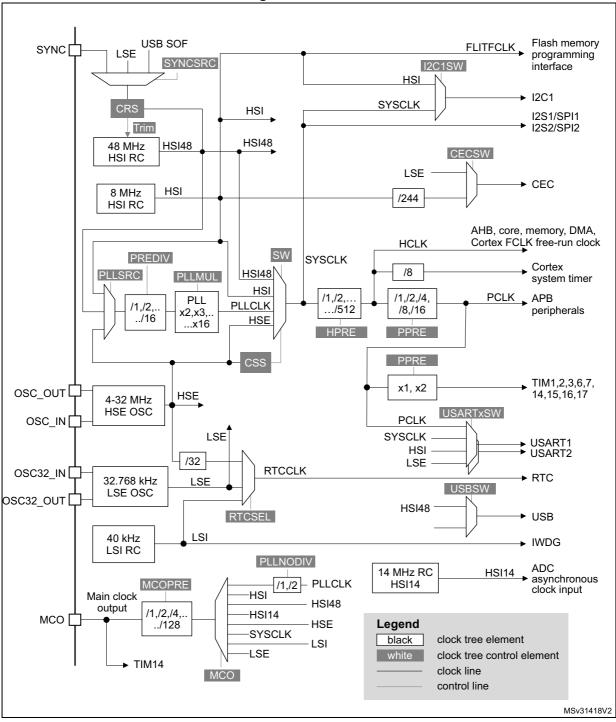

Figure 2. Clock tree

# 3.7 General-purpose inputs/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions.

DocID026006 Rev 4

| Analog I/O group                         | Number of capacitive sensing channels |             |             |  |  |  |  |

|------------------------------------------|---------------------------------------|-------------|-------------|--|--|--|--|

|                                          | STM32F078Vx                           | STM32F078Rx | STM32F078Cx |  |  |  |  |

| G5                                       | 3                                     | 3           | 3           |  |  |  |  |

| G6                                       | 3                                     | 3           | 3           |  |  |  |  |

| G7                                       | 3                                     | 0           | 0           |  |  |  |  |

| G8                                       | 3                                     | 0           | 0           |  |  |  |  |

| Number of capacitive<br>sensing channels | 23                                    | 17          | 16          |  |  |  |  |

Table 5. Number of capacitive sensing channels available on STM32F078CB/RB/VB devices (continued)

# 3.14 Timers and watchdogs

The STM32F078CB/RB/VB devices include up to six general-purpose timers, two basic timers and an advanced control timer.

Table 6 compares the features of the different timers.

| Timer<br>type      | Timer          | Counter resolution | Counter<br>type      | Prescaler<br>factor        | DMA<br>request<br>generation | Capture/compare<br>channels | Complementary<br>outputs |

|--------------------|----------------|--------------------|----------------------|----------------------------|------------------------------|-----------------------------|--------------------------|

| Advanced control   | TIM1           | 16-bit             | Up, down,<br>up/down | integer from<br>1 to 65536 | Yes                          | 4                           | 3                        |

|                    | TIM2           | 32-bit             | Up, down,<br>up/down | integer from<br>1 to 65536 | Yes                          | 4                           | -                        |

|                    | TIM3           | 16-bit             | Up, down,<br>up/down | integer from<br>1 to 65536 | Yes                          | 4                           | -                        |

| General<br>purpose | TIM14          | 16-bit             | Up                   | integer from<br>1 to 65536 | No                           | 1                           | -                        |

|                    | TIM15          | 16-bit             | Up                   | integer from<br>1 to 65536 | Yes                          | 2                           | 1                        |

|                    | TIM16<br>TIM17 | 16-bit             | Up                   | integer from<br>1 to 65536 | Yes                          | 1                           | 1                        |

| Basic              | TIM6<br>TIM7   | 16-bit             | Up                   | integer from<br>1 to 65536 | Yes                          | -                           | -                        |

Table 6. Timer feature comparison

## 3.14.1 Advanced-control timer (TIM1)

The advanced-control timer (TIM1) can be seen as a three-phase PWM multiplexed on six channels. It has complementary PWM outputs with programmable inserted dead times. It

|          | Pin     | numb   | oers            |         | e 12. STM32F078                      |             |               |            | Pin functions                                              |                                                              |  |  |

|----------|---------|--------|-----------------|---------|--------------------------------------|-------------|---------------|------------|------------------------------------------------------------|--------------------------------------------------------------|--|--|

| UFBGA100 | LQFP100 | LQFP64 | LQFP48/UFQFPN48 | WLCSP49 | Pin name<br>(function upon<br>reset) | Pin<br>type | I/O structure | Notes      | Alternate functions                                        | Additional<br>functions                                      |  |  |

| C1       | 7       | 2      | 2               | D5      | PC13                                 | I/O         | тс            | (1)<br>(2) | -                                                          | WKUP2,<br>RTC_TAMP1,<br>RTC_TS,<br>RTC_OUT                   |  |  |

| D1       | 8       | 3      | 3               | C7      | PC14-OSC32_IN<br>(PC14)              | I/O         | тс            | (1)<br>(2) | -                                                          | OSC32_IN                                                     |  |  |

| E1       | 9       | 4      | 4               | C6      | PC15-<br>OSC32_OUT<br>(PC15)         | I/O         | тс            | (1)<br>(2) | -                                                          | OSC32_OUT                                                    |  |  |

| F2       | 10      | -      | -               | -       | PF9                                  | I/O         | FT            | -          | TIM15_CH1                                                  | -                                                            |  |  |

| G2       | 11      | -      | -               | -       | PF10                                 | I/O         | FT            | -          | TIM15_CH2                                                  | -                                                            |  |  |

| F1       | 12      | 5      | 5               | D7      | PF0-OSC_IN<br>(PF0)                  | I/O         | FT            | -          | CRS_SYNC                                                   | OSC_IN                                                       |  |  |

| G1       | 13      | 6      | 6               | D6      | PF1-OSC_OUT<br>(PF1)                 | I/O         | FT            | -          | -                                                          | OSC_OUT                                                      |  |  |

| H2       | 14      | 7      | 7               | E7      | NRST                                 | I/O         | RST           | -          | Device reset input / internal reset output<br>(active low) |                                                              |  |  |

| H1       | 15      | 8      | -               | -       | PC0                                  | I/O         | TTa           | -          | EVENTOUT                                                   | ADC_IN10                                                     |  |  |

| J2       | 16      | 9      | -               | -       | PC1                                  | I/O         | TTa           | -          | EVENTOUT                                                   | ADC_IN11                                                     |  |  |

| J3       | 17      | 10     | -               | -       | PC2                                  | I/O         | ТТа           | -          | SPI2_MISO, I2S2_MCK,<br>EVENTOUT                           | ADC_IN12                                                     |  |  |

| K2       | 18      | 11     | -               | -       | PC3                                  | I/O         | ТТа           | -          | SPI2_MOSI, I2S2_SD,<br>EVENTOUT                            | ADC_IN13                                                     |  |  |

| J1       | 19      | -      | -               | -       | PF2                                  | I/O         | FT            | -          | EVENTOUT                                                   | WKUP8                                                        |  |  |

| K1       | 20      | 12     | 8               | E6      | VSSA                                 | S           | -             | I          | Analog groui                                               | nd                                                           |  |  |

| M1       | 21      | 13     | 9               | F7      | VDDA                                 | S           | -             | -          | Analog power s                                             | upply                                                        |  |  |

| L1       | 22      | -      | -               | -       | PF3                                  | I/O         | FT            | -          | EVENTOUT                                                   |                                                              |  |  |

| L2       | 23      | 14     | 10              | F6      | PA0                                  | I/O         | ТТа           | -          | USART2_CTS,<br>TIM2_CH1_ETR,<br>TSC_G1_IO1,<br>USART4_TX   | RTC_TAMP2,<br>WKUP1,<br>COMP1_OUT,<br>ADC_IN0,<br>COMP1_INM6 |  |  |

Table 12. STM32F078CB/RB/VB pin definitions (continued)

|          | Pin     | numt   | oers            |         |                                      |             | _             |       | Pin functions                                                                         |                         |  |

|----------|---------|--------|-----------------|---------|--------------------------------------|-------------|---------------|-------|---------------------------------------------------------------------------------------|-------------------------|--|

| UFBGA100 | LQFP100 | LQFP64 | LQFP48/UFQFPN48 | WLCSP49 | Pin name<br>(function upon<br>reset) | Pin<br>type | I/O structure | Notes | Alternate functions                                                                   | Additional<br>functions |  |

| M6       | 36      | 27     | 19              | G4      | PB1                                  | I/O         | ТТа           | -     | TIM3_CH4, USART3_RTS,<br>TIM14_CH1, TIM1_CH3N,<br>TSC_G3_IO3                          | ADC_IN9                 |  |

| L6       | 37      | 28     | 20              | G3      | NPOR                                 | I           | POR           | (3)   | Device power-on reset in                                                              | out (active low)        |  |

| M7       | 38      | -      | -               | -       | PE7                                  | I/O         | FT            | -     | TIM1_ETR                                                                              | -                       |  |

| L7       | 39      | -      | -               | -       | PE8                                  | I/O         | FT            | -     | TIM1_CH1N                                                                             | -                       |  |

| M8       | 40      | -      | -               | -       | PE9                                  | I/O         | FT            | -     | TIM1_CH1                                                                              | -                       |  |

| L8       | 41      | -      | -               | -       | PE10                                 | I/O         | FT            | -     | TIM1_CH2N                                                                             | -                       |  |

| M9       | 42      | -      | -               | -       | PE11                                 | I/O         | FT            | -     | TIM1_CH2                                                                              | -                       |  |

| L9       | 43      | -      | -               | -       | PE12                                 | I/O         | FT            | -     | SPI1_NSS, I2S1_WS,<br>TIM1_CH3N                                                       | -                       |  |

| M10      | 44      | -      | -               | -       | PE13                                 | I/O         | FT            | -     | SPI1_SCK, I2S1_CK,<br>TIM1_CH3                                                        | -                       |  |

| M11      | 45      | -      | -               | -       | PE14                                 | I/O         | FT            | -     | SPI1_MISO, I2S1_MCK,<br>TIM1_CH4                                                      | -                       |  |

| M12      | 46      | -      | -               | -       | PE15                                 | I/O         | FT            | -     | SPI1_MOSI, I2S1_SD,<br>TIM1_BKIN                                                      | -                       |  |

| L10      | 47      | 29     | 21              | E3      | PB10                                 | I/O         | FT            | -     | SPI2_SCK, I2C2_SCL,<br>USART3_TX, CEC,<br>TSC_SYNC, TIM2_CH3                          | -                       |  |

| L11      | 48      | 30     | 22              | G2      | PB11                                 | I/O         | FT            | -     | USART3_RX, TIM2_CH4,<br>EVENTOUT, TSC_G6_IO1,<br>I2C2_SDA                             | -                       |  |

| F12      | 49      | 31     | 23              | D3      | VSS                                  | S           | -             | -     | Ground                                                                                |                         |  |

| G12      | 50      | 32     | 24              | F2      | VDD                                  | S           | -             | I     | Digital power su                                                                      | ipply                   |  |

| L12      | 51      | 33     | 25              | E2      | PB12                                 | I/O         | FT            | -     | TIM1_BKIN, TIM15_BKIN,<br>SPI2_NSS, I2S2_WS,<br>USART3_CK,<br>TSC_G6_IO2,<br>EVENTOUT | -                       |  |

| K12      | 52      | 34     | 26              | G1      | PB13                                 | I/O         | FTf           | -     | SPI2_SCK, I2S2_CK,<br>I2C2_SCL, USART3_CTS,<br>TIM1_CH1N, TSC_G6_IO3                  | -                       |  |

Table 12. STM32F078CB/RB/VB pin definitions (continued)

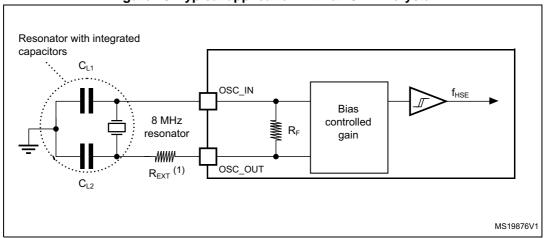

Figure 16. Typical application with an 8 MHz crystal

1.  $R_{EXT}$  value depends on the crystal characteristics.

### Low-speed external clock generated from a crystal resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 37*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                      | Conditions <sup>(1)</sup>        | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit |  |

|-------------------------------------|--------------------------------|----------------------------------|--------------------|-----|--------------------|------|--|

|                                     |                                | low drive capability             | -                  | 0.5 | 0.9                |      |  |

|                                     | LSE current consumption        | medium-low drive capability      | -                  | -   | 1                  |      |  |

| I <sub>DD</sub>                     | LSE current consumption        | medium-high drive capability     | -                  | -   | 1.3                | μA   |  |

|                                     |                                | high drive capability            | -                  | -   | 1.6                |      |  |

|                                     |                                | low drive capability             | 5                  | -   | -                  |      |  |

| ~                                   | Oscillator<br>transconductance | medium-low drive capability      | 8                  | -   | -                  |      |  |

| 9 <sub>m</sub>                      |                                | medium-high drive capability     | 15                 | -   | -                  | µA/V |  |

|                                     |                                | high drive capability            | 25                 | -   | -                  |      |  |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> | Startup time                   | V <sub>DDIOx</sub> is stabilized | -                  | 2   | -                  | S    |  |

| Table 37. LSE oscillator characteristics | (f <sub>LSE</sub> = 32.768 kHz) |

|------------------------------------------|---------------------------------|

|------------------------------------------|---------------------------------|

1. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

2. Guaranteed by design, not tested in production.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

| Symbol                | Ratings                                            | Conditions                                   | Packages   | Class | Maximum<br>value <sup>(1)</sup> | Unit |  |  |

|-----------------------|----------------------------------------------------|----------------------------------------------|------------|-------|---------------------------------|------|--|--|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model) | $T_A$ = +25 °C, conforming<br>to JESD22-A114 | All        | 2     | 2000                            | V    |  |  |

| V                     | Electrostatic discharge voltage                    | T <sub>A</sub> = +25 °C, conforming          | WLCSP49    | C3    | 250                             | V    |  |  |

| V <sub>ESD(CDM)</sub> | (charge device model)                              | to ANSI/ESD STM5.3.1                         | All others | C4    | 500                             | v    |  |  |

Table 47. ESD absolute maximum ratings

1. Data based on characterization results, not tested in production.

### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin.

- A current injection is applied to each input, output and configurable I/O pin.

These tests are compliant with EIA/JESD 78A IC latch-up standard.

| Table 48. | Electrical | sensitivities  |

|-----------|------------|----------------|

|           | LICOLIU    | 30113111411103 |

| Symbol | Parameter             | Conditions                                    | Class      |

|--------|-----------------------|-----------------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +105 \text{ °C conforming to JESD78A}$ | II level A |

## 6.3.12 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DDIOx}$  (for standard, 3.3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of the -5  $\mu$ A/+0  $\mu$ A range) or other functional failure (for example reset occurrence or oscillator frequency deviation).

The characterization results are given in *Table 49*.

Negative induced leakage current is caused by negative injection and positive induced leakage current is caused by positive injection.

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to +/-8 mA, and sink or source up to +/- 20 mA (with a relaxed  $V_{OL}/V_{OH}$ ).

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in Section 6.2:

- The sum of the currents sourced by all the I/Os on V<sub>DDIOx</sub>, plus the maximum consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 20: Voltage characteristics*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub>, plus the maximum consumption of the MCU sunk on V<sub>SS</sub>, cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see *Table 20: Voltage characteristics*).

### **Output voltage levels**

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 23: General operating conditions*. All I/Os are CMOS- and TTL-compliant (FT, TTa or TC unless otherwise specified).

| Symbol                            | Parameter                                                  | Conditions                                                                                                                                                                        | Min                     | Max | Unit |

|-----------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----|------|

| V <sub>OL</sub>                   | Output low level voltage for an I/O pin                    | CMOS port <sup>(2)</sup>                                                                                                                                                          | -                       | 0.4 |      |

| V <sub>OH</sub>                   | Output high level voltage for an I/O pin                   | I <sub>IO</sub>   = 8 mA<br>V <sub>DDIOx</sub> ≥ 2.7 V                                                                                                                            | V <sub>DDIOx</sub> -0.4 | -   | V    |

| V <sub>OL</sub>                   | Output low level voltage for an I/O pin                    | TTL port <sup>(2)</sup>                                                                                                                                                           | -                       | 0.4 |      |

| V <sub>OH</sub>                   | Output high level voltage for an I/O pin                   | TTL port <sup>(2)</sup><br>$ I_{IO}  = 8 \text{ mA}$<br>$V_{DDIOX} \ge 2.7 \text{ V}$<br>$ I_{IO}  = 20 \text{ mA}$<br>$V_{DDIOX} \ge 2.7 \text{ V}$<br>$ I_{IO}  = 6 \text{ mA}$ | 2.4                     | -   | V    |

| V <sub>OL</sub> <sup>(3)</sup>    | Output low level voltage for an I/O pin                    | I <sub>IO</sub>   = 20 mA                                                                                                                                                         | -                       | 1.3 | V    |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin                   | V <sub>DDIOx</sub> ≥ 2.7 V                                                                                                                                                        | V <sub>DDIOx</sub> -1.3 | -   | v    |

| V <sub>OL</sub> <sup>(3)</sup>    | Output low level voltage for an I/O pin                    | I <sub>IO</sub>   = 6 mA                                                                                                                                                          | -                       | 0.4 | V    |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin                   | V <sub>DDIOx</sub> ≥ 2 V                                                                                                                                                          | V <sub>DDIOx</sub> -0.4 | -   | v    |

| V <sub>OL</sub> <sup>(4)</sup>    | Output low level voltage for an I/O pin                    | II I = 4 m A                                                                                                                                                                      | -                       | 0.4 | V    |

| V <sub>OH</sub> <sup>(4)</sup>    | Output high level voltage for an I/O pin                   | I <sub>IO</sub>   = 4 mA                                                                                                                                                          | V <sub>DDIOx</sub> -0.4 | -   | V    |

| V <sub>OLFm+</sub> <sup>(3)</sup> | Output low level voltage for an FTf I/O pin in<br>Fm+ mode | I <sub>IO</sub>   = 20 mA<br>V <sub>DDIOx</sub> ≥ 2.7 V                                                                                                                           | -                       | 0.4 | V    |

|                                   |                                                            | I <sub>IO</sub>   = 10 mA                                                                                                                                                         | -                       | 0.4 | V    |

#### Table 51. Output voltage characteristics<sup>(1)</sup>

The I<sub>IO</sub> current sourced or sunk by the device must always respect the absolute maximum rating specified in Table 20: Voltage characteristics, and the sum of the currents sourced or sunk by all the I/Os (I/O ports and control pins) must always respect the absolute maximum ratings ΣI<sub>IO</sub>.

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. Data based on characterization results. Not tested in production.

4. Data based on characterization results. Not tested in production.

| Symbol                 | Parameter                                       | Conditions        | Min                                       | Тур                | Мах                                         | Unit |

|------------------------|-------------------------------------------------|-------------------|-------------------------------------------|--------------------|---------------------------------------------|------|

| V <sub>IL(NPOR)</sub>  | NPOR Input low level voltage                    | -                 | -                                         | -                  | 0.475 V <sub>DDA</sub> - 0.2 <sup>(1)</sup> |      |

| V <sub>IH(NPOR)</sub>  | NPOR Input high level voltage                   | -                 | 0.5 V <sub>DDA</sub> + 0.2 <sup>(1)</sup> | -                  | -                                           | V    |

| V <sub>hys(NPOR)</sub> | NPOR Schmitt trigger voltage<br>hysteresis      | -                 | -                                         | 100 <sup>(1)</sup> | -                                           | mV   |

| R <sub>PU</sub>        | Weak pull-up equivalent resistor <sup>(2)</sup> | $V_{IN} = V_{SS}$ | 25                                        | 40                 | 55                                          | kΩ   |

Table 54. NPOR pin characteristics

1. Guaranteed by design, not tested in production.

2. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimal ( $\sim$ 10% order).

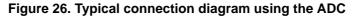

## 6.3.15 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 55* are derived from tests performed under the conditions summarized in *Table 23: General operating conditions*.

Note: It is recommended to perform a calibration after each power-up.

| Symbol                             | Parameter                                     | Conditions                                            | Min   | Тур | Max              | Unit               |

|------------------------------------|-----------------------------------------------|-------------------------------------------------------|-------|-----|------------------|--------------------|

| V <sub>DDA</sub>                   | Analog supply voltage for ADC ON              | -                                                     | 2.4   | -   | 3.6              | V                  |

| I <sub>DDA (ADC)</sub>             | Current consumption of the ADC <sup>(1)</sup> | V <sub>DDA</sub> = 3.3 V                              | -     | 0.9 | -                | mA                 |

| f <sub>ADC</sub>                   | ADC clock frequency                           | -                                                     | 0.6   | -   | 14               | MHz                |

| f <sub>S</sub> <sup>(2)</sup>      | Sampling rate                                 | 12-bit resolution                                     | 0.043 | -   | 1                | MHz                |

| f <sub>TRIG</sub> <sup>(2)</sup>   | External trigger frequency                    | f <sub>ADC</sub> = 14 MHz,<br>12-bit resolution       | -     | -   | 823              | kHz                |

|                                    |                                               | 12-bit resolution                                     | -     | -   | 17               | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                   | Conversion voltage range                      | -                                                     | 0     | -   | V <sub>DDA</sub> | V                  |

| R <sub>AIN</sub> <sup>(2)</sup>    | External input impedance                      | See <i>Equation 1</i> and <i>Table 56</i> for details | -     | -   | 50               | kΩ                 |

| $R_{ADC}^{(2)}$                    | Sampling switch resistance                    | -                                                     | -     | -   | 1                | kΩ                 |

| C <sub>ADC</sub> <sup>(2)</sup>    | Internal sample and hold capacitor            | -                                                     | -     | -   | 8                | pF                 |

| t <sub>CAL</sub> <sup>(2)(3)</sup> | Calibration time                              | f <sub>ADC</sub> = 14 MHz                             |       | 5.9 |                  | μs                 |

| <sup>L</sup> CAL                   |                                               | -                                                     | 83    |     |                  | 1/f <sub>ADC</sub> |

Table 55. ADC characteristics

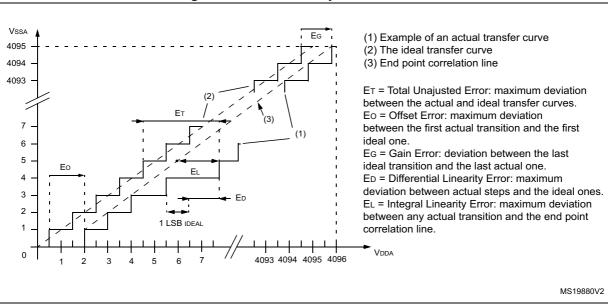

#### Figure 25. ADC accuracy characteristics

Refer to Table 55: ADC characteristics for the values of RAIN, RADC and CADC. 1.

$C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high  $C_{parasitic}$  value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced. 2.

#### General PCB design guidelines

Power supply decoupling should be performed as shown in Figure 12: Power supply scheme. The 10 nF capacitor should be ceramic (good quality) and it should be placed as close as possible to the chip.

| Symbol          | Parameter Min                                                    |                   | Мах                | Unit |

|-----------------|------------------------------------------------------------------|-------------------|--------------------|------|

| t <sub>AF</sub> | Maximum width of spikes that are suppressed by the analog filter | 50 <sup>(2)</sup> | 260 <sup>(3)</sup> | ns   |

Table 65. I<sup>2</sup>C analog filter characteristics<sup>(1)</sup>

1. Guaranteed by design, not tested in production.

2. Spikes with widths below  $t_{AF(min)}$  are filtered.

3. Spikes with widths above  $t_{AF(max)}$  are not filtered

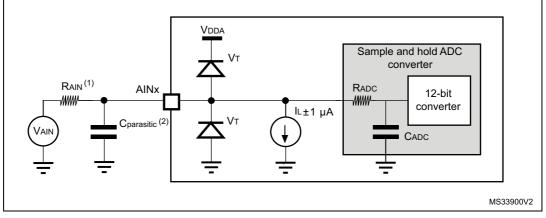

## SPI/I<sup>2</sup>S characteristics

Unless otherwise specified, the parameters given in *Table 66* for SPI or in *Table 67* for  $I^2S$  are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and supply voltage conditions summarized in *Table 23: General operating conditions*.

Refer to Section 6.3.13: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI and WS, CK, SD for I<sup>2</sup>S).

| Symbol                                       | Parameter                           | Conditions                                            | Min         | Max         | Unit  |

|----------------------------------------------|-------------------------------------|-------------------------------------------------------|-------------|-------------|-------|

| f <sub>SCK</sub>                             | SDI clock froguency                 | Master mode                                           | -           | 18          | MHz   |

| 1/t <sub>c(SCK)</sub>                        | SPI clock frequency                 | Slave mode                                            | -           | 18          | IVITZ |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>   | SPI clock rise and fall time        | Capacitive load: C = 15 pF                            | -           | 6           | ns    |

| t <sub>su(NSS)</sub>                         | NSS setup time                      | Slave mode                                            | 4Tpclk      | -           |       |

| t <sub>h(NSS)</sub>                          | NSS hold time                       | Slave mode                                            | 2Tpclk + 10 | -           |       |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time               | Master mode, f <sub>PCLK</sub> = 36 MHz,<br>presc = 4 | Tpclk/2 -2  | Tpclk/2 + 1 |       |

| t <sub>su(MI)</sub>                          | Data input setup time               | Master mode                                           | 4           | -           |       |

| t <sub>su(SI)</sub>                          |                                     | Slave mode                                            | 5           | -           |       |

| t <sub>h(MI)</sub>                           | Data input hold time                | Master mode                                           | 4           | -           |       |

| t <sub>h(SI)</sub>                           | Data input hold time                | Slave mode                                            | 5           | -           | ns    |

| t <sub>a(SO)</sub> <sup>(2)</sup>            | Data output access time             | Slave mode, f <sub>PCLK</sub> = 20 MHz                | 0           | 3Tpclk      |       |

| t <sub>dis(SO)</sub> <sup>(3)</sup>          | Data output disable time            | Slave mode                                            | 0           | 18          |       |

| t <sub>v(SO)</sub>                           | Data output valid time              | Slave mode (after enable edge)                        | -           | 22.5        |       |

| t <sub>v(MO)</sub>                           | Data output valid time              | Master mode (after enable edge)                       | -           | 6           |       |

| t <sub>h(SO)</sub>                           | Data output hold time               | Slave mode (after enable edge)                        | 11.5        | -           |       |

| t <sub>h(MO)</sub>                           |                                     | Master mode (after enable edge)                       | 2           | -           |       |

| DuCy(SCK)                                    | SPI slave input clock<br>duty cycle | Slave mode                                            | 25          | 75          | %     |

#### Table 66. SPI characteristics<sup>(1)</sup>

1. Data based on characterization results, not tested in production.

2. Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

3. Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z

Figure 31. SPI timing diagram - master mode

1. Measurement points are done at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}$

Table 67. I<sup>2</sup>S characteristics<sup>(1)</sup>

| Symbol                                  | Parameter                                     | Conditions                                               | Min   | Мах   | Unit |

|-----------------------------------------|-----------------------------------------------|----------------------------------------------------------|-------|-------|------|

| f <sub>CK</sub><br>1/t <sub>c(CK)</sub> | I <sup>2</sup> S clock frequency              | Master mode (data: 16 bits, Audio<br>frequency = 48 kHz) | 1.597 | 1.601 | MHz  |

|                                         |                                               | Slave mode                                               | 0     | 6.5   |      |

| t <sub>r(CK)</sub>                      | I <sup>2</sup> S clock rise time              | Consolitive load C = 15 pE                               | -     | 10    |      |

| t <sub>f(CK)</sub>                      | I <sup>2</sup> S clock fall time              | Capacitive load C <sub>L</sub> = 15 pF                   | -     | 12    |      |

| t <sub>w(CKH)</sub>                     | I <sup>2</sup> S clock high time              | Master f <sub>PCLK</sub> = 16 MHz, audio                 | 306   | -     |      |

| t <sub>w(CKL)</sub>                     | I <sup>2</sup> S clock low time               | frequency = 48 kHz                                       | 312   | -     |      |

| t <sub>v(WS)</sub>                      | WS valid time                                 | Master mode                                              | 2     | -     | ns   |

| t <sub>h(WS)</sub>                      | WS hold time                                  | Master mode                                              | 2     | -     |      |

| t <sub>su(WS)</sub>                     | WS setup time                                 | Slave mode                                               | 7     | -     |      |

| t <sub>h(WS)</sub>                      | WS hold time                                  | Slave mode                                               | 0     | -     |      |

| DuCy(SCK)                               | I <sup>2</sup> S slave input clock duty cycle | Slave mode                                               | 25    | 75    | %    |

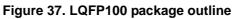

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 36. UFBGA100 package marking example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

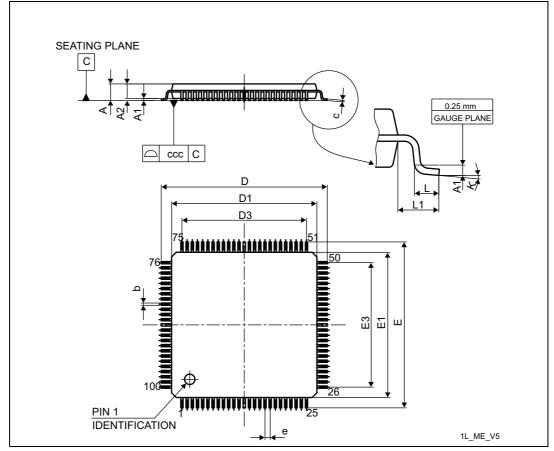

# 7.2 LQFP100 package information

LQFP100 is a100-pin, 14 x 14 mm low-profile quad flat package.

1. Drawing is not to scale.

| Symbol |        | millimeters |        |        | inches <sup>(1)</sup> |        |

|--------|--------|-------------|--------|--------|-----------------------|--------|

|        | Min    | Тур         | Мах    | Min    | Тур                   | Max    |

| А      | -      | -           | 1.600  | -      | -                     | 0.0630 |

| A1     | 0.050  | -           | 0.150  | 0.0020 | -                     | 0.0059 |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531 | 0.0551                | 0.0571 |

| b      | 0.170  | 0.220       | 0.270  | 0.0067 | 0.0087                | 0.0106 |

| С      | 0.090  | -           | 0.200  | 0.0035 | -                     | 0.0079 |

| D      | 15.800 | 16.000      | 16.200 | 0.6220 | 0.6299                | 0.6378 |

| D1     | 13.800 | 14.000      | 14.200 | 0.5433 | 0.5512                | 0.5591 |

| D3     | -      | 12.000      | -      | -      | 0.4724                | -      |

| E      | 15.800 | 16.000      | 16.200 | 0.6220 | 0.6299                | 0.6378 |

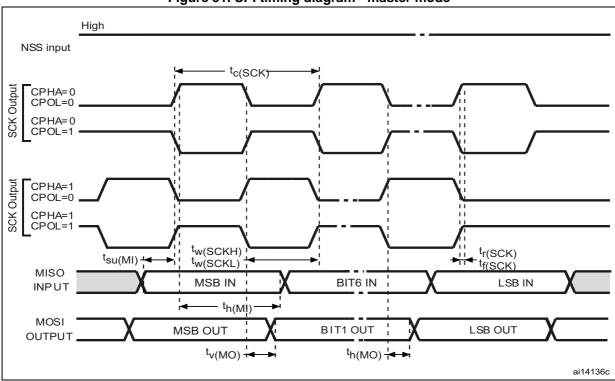

#### **Device marking**

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 44. WLCSP49 package marking example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

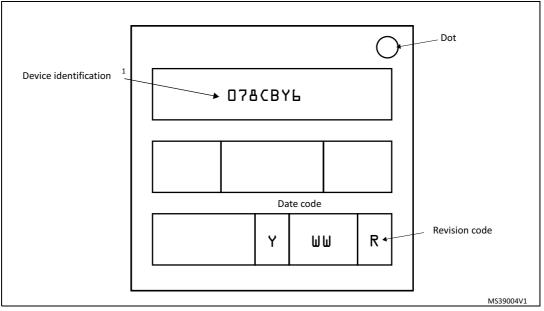

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |  |

|--------|-------|-------------|-------|--------|-----------------------|--------|--|

|        | Min   | Тур         | Max   | Min    | Тур                   | Max    |  |

| А      | 0.500 | 0.550       | 0.600 | 0.0197 | 0.0217                | 0.0236 |  |

| A1     | 0.000 | 0.020       | 0.050 | 0.0000 | 0.0008                | 0.0020 |  |

| D      | 6.900 | 7.000       | 7.100 | 0.2717 | 0.2756                | 0.2795 |  |

| E      | 6.900 | 7.000       | 7.100 | 0.2717 | 0.2756                | 0.2795 |  |

| D2     | 5.500 | 5.600       | 5.700 | 0.2165 | 0.2205                | 0.2244 |  |

| E2     | 5.500 | 5.600       | 5.700 | 0.2165 | 0.2205                | 0.2244 |  |

| L      | 0.300 | 0.400       | 0.500 | 0.0118 | 0.0157                | 0.0197 |  |

| Т      | -     | 0.152       | -     | -      | 0.0060                | -      |  |

| b      | 0.200 | 0.250       | 0.300 | 0.0079 | 0.0098                | 0.0118 |  |

| е      | -     | 0.500       | -     | -      | 0.0197                | -      |  |

| ddd    | -     | -           | 0.080 | -      | -                     | 0.0031 |  |

Table 75. UFQFPN48 package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

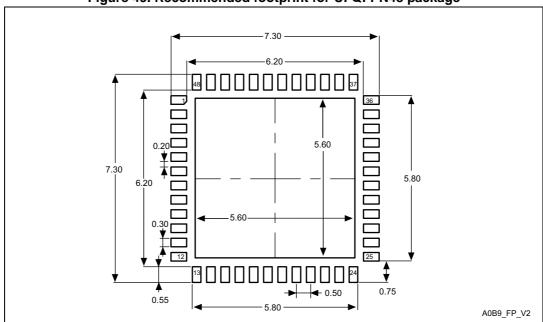

## Figure 49. Recommended footprint for UFQFPN48 package

1. Dimensions are expressed in millimeters.

# 8 Ordering information

For a list of available options (memory, package, and so on) or for further information on any aspect of this device, please contact your nearest ST sales office.

| Example:                                 | STM32 | F | 078 | R | В | Т | 6 | x |

|------------------------------------------|-------|---|-----|---|---|---|---|---|

|                                          |       |   |     |   |   |   |   |   |

| Device family                            |       |   |     |   |   |   |   |   |

| STM32 = ARM-based 32-bit microcontroller |       |   |     |   |   |   |   |   |

|                                          |       |   |     |   |   |   |   |   |

| Product type                             |       |   |     |   |   |   |   |   |

| F = General-purpose                      |       |   |     |   |   |   |   |   |

|                                          |       |   |     |   |   |   |   |   |

| Sub-family                               |       |   |     |   |   |   |   |   |

| 078 = STM32F078xx                        |       |   |     |   |   |   |   |   |

|                                          |       |   |     |   |   |   |   |   |

| Pin count                                |       |   |     |   |   |   |   |   |

| C = 48/49 pins                           |       |   |     |   |   |   |   |   |

| R = 64 pins                              |       |   |     |   |   |   |   |   |

| V = 100 pins                             |       |   |     |   |   |   |   |   |

|                                          |       |   |     |   |   |   |   |   |

| User code memory size                    |       |   |     |   |   |   |   |   |

| B = 128 Kbyte                            |       |   |     |   |   |   |   |   |

|                                          |       |   |     |   |   |   |   |   |

| Package                                  |       |   |     |   |   |   |   |   |

| H = UFBGA                                |       |   |     |   |   |   |   |   |

| T = LQFP                                 |       |   |     |   |   |   |   |   |

| U = UFQFPN                               |       |   |     |   |   |   |   |   |

| Y = WLCSP                                |       |   |     |   |   |   |   |   |

|                                          |       |   |     |   |   |   |   |   |

| Temperature range                        |       |   |     |   |   |   |   |   |

| 6 = -40 to 85 °C                         |       |   |     |   |   |   | _ |   |

| 7 = -40 to 105 °C                        |       |   |     |   |   |   |   |   |

|                                          |       |   |     |   |   |   |   |   |

| Options                                  |       |   |     |   |   |   |   |   |

xxx = code ID of programmed parts (includes packing type) TR = tape and reel packing blank = tray packing