Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M0                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 48MHz                                                                   |

| Connectivity               | HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, I²S, POR, PWM, WDT                                                 |

| Number of I/O              | 50                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 16K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                            |

| Data Converters            | A/D 19x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-UFBGA                                                                |

| Supplier Device Package    | 64-UFBGA (5x5)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f078rbh7tr |

# List of tables

| Table 1.  | STM32F078CB/RB/VB family device features and peripheral counts                                 | 11 |

|-----------|------------------------------------------------------------------------------------------------|----|

| Table 2.  | Temperature sensor calibration values                                                          |    |

| Table 3.  | Internal voltage reference calibration values                                                  |    |

| Table 4.  | Capacitive sensing GPIOs available on STM32F078CB/RB/VB devices                                | 20 |

| Table 5.  | Number of capacitive sensing channels available                                                |    |

|           | on STM32F078CB/RB/VB devices                                                                   | 20 |

| Table 6.  | Timer feature comparison                                                                       | 21 |

| Table 7.  | Comparison of I <sup>2</sup> C analog and digital filters                                      | 24 |

| Table 8.  | STM32F078CB/RB/VB I <sup>2</sup> C implementation                                              | 25 |

| Table 9.  | STM32F078CB/RB/VB USART implementation                                                         | 25 |

| Table 10. | STM32F078CB/RB/VB SPI/I <sup>2</sup> S implementation                                          | 26 |

| Table 11. | Legend/abbreviations used in the pinout table                                                  | 32 |

| Table 12. | STM32F078CB/RB/VB pin definitions                                                              |    |

| Table 13. | Alternate functions selected through GPIOA_AFR registers for port A                            | 39 |

| Table 14. | Alternate functions selected through GPIOB_AFR registers for port B                            |    |

| Table 15. | Alternate functions selected through GPIOC_AFR registers for port C                            | 41 |

| Table 16. | Alternate functions selected through GPIOD_AFR registers for port D                            |    |

| Table 17. | Alternate functions selected through GPIOE_AFR registers for port E                            |    |

| Table 18. | Alternate functions available on port F                                                        |    |

| Table 19. | STM32F078CB/RB/VB peripheral register boundary addresses                                       | 44 |

| Table 20. | Voltage characteristics                                                                        | 49 |

| Table 21. | Current characteristics                                                                        | 50 |

| Table 22. | Thermal characteristics                                                                        | 50 |

| Table 23. | General operating conditions                                                                   | 51 |

| Table 24. | Operating conditions at power-up / power-down                                                  | 52 |

| Table 25. | Embedded internal reference voltage                                                            |    |

| Table 26. | Typical and maximum current consumption from $V_{DD}$ supply at $V_{DD} = 1.8 \text{ V} \dots$ | 53 |

| Table 27. | Typical and maximum current consumption from the V <sub>DDA</sub> supply                       |    |

| Table 28. | Typical and maximum current consumption from the V <sub>BAT</sub> supply                       |    |

| Table 29. | Typical current consumption, code executing from Flash memory,                                 |    |

|           | running from HSE 8 MHz crystal                                                                 | 56 |

| Table 30. | Typical and maximum consumption in Stop mode                                                   | 57 |

| Table 31. | Switching output I/O current consumption                                                       | 58 |

| Table 32. | Peripheral current consumption                                                                 |    |

| Table 33. | Low-power mode wakeup timings                                                                  | 61 |

| Table 34. | High-speed external user clock characteristics                                                 | 61 |

| Table 35. | Low-speed external user clock characteristics                                                  |    |

| Table 36. | HSE oscillator characteristics                                                                 | 63 |

| Table 37. | LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz)                                 | 64 |

| Table 38. | HSI oscillator characteristics                                                                 |    |

| Table 39. | HSI14 oscillator characteristics                                                               | 67 |

| Table 40. | HSI48 oscillator characteristics                                                               | 68 |

| Table 41. | LSI oscillator characteristics                                                                 | 69 |

| Table 42. | PLL characteristics                                                                            | 69 |

| Table 43. | Flash memory characteristics                                                                   | 69 |

| Table 44. | Flash memory endurance and data retention                                                      |    |

| Table 45. | EMS characteristics                                                                            |    |

| Table 46. | EMI characteristics                                                                            |    |

### Stop mode

Stop mode achieves very low power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled.

The device can be woken up from Stop mode by any of the EXTI lines. The EXTI line source can be one of the 16 external lines, RTC, I2C1, USART1, USART2, USB, COMPx,  $V_{DDIO2}$  supply comparator or the CEC.

The CEC, USART1, USART2 and I2C1 peripherals can be configured to enable the HSI RC oscillator so as to get clock for processing incoming data.

Note:

The RTC, the IWDG, and the corresponding clock sources are not stopped by entering Stop mode.

# 3.6 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-32 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example on failure of an indirectly used external crystal, resonator or oscillator).

Several prescalers allow the application to configure the frequency of the AHB and the APB domains. The maximum frequency of the AHB and the APB domains is 48 MHz.

Additionally, also the internal RC 48 MHz oscillator can be selected for system clock or PLL input source. This oscillator can be automatically fine-trimmed by the means of the CRS peripheral using the external synchronization.

sensor, voltage reference, VBAT voltage measurement) channels and performs conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

## 3.10.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $V_{\text{SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

| Calibration value name | Description                                                                                      | Memory address            |

|------------------------|--------------------------------------------------------------------------------------------------|---------------------------|

| TS_CAL1                | TS ADC raw data acquired at a temperature of 30 °C (± 5 °C), V <sub>DDA</sub> = 3.3 V (± 10 mV)  | 0x1FFF F7B8 - 0x1FFF F7B9 |

| TS_CAL2                | TS ADC raw data acquired at a temperature of 110 °C (± 5 °C), V <sub>DDA</sub> = 3.3 V (± 10 mV) | 0x1FFF F7C2 - 0x1FFF F7C3 |

Table 2. Temperature sensor calibration values

# 3.10.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

Table 3. Internal voltage reference calibration values

| Calibration value name | Description                                                                              | Memory address            |  |  |

|------------------------|------------------------------------------------------------------------------------------|---------------------------|--|--|

|                        | Raw data acquired at a temperature of 30 °C (± 5 °C), V <sub>DDA</sub> = 3.3 V (± 10 mV) | 0x1FFF F7BA - 0x1FFF F7BB |  |  |

TIM15 can be synchronized with TIM16 and TIM17.

TIM15, TIM16 and TIM17 have a complementary output with dead-time generation and independent DMA request generation.

Their counters can be frozen in debug mode.

### 3.14.3 Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger generation. They can also be used as generic 16-bit time bases.

### 3.14.4 Independent watchdog (IWDG)

The independent watchdog is based on an 8-bit prescaler and 12-bit downcounter with user-defined refresh window. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop mode. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

### 3.14.5 System window watchdog (WWDG)

The system window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the APB clock (PCLK). It has an early warning interrupt capability and the counter can be frozen in debug mode.

## 3.14.6 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard down counter. It features:

- a 24-bit down counter

- autoreload capability

- maskable system interrupt generation when the counter reaches 0

- programmable clock source (HCLK or HCLK/8)

# 3.15 Real-time clock (RTC) and backup registers

The RTC and the five backup registers are supplied through a switch that takes power either on  $V_{DD}$  supply when present or through the  $V_{BAT}$  pin. The backup registers are five 32-bit registers used to store 20 bytes of user application data when  $V_{DD}$  power is not present. They are not reset by a system or power reset.

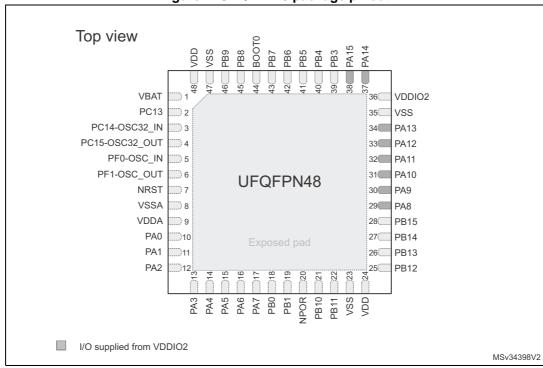

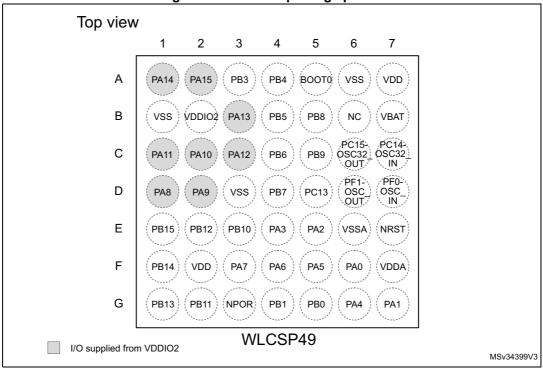

Figure 7. UFQFPN48 package pinout

<sup>1.</sup> The above figure shows the package in top view, changing from bottom view in the previous document versions

Table 12. STM32F078CB/RB/VB pin definitions (continued)

|          | Pin     | numb   | oers            |         |                                      |             |               |            | Pin functions                                            |                                                              |  |

|----------|---------|--------|-----------------|---------|--------------------------------------|-------------|---------------|------------|----------------------------------------------------------|--------------------------------------------------------------|--|

| UFBGA100 | LQFP100 | LQFP64 | LQFP48/UFQFPN48 | WLCSP49 | Pin name<br>(function upon<br>reset) | Pin<br>type | I/O structure | Notes      | Alternate functions                                      | Additional<br>functions                                      |  |

| C1       | 7       | 2      | 2               | D5      | PC13                                 | I/O         | TC            | (1)<br>(2) | -                                                        | WKUP2,<br>RTC_TAMP1,<br>RTC_TS,<br>RTC_OUT                   |  |

| D1       | 8       | 3      | 3               | C7      | PC14-OSC32_IN<br>(PC14)              | I/O         | тс            | (1)<br>(2) | -                                                        | OSC32_IN                                                     |  |

| E1       | 9       | 4      | 4               | C6      | PC15-<br>OSC32_OUT<br>(PC15)         | I/O         | тс            | (1)<br>(2) | -                                                        | OSC32_OUT                                                    |  |

| F2       | 10      | -      | -               | -       | PF9                                  | I/O         | FT            | -          | TIM15_CH1                                                | -                                                            |  |

| G2       | 11      | ı      | -               | -       | PF10                                 | I/O         | FT            | -          | TIM15_CH2                                                | -                                                            |  |

| F1       | 12      | 5      | 5               | D7      | PF0-OSC_IN<br>(PF0)                  | I/O         | FT            | ı          | CRS_SYNC                                                 | OSC_IN                                                       |  |

| G1       | 13      | 6      | 6               | D6      | PF1-OSC_OUT<br>(PF1)                 | I/O         | FT            | -          | -                                                        | OSC_OUT                                                      |  |

| H2       | 14      | 7      | 7               | E7      | NRST                                 | I/O         | RST           | -          | Device reset input / interi<br>(active low)              | •                                                            |  |

| H1       | 15      | 8      | -               | -       | PC0                                  | I/O         | TTa           | -          | EVENTOUT                                                 | ADC_IN10                                                     |  |

| J2       | 16      | 9      | -               | -       | PC1                                  | I/O         | TTa           | ı          | EVENTOUT                                                 | ADC_IN11                                                     |  |

| J3       | 17      | 10     | -               | -       | PC2                                  | I/O         | ТТа           | ı          | SPI2_MISO, I2S2_MCK,<br>EVENTOUT                         | ADC_IN12                                                     |  |

| K2       | 18      | 11     | -               | -       | PC3                                  | I/O         | TTa           | -          | SPI2_MOSI, I2S2_SD,<br>EVENTOUT                          | ADC_IN13                                                     |  |

| J1       | 19      | -      | -               | -       | PF2                                  | I/O         | FT            | -          | EVENTOUT                                                 | WKUP8                                                        |  |

| K1       | 20      | 12     | 8               | E6      | VSSA                                 | S           | -             | ı          | Analog groui                                             | nd                                                           |  |

| M1       | 21      | 13     | 9               | F7      | VDDA                                 | S           | -             | -          | Analog power supply                                      |                                                              |  |

| L1       | 22      | -      | -               | -       | PF3                                  | I/O         | FT            | -          | EVENTOUT                                                 |                                                              |  |

| L2       | 23      | 14     | 10              | F6      | PA0                                  | I/O         | ТТа           | -          | USART2_CTS,<br>TIM2_CH1_ETR,<br>TSC_G1_IO1,<br>USART4_TX | RTC_TAMP2,<br>WKUP1,<br>COMP1_OUT,<br>ADC_IN0,<br>COMP1_INM6 |  |

Table 12. STM32F078CB/RB/VB pin definitions (continued)

|          | Pin     | numb   | ers             |         |                                      |             |               |       | Pin functions                                                         |                         |  |

|----------|---------|--------|-----------------|---------|--------------------------------------|-------------|---------------|-------|-----------------------------------------------------------------------|-------------------------|--|

| UFBGA100 | LQFP100 | LQFP64 | LQFP48/UFQFPN48 | WLCSP49 | Pin name<br>(function upon<br>reset) | Pin<br>type | I/O structure | Notes | Alternate functions                                                   | Additional<br>functions |  |

| A7       | 90      | 56     | 40              | A4      | PB4                                  | I/O         | FT            | -     | SPI1_MISO, I2S1_MCK,<br>TIM17_BKIN, TIM3_CH1,<br>TSC_G5_IO2, EVENTOUT | -                       |  |

| C5       | 91      | 57     | 41              | B4      | PB5                                  | I/O         | FT            | -     | SPI1_MOSI, I2S1_SD,<br>I2C1_SMBA, TIM16_BKIN,<br>TIM3_CH2             | WKUP6                   |  |

| B5       | 92      | 58     | 42              | C4      | PB6                                  | I/O         | FTf           | -     | I2C1_SCL, USART1_TX,<br>TIM16_CH1N,<br>TSC_G5_I03                     | -                       |  |

| B4       | 93      | 59     | 43              | D4      | PB7                                  | I/O         | FTf           | -     | I2C1_SDA, USART1_RX,<br>USART4_CTS,<br>TIM17_CH1N,<br>TSC_G5_IO4      | -                       |  |

| A4       | 94      | 60     | 44              | A5      | воото                                | I           | В             | -     | Boot memory sel                                                       | ection                  |  |

| A3       | 95      | 61     | 45              | B5      | PB8                                  | I/O         | FTf           | -     | I2C1_SCL, CEC,<br>TIM16_CH1, TSC_SYNC                                 | -                       |  |

| В3       | 96      | 62     | 46              | C5      | PB9                                  | I/O         | FTf           | -     | SPI2_NSS, I2S2_WS,<br>I2C1_SDA, IR_OUT,<br>TIM17_CH1, EVENTOUT        | -                       |  |

| СЗ       | 97      | -      | -               | -       | PE0                                  | I/O         | FT            | -     | EVENTOUT, TIM16_CH1                                                   | -                       |  |

| A2       | 98      | 1      | -               | -       | PE1                                  | I/O         | FT            | -     | EVENTOUT, TIM17_CH1                                                   | -                       |  |

| D3       | 99      | 63     | 47              | A6      | VSS                                  | S           | -             | -     | Ground                                                                |                         |  |

| C4       | 100     | 64     | 48              | A7      | VDD                                  | S           | -             | -     | Digital power su                                                      | ıpply                   |  |

PC13, PC14 and PC15 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 in output mode is limited:

The speed should not exceed 2 MHz with a maximum load of 30 pF.

DocID026006 Rev 4 38/120

<sup>-</sup> These GPIOs must not be used as current sources (e.g. to drive an LED).

<sup>2.</sup> After the first RTC domain power-up, PC13, PC14 and PC15 operate as GPIOs. Their function then depends on the content of the RTC registers which are not reset by the system reset. For details on how to manage these GPIOs, refer to the RTC domain and RTC register descriptions in the reference manual.

<sup>3.</sup> This pin is supplied by  $V_{DDA}$ .

<sup>4.</sup> PC6, PC7, PC8, PC9, PA8, PA9, PA10, PA11, PA12, PA13, PF6, PA14, PA15, PC10, PC11, PC12, PD0, PD1 and PD2 I/Os

<sup>5.</sup> After reset, these pins are configured as SWDIO and SWCLK alternate functions, and the internal pull-up on the SWDIO pin and the internal pull-down on the SWCLK pin are activated.

Table 15. Alternate functions selected through GPIOC\_AFR registers for port C

| Pin name | AF0        | AF1                 |

|----------|------------|---------------------|

| PC0      | EVENTOUT   | -                   |

| PC1      | EVENTOUT   | -                   |

| PC2      | EVENTOUT   | SPI2_MISO, I2S2_MCK |

| PC3      | EVENTOUT   | SPI2_MOSI, I2S2_SD  |

| PC4      | EVENTOUT   | USART3_TX           |

| PC5      | TSC_G3_IO1 | USART3_RX           |

| PC6      | TIM3_CH1   | -                   |

| PC7      | TIM3_CH2   | -                   |

| PC8      | TIM3_CH3   | -                   |

| PC9      | TIM3_CH4   | -                   |

| PC10     | USART4_TX  | USART3_TX           |

| PC11     | USART4_RX  | USART3_RX           |

| PC12     | USART4_CK  | USART3_CK           |

| PC13     | -          | -                   |

| PC14     | -          | -                   |

| PC15     | -          | -                   |

Table 16. Alternate functions selected through GPIOD\_AFR registers for port D

| Pin name | AF0        | AF1                 |

|----------|------------|---------------------|

| PD0      | -          | SPI2_NSS, I2S2_WS   |

| PD1      | -          | SPI2_SCK, I2S2_CK   |

| PD2      | TIM3_ETR   | USART3_RTS          |

| PD3      | USART2_CTS | SPI2_MISO, I2S2_MCK |

| PD4      | USART2_RTS | SPI2_MOSI, I2S2_SD  |

| PD5      | USART2_TX  | -                   |

| PD6      | USART2_RX  | -                   |

| PD7      | USART2_CK  | -                   |

| PD8      | USART3_TX  | -                   |

| PD9      | USART3_RX  | -                   |

| PD10     | USART3_CK  | -                   |

| PD11     | USART3_CTS | -                   |

| PD12     | USART3_RTS | TSC_G8_IO1          |

| PD13     | -          | TSC_G8_IO2          |

| PD14     | -          | TSC_G8_IO3          |

| PD15     | CRS_SYNC   | TSC_G8_IO4          |

Table 19. STM32F078CB/RB/VB peripheral register boundary addresses (continued)

| Bus | Boundary address          | Size | Peripheral |

|-----|---------------------------|------|------------|

|     | 0x4000 7C00 - 0x4000 7FFF | 1 KB | Reserved   |

|     | 0x4000 7800 - 0x4000 7BFF | 1 KB | CEC        |

|     | 0x4000 7400 - 0x4000 77FF | 1 KB | DAC        |

|     | 0x4000 7000 - 0x4000 73FF | 1 KB | PWR        |

|     | 0x4000 6C00 - 0x4000 6FFF | 1 KB | CRS        |

|     | 0x4000 6400 - 0x4000 6BFF | 2 KB | Reserved   |

|     | 0x4000 6000 - 0x4000 63FF | 1 KB | USB RAM    |

|     | 0x4000 5C00 - 0x4000 5FFF | 1 KB | USB        |

|     | 0x4000 5800 - 0x4000 5BFF | 1 KB | I2C2       |

|     | 0x4000 5400 - 0x4000 57FF | 1 KB | I2C1       |

|     | 0x4000 5000 - 0x4000 53FF | 1 KB | Reserved   |

|     | 0x4000 4C00 - 0x4000 4FFF | 1 KB | USART4     |

|     | 0x4000 4800 - 0x4000 4BFF | 1 KB | USART3     |

|     | 0x4000 4400 - 0x4000 47FF | 1 KB | USART2     |

|     | 0x4000 3C00 - 0x4000 43FF | 2 KB | Reserved   |

|     | 0x4000 3800 - 0x4000 3BFF | 1 KB | SPI2       |

|     | 0x4000 3400 - 0x4000 37FF | 1 KB | Reserved   |

| APB | 0x4000 3000 - 0x4000 33FF | 1 KB | IWDG       |

|     | 0x4000 2C00 - 0x4000 2FFF | 1 KB | WWDG       |

|     | 0x4000 2800 - 0x4000 2BFF | 1 KB | RTC        |

|     | 0x4000 2400 - 0x4000 27FF | 1 KB | Reserved   |

|     | 0x4000 2000 - 0x4000 23FF | 1 KB | TIM14      |

|     | 0x4000 1800 - 0x4000 1FFF | 2 KB | Reserved   |

|     | 0x4000 1400 - 0x4000 17FF | 1 KB | TIM7       |

|     | 0x4000 1000 - 0x4000 13FF | 1 KB | TIM6       |

|     | 0x4000 0800 - 0x4000 0FFF | 2 KB | Reserved   |

|     | 0x4000 0400 - 0x4000 07FF | 1 KB | TIM3       |

|     | 0x4000 0000 - 0x4000 03FF | 1 KB | TIM2       |

# 6.1.7 Current consumption measurement

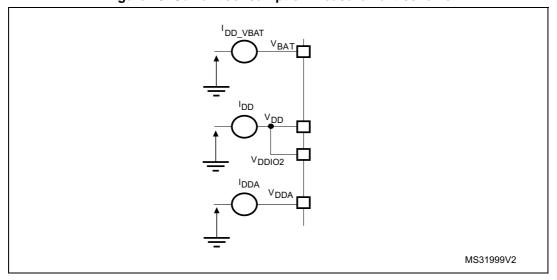

Figure 13. Current consumption measurement scheme

### Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in analog input mode

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time is adjusted to the f<sub>HCLK</sub> frequency:

- 0 wait state and Prefetch OFF from 0 to 24 MHz

- 1 wait state and Prefetch ON above 24 MHz

- When the peripherals are enabled f<sub>PCLK</sub> = f<sub>HCLK</sub>

The parameters given in *Table 26* to *Table 30* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 23: General operating conditions*.

Table 26. Typical and maximum current consumption from  $V_{DD}$  supply at  $V_{DD} = 1.8 \text{ V}$

| _   _           |                                        |                        |            | All        | peripher   | als enab   | led <sup>(1)</sup> | All        | periphe           | rals disa | abled  |                      |     |  |                                     |  |      |

|-----------------|----------------------------------------|------------------------|------------|------------|------------|------------|--------------------|------------|-------------------|-----------|--------|----------------------|-----|--|-------------------------------------|--|------|

| Symbol          | Parameter                              | Conditions             | Conditions | Conditions | Conditions | Conditions | Conditions         | Conditions | f <sub>HCLK</sub> |           | N      | lax @ T <sub>A</sub> | (2) |  | Max @ T <sub>A</sub> <sup>(2)</sup> |  | Unit |

| S               | Par                                    |                        |            | Тур        | 25 °C      | 85 °C      | 105 °C             | Тур        | 25 °C             | 85 °C     | 105 °C |                      |     |  |                                     |  |      |

|                 |                                        | HSI48                  | 48 MHz     | 23.0       | 24.8       | 25.8       | 26.7               | 12.9       | 13.7              | 14.1      | 15.3   |                      |     |  |                                     |  |      |

|                 | lony                                   |                        | 48 MHz     | 22.9       | 24.6       | 25.7       | 26.6               | 12.8       | 13.6              | 13.9      | 15.2   |                      |     |  |                                     |  |      |

|                 | Run mode,<br>Flash memory              | HSE bypass,<br>PLL on  | 32 MHz     | 15.5       | 16.6       | 17.2       | 19.1               | 8.7        | 9.2               | 9.4       | 10.0   |                      |     |  |                                     |  |      |

|                 | ın m<br>ash ı                          |                        | 24 MHz     | 12.0       | 12.8       | 13.2       | 14.3               | 6.8        | 7.2               | 7.3       | 7.7    |                      |     |  |                                     |  |      |

|                 |                                        | HSE bypass,<br>PLL off | 8 MHz      | 4.2        | 4.4        | 4.5        | 4.6                | 2.4        | 2.6               | 2.6       | 2.7    |                      |     |  |                                     |  |      |

| I <sub>DD</sub> | current in                             |                        | 1 MHz      | 0.7        | 0.9        | 1.0        | 1.1                | 0.5        | 0.6               | 0.7       | 0.7    | mA                   |     |  |                                     |  |      |

|                 | curr                                   |                        | 48 MHz     | 22.9       | 24.6       | 25.7       | 27.6               | 12.8       | 13.6              | 13.9      | 15.2   |                      |     |  |                                     |  |      |

|                 | Supply current in<br>le executing from | HSI clock,<br>PLL on   | 32 MHz     | 15.5       | 16.6       | 17.2       | 19.1               | 8.7        | 9.2               | 9.4       | 10.0   |                      |     |  |                                     |  |      |

| l Su            | Su<br>code e                           |                        | 24 MHz     | 12.0       | 12.8       | 13.2       | 14.3               | 6.8        | 7.2               | 7.3       | 7.7    |                      |     |  |                                     |  |      |

|                 | 8                                      | HSI clock,<br>PLL off  | 8 MHz      | 4.2        | 4.4        | 4.5        | 4.6                | 2.4        | 2.6               | 2.6       | 2.7    |                      |     |  |                                     |  |      |

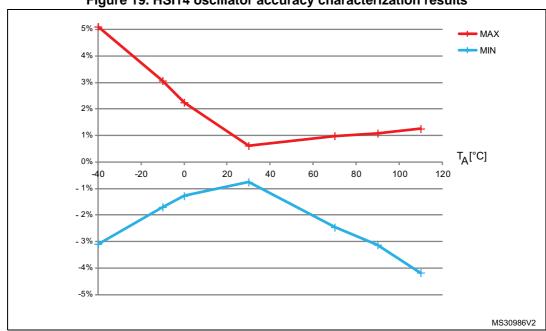

# High-speed internal 14 MHz (HSI14) RC oscillator (dedicated to ADC)

Table 39. HSI14 oscillator characteristics<sup>(1)</sup>

| Symbol                  | Parameter                                             | Conditions                                   | Min                 | Тур | Max                | Unit |

|-------------------------|-------------------------------------------------------|----------------------------------------------|---------------------|-----|--------------------|------|

| f <sub>HSI14</sub>      | Frequency                                             | -                                            | -                   | 14  | -                  | MHz  |

| TRIM                    | HSI14 user-trimming step                              | -                                            | -                   | -   | 1 <sup>(2)</sup>   | %    |

| DuCy <sub>(HSI14)</sub> | Duty cycle                                            | -                                            | 45 <sup>(2)</sup>   | -   | 55 <sup>(2)</sup>  | %    |

|                         |                                                       | $T_A = -40 \text{ to } 105 ^{\circ}\text{C}$ | -4.2 <sup>(3)</sup> | -   | 5.1 <sup>(3)</sup> | %    |

| ACC                     | Accuracy of the HSI14 oscillator (factory calibrated) | T <sub>A</sub> = -10 to 85 °C                | $-3.2^{(3)}$        | -   | 3.1 <sup>(3)</sup> | %    |

| ACC <sub>HSI14</sub>    |                                                       | T <sub>A</sub> = 0 to 70 °C                  | -2.5 <sup>(3)</sup> | -   | 2.3 <sup>(3)</sup> | %    |

|                         |                                                       | T <sub>A</sub> = 25 °C                       | -1                  | -   | 1                  | %    |

| t <sub>su(HSI14)</sub>  | HSI14 oscillator startup time                         | -                                            | 1 <sup>(2)</sup>    | -   | 2 <sup>(2)</sup>   | μs   |

| I <sub>DDA(HSI14)</sub> | HSI14 oscillator power consumption                    | -                                            | -                   | 100 | 150 <sup>(2)</sup> | μΑ   |

- 1.  $V_{DDA}$  = 3.3 V,  $T_{A}$  = -40 to 105 °C unless otherwise specified.

- 2. Guaranteed by design, not tested in production.

- 3. Data based on characterization results, not tested in production.

Figure 19. HSI14 oscillator accuracy characterization results

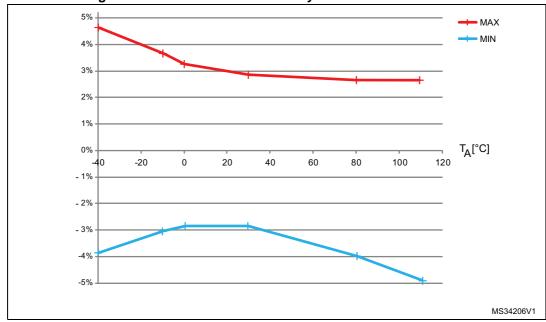

## High-speed internal 48 MHz (HSI48) RC oscillator

Table 40. HSI48 oscillator characteristics<sup>(1)</sup>

| Symbol                  | Parameter                                             | Conditions                                   | Min                 | Тур  | Max                | Unit |

|-------------------------|-------------------------------------------------------|----------------------------------------------|---------------------|------|--------------------|------|

| f <sub>HSI48</sub>      | Frequency                                             | -                                            | -                   | 48   | -                  | MHz  |

| TRIM                    | HSI48 user-trimming step                              | -                                            | 0.09 <sup>(2)</sup> | 0.14 | 0.2 <sup>(2)</sup> | %    |

| DuCy <sub>(HSI48)</sub> | Duty cycle                                            | -                                            | 45 <sup>(2)</sup>   | -    | 55 <sup>(2)</sup>  | %    |

|                         |                                                       | $T_A = -40 \text{ to } 105 ^{\circ}\text{C}$ | -4.9 <sup>(3)</sup> | -    | 4.7 <sup>(3)</sup> | %    |

| ACC                     | Accuracy of the HSI48 oscillator (factory calibrated) | $T_A = -10 \text{ to } 85 ^{\circ}\text{C}$  | -4.1 <sup>(3)</sup> | -    | 3.7 <sup>(3)</sup> | %    |

| ACC <sub>HSI48</sub>    |                                                       | T <sub>A</sub> = 0 to 70 °C                  | -3.8 <sup>(3)</sup> | -    | 3.4 <sup>(3)</sup> | %    |

|                         |                                                       | T <sub>A</sub> = 25 °C                       | -2.8                | -    | 2.9                | %    |

| t <sub>su(HSI48)</sub>  | HSI48 oscillator startup time                         | -                                            | -                   | -    | 6 <sup>(2)</sup>   | μs   |

| I <sub>DDA(HSI48)</sub> | HSI48 oscillator power consumption                    | -                                            | -                   | 312  | 350 <sup>(2)</sup> | μА   |

- 1.  $V_{DDA}$  = 3.3 V,  $T_{A}$  = -40 to 105 °C unless otherwise specified.

- 2. Guaranteed by design, not tested in production.

- 3. Data based on characterization results, not tested in production.

Figure 20. HSI48 oscillator accuracy characterization results

| Symbol                | Ratings                                            | Conditions                                         | Packages   | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|----------------------------------------------------|----------------------------------------------------|------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model) | T <sub>A</sub> = +25 °C, conforming to JESD22-A114 | All        | 2     | 2000                            | ٧    |

| V                     | Electrostatic discharge voltage                    | T <sub>A</sub> = +25 °C, conforming                | WLCSP49    | C3    | 250                             | V    |

| V <sub>ESD(CDM)</sub> | (charge device model)                              | to ANSI/ESD STM5.3.1                               | All others | C4    | 500                             | V    |

Table 47. ESD absolute maximum ratings

### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin.

- A current injection is applied to each input, output and configurable I/O pin.

These tests are compliant with EIA/JESD 78A IC latch-up standard.

Table 48. Electrical sensitivities

|   | Symbol | Parameter             | Conditions                                     | Class      |

|---|--------|-----------------------|------------------------------------------------|------------|

| i | LU     | Static latch-up class | T <sub>A</sub> = +105 °C conforming to JESD78A | II level A |

### 6.3.12 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DDIOx}$  (for standard, 3.3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of the -5  $\mu$ A/+0  $\mu$ A range) or other functional failure (for example reset occurrence or oscillator frequency deviation).

The characterization results are given in *Table 49*.

Negative induced leakage current is caused by negative injection and positive induced leakage current is caused by positive injection.

<sup>1.</sup> Data based on characterization results, not tested in production.

### 6.3.18 Temperature sensor characteristics

Table 60. TS characteristics

| Symbol                             | Parameter                                     | Min  | Тур  | Max  | Unit  |

|------------------------------------|-----------------------------------------------|------|------|------|-------|

| T <sub>L</sub> <sup>(1)</sup>      | V <sub>SENSE</sub> linearity with temperature | -    | ± 1  | ± 2  | °C    |

| Avg_Slope <sup>(1)</sup>           | Average slope                                 | 4.0  | 4.3  | 4.6  | mV/°C |

| V <sub>30</sub>                    | Voltage at 30 °C (± 5 °C) <sup>(2)</sup>      | 1.34 | 1.43 | 1.52 | V     |

| t <sub>START</sub> (1)             | ADC_IN16 buffer startup time                  | -    | -    | 10   | μs    |

| t <sub>S_temp</sub> <sup>(1)</sup> | ADC compling time when reading the            |      | -    | -    | μs    |

<sup>1.</sup> Guaranteed by design, not tested in production.

# 6.3.19 V<sub>BAT</sub> monitoring characteristics

Table 61. V<sub>BAT</sub> monitoring characteristics

| Symbol                             | Parameter                                           |    | Тур    | Max | Unit |

|------------------------------------|-----------------------------------------------------|----|--------|-----|------|

| R                                  | Resistor bridge for V <sub>BAT</sub>                | -  | 2 x 50 | -   | kΩ   |

| Q                                  | Ratio on V <sub>BAT</sub> measurement               |    | 2      | -   | -    |

| Er <sup>(1)</sup>                  | Error on Q                                          | -1 | -      | +1  | %    |

| t <sub>S_vbat</sub> <sup>(1)</sup> | ADC sampling time when reading the V <sub>BAT</sub> | 4  | -      | -   | μs   |

<sup>1.</sup> Guaranteed by design, not tested in production.

### 6.3.20 Timer characteristics

The parameters given in the following tables are guaranteed by design.

Refer to Section 6.3.13: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

**Table 62. TIMx characteristics**

| Symbol                 | Parameter                                                  | Conditions                    | Min | Тур                     | Max | Unit                 |

|------------------------|------------------------------------------------------------|-------------------------------|-----|-------------------------|-----|----------------------|

| t =                    | Timer resolution time                                      | -                             | -   | 1                       | -   | t <sub>TIMxCLK</sub> |

| <sup>t</sup> res(TIM)  | Timer resolution time                                      | f <sub>TIMxCLK</sub> = 48 MHz | -   | 20.8                    | ı   | ns                   |

| f                      | Timer external clock<br>frequency on CH1 to<br>CH4         | -                             | -   | f <sub>TIMxCLK</sub> /2 | -   | MHz                  |

| f <sub>EXT</sub>       |                                                            | f <sub>TIMxCLK</sub> = 48 MHz | -   | 24                      | -   | MHz                  |

|                        | 16-bit timer maximum period  32-bit counter maximum period | -                             | ı   | 2 <sup>16</sup>         | ı   | t <sub>TIMxCLK</sub> |

| t <sub>MAX_COUNT</sub> |                                                            | f <sub>TIMxCLK</sub> = 48 MHz | -   | 1365                    | ı   | μs                   |

|                        |                                                            | -                             | -   | 2 <sup>32</sup>         | -   | t <sub>TIMxCLK</sub> |

|                        |                                                            | f <sub>TIMxCLK</sub> = 48 MHz | -   | 89.48                   | -   | s                    |

Measured at V<sub>DDA</sub> = 3.3 V ± 10 mV. The V<sub>30</sub> ADC conversion result is stored in the TS\_CAL1 byte. Refer to Table 2: Temperature sensor calibration values.

Table 65. I<sup>2</sup>C analog filter characteristics<sup>(1)</sup>

| Symbol          | Parameter                                                        | Min               | Max                | Unit |

|-----------------|------------------------------------------------------------------|-------------------|--------------------|------|

| t <sub>AF</sub> | Maximum width of spikes that are suppressed by the analog filter | 50 <sup>(2)</sup> | 260 <sup>(3)</sup> | ns   |

- 1. Guaranteed by design, not tested in production.

- 2. Spikes with widths below t<sub>AF(min)</sub> are filtered.

- 3. Spikes with widths above  $t_{\text{AF}(\text{max})}$  are not filtered

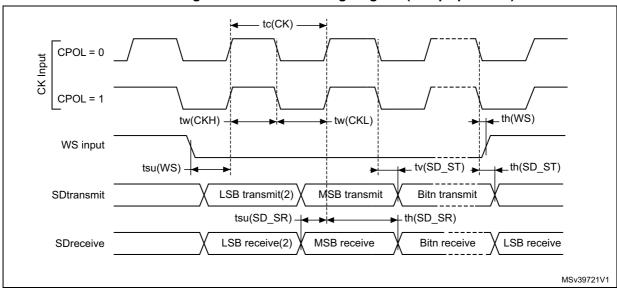

## SPI/I<sup>2</sup>S characteristics

Unless otherwise specified, the parameters given in *Table 66* for SPI or in *Table 67* for I<sup>2</sup>S are derived from tests performed under the ambient temperature, f<sub>PCLKx</sub> frequency and supply voltage conditions summarized in *Table 23: General operating conditions*.

Refer to Section 6.3.13: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI and WS, CK, SD for I<sup>2</sup>S).

Table 66. SPI characteristics<sup>(1)</sup>

| Symbol                                       | Parameter                        | Conditions                                            | Min         | Max         | Unit    |

|----------------------------------------------|----------------------------------|-------------------------------------------------------|-------------|-------------|---------|

| f <sub>SCK</sub>                             | SPI clock frequency              | Master mode                                           | -           | 18          | MHz     |

| 1/t <sub>c(SCK)</sub>                        | SFI Clock frequency              | Slave mode                                            | -           | 18          | IVII IZ |

| t <sub>r(SCK)</sub>                          | SPI clock rise and fall time     | Capacitive load: C = 15 pF                            | -           | 6           | ns      |

| t <sub>su(NSS)</sub>                         | NSS setup time                   | Slave mode                                            | 4Tpclk      | -           |         |

| t <sub>h(NSS)</sub>                          | NSS hold time                    | Slave mode                                            | 2Tpclk + 10 | -           |         |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time            | Master mode, f <sub>PCLK</sub> = 36 MHz,<br>presc = 4 | Tpclk/2 -2  | Tpclk/2 + 1 |         |

| t <sub>su(MI)</sub>                          | Data input setup time            | Master mode                                           | 4           | -           |         |

| t <sub>su(SI)</sub>                          |                                  | Slave mode                                            | 5           | -           |         |

| t <sub>h(MI)</sub>                           | Data input hold time             | Master mode                                           | 4           | -           |         |

| t <sub>h(SI)</sub>                           | Data iriput riolu tirrie         | Slave mode                                            | 5           | -           | ns      |

| t <sub>a(SO)</sub> <sup>(2)</sup>            | Data output access time          | Slave mode, f <sub>PCLK</sub> = 20 MHz                | 0           | 3Tpclk      |         |

| t <sub>dis(SO)</sub> (3)                     | Data output disable time         | Slave mode                                            | 0           | 18          |         |

| t <sub>v(SO)</sub>                           | Data output valid time           | Slave mode (after enable edge)                        | -           | 22.5        |         |

| t <sub>v(MO)</sub>                           | Data output valid time           | Master mode (after enable edge)                       | -           | 6           |         |

| t <sub>h(SO)</sub>                           | Data output hold time            | Slave mode (after enable edge)                        | 11.5        | -           |         |

| t <sub>h(MO)</sub>                           | Data output noid time            | Master mode (after enable edge)                       | 2           | -           |         |

| DuCy(SCK)                                    | SPI slave input clock duty cycle | Slave mode                                            | 25          | 75          | %       |

- 1. Data based on characterization results, not tested in production.

- 2. Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

- 3. Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z

**Conditions Symbol Parameter** Min Max Unit Master receiver 6 t<sub>su(SD\_MR)</sub> Data input setup time 2  $t_{su(SD\_SR)}$ Slave receiver  $t_{h(SD\_MR)}^{(2)}$ 4 Master receiver Data input hold time  $t_{h(SD\ SR)}^{(2)}$ Slave receiver 0.5 ns  $t_{v(SD\_MT)}^{(2)}$ 4 Master transmitter Data output valid time Slave transmitter 31 Master transmitter 0  $t_{h(SD\_MT)}$ Data output hold time Slave transmitter 13  $t_{h(SD\_ST)}$

Table 67. I<sup>2</sup>S characteristics<sup>(1)</sup> (continued)

- 1. Data based on design simulation and/or characterization results, not tested in production.

- 2. Depends on  $f_{PCLK}$ . For example, if  $f_{PCLK}$  = 8 MHz, then  $T_{PCLK}$  = 1/ $f_{PLCLK}$  = 125 ns.

Figure 32. I<sup>2</sup>S slave timing diagram (Philips protocol)

- 1. Measurement points are done at CMOS levels: 0.3 ×  $V_{DDIOX}$  and 0.7 ×  $V_{DDIOX}$ .

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

#### **USB** characteristics

The STM32F078CB/RB/VB USB interface is fully compliant with the USB specification version 2.0 and is USB-IF certified (for Full-speed device operation).

Table 68. USB electrical characteristics

| Symbol                                                                 | Parameter                                      | Conditions           | Min.               | Тур  | Max. | Unit |

|------------------------------------------------------------------------|------------------------------------------------|----------------------|--------------------|------|------|------|

| V <sub>DDIO2</sub>                                                     | USB transceiver operating voltage              | -                    | 3.0 <sup>(1)</sup> | -    | 3.6  | V    |

| t <sub>STARTUP</sub> (2)                                               | USB transceiver startup time                   | -                    | -                  | -    | 1.0  | μs   |

| R <sub>PUI</sub>                                                       | Embedded USB_DP pull-up value during idle      | -                    | 1.1                | 1.26 | 1.5  | kΩ   |

| R <sub>PUR</sub>                                                       | Embedded USB_DP pull-up value during reception | -                    | 2.0                | 2.26 | 2.6  | K12  |

| Z <sub>DRV</sub> <sup>(2)</sup> Output driver impedance <sup>(3)</sup> |                                                | Driving high and low | 28                 | 40   | 44   | Ω    |

<sup>1.</sup> The STM32F078CB/RB/VB USB functionality is ensured down to 2.7 V but not the full USB electrical characteristics which are degraded in the 2.7-to-3.0 V voltage range.

<sup>2.</sup> Guaranteed by design, not tested in production.

<sup>3.</sup> No external termination series resistors are required on USB\_DP (D+) and USB\_DM (D-); the matching impedance is already included in the embedded driver.

Table 75. UFQFPN48 package mechanical data

| Symbol | millimeters |       |       |        | inches <sup>(1)</sup> |        |

|--------|-------------|-------|-------|--------|-----------------------|--------|

| Cymbol | Min         | Тур   | Max   | Min    | Тур                   | Max    |

| А      | 0.500       | 0.550 | 0.600 | 0.0197 | 0.0217                | 0.0236 |

| A1     | 0.000       | 0.020 | 0.050 | 0.0000 | 0.0008                | 0.0020 |

| D      | 6.900       | 7.000 | 7.100 | 0.2717 | 0.2756                | 0.2795 |

| Е      | 6.900       | 7.000 | 7.100 | 0.2717 | 0.2756                | 0.2795 |

| D2     | 5.500       | 5.600 | 5.700 | 0.2165 | 0.2205                | 0.2244 |

| E2     | 5.500       | 5.600 | 5.700 | 0.2165 | 0.2205                | 0.2244 |

| L      | 0.300       | 0.400 | 0.500 | 0.0118 | 0.0157                | 0.0197 |

| Т      | -           | 0.152 | -     | -      | 0.0060                | -      |

| b      | 0.200       | 0.250 | 0.300 | 0.0079 | 0.0098                | 0.0118 |

| е      | -           | 0.500 | -     | -      | 0.0197                | -      |

| ddd    | -           | -     | 0.080 | -      | -                     | 0.0031 |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

116/120

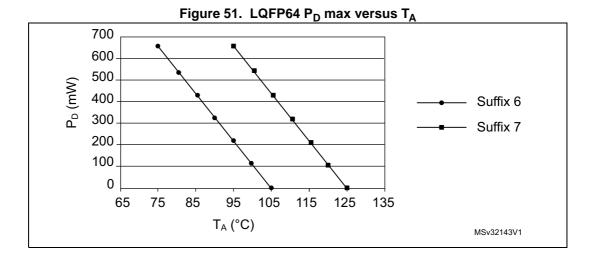

This is above the range of the suffix 6 version parts ( $-40 < T_J < 105$  °C).

In this case, parts must be ordered at least with the temperature range suffix 7 (see Section 8: Ordering information) unless we reduce the power dissipation in order to be able to use suffix 6 parts.

Refer to *Figure 51* to select the required temperature range (suffix 6 or 7) according to your temperature or power requirements.

DocID026006 Rev 4