# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB        |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 86                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 16K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 19x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-LQFP                                                              |

| Supplier Device Package    | 100-LQFP (14x14)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f078vbt6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2 Description

The STM32F078CB/RB/VB microcontrollers incorporate the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M0 32-bit RISC core operating at up to 48 MHz frequency, high-speed embedded memories (128 Kbytes of Flash memory and 16 Kbytes of SRAM), and an extensive range of enhanced peripherals and I/Os. All devices offer standard communication interfaces (two I<sup>2</sup>Cs, two SPI/I<sup>2</sup>S, one HDMI CEC and four USARTs), one USB Full-speed device (crystalless), one 12-bit ADC, one 12-bit DAC with two channels, seven 16-bit timers, one 32-bit timer and an advanced-control PWM timer.

The STM32F078CB/RB/VB microcontrollers operate in the -40 to +85 °C and -40 to +105 °C temperature ranges from a 1.8 V  $\pm$  8% power supply. A comprehensive set of power-saving modes allows the design of low-power applications.

The STM32F078CB/RB/VB microcontrollers include devices in six different packages ranging from 48 pins to 100 pins with a die form also available upon request. Depending on the device chosen, different sets of peripherals are included.

These features make the STM32F078CB/RB/VB microcontrollers suitable for a wide range of applications such as application control and user interfaces, hand-held equipment, A/V receivers and digital TV, PC peripherals, gaming and GPS platforms, industrial applications, PLCs, inverters, printers, scanners, alarm systems, video intercoms and HVACs.

TIM15 can be synchronized with TIM16 and TIM17.

TIM15, TIM16 and TIM17 have a complementary output with dead-time generation and independent DMA request generation.

Their counters can be frozen in debug mode.

#### 3.14.3 Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger generation. They can also be used as generic 16-bit time bases.

#### 3.14.4 Independent watchdog (IWDG)

The independent watchdog is based on an 8-bit prescaler and 12-bit downcounter with user-defined refresh window. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop mode. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

#### 3.14.5 System window watchdog (WWDG)

The system window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the APB clock (PCLK). It has an early warning interrupt capability and the counter can be frozen in debug mode.

#### 3.14.6 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard down counter. It features:

- a 24-bit down counter

- autoreload capability

- maskable system interrupt generation when the counter reaches 0

- programmable clock source (HCLK or HCLK/8)

## 3.15 Real-time clock (RTC) and backup registers

The RTC and the five backup registers are supplied through a switch that takes power either on  $V_{DD}$  supply when present or through the  $V_{BAT}$  pin. The backup registers are five 32-bit registers used to store 20 bytes of user application data when  $V_{DD}$  power is not present. They are not reset by a system or power reset.

|          | Pin     | numt   | oers            |         |                                      |             | _             |       | Pin function                                                                          | IS                      |

|----------|---------|--------|-----------------|---------|--------------------------------------|-------------|---------------|-------|---------------------------------------------------------------------------------------|-------------------------|

| UFBGA100 | LQFP100 | LQFP64 | LQFP48/UFQFPN48 | WLCSP49 | Pin name<br>(function upon<br>reset) | Pin<br>type | I/O structure | Notes | Alternate functions                                                                   | Additional<br>functions |

| M6       | 36      | 27     | 19              | G4      | PB1                                  | I/O         | ТТа           | -     | TIM3_CH4, USART3_RTS,<br>TIM14_CH1, TIM1_CH3N,<br>TSC_G3_IO3                          | ADC_IN9                 |

| L6       | 37      | 28     | 20              | G3      | NPOR                                 | I           | POR           | (3)   | Device power-on reset in                                                              | out (active low)        |

| M7       | 38      | -      | -               | -       | PE7                                  | I/O         | FT            | -     | TIM1_ETR                                                                              | -                       |

| L7       | 39      | -      | -               | -       | PE8                                  | I/O         | FT            | -     | TIM1_CH1N                                                                             | -                       |

| M8       | 40      | -      | -               | -       | PE9                                  | I/O         | FT            | -     | TIM1_CH1                                                                              | -                       |

| L8       | 41      | -      | -               | -       | PE10                                 | I/O         | FT            | -     | TIM1_CH2N                                                                             | -                       |

| M9       | 42      | -      | -               | -       | PE11                                 | I/O         | FT            | -     | TIM1_CH2                                                                              | -                       |

| L9       | 43      | -      | -               | -       | PE12                                 | I/O         | FT            | -     | SPI1_NSS, I2S1_WS,<br>TIM1_CH3N                                                       | -                       |

| M10      | 44      | -      | -               | -       | PE13                                 | I/O         | FT            | -     | SPI1_SCK, I2S1_CK,<br>TIM1_CH3                                                        | -                       |

| M11      | 45      | -      | -               | -       | PE14                                 | I/O         | FT            | -     | SPI1_MISO, I2S1_MCK,<br>TIM1_CH4                                                      | -                       |

| M12      | 46      | -      | -               | -       | PE15                                 | I/O         | FT            | -     | SPI1_MOSI, I2S1_SD,<br>TIM1_BKIN                                                      | -                       |

| L10      | 47      | 29     | 21              | E3      | PB10                                 | I/O         | FT            | -     | SPI2_SCK, I2C2_SCL,<br>USART3_TX, CEC,<br>TSC_SYNC, TIM2_CH3                          | -                       |

| L11      | 48      | 30     | 22              | G2      | PB11                                 | I/O         | FT            | -     | USART3_RX, TIM2_CH4,<br>EVENTOUT, TSC_G6_IO1,<br>I2C2_SDA                             | -                       |

| F12      | 49      | 31     | 23              | D3      | VSS                                  | S           | -             | -     | Ground                                                                                |                         |

| G12      | 50      | 32     | 24              | F2      | VDD                                  | S           | -             | I     | Digital power su                                                                      | ipply                   |

| L12      | 51      | 33     | 25              | E2      | PB12                                 | I/O         | FT            | -     | TIM1_BKIN, TIM15_BKIN,<br>SPI2_NSS, I2S2_WS,<br>USART3_CK,<br>TSC_G6_IO2,<br>EVENTOUT | -                       |

| K12      | 52      | 34     | 26              | G1      | PB13                                 | I/O         | FTf           | -     | SPI2_SCK, I2S2_CK,<br>I2C2_SCL, USART3_CTS,<br>TIM1_CH1N, TSC_G6_IO3                  | -                       |

Table 12. STM32F078CB/RB/VB pin definitions (continued)

| Pin name | AF0       | AF1                 |

|----------|-----------|---------------------|

|          |           |                     |

| PE0      | TIM16_CH1 | EVENTOUT            |

| PE1      | TIM17_CH1 | EVENTOUT            |

| PE2      | TIM3_ETR  | TSC_G7_IO1          |

| PE3      | TIM3_CH1  | TSC_G7_IO2          |

| PE4      | TIM3_CH2  | TSC_G7_IO3          |

| PE5      | TIM3_CH3  | TSC_G7_IO4          |

| PE6      | TIM3_CH4  | -                   |

| PE7      | TIM1_ETR  | -                   |

| PE8      | TIM1_CH1N | -                   |

| PE9      | TIM1_CH1  | -                   |

| PE10     | TIM1_CH2N | -                   |

| PE11     | TIM1_CH2  | -                   |

| PE12     | TIM1_CH3N | SPI1_NSS, I2S1_WS   |

| PE13     | TIM1_CH3  | SPI1_SCK, I2S1_CK   |

| PE14     | TIM1_CH4  | SPI1_MISO, I2S1_MCK |

| PE15     | TIM1_BKIN | SPI1_MOSI, I2S1_SD  |

### Table 17. Alternate functions selected through GPIOE\_AFR registers for port E

#### Table 18. Alternate functions available on port F

| Pin name | AF        |  |  |  |  |  |

|----------|-----------|--|--|--|--|--|

| PF0      | CRS_SYNC  |  |  |  |  |  |

| PF1      | -         |  |  |  |  |  |

| PF2      | EVENTOUT  |  |  |  |  |  |

| PF3      | EVENTOUT  |  |  |  |  |  |

| PF6      | -         |  |  |  |  |  |

| PF9      | TIM15_CH1 |  |  |  |  |  |

| PF10     | TIM15_CH2 |  |  |  |  |  |

# 6 Electrical characteristics

## 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

#### 6.1.1 Minimum and maximum values

Unless otherwise specified, the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean  $\pm 3\sigma$ ).

#### 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 1.8$  V and  $V_{DDA} = 3.3$  V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean  $\pm 2\sigma$ ).

#### 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

#### 6.1.4 Loading capacitor

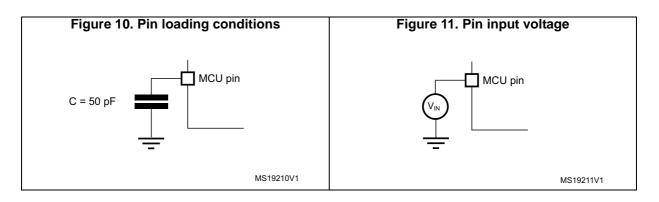

The loading conditions used for pin parameter measurement are shown in *Figure 10*.

#### 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 11*.

DocID026006 Rev 4

#### Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in analog input mode

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time is adjusted to the f<sub>HCLK</sub> frequency:

- 0 wait state and Prefetch OFF from 0 to 24 MHz

- 1 wait state and Prefetch ON above 24 MHz

- When the peripherals are enabled f<sub>PCLK</sub> = f<sub>HCLK</sub>

The parameters given in *Table 26* to *Table 30* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 23: General operating conditions*.

|                 | Ŀ                                     |                       |                   |        |       |                      | All    | periphera | als enab | led <sup>(1)</sup>  | All peripherals disabled |      |  |  |  |

|-----------------|---------------------------------------|-----------------------|-------------------|--------|-------|----------------------|--------|-----------|----------|---------------------|--------------------------|------|--|--|--|

| Symbol          | Parameter                             | Conditions            | f <sub>HCLK</sub> |        | N     | lax @ T <sub>A</sub> | (2)    |           | м        | ax @ T <sub>A</sub> | (2)                      | Unit |  |  |  |

| ŝ               | Par                                   |                       |                   | Тур    | 25 °C | 85 °C                | 105 °C | Тур       | 25 °C    | 85 °C               | 105 °C                   |      |  |  |  |

|                 |                                       | HSI48                 | 48 MHz            | 23.0   | 24.8  | 25.8                 | 26.7   | 12.9      | 13.7     | 14.1                | 15.3                     |      |  |  |  |

|                 | διο                                   |                       | 48 MHz            | 22.9   | 24.6  | 25.7                 | 26.6   | 12.8      | 13.6     | 13.9                | 15.2                     |      |  |  |  |

|                 | ode,<br>nem                           | HSE bypass,<br>PLL on | 32 MHz            | 15.5   | 16.6  | 17.2                 | 19.1   | 8.7       | 9.2      | 9.4                 | 10.0                     |      |  |  |  |

|                 | ר Run mode,<br>ר Flash memory         | n m<br>ash r          |                   | 24 MHz | 12.0  | 12.8                 | 13.2   | 14.3      | 6.8      | 7.2                 | 7.3                      | 7.7  |  |  |  |

|                 |                                       | HSE bypass,           | 8 MHz             | 4.2    | 4.4   | 4.5                  | 4.6    | 2.4       | 2.6      | 2.6                 | 2.7                      |      |  |  |  |

| I <sub>DD</sub> | current in<br>uting from              | PLL off               | 1 MHz             | 0.7    | 0.9   | 1.0                  | 1.1    | 0.5       | 0.6      | 0.7                 | 0.7                      | mA   |  |  |  |

|                 | Supply current in code executing from | curri<br>uting        |                   | 48 MHz | 22.9  | 24.6                 | 25.7   | 27.6      | 12.8     | 13.6                | 13.9                     | 15.2 |  |  |  |

|                 |                                       | HSI clock,<br>PLL on  | 32 MHz            | 15.5   | 16.6  | 17.2                 | 19.1   | 8.7       | 9.2      | 9.4                 | 10.0                     |      |  |  |  |

|                 |                                       |                       | 24 MHz            | 12.0   | 12.8  | 13.2                 | 14.3   | 6.8       | 7.2      | 7.3                 | 7.7                      |      |  |  |  |

|                 | 20                                    | HSI clock,<br>PLL off | 8 MHz             | 4.2    | 4.4   | 4.5                  | 4.6    | 2.4       | 2.6      | 2.6                 | 2.7                      |      |  |  |  |

| Table 26. Typical and maximum current consumption from | $V_{DD}$ supply at $V_{DD}$ = 1.8 V |

|--------------------------------------------------------|-------------------------------------|

|--------------------------------------------------------|-------------------------------------|

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

| Symbol          | Parameter   | Conditions <sup>(1)</sup>                                                         | I/O toggling<br>frequency (f <sub>SW</sub> ) | Тур  | Unit |

|-----------------|-------------|-----------------------------------------------------------------------------------|----------------------------------------------|------|------|

|                 |             |                                                                                   | 2 MHz                                        | 0.09 |      |

|                 |             |                                                                                   | 4 MHz                                        | 0.17 |      |

|                 |             | $V_{\text{DDIOx}} = 1.8 \text{ V}$                                                | 8 MHz                                        | 0.34 |      |

|                 |             | $C_{EXT} = 0 \text{ pF}$<br>$C = C_{INT} + C_{EXT} + C_S$                         | 18 MHz                                       | 0.79 |      |

|                 |             |                                                                                   | 36 MHz                                       | 1.50 |      |

|                 |             |                                                                                   | 48 MHz                                       | 2.06 |      |

|                 |             |                                                                                   | 2 MHz                                        | 0.13 |      |

|                 |             |                                                                                   | 4 MHz                                        | 0.26 |      |

|                 |             | $V_{\text{DDIOx}} = 1.8 \text{ V}$                                                | 8 MHz                                        | 0.50 |      |

|                 |             | $C_{EXT} = 10 \text{ pF}$<br>$C = C_{INT} + C_{EXT} + C_S$                        | 18 MHz                                       | 1.18 |      |

|                 |             |                                                                                   | 36 MHz                                       | 2.27 |      |

|                 |             |                                                                                   | 48 MHz                                       | 3.03 |      |

|                 | I/O current | $V_{DDIOx}$ = 1.8 V<br>$C_{EXT}$ = 22 pF<br>$C$ = $C_{INT}$ + $C_{EXT}$ + $C_{S}$ | 2 MHz                                        | 0.18 |      |

| I <sub>SW</sub> | consumption |                                                                                   | 4 MHz                                        | 0.36 | mA   |

|                 |             |                                                                                   | 8 MHz                                        | 0.69 |      |

|                 |             |                                                                                   | 18 MHz                                       | 1.60 |      |

|                 |             |                                                                                   | 36 MHz                                       | 3.27 |      |

|                 |             |                                                                                   | 2 MHz                                        | 0.23 |      |

|                 |             | V <sub>DDIOx</sub> = 1.8 V                                                        | 4 MHz                                        | 0.45 |      |

|                 |             | C <sub>EXT</sub> = 33 pF                                                          | 8 MHz                                        | 0.87 |      |

|                 |             | $C = C_{INT} + C_{EXT} + C_S$                                                     | 18 MHz                                       | 2.0  |      |

|                 |             |                                                                                   | 36 MHz                                       | 3.7  |      |

|                 |             |                                                                                   | 2 MHz                                        | 0.29 |      |

|                 |             | V <sub>DDIOx</sub> = 1.8 V<br>C <sub>EXT</sub> = 47 pF                            | 4 MHz                                        | 0.55 |      |

|                 |             | $C_{EXT} = 47 \text{ pr}$<br>$C = C_{INT} + C_{EXT} + C_S$                        | 8 MHz                                        | 1.09 |      |

|                 |             |                                                                                   | 18 MHz                                       | 2.43 |      |

| Table 31. Switching output I/0 | O current consumption |

|--------------------------------|-----------------------|

|--------------------------------|-----------------------|

1.  $C_S = 5 \text{ pF}$  (estimated value).

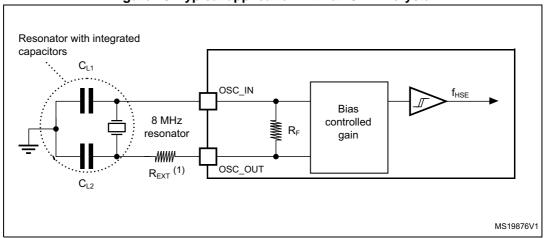

Figure 16. Typical application with an 8 MHz crystal

1.  $R_{EXT}$  value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 37*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                      | Conditions <sup>(1)</sup>        | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit |

|-------------------------------------|--------------------------------|----------------------------------|--------------------|-----|--------------------|------|

|                                     |                                | low drive capability             | -                  | 0.5 | 0.9                |      |

|                                     | LSE current consumption        | medium-low drive capability      | -                  | -   | 1                  |      |

| I <sub>DD</sub>                     | LSE current consumption        | medium-high drive capability     | -                  | -   | 1.3                | μA   |

|                                     |                                | high drive capability            | -                  | -   | 1.6                |      |

|                                     |                                | low drive capability             | 5                  | -   | -                  |      |

| g <sub>m</sub>                      | Oscillator<br>transconductance | medium-low drive capability      | 8                  | -   | -                  |      |

|                                     |                                | medium-high drive capability     | 15                 | -   | -                  | μA/V |

|                                     |                                | high drive capability            | 25                 | -   | -                  |      |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> | Startup time                   | V <sub>DDIOx</sub> is stabilized | -                  | 2   | -                  | S    |

| Table 37. LSE oscillator characteristics | (f <sub>LSE</sub> = 32.768 kHz) |

|------------------------------------------|---------------------------------|

|------------------------------------------|---------------------------------|

1. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

2. Guaranteed by design, not tested in production.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

#### High-speed internal (HSI) RC oscillator

| Symbol                | Parameter                         | Conditions                    | Min                 | Тур | Max                | Unit |

|-----------------------|-----------------------------------|-------------------------------|---------------------|-----|--------------------|------|

| f <sub>HSI</sub>      | Frequency                         | -                             | -                   | 8   | -                  | MHz  |

| TRIM                  | HSI user trimming step            | -                             | -                   | -   | 1 <sup>(2)</sup>   | %    |

| DuCy <sub>(HSI)</sub> | Duty cycle                        | -                             | 45 <sup>(2)</sup>   | -   | 55 <sup>(2)</sup>  | %    |

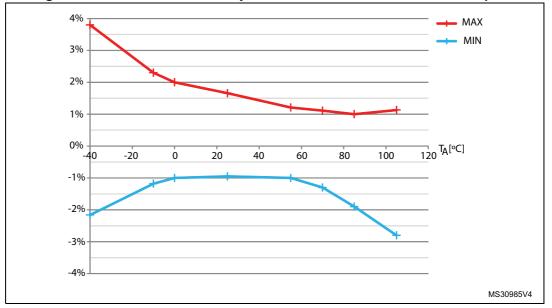

|                       |                                   | T <sub>A</sub> = -40 to 105°C | -2.8 <sup>(3)</sup> | -   | 3.8 <sup>(3)</sup> |      |

|                       | Accuracy of the HSI<br>oscillator | T <sub>A</sub> = -10 to 85°C  | -1.9 <sup>(3)</sup> | -   | 2.3 <sup>(3)</sup> | %    |

| 100                   |                                   | T <sub>A</sub> = 0 to 85°C    | -1.9 <sup>(3)</sup> | -   | 2 <sup>(3)</sup>   |      |

| ACC <sub>HSI</sub>    |                                   | $T_A = 0$ to $70^{\circ}C$    | -1.3 <sup>(3)</sup> | -   | 2 <sup>(3)</sup>   |      |

|                       |                                   | $T_A = 0$ to 55°C             | -1 <sup>(3)</sup>   | -   | 2 <sup>(3)</sup>   |      |

|                       |                                   | $T_A = 25^{\circ}C^{(4)}$     | -1                  | -   | 1                  |      |

| t <sub>su(HSI)</sub>  | HSI oscillator startup time       | -                             | 1 <sup>(2)</sup>    | -   | 2 <sup>(2)</sup>   | μs   |

| I <sub>DDA(HSI)</sub> | HSI oscillator power consumption  | -                             | -                   | 80  | 100 <sup>(2)</sup> | μA   |

#### Table 38. HSI oscillator characteristics<sup>(1)</sup>

1.  $V_{DDA}$  = 3.3 V,  $T_A$  = -40 to 105°C unless otherwise specified.

2. Guaranteed by design, not tested in production.

3. Data based on characterization results, not tested in production.

4. Factory calibrated, parts not soldered.

#### Figure 18. HSI oscillator accuracy characterization results for soldered parts

#### Low-speed internal (LSI) RC oscillator

| Table 41. | LSI | oscillator | characteristics <sup>(1)</sup> |

|-----------|-----|------------|--------------------------------|

|-----------|-----|------------|--------------------------------|

| Symbol                               | Parameter                        | Min | Тур  | Max | Unit |

|--------------------------------------|----------------------------------|-----|------|-----|------|

| f <sub>LSI</sub>                     | Frequency                        | 30  | 40   | 50  | kHz  |

| t <sub>su(LSI)</sub> <sup>(2)</sup>  | LSI oscillator startup time      | -   | -    | 85  | μs   |

| I <sub>DDA(LSI)</sub> <sup>(2)</sup> | LSI oscillator power consumption | -   | 0.75 | 1.2 | μΑ   |

1. V<sub>DDA</sub> = 3.3 V, T<sub>A</sub> = –40 to 105  $^\circ\text{C}$  unless otherwise specified.

2. Guaranteed by design, not tested in production.

#### 6.3.8 PLL characteristics

The parameters given in *Table 42* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 23: General operating conditions*.

| Symbol                | Parameter                      | Value             |     | Unit               |      |

|-----------------------|--------------------------------|-------------------|-----|--------------------|------|

|                       | Faranieler                     | Min               | Тур | Мах                | Onic |

| f <sub>PLL_IN</sub>   | PLL input clock <sup>(1)</sup> | 1 <sup>(2)</sup>  | 8.0 | 24 <sup>(2)</sup>  | MHz  |

|                       | PLL input clock duty cycle     | 40 <sup>(2)</sup> | -   | 60 <sup>(2)</sup>  | %    |

| f <sub>PLL_OUT</sub>  | PLL multiplier output clock    | 16 <sup>(2)</sup> | -   | 48                 | MHz  |

| t <sub>LOCK</sub>     | PLL lock time                  | -                 | -   | 200 <sup>(2)</sup> | μs   |

| Jitter <sub>PLL</sub> | Cycle-to-cycle jitter          | -                 | _   | 300 <sup>(2)</sup> | ps   |

Table 42. PLL characteristics

1. Take care to use the appropriate multiplier factors to obtain PLL input clock values compatible with the range defined by f<sub>PLL\_OUT</sub>.

2. Guaranteed by design, not tested in production.

#### 6.3.9 Memory characteristics

#### **Flash memory**

The characteristics are given at  $T_A$  = -40 to 105 °C unless otherwise specified.

| Symbol             | Parameter               | Conditions                       | Min | Тур  | Max <sup>(1)</sup> | Unit |

|--------------------|-------------------------|----------------------------------|-----|------|--------------------|------|

| t <sub>prog</sub>  | 16-bit programming time | T <sub>A</sub> = - 40 to +105 °C | 40  | 53.5 | 60                 | μs   |

| t <sub>ERASE</sub> | Page (2 KB) erase time  | T <sub>A</sub> = - 40 to +105 °C | 20  | -    | 40                 | ms   |

| t <sub>ME</sub>    | Mass erase time         | T <sub>A</sub> = - 40 to +105 °C | 20  | -    | 40                 | ms   |

| 1                  | Supply ourrant          | Write mode                       | -   | -    | 10                 | mA   |

| IDD                | Supply current          | Erase mode                       | -   | -    | 12                 | mA   |

1. Guaranteed by design, not tested in production.

| Symbol           | Parameter      | Conditions                                         | Min <sup>(1)</sup> | Unit   |  |  |

|------------------|----------------|----------------------------------------------------|--------------------|--------|--|--|

| N <sub>END</sub> | Endurance      | T <sub>A</sub> = -40 to +105 °C                    | 10                 | kcycle |  |  |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C  | 30                 |        |  |  |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C | 10                 | Year   |  |  |

|                  |                | 10 kcycle <sup>(2)</sup> at T <sub>A</sub> = 55 °C | 20                 |        |  |  |

Table 44. Flash memory endurance and data retention

1. Data based on characterization results, not tested in production.

2. Cycling performed over the whole temperature range.

### 6.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- **FTB**: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 45*. They are based on the EMS levels and classes defined in application note AN1709.

| Syml            | bol | Parameter                                                                                                                         | Conditions                                                                                                        | Level/<br>Class |

|-----------------|-----|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FE</sub> | SD  | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 1.8 V, LQFP100, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 48 MHz,<br>conforming to IEC 61000-4-2 | 2B              |

| V <sub>EF</sub> | ТВ  | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD}$ = 1.8 V, LQFP100, T <sub>A</sub> = +25°C,<br>f <sub>HCLK</sub> = 48 MHz,<br>conforming to IEC 61000-4-4  | 4B              |

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

| Symbol           | Parameter                                               | Conditions                                                                     | Min | Тур | Мах   | Unit |

|------------------|---------------------------------------------------------|--------------------------------------------------------------------------------|-----|-----|-------|------|

| l <sub>ikg</sub> |                                                         | TC, FT and FTf I/O<br>TTa in digital mode<br>$V_{SS} \le V_{IN} \le V_{DDIOX}$ | -   | -   | ± 0.1 |      |

|                  | Input leakage<br>current <sup>(2)</sup>                 | TTa in digital mode<br>V <sub>DDIOx</sub> ≤ V <sub>IN</sub> ≤ V <sub>DDA</sub> | -   | -   | 1     | μA   |

|                  |                                                         | TTa in analog mode<br>V <sub>SS</sub> ≤ V <sub>IN</sub> ≤ V <sub>DDA</sub>     | -   | -   | ± 0.2 | -    |

|                  |                                                         | FT and FTf I/O<br>V <sub>DDIOx</sub> ≤ V <sub>IN</sub> ≤ 5 V                   | -   | -   | 10    |      |

| R <sub>PU</sub>  | Weak pull-up<br>equivalent resistor<br>(3)              | V <sub>IN</sub> = V <sub>SS</sub>                                              | 25  | 40  | 55    | kΩ   |

| R <sub>PD</sub>  | Weak pull-down<br>equivalent<br>resistor <sup>(3)</sup> | V <sub>IN</sub> = - V <sub>DDIOx</sub>                                         | 25  | 40  | 55    | kΩ   |

| C <sub>IO</sub>  | I/O pin capacitance                                     | -                                                                              | -   | 5   | -     | pF   |

#### Table 50. I/O static characteristics (continued)

1. Data based on design simulation only. Not tested in production.

2. The leakage could be higher than the maximum value, if negative current is injected on adjacent pins. Refer to *Table 49: I/O current injection susceptibility.*

Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimal (~10% order).

All I/Os are CMOS- and TTL-compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 21* for standard I/Os, and in *Figure 22* for 5 V-tolerant I/Os. The following curves are design simulation results, not tested in production.

#### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 23* and *Table 52*, respectively. Unless otherwise specified, the parameters given are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 23: General operating conditions*.

| OSPEEDRy<br>[1:0] value <sup>(1)</sup> | Symbol                                                   | Parameter                        | Conditions                                         | Min | Max    | Unit |

|----------------------------------------|----------------------------------------------------------|----------------------------------|----------------------------------------------------|-----|--------|------|

|                                        | f <sub>max(IO)out</sub>                                  | Maximum frequency <sup>(3)</sup> |                                                    | -   | 2      | MHz  |

|                                        | t <sub>f(IO)out</sub>                                    | Output fall time                 | $C_L = 50 \text{ pF}, V_{DDIOx} \ge 2 \text{ V}$   | -   | 125    | ne   |

| x0                                     | t <sub>r(IO)out</sub>                                    | Output rise time                 |                                                    |     | 125    | ns   |

| ×0                                     | f <sub>max(IO)out</sub>                                  | Maximum frequency <sup>(3)</sup> |                                                    | -   | 1      | MHz  |

|                                        | t <sub>f(IO)out</sub>                                    | Output fall time                 | $C_L$ = 50 pF, $V_{DDIOx}$ < 2 V                   | -   | 125    | ns   |

|                                        | t <sub>r(IO)out</sub>                                    | Output rise time                 |                                                    | -   | 125    | 115  |

|                                        | f <sub>max(IO)out</sub> Maximum frequency <sup>(3)</sup> |                                  | -                                                  | 10  | MHz    |      |

|                                        | t <sub>f(IO)out</sub>                                    | Output fall time                 | $C_L$ = 50 pF, $V_{DDIOx} \ge 2 V$                 | -   | 25     | ns   |

| 01                                     | t <sub>r(IO)out</sub>                                    | Output rise time                 |                                                    | -   | 25     | 115  |

| 01                                     | f <sub>max(IO)out</sub>                                  | Maximum frequency <sup>(3)</sup> | C <sub>L</sub> = 50 pF, V <sub>DDIOx</sub> < 2 V   |     | 4      | MHz  |

|                                        | t <sub>f(IO)out</sub>                                    | Output fall time                 |                                                    |     | 62.5   | ns   |

|                                        | t <sub>r(IO)out</sub>                                    | Output rise time                 |                                                    | -   | - 62.5 |      |

|                                        |                                                          |                                  | C <sub>L</sub> = 30 pF, V <sub>DDIOx</sub> ≥ 2.7 V |     | 50     |      |

|                                        | f                                                        | Maximum frequency <sup>(3)</sup> | $C_L$ = 50 pF, $V_{DDIOx} \ge 2.7 V$               | -   | 30     | MHz  |

|                                        | f <sub>max(IO)out</sub>                                  |                                  | $C_L$ = 50 pF, 2 V ≤ $V_{DDIOx}$ < 2.7 V           | -   | 20     |      |

|                                        |                                                          |                                  | $C_L$ = 50 pF, $V_{DDIOx}$ < 2 V                   | -   | 10     |      |

|                                        |                                                          |                                  | $C_L$ = 30 pF, $V_{DDIOx} \ge 2.7 V$               | -   | 5      |      |

| 11                                     | town                                                     | Output fall time                 | $C_L$ = 50 pF, $V_{DDIOx} \ge 2.7 V$               | -   | 8      |      |

|                                        | t <sub>f(IO)</sub> out                                   |                                  | $C_L$ = 50 pF, 2 V ≤ $V_{DDIOx}$ < 2.7 V           | -   | 12     |      |

|                                        |                                                          |                                  | $C_L$ = 50 pF, $V_{DDIOx}$ < 2 V                   | -   | 25     | ne   |

|                                        |                                                          |                                  | $C_L$ = 30 pF, $V_{DDIOx} \ge 2.7 V$               | -   | 5      | ns   |

|                                        | ture                                                     | Output rise time                 | C <sub>L</sub> = 50 pF, V <sub>DDIOx</sub> ≥ 2.7 V | -   | 8      |      |

|                                        | t <sub>r(IO)out</sub>                                    |                                  | $C_L$ = 50 pF, 2 V ≤ $V_{DDIOx}$ < 2.7 V           | -   | 12     |      |

|                                        |                                                          |                                  | $C_L$ = 50 pF, $V_{DDIOx}$ < 2 V                   | -   | 25     |      |

Table 52. I/O AC characteristics<sup>(1)(2)</sup>

## 6.3.18 Temperature sensor characteristics

| Symbol                             | Parameter                                      | Min  | Тур  | Max  | Unit  |

|------------------------------------|------------------------------------------------|------|------|------|-------|

| T <sub>L</sub> <sup>(1)</sup>      | V <sub>SENSE</sub> linearity with temperature  | -    | ± 1  | ± 2  | °C    |

| Avg_Slope <sup>(1)</sup>           | Average slope                                  | 4.0  | 4.3  | 4.6  | mV/°C |

| V <sub>30</sub>                    | Voltage at 30 °C (± 5 °C) <sup>(2)</sup>       | 1.34 | 1.43 | 1.52 | V     |

| t <sub>START</sub> <sup>(1)</sup>  | ADC_IN16 buffer startup time                   | -    | -    | 10   | μs    |

| t <sub>S_temp</sub> <sup>(1)</sup> | ADC sampling time when reading the temperature | 4    | -    | -    | μs    |

1. Guaranteed by design, not tested in production.

2. Measured at  $V_{DDA}$  = 3.3 V ± 10 mV. The  $V_{30}$  ADC conversion result is stored in the TS\_CAL1 byte. Refer to Table 2: Temperature sensor calibration values.

## 6.3.19 V<sub>BAT</sub> monitoring characteristics

| Symbol                             | Parameter                                    | Min | Тур    | Мах | Unit |

|------------------------------------|----------------------------------------------|-----|--------|-----|------|

| R                                  | Resistor bridge for V <sub>BAT</sub>         | -   | 2 x 50 | -   | kΩ   |

| Q                                  | Ratio on V <sub>BAT</sub> measurement        | -   | 2      | -   | -    |

| Er <sup>(1)</sup>                  | Error on Q                                   | -1  | -      | +1  | %    |

| t <sub>S_vbat</sub> <sup>(1)</sup> | ADC sampling time when reading the $V_{BAT}$ | 4   | -      | -   | μs   |

#### Table 61. V<sub>BAT</sub> monitoring characteristics

1. Guaranteed by design, not tested in production.

#### 6.3.20 Timer characteristics

The parameters given in the following tables are guaranteed by design.

Refer to Section 6.3.13: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                   | Parameter               | Conditions                    | Min      | Тур                     | Max | Unit                 |

|--------------------------|-------------------------|-------------------------------|----------|-------------------------|-----|----------------------|

| t <sub>ere</sub> (TIN () | Timer resolution time   | -                             | -        | 1                       | -   | t <sub>TIMxCLK</sub> |

| t <sub>res(TIM)</sub>    |                         | f <sub>TIMxCLK</sub> = 48 MHz | -        | 20.8                    | -   | ns                   |

|                          | Timer external clock    | -                             | -        | f <sub>TIMxCLK</sub> /2 | -   | MHz                  |

|                          | frequency on CH1 to CH4 | f <sub>TIMxCLK</sub> = 48 MHz | -        | 24                      | -   | MHz                  |

|                          | 16-bit timer maximum    | -                             | -        | 2 <sup>16</sup>         | -   | t <sub>TIMxCLK</sub> |

| +                        | period                  | f <sub>TIMxCLK</sub> = 48 MHz | z - 1365 |                         | -   | μs                   |

| t <sub>MAX_COUNT</sub>   | 32-bit counter          | -                             | -        | 2 <sup>32</sup>         | -   | t <sub>TIMxCLK</sub> |

|                          | maximum period          | f <sub>TIMxCLK</sub> = 48 MHz | -        | 89.48                   | -   | S                    |

| Table | 62. | TIMx | characteristics |

|-------|-----|------|-----------------|

|-------|-----|------|-----------------|

| Symbol          | Parameter                                                        | Min               | Max                | Unit |

|-----------------|------------------------------------------------------------------|-------------------|--------------------|------|

| t <sub>AF</sub> | Maximum width of spikes that are suppressed by the analog filter | 50 <sup>(2)</sup> | 260 <sup>(3)</sup> | ns   |

Table 65. I<sup>2</sup>C analog filter characteristics<sup>(1)</sup>

1. Guaranteed by design, not tested in production.

2. Spikes with widths below  $t_{AF(min)}$  are filtered.

3. Spikes with widths above  $t_{AF(max)}$  are not filtered

## SPI/I<sup>2</sup>S characteristics

Unless otherwise specified, the parameters given in *Table 66* for SPI or in *Table 67* for  $I^2S$  are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and supply voltage conditions summarized in *Table 23: General operating conditions*.

Refer to Section 6.3.13: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI and WS, CK, SD for I<sup>2</sup>S).

| Symbol                                       | Parameter                                 | Conditions                                            | Min         | Max         | Unit  |

|----------------------------------------------|-------------------------------------------|-------------------------------------------------------|-------------|-------------|-------|

| f <sub>SCK</sub>                             | SDI clock froguency                       | Master mode                                           | -           | 18          | MHz   |

| 1/t <sub>c(SCK)</sub>                        | SPI clock frequency                       | Slave mode                                            | -           | 18          | IVITZ |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>   | SPI clock rise and fall time              | Capacitive load: C = 15 pF                            | -           | 6           | ns    |

| t <sub>su(NSS)</sub>                         | NSS setup time                            | Slave mode                                            | 4Tpclk      | -           |       |

| t <sub>h(NSS)</sub>                          | NSS hold time                             | Slave mode                                            | 2Tpclk + 10 | -           |       |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time                     | Master mode, f <sub>PCLK</sub> = 36 MHz,<br>presc = 4 | Tpclk/2 -2  | Tpclk/2 + 1 |       |

| t <sub>su(MI)</sub>                          | t <sub>su(MI)</sub> Data input setup time | Master mode                                           | 4           | -           |       |

| t <sub>su(SI)</sub>                          |                                           | Slave mode                                            | 5           | -           |       |

| t <sub>h(MI)</sub>                           | Data input hold time                      | Master mode                                           | 4           | -           |       |

| t <sub>h(SI)</sub>                           | Data input hold time                      | Slave mode                                            | 5           | -           | ns    |

| t <sub>a(SO)</sub> <sup>(2)</sup>            | Data output access time                   | Slave mode, f <sub>PCLK</sub> = 20 MHz                | 0           | 3Tpclk      |       |

| t <sub>dis(SO)</sub> <sup>(3)</sup>          | Data output disable time                  | Slave mode                                            | 0           | 18          |       |

| t <sub>v(SO)</sub>                           | Data output valid time                    | Slave mode (after enable edge)                        | -           | 22.5        |       |

| t <sub>v(MO)</sub>                           | Data output valid time                    | Master mode (after enable edge)                       | -           | 6           |       |

| t <sub>h(SO)</sub>                           | Data output hold time                     | Slave mode (after enable edge)                        | 11.5        | -           |       |

| t <sub>h(MO)</sub>                           |                                           | Master mode (after enable edge)                       | 2           | -           |       |

| DuCy(SCK)                                    | SPI slave input clock<br>duty cycle       | Slave mode                                            | 25          | 75          | %     |

#### Table 66. SPI characteristics<sup>(1)</sup>

1. Data based on characterization results, not tested in production.

2. Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

3. Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

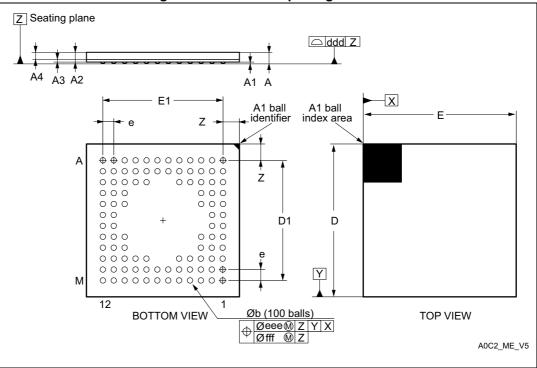

## 7.1 UFBGA100 package information

UFBGA100 is a 100-ball, 7 x 7 mm, 0.50 mm pitch, ultra-fine-profile ball grid array package.

Figure 34. UFBGA100 package outline

1. Drawing is not to scale.

| Symbol |      | millimeters |       | inches <sup>(1)</sup> |        |        |

|--------|------|-------------|-------|-----------------------|--------|--------|

| Symbol | Min. | Тур.        | Max.  | Min.                  | Тур.   | Max.   |

| А      | -    | -           | 0.600 | -                     | -      | 0.0236 |

| A1     | -    | -           | 0.110 | -                     | -      | 0.0043 |

| A2     | -    | 0.450       | -     | -                     | 0.0177 | -      |

| A3     | -    | 0.130       | -     | -                     | 0.0051 | 0.0094 |

| A4     | -    | 0.320       | -     | -                     | 0.0126 | -      |

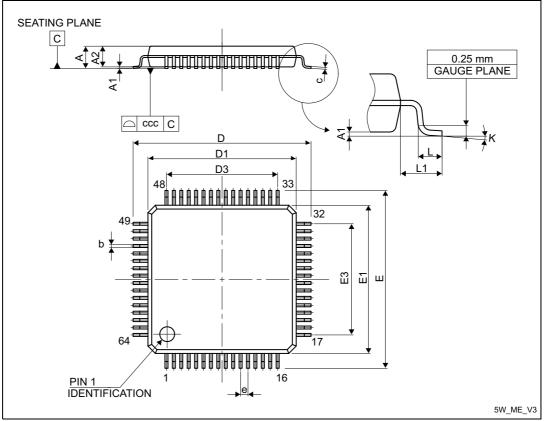

## 7.3 LQFP64 package information

LQFP64 is a 64-pin, 10 x 10 mm low-profile quad flat package.

Figure 40. LQFP64 package outline

1. Drawing is not to scale.

| Symbol |       | millimeters |       | inches <sup>(1)</sup> |        |        |

|--------|-------|-------------|-------|-----------------------|--------|--------|

| Symbol | Min   | Тур         | Max   | Min                   | Тур    | Max    |

| А      | -     | -           | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050 | -           | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350 | 1.400       | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170 | 0.220       | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| с      | 0.090 | -           | 0.200 | 0.0035                | -      | 0.0079 |

| D      | -     | 12.000      | -     | -                     | 0.4724 | -      |

| D1     | -     | 10.000      | -     | -                     | 0.3937 | -      |

| D3     | -     | 7.500       | -     | -                     | 0.2953 | -      |

| E      | -     | 12.000      | -     | -                     | 0.4724 | -      |

| E1     | -     | 10.000      | -     | -                     | 0.3937 | -      |

| Symbol |       | millimeters |       | inches <sup>(1)</sup> |        |        |

|--------|-------|-------------|-------|-----------------------|--------|--------|

| Symbol | Min   | Тур         | Max   | Min                   | Тур    | Max    |

| А      | -     | -           | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050 | -           | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350 | 1.400       | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170 | 0.220       | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| с      | 0.090 | -           | 0.200 | 0.0035                | -      | 0.0079 |

| D      | 8.800 | 9.000       | 9.200 | 0.3465                | 0.3543 | 0.3622 |

| D1     | 6.800 | 7.000       | 7.200 | 0.2677                | 0.2756 | 0.2835 |

| D3     | -     | 5.500       | -     | -                     | 0.2165 | -      |

| E      | 8.800 | 9.000       | 9.200 | 0.3465                | 0.3543 | 0.3622 |

| E1     | 6.800 | 7.000       | 7.200 | 0.2677                | 0.2756 | 0.2835 |

| E3     | -     | 5.500       | -     | -                     | 0.2165 | -      |

| е      | -     | 0.500       | -     | -                     | 0.0197 | -      |

| L      | 0.450 | 0.600       | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1     | -     | 1.000       | -     | -                     | 0.0394 | -      |

| k      | 0°    | 3.5°        | 7°    | 0°                    | 3.5°   | 7°     |

| ССС    | -     | -           | 0.080 | -                     | -      | 0.0031 |

| Table 74. | LQFP48 | package | mechanical | data |

|-----------|--------|---------|------------|------|

|           |        | pachage | meenamear  | uata |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

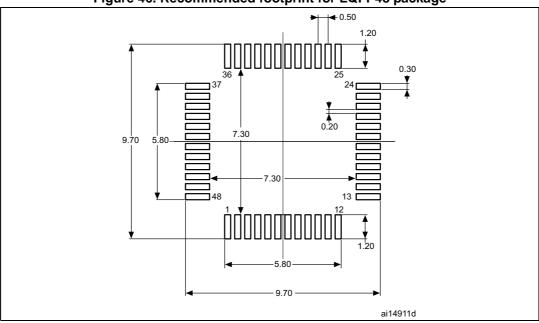

#### Figure 46. Recommended footprint for LQFP48 package

1. Dimensions are expressed in millimeters.

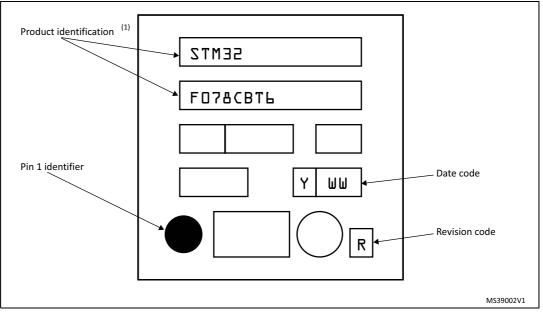

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |  |

|--------|-------|-------------|-------|--------|-----------------------|--------|--|

| Symbol | Min   | Тур         | Max   | Min    | Тур                   | Max    |  |

| А      | 0.500 | 0.550       | 0.600 | 0.0197 | 0.0217                | 0.0236 |  |

| A1     | 0.000 | 0.020       | 0.050 | 0.0000 | 0.0008                | 0.0020 |  |

| D      | 6.900 | 7.000       | 7.100 | 0.2717 | 0.2756                | 0.2795 |  |

| E      | 6.900 | 7.000       | 7.100 | 0.2717 | 0.2756                | 0.2795 |  |

| D2     | 5.500 | 5.600       | 5.700 | 0.2165 | 0.2205                | 0.2244 |  |

| E2     | 5.500 | 5.600       | 5.700 | 0.2165 | 0.2205                | 0.2244 |  |

| L      | 0.300 | 0.400       | 0.500 | 0.0118 | 0.0157                | 0.0197 |  |

| Т      | -     | 0.152       | -     | -      | 0.0060                | -      |  |

| b      | 0.200 | 0.250       | 0.300 | 0.0079 | 0.0098                | 0.0118 |  |

| е      | -     | 0.500       | -     | -      | 0.0197                | -      |  |

| ddd    | -     | -           | 0.080 | -      | -                     | 0.0031 |  |

Table 75. UFQFPN48 package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

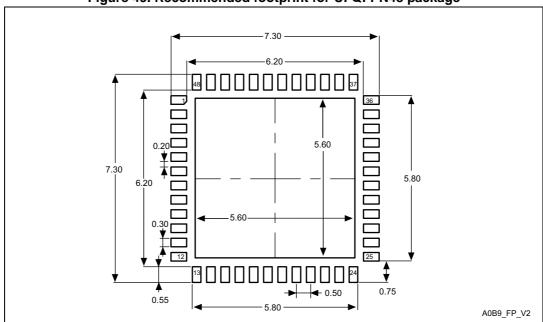

#### Figure 49. Recommended footprint for UFQFPN48 package

1. Dimensions are expressed in millimeters.