Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                        |

|----------------------------|----------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                 |

| Core Processor             | 8052                                                                                   |

| Core Size                  | 8-Bit                                                                                  |

| Speed                      | 40MHz                                                                                  |

| Connectivity               | EBI/EMI, UART/USART                                                                    |

| Peripherals                | POR, WDT                                                                               |

| Number of I/O              | 36                                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | -                                                                                      |

| RAM Size                   | 256 x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                                            |

| Data Converters            | -                                                                                      |

| Oscillator Type            | External                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                      |

| Mounting Type              | Surface Mount                                                                          |

| Package / Case             | 44-LCC (J-Lead)                                                                        |

| Supplier Device Package    | -                                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/w78i054dpg |

## 1 GENERAL DESCRIPTION

The W78I054D/W78I052D/W78I051D series is an 8-bit microcontroller which can accommodate a wider frequency range with low power consumption. The instruction set for the W78I054D/ W78I052D/ W78I051D series is fully compatible with the standard 8052.

The W78I054D/W78I052D/W78I051D series contains 16K/8K/4K bytes Flash EPROM programmable by hardware writer; a 256 bytes RAM; four 8-bit bi-directional (P0, P1, P2, P3) and bit-addressable I/O ports; an additional 4-bit I/O port P4; three 16-bit timer/counters; a hardware watchdog timer and a serial port. These peripherals are supported by 8 sources 4-level interrupt capability. To facilitate programming and verification, the Flash EPROM inside the W78I054D/W78I052D/W78I051D series allows the program memory to be programmed and read electronically. Once the code is confirmed, the user can protect the code for security.

The W78I054D/W78I052D/W78I051D series microcontroller has two power reduction modes, idle mode and power-down mode, both of which are software selectable. The idle mode turns off the processor clock but allows for continued peripheral operation. The power-down mode stops the crystal oscillator for minimum power consumption. The external clock can be stopped at any time and in any state without affecting the processor. The W78I054D/W78I052D/W78I051D series contains In-System Programmable (ISP) 2KB LD Flash EPROM for loader program, operating voltage from 3.3V to 5.5V.

The W78I054D/W78I052D/W78I051D series feature industrial temperature rage (-40 degrees Celsius to +85 degrees Celsius).

## 2 FEATURES

- Fully static design 8-bit CMOS microcontroller

- Optional 12T or 6T mode

- 12T Mode, 12 clocks per machine cycle operation (default), Speed up to 40 MHz/5V

- 6T Mode, 6 clocks per machine cycle operation set by the writer, Speed up to 20 MHz/5V

- Wide supply voltage of 2.4V to 5.5V

- Temperature grade is (-40°C~85°C)

- Pin and Instruction-sets compatible with MCS-51

- 256 bytes of on-chip scratchpad RAM

- 16K/8K/4K bytes electrically erasable/programmable Flash EPROM

- 2K bytes LDROM support ISP function (Reference Application Note)

- 64KB program memory address space

- 64KB data memory address space

- Four 8-bit bi-directional ports

- 8-sources, 4-level interrupt capability

- One extra 4-bit bit-addressable I/O port, additional INT2 / INT3 (available on PQFP, PLCC and LQFP package)

- 5 -

- Three 16-bit timer/counters

- One full duplex serial port

- Watchdog Timer

- EMI reduction mode

- Software Reset

- Built-in power management with idle mode and power down mode

- Code protection

- · Packages:

| - | Lead Free (RoHS) DIP 40:  | W78I054DDG |

|---|---------------------------|------------|

| - | Lead Free (RoHS) PLCC 44: | W78I054DPG |

| - | Lead Free (RoHS) PQFP 44: | W78I054DFG |

| - | Lead Free (RoHS) LQFP 48: | W78I054DLG |

| - | Lead Free (RoHS) DIP 40:  | W78I052DDG |

| - | Lead Free (RoHS) PLCC 44: | W78I052DPG |

| - | Lead Free (RoHS) PQFP 44: | W78I052DFG |

| - | Lead Free (RoHS) LQFP 48: | W78I052DLG |

| - | Lead Free (RoHS) DIP 40:  | W78I051DDG |

| - | Lead Free (RoHS) PLCC 44: | W78I051DPG |

| - | Lead Free (RoHS) PQFP 44: | W78I051DFG |

| - | Lead Free (RoHS) LQFP 48: | W78I051DLG |

# 5 PIN DESCRIPTIONS

|           | •      |                                                                                                                                                                                                                 |

|-----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYMBOL    | TYPE   | DESCRIPTIONS                                                                                                                                                                                                    |

| ĒĀ        | ı      | EXTERNAL ACCESS ENABLE: This pin forces the processor to execute out of external ROM. It should be kept high to access internal ROM. The ROM address                                                            |

|           |        | and data will not be present on the bus if EA pin is high and the program counter is within internal ROM area. Otherwise they will be present on the bus.                                                       |

| PSEN      | ОН     | PROGRAM STORE ENABLE: PSEN enables the external ROM data onto the Port 0 address/data bus during fetch and MOVC operations. When internal ROM access is performed, no PSEN strobe signal outputs from this pin. |

| ALE       | ОН     | ADDRESS LATCH ENABLE: ALE is used to enable the address latch that separates the address from the data on Port 0.                                                                                               |

| RST       | ۱L     | RESET: A high on this pin for two machine cycles while the oscillator is running resets the device.                                                                                                             |

| XTAL1     | I      | CRYSTAL1: This is the crystal oscillator input. This pin may be driven by an external clock.                                                                                                                    |

| XTAL2     | 0      | CRYSTAL2: This is the crystal oscillator output. It is the inversion of XTAL1.                                                                                                                                  |

| VSS       | I      | GROUND: Ground potential                                                                                                                                                                                        |

| VDD       | I      | POWER SUPPLY: Supply voltage for operation.                                                                                                                                                                     |

| P0.0–P0.7 | I/O H  | PORT 0: Port 0 is an open-drain bi-directional I/O port. This port also provides a multiplexed low order address/data bus during accesses to external memory.                                                   |

|           | ./0.11 | PORT 1: Port 1 is a bi-directional I/O port with internal pull-ups. The bits have alternate functions which are described below:                                                                                |

| P1.0–P1.7 | I/O H  | T2 (P1.0): Timer/Counter 2 external count input T2EX (P1.1): Timer/Counter 2 Reload/Capture control                                                                                                             |

| P2.0-P2.7 | I/O H  | PORT 2: Port 2 is a bi-directional I/O port with internal pull-ups. This port also provides the upper address bits for accesses to external memory.                                                             |

-9-

# Pin Description, continued

| SYMBOL    | TVDE  | DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STIVIBOL  | IIFE  | DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                |

| P3.0-P3.7 |       | PORT 3: Port 3 is a bi-directional I/O port with internal pull-ups. All bits have alternate functions, which are described below:  RXD (P3.0): Serial Port 0 input  TXD (P3.1): Serial Port 0 output  INTO (P3.2): External Interrupt 0  INT1 (P3.3): External Interrupt 1  T0 (P3.4): Timer 0 External Input  T1 (P3.5): Timer 1 External Input  WR (P3.6): External Data Memory Write Strobe  RD (P3.7): External Data Memory Read Strobe |

| P4.0-P4.3 | I/O H | PORT 4: Another bit-addressable bidirectional I/O port P4. P4.3 and P4.2 are alternative function pins. It can be used as general I/O port or external interrupt input sources (INT2 /INT3).                                                                                                                                                                                                                                                |

<sup>\*</sup> Note: TYPE I: input, O: output, I/O: bi-directional, H: pull-high, L: pull-low, D: open drain.

In application if MCU pins need external pull-up, it is recommended to add a pull-up resistor (10K $\Omega$ ) between pin and power (V<sub>DD</sub>) instead of directly wiring pin to V<sub>DD</sub> for enhancing EMC.

#### 7.6 Data Pointers

The data pointer of W78I054D/W78I052D/W78I051D series is same as standard 8052 that have one 16-bit Data Pointer (DPTR).

#### 7.7 Architecture

The W78I054D/W78I052D/W78I051D series are based on the standard 8052 device. It is built around an 8-bit ALU that uses internal registers for temporary storage and control of the peripheral devices. It can execute the standard 8052 instruction set.

#### 7.7.1 ALU

The ALU is the heart of the W78I054D/W78I052D/W78I051D series. It is responsible for the arithmetic and logical functions. It is also used in decision making, in case of jump instructions, and is also used in calculating jump addresses. The user cannot directly use the ALU, but the Instruction Decoder reads the op-code, decodes it, and sequences the data through the ALU and its associated registers to generate the required result. The ALU mainly uses the ACC which is a special function register (SFR) on the chip. Another SFR, namely B register is also used Multiply and Divide instructions. The ALU generates several status signals which are stored in the Program Status Word register (PSW).

#### 7.7.2 Accumulator

The Accumulator (ACC) is the primary register used in arithmetic, logical and data transfer operations in the W78I054D/W78I052D/W78I051D series. Since the Accumulator is directly accessible by the CPU, most of the high speed instructions make use of the ACC as one argument.

### 7.7.3 B Register

This is an 8-bit register that is used as the second argument in the MUL and DIV instructions. For all other instructions it can be used simply as a general purpose register.

### 7.7.4 Program Status Word

This is an 8-bit SFR that is used to store the status bits of the ALU. It holds the Carry flag, the Auxiliary Carry flag, General purpose flags, the Register Bank Select, the Overflow flag, and the Parity flag.

## 7.7.5 Scratch-pad RAM

The W78I054D/W78I052D/W78I051D series has a 256 byte on-chip scratch-pad RAM. This can be used by the user for temporary storage during program execution. A certain section of this RAM is bit addressable, and can be directly addressed for this purpose.

## 7.7.6 Stack Pointer

The W78I054D/W78I052D/W78I051D series has an 8-bit Stack Pointer which points to the top of the Stack. This stack resides in the Scratch Pad RAM in the W78I054D/W78I052D/W78I051D. Hence the size of the stack is limited by the size of this RAM.

## 8.2.2 Bit addressable Locations

The Scratch-pad RAM area from location 20h to 2Fh is byte as well as bit addressable. This means that a bit in this area can be individually addressed. In addition some of the SFRs are also bit addressable. The instruction decoder is able to distinguish a bit access from a byte access by the type of the instruction itself. In the SFR area, any existing SFR whose address ends in a 0 or 8 is bit addressable.

## 8.2.3 Stack

The scratch-pad RAM can be used for the stack. This area is selected by the Stack Pointer (SP), which stores the address of the top of the stack. Whenever a jump, call or interrupt is invoked the return address is placed on the stack. There is no restriction as to where the stack can begin in the RAM. By default however, the Stack Pointer contains 07h at reset. The user can then change this to any value desired. The SP will point to the last used value. Therefore, the SP will be incremented and then address saved onto the stack. Conversely, while popping from the stack the contents will be read first, and then the SP is decreased.

- 17 -

# Special Function Registers:

| SYMBOL | DEFINITION ADDRESS MSB BIT ADDRESS, SYMBOL |     |                |              |              |              |               | LSB          | RESET        |                |            |

|--------|--------------------------------------------|-----|----------------|--------------|--------------|--------------|---------------|--------------|--------------|----------------|------------|

| В      | B register                                 | F0H | (F7)           | (F6)         | (F5)         | (F4)         | (F3)          | (F2)         | (F1)         | (F0)           | 0000 0000B |

| ACC    | Accumulator                                | E0H | (E7)           | (E6)         | (E5)         | (E4)         | (E3)          | (E2)         | (E1)         | (E0)           | 0000 0000B |

| P4     | Port 4                                     | D8H | ,              |              |              |              | INT2          | INT3         | , ,          | , ,            | 0000 1111B |

| PSW    | Program status word                        | D0H | (D7)           | (D6)         | (D5)         | (D4)         | (D3)          | (D2)         | (D1)         | (D0)           | 0000 0000B |

|        |                                            |     | CY             | AC           | F0           | RS1          | RS0           | OV           | F1           | Р              |            |

| TH2    | T2 reg. high                               | CDH |                |              |              |              |               |              |              |                | 0000 0000B |

| TL2    | T2 reg. low                                | CCH |                |              |              |              |               |              |              |                | 0000 0000B |

| RCAP2H | T2 capture low                             | СВН |                |              |              |              |               |              |              |                | 0000 0000B |

| RCAP2L | T2 capture high                            | CAH |                |              |              |              |               |              |              |                | 0000 0000B |

| T2MOD  | Timer 2 Mode                               | C9  |                |              |              |              |               |              |              | DCEN           | 0000 0000B |

| T2CON  | Timer 2 control                            | C8H | (CF)<br>TF2    | (CE)<br>EXF2 | (CD)<br>RCLK | (CC)<br>TCLK | (CB)<br>EXEN2 | (CA)<br>TR2  | (C9)<br>C/T2 | (C8)<br>CP/RL2 | 0000 0000B |

| SFRCN  | SFR program of control                     | C7H |                |              | NOE          | NCE          | CTRL3         | CTRL2        | CTRL1        | CTRL0          | 0000 0000B |

| SFRRD  | SFR program of data register               | C6H |                |              |              |              |               |              |              |                | 0000 0000B |

| SFRAH  | SFR program of address high byte           | C5H |                |              |              |              |               |              |              |                | 0000 0000B |

| SFRAL  | SFR program of address low byte            | C4H |                |              |              |              |               |              |              |                | 0000 0000B |

| XICON  | External interrupt control                 | C0H | PX3            | EX3          | IE3          | IT3          | PX2           | EX2          | IE2          | IT2            | 0000 0000B |

| CHPCON | Chip control                               | BFH | SWRST          | -            |              | -            | -             | -            | FBOOTS<br>L  | ENP            | 0000 0000B |

| EAPAGE | Erase page operation modes                 | BEH |                |              |              |              |               |              | EAPG1        | EAPG0          | 0000 0000B |

| IP     | Interrupt priority                         | В8Н | (BF)           | (BE)         | (BD)<br>PT2  | (BC)<br>PS   | (BB)<br>PT1   | (BA)<br>PX1  | (B9)<br>PT0  | (B8)<br>PX0    | 1100 0000B |

| IPH    | Interrupt priority High                    | B7H |                |              |              |              |               |              |              |                | 0000 0000B |

| P3     | Port 3                                     | вон | (B7)<br>RD     | (B6)<br>WR   | (B5)<br>T1   | (B4)<br>T0   | (B3)<br>INT1  | (B2)<br>INT0 | (B1)<br>TXD  | (B0)<br>RXD    | 1111 1111B |

| IE     | Interrupt enable                           | A8H | (AF)<br>EA     | (AE)         | (AD)<br>ET2  | (AC)         | (AB)<br>ET1   | (AA)<br>EX1  | (A9)<br>ET0  | (A8)<br>EX0    | 0100 0000B |

| P2     | Port 2                                     | A0H | (A7)           | (A6)         | (A5)         | (A4)         | (A3)          | (A2)         | (A1)         | (A0)           | 1111 1111B |

|        |                                            |     | A15            | A14          | A13          | A12          | A11           | A10          | A9           | A8             |            |

| SBUF   | Serial buffer                              | 99H |                |              |              |              |               |              |              |                | 0000 0000B |

| SCON   | Serial control                             | 98H | (9F)<br>SM0/FE | (9E)<br>SM1  | (9D)<br>SM2  | (9C)<br>REN  | (9B)<br>TB8   | (9A)<br>RB8  | (99)<br>TI   | (98)<br>RI     | 0000 0000B |

| P1     | Port 1                                     | 90H | (97)           | (96)         | (95)         | (94)         | (93)          | (92)         | (91)<br>T2EX | (90)<br>T2     | 1111 1111B |

| WDTC   | Watchdog control                           | 8FH | ENW            | CLRW         | WIDL         | -            | -             | PS2          | PS1          | PS0            | 0000 0000B |

| AUXR   | Auxiliary                                  | 8EH | -              | -            | -            | -            |               |              |              | ALEOFF         | 0000 0110B |

| TH1    | Timer high 1                               | 8DH |                |              |              |              |               |              |              |                | 0000 0000B |

| TH0    | Timer high 0                               | 8CH |                |              |              |              |               |              |              |                | 0000 0000B |

| TL1    | Timer low 1                                | 8BH | İ              |              |              |              | İ             |              |              | İ              | 0000 0000B |

| TL0    | Timer low 0                                | 8AH |                |              |              |              |               |              |              |                | 0000 0000B |

| TMOD   | Timer mode                                 | 89H | GATE           | C/T          | M1           | МО           | GATE          | C/T          | M1           | МО             | 0000 0000B |

| TCON   | Timer control                              | 88H | (8F)<br>TF1    | (8E)<br>TR1  | (8D)<br>TF0  | (8C)<br>TR0  | (8B)<br>IE1   | (8A)<br>IT1  | (89)<br>IE0  | (88)<br>IT0    | 0000 0000B |

| PCON   | Power control                              | 87H | SMOD           | SMOD0        | -            | POR          | GF1           | GF0          | PD           | IDL            | 0011 0000B |

| P0UPR  | Port 0 pull up option Register             | 86H | -              | -            | -            | -            | -             | -            | -            | P0UP           | 0000 0001B |

| DPH    | Data pointer high                          | 83H |                |              |              |              |               |              |              |                | 0000 0000B |

- 19 -

| BIT | NAME    | FUNCTION                |

|-----|---------|-------------------------|

| 0   | ALE_OFF | 1: Disenable ALE output |

|     |         | 0: Enable ALE output    |

# **Watchdog Timer Control Register**

| Bit: | 7   | 6    | 5    | 4 | 3 | 2   | 1   | 0   |

|------|-----|------|------|---|---|-----|-----|-----|

|      | ENW | CLRW | WIDL | - | - | PS2 | PS1 | PS0 |

Mnemonic: WDTC Address: 8FH

| BIT | NAME  | FUNCTION                                                                                                                         |                                |                                |  |  |  |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------|--|--|--|

| 7   | ENW   | Enable watch-dog if set.                                                                                                         |                                |                                |  |  |  |

| 6   | CLRW  | Clear watch-dog time cally.                                                                                                      | er and Pre-scalar if set. This | flag will be cleared automati- |  |  |  |

| 5   | WIDL  | If this bit is set, watch-dog is enabled under IDLE mode. If cleared, watch-dog is disabled under IDLE mode. Default is cleared. |                                |                                |  |  |  |

| 2-0 | PS2-0 | lows:                                                                                                                            |                                | lected when set PS2-0 as fol-  |  |  |  |

|     |       | PS2 PS1 PS0                                                                                                                      | PRE-SCALAR SELECT              |                                |  |  |  |

|     |       | 0 0 0                                                                                                                            | 2                              |                                |  |  |  |

|     |       | 0 0 1                                                                                                                            | 8                              |                                |  |  |  |

|     |       | 0 1 0                                                                                                                            | 4                              |                                |  |  |  |

|     |       | 0 1 1                                                                                                                            | 16                             |                                |  |  |  |

|     |       | 1 0 0                                                                                                                            | 32                             |                                |  |  |  |

|     |       |                                                                                                                                  | 32                             |                                |  |  |  |

|     |       | 1 0 1                                                                                                                            | 64                             |                                |  |  |  |

## Port 1

| Bit: | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|------|

|      | P1.7 | P1.6 | P1.5 | P1.4 | P1.3 | P1.2 | P1.1 | P1.0 |

256

Mnemonic: P1 Address: 90h

| BIT | NAME     | FUNCTION                                                                                                                                                                      |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0 | P1.[7:0] | General purpose I/O port. Most instructions will read the port pins in case of a port read access, however in case of read-modify-write instructions, the port latch is read. |

## **Serial Port Control**

Bit:

7

6

5

4

3

2

1

0

SM0/FE

SM1

SM2

REN

TB8

RB8

TI

RI

Mnemonic: SCON Address: 98h

| BIT | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SM0/FE | Serial port mode select bit 0 or Framing Error Flag: The SMOD0 bit in PCON SFR determines whether this bit acts as SM0 or as FE. The operation of SM0 is described below. When used as FE, this bit will be set to indicate an invalid stop bit. This bit must be manually cleared in software to clear the FE condition.                                                                                                                                                                                                                                                                                                                                       |

| 6   | SM1    | Serial Port mode select bit 1. See table below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5   | SM2    | Multiple processors communication. Setting this bit to 1 enables the multiprocessor communication feature in mode 2 and 3. In mode 2 or 3, if SM2 is set to 1, then RI will not be activated if the received 9th data bit (RB8) is 0. In mode 1, if SM2 = 1, then RI will not be activated if a valid stop bit was not received. In mode 0, the SM2 bit controls the serial port clock. If set to 0, then the serial port runs at a divide by 12 clock of the oscillator. This gives compatibility with the standard 8052. When set to 1, the serial clock become divide by 4 of the oscillator clock. This results in faster synchronous serial communication. |

| 4   | REN    | Receive enable:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |        | Disable serial reception.     Enable serial reception.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3   | TB8    | This is the 9th bit to be transmitted in modes 2 and 3. This bit is set and cleared by software as desired.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2   | RB8    | In modes 2 and 3 this is the received 9th data bit. In mode 1, if SM2 = 0, RB8 is the stop bit that was received. In mode 0 it has no function.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1   | TI     | Transmit interrupt flag: This flag is set by hardware at the end of the 8th bit time in mode 0, or at the beginning of the stop bit in all other modes during serial transmission. This bit must be cleared by software.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0   | RI     | Receive interrupt flag: This flag is set by hardware at the end of the 8th bit time in mode 0, or halfway through the stop bits time in the other modes during serial reception. However the restrictions of SM2 apply to this bit. This bit can be cleared only by software.                                                                                                                                                                                                                                                                                                                                                                                   |

# SM1, SM0: Mode Select bits:

| Mode | SM0 | SM1 | Description  | Length | Baud Rate                |

|------|-----|-----|--------------|--------|--------------------------|

| 0    | 0   | 0   | Synchronous  | 8      | Tclk divided by 4 or 12  |

| 1    | 0   | 1   | Asynchronous | 10     | Variable                 |

| 2    | 1   | 0   | Asynchronous | 11     | Tclk divided by 32 or 64 |

| 3    | 1   | 1   | Asynchronous | 11     | Variable                 |

## **Serial Data Buffer**

| Bit: | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|------|--------|--------|--------|--------|--------|--------|--------|--------|

| ·    | SBUF.7 | SBUF.6 | SBUF.5 | SBUF.4 | SBUF.3 | SBUF.2 | SBUF.1 | SBUF.0 |

Mnemonic: SBUF Address: 99h

# 10 INSTRUCTION

The W78I054D/W78I052D/W78I051D series execute all the instructions of the standard 8052 family. The operations of these instructions, as well as their effects on flag and status bits, are exactly the same.

| Op-code        | HEX Code | Bytes | W78I054D/W78I052D/W<br>78I051D series Clock<br>cycles |

|----------------|----------|-------|-------------------------------------------------------|

| NOP            | 00       | 1     | 12                                                    |

| ADD A, R0      | 28       | 1     | 12                                                    |

| ADD A, R1      | 29       | 1     | 12                                                    |

| ADD A, R2      | 2A       | 1     | 12                                                    |

| ADD A, R3      | 2B       | 1     | 12                                                    |

| ADD A, R4      | 2C       | 1     | 12                                                    |

| ADD A, R5      | 2D       | 1     | 12                                                    |

| ADD A, R6      | 2E       | 1     | 12                                                    |

| ADD A, R7      | 2F       | 1     | 12                                                    |

| ADD A, @R0     | 26       | 1     | 12                                                    |

| ADD A, @R1     | 27       | 1     | 12                                                    |

| ADD A, direct  | 25       | 2     | 12                                                    |

| ADD A, #data   | 24       | 2     | 12                                                    |

| ADDC A, R0     | 38       | 1     | 12                                                    |

| ADDC A, R1     | 39       | 1     | 12                                                    |

| ADDC A, R2     | 3A       | 1     | 12                                                    |

| ADDC A, R3     | 3B       | 1     | 12                                                    |

| ADDC A, R4     | 3C       | 1     | 12                                                    |

| ADDC A, R5     | 3D       | 1     | 12                                                    |

| ADDC A, R6     | 3E       | 1     | 12                                                    |

| ADDC A, R7     | 3F       | 1     | 12                                                    |

| ADDC A, @R0    | 36       | 1     | 12                                                    |

| ADDC A, @R1    | 37       | 1     | 12                                                    |

| ADDC A, direct | 35       | 2     | 12                                                    |

| ADDC A, #data  | 34       | 2     | 12                                                    |

| SUBB A, R0     | 98       | 1     | 12                                                    |

| SUBB A, R1     | 99       | 1     | 12                                                    |

| SUBB A, R2     | 9A       | 1     | 12                                                    |

- 35 -

Each interrupt source can be individually programmed to one of 2 priority levels by setting or clearing bits in the IP registers. An interrupt service routine in progress can be interrupted by a higher priority interrupt, but not by another interrupt of the same or lower priority. The highest priority interrupt service cannot be interrupted by any other interrupt source. So, if two requests of different priority levels are received simultaneously, the request of higher priority level is serviced.

If requests of the same priority level are received simultaneously, an internal polling sequence determines which request is serviced. This is called the arbitration ranking. Note that the arbitration ranking is only used to resolve simultaneous requests of the same priority level.

Table below summarizes the interrupt sources, flag bits, vector addresses, enable bits, priority bits, arbitration ranking, and External interrupt may wake up the CPU from Power Down mode.

| Source                      | Flag       | Vector<br>address | Enable bit       | Interrupt<br>Priority | Flag cleared<br>by    | Arbitration ranking | Power-<br>down<br>wakeup |

|-----------------------------|------------|-------------------|------------------|-----------------------|-----------------------|---------------------|--------------------------|

| External Interrupt 0        | IE0        | 0003H             | EX0 (IE.0)       | IPH.0, IP.0           | Hardware,<br>software | 1(highest)          | Yes                      |

| Timer 0 Overflow            | TF0        | 000BH             | ET0 (IE.1)       | IPH.1, IP.1           | Hardware,<br>software | 2                   | No                       |

| External Interrupt 1        | IE1        | 0013H             | EX1 (IE.2)       | IPH.2, IP.2           | Hardware,<br>software | 3                   | Yes                      |

| Timer 1 Overflow            | TF1        | 001BH             | ET1 (IE.3)       | IPH.3, IP.3           | Hardware,<br>software | 4                   | No                       |

| Serial Port                 | RI +<br>TI | 0023H             | ES (IE.4)        | IPH.4, IP.4           | Software              | 5                   | No                       |

| Timer 2 Over-<br>flow/Match | TF2        | 002BH             | ET2 (IE.5)       | IPH.5, IP.5           | Software              | 6                   | No                       |

| External Interrupt 2        | IE2        | 0033H             | EX2<br>(XICON.2) | IPH.6,<br>PX2         | Hardware,<br>software | 7                   | Yes                      |

| External Interrupt 3        | IE3        | 003BH             | EX3<br>(XICON.6) | IPH.7,<br>PX3         | Hardware,<br>software | 8(lowest)           | Yes                      |

Table 13- 2 Summary of interrupt sources

## 13.5 Interrupt Response Time

The response time for each interrupt source depends on several factors, such as the nature of the interrupt and the instruction underway. In the case of external interrupts  $\overline{\text{INT0}}$  and  $\overline{\text{INT1}}$ , they are sampled at S5P2 of every machine cycle and then their corresponding interrupt flags IEx will be set or reset. The Timer 0 and 1 overflow flags are set at C3 of the machine cycle in which overflow has occurred. These flag values are polled only in the next machine cycle. If a request is active and all three conditions are met, then the hardware generated LCALL is executed. This LCALL itself takes four machine cycles to be completed. Thus there is a minimum time of five machine cycles between the interrupt flag being set and the interrupt service routine being executed.

A longer response time should be anticipated if any of the three conditions are not met. If a higher or equal priority is being serviced, then the interrupt latency time obviously depends on the nature of the

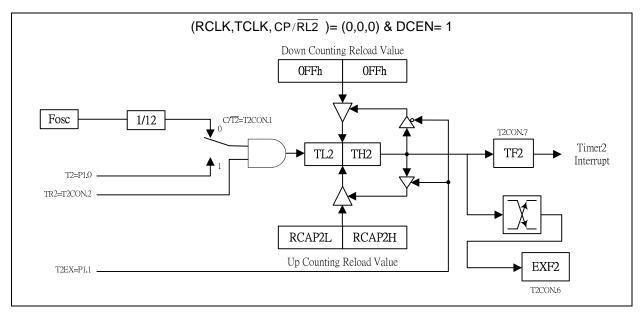

Figure 14- 6 16-Bit Auto-reload Mode, Counting Up

### 14.3.4 Baud Rate Generator Mode

The baud rate generator mode is enabled by setting either the RCLK or TCLK bits in T2CON register. While in the baud rate generator mode, Timer/Counter 2 is a 16 bit counter with auto reload when the count rolls over from 0FFFFh. However, rolling over does not set the TF2 bit. If EXEN2 bit is set, then a negative transition of the T2EX pin will set EXF2 bit in the T2CON register and cause an interrupt request.

Figure 14-7 Baud Rate Generator Mode

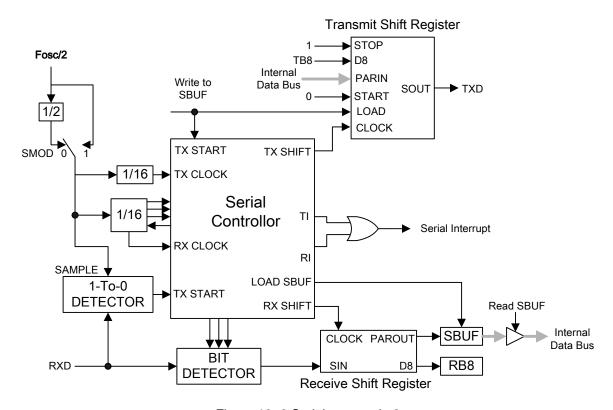

grammable to 1/32 or 1/64 of the oscillator frequency, which is determined by the SMOD bit in PCON SFR. Transmission begins with a write to SBUF. The serial data is brought out on to TxD pin at S6P2 following the first roll-over of the divide by 16 counter. The next bit is placed on TxD pin at S6P2 following the next rollover of the divide by 16 counter. Thus the transmission is synchronized to the divide by 16 counters, and not directly to the write to SBUF signal. After all 9 bits of data are transmitted, the stop bit is transmitted. The TI flag is set in the S6P2 state after the stop bit has been put out on TxD pin. This will be at the 11th rollover of the divide by 16 counters after a write to SBUF. Reception is enabled only if REN is high. The serial port actually starts the receiving of serial data, with the detection of a falling edge on the RxD pin. The 1-to-0 detector continuously monitors the RxD line, sampling it at the rate of 16 times the selected baud rate. When a falling edge is detected, the divide by 16 counters is immediately reset. This helps to align the bit boundaries with the rollovers of the divide by 16 counters. The 16 states of the counter effectively divide the bit time into 16 slices. The bit detection is done on a best of three basis. The bit detector samples the RxD pin, at the 8th, 9th and 10th counter states. By using a majority 2 of 3 voting system, the bit value is selected. This is done to improve the noise rejection feature of the serial port.

Figure 16-3 Serial port mode 2

If the first bit detected after the falling edge of RxD pin, is not 0, then this indicates an invalid start bit, and the reception is immediately aborted. The serial port again looks for a falling edge in the RxD line. If a valid start bit is detected, then the rest of the bits are also detected and shifted into the SBUF. After shifting in 9 data bits, there is one more shift to do, after which the SBUF and RB8 are loaded and RI is set. However certain conditions must be met before the loading and setting of RI can be done.

- 1. RI must be 0 and

- 2. Either SM2 = 0, or the received stop bit = 1.

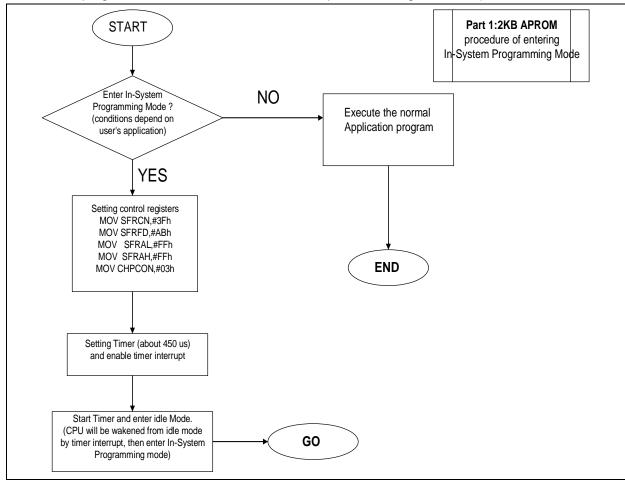

# 18 ISP(IN-SYSTEM PROGRAMMING)

ISP is the ability of program MCU to be programmed while F/W code in AP-ROM or LD-ROM. (Note: Timer 0 for program, erase, read on ISP mode. ISP operation voltage 3.3- 5.5V)

- 63 -

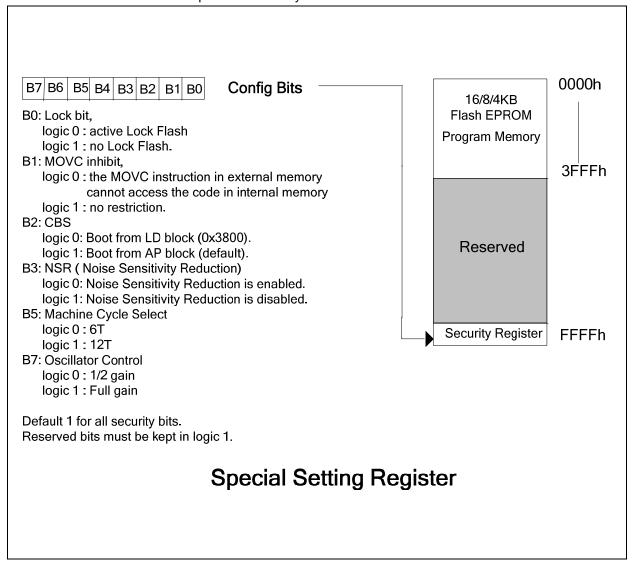

## 19 CONFIG BITS

During the on-chip Flash EPROM operation mode, the Flash EPROM can be programmed and verified repeatedly. Until the code inside the Flash EPROM is confirmed OK, the code can be protected. The protection of Flash EPROM and those operations on it are described below.

The W78I054D/W78I052D/W78I051D has a Special Setting Register, the config Bits, which can not be accessed in normal mode. The Security register can only be accessed from the Flash EPROM operation mode. Those bits of the Security Registers can not be changed once they have been programmed from high to low. They can only be reset through erase-all operation. The Security Register is addressed in the Flash EPROM operation mode by address #0FFFFh.

- 67 -

# 21 ELECTRICAL CHARACTERISTICS

# 21.1 Absolute Maximum Ratings

| SYMBOL                                                    | PARAMETER       | Min                  | MAX                  | UNIT |

|-----------------------------------------------------------|-----------------|----------------------|----------------------|------|

| DC Power Supply                                           | $V_{DD}-V_{SS}$ | 2.4                  | 5.5                  | V    |

| Input Voltage                                             | V <sub>IN</sub> | V <sub>SS</sub> -0.3 | V <sub>DD</sub> +0.3 | V    |

| Operating Temperature<br>(W78I054D/W78I052D/W78I0<br>51D) | T <sub>A</sub>  | -40                  | +85                  | °C   |

Note: Exposure to conditions beyond those listed under absolute maximum ratings may adversely affects the lift and reliability of the device.

3. There are no duty cycle requirements on the XTAL1 input.

# 21.3.2 Program Fetch Cycle

| PARAMETER                  | SYMBOL | MIN.         | TYP.  | MAX.  | UNIT | NOTES |

|----------------------------|--------|--------------|-------|-------|------|-------|

| Address Valid to ALE Low   | Taas   | 1 TCP -<br>Δ | -     | -     | nS   | 4     |

| Address Hold from ALE Low  | Taah   | 1 TCP -<br>Δ | -     | -     | nS   | 1, 4  |

| ALE Low to PSEN Low        | Tapl   | 1 TCP -<br>Δ | -     | -     | nS   | 4     |

| PSEN Low to Data Valid     | Tpda   | -            | -     | 2 TCP | nS   | 2     |

| Data Hold after PSEN High  | Tpdh   | 0            | -     | 1 TCP | nS   | 3     |

| Data Float after PSEN High | Tpdz   | 0            | -     | 1 TCP | nS   |       |

| ALE Pulse Width            | Talw   | 2 TCP -<br>Δ | 2 TCP | -     | nS   | 4     |

| PSEN Pulse Width           | Tpsw   | 3 TCP -<br>Δ | 3 TCP | -     | nS   | 4     |

## Notes:

- 1. P0.0–P0.7, P2.0–P2.7 remain stable throughout entire memory cycle.

- 2. Memory access time is 3 TCP.

- 3. Data have been latched internally prior to PSEN going high.

- 4. " $\Delta$ " (due to buffer driving delay and wire loading) is 20 nS.

# 21.3.3 Data Read Cycle

| PARAMETER               | SYMBOL | MIN.     | TYP.  | MAX.     | UNIT | NOTES |

|-------------------------|--------|----------|-------|----------|------|-------|

| ALE Low to RD Low       | Tdar   | 3 TCP -∆ | -     | 3 TCP +∆ | nS   | 1, 2  |

| RD Low to Data Valid    | Tdda   | -        | -     | 4 TCP    | nS   | 1     |

| Data Hold from RD High  | Tddh   | 0        | -     | 2 TCP    | nS   |       |

| Data Float from RD High | Tddz   | 0        | -     | 2 TCP    | nS   |       |

| RD Pulse Width          | Tdrd   | 6 TCP -Δ | 6 TCP | -        | nS   | 2     |

### Notes:

- 1. Data memory access time is 8 TCP.

- 2. "\(\Delta\)" (due to buffer driving delay and wire loading) is 20 nS.

# 21.3.4 Data Write Cycle

| PARAMETER              | SYMBOL | MIN.     | TYP.  | MAX.     | UNIT |

|------------------------|--------|----------|-------|----------|------|

| ALE Low to WR Low      | Tdaw   | 3 TCP -∆ | -     | 3 TCP +∆ | nS   |

| Data Valid to WR Low   | Tdad   | 1 TCP -Δ | -     | -        | nS   |

| Data Hold from WR High | Tdwd   | 1 TCP -Δ | -     | -        | nS   |

| WR Pulse Width         | Tdwr   | 6 TCP -Δ | 6 TCP | -        | nS   |

Note: " $\Delta$ " (due to buffer driving delay and wire loading) is 20 nS.

# 21.3.5 Port Access Cycle

| PARAMETER                    | SYMBOL | MIN.  | TYP. | MAX. | UNIT |

|------------------------------|--------|-------|------|------|------|

| Port Input Setup to ALE Low  | Tpds   | 1 TCP | 1    | -    | nS   |

| Port Input Hold from ALE Low | Tpdh   | 0     | -    | -    | nS   |

| Port Output to ALE           | Tpda   | 1 TCP | ı    | -    | nS   |

Note: Ports are read during S5P2, and output data becomes available at the end of S6P2. The timing data are referenced to

ALE, since it provides a convenient reference.

## 21.3.6 Program Operation

| PARAMETER                                    | Symbol | Min. | TYP. | Max. | Unit |

|----------------------------------------------|--------|------|------|------|------|

| VPP Setup Time                               | TVPS   | 2.0  | -    | -    | μS   |

| Data Setup Time                              | TDS    | 2.0  | -    | -    | μS   |

| Data Hold Time                               | TDH    | 2.0  | -    | -    | μS   |

| Address Setup Time                           | TAS    | 2.0  | -    | -    | μS   |

| Address Hold Time                            | TAH    | 0    | -    | -    | μS   |

| CE Program Pulse Width for Program Operation | TPWP   | 290  | 300  | 310  | μS   |

| OECTRL Setup Time                            | TOCS   | 2.0  | -    | -    | μS   |

| OECTRL Hold Time                             | TOCH   | 2.0  | -    | -    | μS   |

| OE Setup Time                                | TOES   | 2.0  | -    | -    | μS   |

| OE High to Output Float                      | TDFP   | 0    | -    | 130  | nS   |

| Data Valid from OE                           | TOEV   | -    | -    | 150  | nS   |

Note: Flash data can be accessed only in flash mode. The RST pin must pull in VIH status, the ALE pin must pull in VIL status, and the PSEN pin must pull in VIH status.

# nuvoTon

```

CHPCON, #00000011b

mov

TF0

clr

c1r

TRO

A.SFRFD

; read device id high byte

mov

; * read device ID low

Read_Device_ID_LOW:

mov

SFRAL, #0FEh

SFRAH, #0FFh

mov

SFRCN, #READ_DID

mov

TLO, #LOW (65536-READ_TIME)

mov

THO, #HIGH(65536-READ_TIME)

mov

TR0

setb

mov

CHPCON, #00000011b

clr

TF0

c1r

TRO

A.SFRFD

; read device id low byte

mov

ret

;* Flash standby mode

Standby:

SFRCN, #FLASH STANDBY

mov

SFRFD,#0FFh

mov

mov

SFRAL, #0FFh

SFRAH, #0FFh

mov

setb

TRO

CHPCON, #00000011b

mov

clr

TF0

clr

TR0

Erase APROM

Erase_APROM:

EAPAGE,#01h

;set EAPAGE is APROM

mov

SFRCN, #ERASE_ROM

mov

```

# nuvoTon

```

SFRCN, #PROGRAM_ROM

mov

DPTR,#0000h

mov

A,#055h

mov

wr_lp:

THO, #HIGH(65536-PROGRAM_TIME)

mov

TLO, #LOW (65536-PROGRAM_TIME)

mov

SFRFD, A

mov

SFRAL, DPL

mov

mov

SFRAH, DPH

setb

TR0

CHPCON, #00000011b

mov

clr

TF0

TR0

clr

cpl

Α

inc

DPTR

mov

RO, DPL

RO, #LOW (APROM_END_ADDRESS), wr_1p

cjne

mov

R1,DPH

cjne

R1, #HIGH(APROM_END_ADDRESS), wr_lp

ret

;*Program Verify APROM BANK, read APROM 55h,AAh,55h,AAh......

Program_Verify_APROM:

SFRCN, #PROGRAM VERIFY ROM

mov

DPTR,#0000h

mov

mov

B,#055h

rd_lp:

THO, #HIGH(65536-READ_TIME)

mov

TLO, #LOW (65536-READ_TIME)

mov

SFRAL, DPL

mov

SFRAH, DPH

mov

setb

TR0

mov

CHPCON, #00000011b

TF0

clr

TR0

clr

mov

A, SFRFD

A,B,Program_Fail

cine

A.B

mov

```