Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detano                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | SH-2                                                                            |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | SCI                                                                             |

| Peripherals                | POR, PWM, WDT                                                                   |

| Number of I/O              | 63                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                       |

| Data Converters            | A/D 12x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-LQFP                                                                        |

| Supplier Device Package    | 100-LFQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/de71494rn80fpv |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|       | 9.4.2    | CSn Space Bus Control Register (CSnBCR) (n = 0 and 1)        |  |

|-------|----------|--------------------------------------------------------------|--|

|       | 9.4.3    | CSn Space Wait Control Register (CSnWCR) (n = 0 and 1)       |  |

|       | 9.4.4    | Bus Function Extending Register (BSCEHR)                     |  |

| 9.5   | Operatio | n                                                            |  |

|       | 9.5.1    | Endian/Access Size and Data Alignment                        |  |

|       | 9.5.2    | Normal Space Interface                                       |  |

|       | 9.5.3    | Access Wait Control                                          |  |

|       | 9.5.4    | CSn Assert Period Extension                                  |  |

|       | 9.5.5    | Wait between Access Cycles                                   |  |

|       | 9.5.6    | Bus Arbitration                                              |  |

|       | 9.5.7    | Others                                                       |  |

|       | 9.5.8    | Access to On-Chip FLASH and On-Chip RAM by CPU               |  |

|       | 9.5.9    | Access to On-Chip Peripheral I/O Registers by CPU            |  |

|       | 9.5.10   | Access to External Memory by CPU                             |  |

|       |          |                                                              |  |

| Secti | on 10 M  | Iulti-Function Timer Pulse Unit 2 (MTU2)                     |  |

| 10.1  | Features |                                                              |  |

| 10.2  | Input/Ou | ıtput Pins                                                   |  |

| 10.3  | Register | Descriptions                                                 |  |

|       | 10.3.1   | Timer Control Register (TCR)                                 |  |

|       | 10.3.2   | Timer Mode Register (TMDR)                                   |  |

|       | 10.3.3   | Timer I/O Control Register (TIOR)                            |  |

|       | 10.3.4   | Timer Compare Match Clear Register (TCNTCMPCLR)              |  |

|       | 10.3.5   | Timer Interrupt Enable Register (TIER)                       |  |

|       | 10.3.6   | Timer Status Register (TSR)                                  |  |

|       | 10.3.7   | Timer Buffer Operation Transfer Mode Register (TBTM)         |  |

|       | 10.3.8   | Timer Input Capture Control Register (TICCR)                 |  |

|       | 10.3.9   | Timer Synchronous Clear Register (TSYCR)                     |  |

|       | 10.3.10  | Timer A/D Converter Start Request Control Register (TADCR)   |  |

|       | 10.3.11  | Timer A/D Converter Start Request Cycle Set Registers        |  |

|       |          | (TADCORA_4 and TADCORB_4)                                    |  |

|       | 10.3.12  | Timer A/D Converter Start Request Cycle Set Buffer Registers |  |

|       |          | (TADCOBRA_4 and TADCOBRB_4)                                  |  |

|       | 10.3.13  | Timer Counter (TCNT)                                         |  |

|       | 10.3.14  | Timer General Register (TGR)                                 |  |

|       | 10.3.15  | Timer Start Register (TSTR)                                  |  |

|       | 10.3.16  | Timer Synchronous Register (TSYR)                            |  |

|       | 10.3.17  | Timer Counter Synchronous Start Register (TCSYSTR)           |  |

|       | 10.3.18  | Timer Read/Write Enable Register (TRWER)                     |  |

|       | 10.3.19  | Timer Output Master Enable Register (TOER)                   |  |

| Items                                                                                               | Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| On-chip ROM                                                                                         | 256 kbytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| On-chip RAM                                                                                         | 8 kbytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Bus state controller<br>(BSC)                                                                       | Address space: A maximum 64 Mbytes for each of two areas (CS0 and CS1) (only in SH7149)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                     | 8-bit external bus (only in SH7149)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                     | 16-bit external bus (only in SH7149)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                     | The following features settable for each area independently                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                     | — Bus size (8 or 16 bits)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                     | <ul> <li>Number of access wait cycles</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                     | — Idle wait cycle insertion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                     | — Supports SRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                     | Outputs a chip select signal according to the target area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

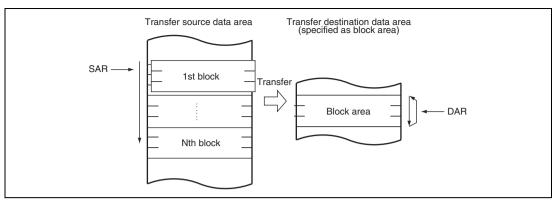

| Data transfer<br>controller (DTC)<br>(only in F-ZTAT<br>version)                                    | <ul> <li>Data transfer activated by an on-chip peripheral module interrupt can be done independently of the CPU transfer.</li> <li>Transfer mode selectable for each interrupt source (transfer mode is specified in memory)</li> <li>Multiple data transfer enabled for one activation source</li> <li>Various transfer modes <ul> <li>Normal mode, repeat mode, or block transfer mode can be selected.</li> </ul> </li> <li>Data transfer size can be specified as byte, word, or longword</li> <li>The interrupt that activated the DTC can be issued to the CPU. <ul> <li>A CPU interrupt can be requested after one data transfer completion.</li> </ul> </li> </ul> |

| Interrupt controller                                                                                | • Five external interrupt pins (NMI and IRQ3 to IRQ0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| (INTC)                                                                                              | On-chip peripheral interrupts: Priority level set for each module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                     | Vector addresses: A vector address for each interrupt source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| User debugging<br>interface (H-UDI)<br>(only in F-ZTAT<br>version)                                  | E10A emulator support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Advanced user<br>debugger (AUD)<br>(only in F-ZTAT<br>version supporting full<br>functions of E10A) | E10A emulator support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

## 7.3.11 Break Control Register (BRCR)

BRCR sets the following conditions:

- 1. Channels A and B are used in two independent channel conditions or under the sequential condition.

- 2. A user break is set before or after instruction execution.

- 3. Specify whether to include the number of execution times on channel B in comparison conditions.

- 4. Determine whether to include data bus on channels A and B in comparison conditions.

- 5. Enable PC trace.

- 6. Select the UBCTRG output pulse width.

- 7. Specify whether to request the user break interrupt when channels A and B match with comparison conditions.

BRCR is a 32-bit readable/writable register that has break conditions match flags and bits for setting a variety of break conditions.

| Bit:           | 31         | 30         | 29          | 28          | 27    | 26   | 25 | 24 | 23    | 22   | 21    | 20     | 19    | 18 | 17    | 16    |

|----------------|------------|------------|-------------|-------------|-------|------|----|----|-------|------|-------|--------|-------|----|-------|-------|

|                | -          | -          | -           | -           | -     | -    | -  | -  | -     | -    | UTRG  | W[1:0] | UBIDB | -  | UBIDA | -     |

| Initial value: | 0          | 0          | 0           | 0           | 0     | 0    | 0  | 0  | 0     | 0    | 0     | 0      | 0     | 0  | 0     | 0     |

| R/W:           | R          | R          | R           | R           | R     | R    | R  | R  | R     | R    | R/W   | R/W    | R/W   | R  | R/W   | R     |

|                |            |            |             |             |       |      |    |    |       |      |       |        |       |    |       |       |

| Bit:           | 15         | 14         | 13          | 12          | 11    | 10   | 9  | 8  | 7     | 6    | 5     | 4      | 3     | 2  | 1     | 0     |

|                | SCM<br>FCA | SCM<br>FCB | SCM<br>FDA* | SCM<br>FDB* | PCTE* | PCBA | -  | -  | DBEA* | PCBB | DBEB* | -      | SEQ*  | -  | -     | ETBE* |

| Initial value: | 0          | 0          | 0           | 0           | 0     | 0    | 0  | 0  | 0     | 0    | 0     | 0      | 0     | 0  | 0     | 0     |

| R/W:           | R/W        | R/W        | R/W         | R/W         | R/W   | R/W  | R  | R  | R/W   | R/W  | R/W   | R      | R/W   | R  | R     | R/W   |

Note: \* In the masked ROM version, this bit is used as a reserved bit. This bit is always read as 0. The write value should always be 0.

RENESAS

#### 8.5.6 Chain Transfer

Setting the CHNE bit in MRB to 1 enables a number of data transfers to be performed consecutively in response to a single transfer request. Setting the CHNE and CHNS bits in MRB set to 1 enables a chain transfer only when the transfer counter reaches 0. SAR, DAR, CRA, CRB, MRA, and MRB, which define data transfers, can be set independently. Figure 8.9 shows the chain transfer operation.

In the case of transfer with CHNE set to 1, an interrupt request to the CPU is not generated at the end of the specified number of transfers or by setting the DISEL bit to 1, and the interrupt source flag for the activation source and DTCER are not affected.

In repeat transfer mode, setting the RCHNE bit in DTCCR and the CHNE and CHNS bits in MRB to 1 enables a chain transfer after transfer with transfer counter = 1 has been completed.

|     |          | Initial |     | <b>_</b>                                                                                                                                                                                                 |

|-----|----------|---------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Bit Name | Value   | R/W | Description                                                                                                                                                                                              |

| 11  | DTBST    | 0       | R/W | DTC Burst Enable                                                                                                                                                                                         |

|     |          |         |     | Selects whether or not the DTC retains the bus<br>mastership and remains continuously active until all<br>transfer operations are complete when multiple DTC<br>activation requests have been generated. |

|     |          |         |     | 0: Release the bus on the completion of transfer for each individual DTC activation source.                                                                                                              |

|     |          |         |     | <ol> <li>Keep the DTC continuously active, i.e. only release<br/>the bus on completion of processing for all DTC<br/>activation sources.</li> </ol>                                                      |

|     |          |         |     | Notes: When this bit is set to 1, the following restrictions apply.                                                                                                                                      |

|     |          |         |     | <ol> <li>Clock setting with the frequency control register<br/>(FRQCR) must be lφ: Bφ: Pφ: Mlφ: MPφ: = 8: 4:<br/>4: 4: 4, 4: 2: 2: 2: 2, or 2: 1: 1: 1: 1</li> </ol>                                     |

|     |          |         |     | <ol><li>The vector information must be in on-chip ROM<br/>or on-chip RAM.</li></ol>                                                                                                                      |

|     |          |         |     | 3. The transfer information must be in on-chip RAM.                                                                                                                                                      |

|     |          |         |     | <ol> <li>Transfer must be between the on-chip RAM<br/>and an on-chip peripheral module or between<br/>external memory and an on-chip peripheral<br/>module.</li> </ol>                                   |

| 10  | DTSA     | 0       | R/W | DTC Short Address Mode                                                                                                                                                                                   |

|     |          |         |     | In this mode, the information that specifies a DTC transfer takes up only 3 longwords.                                                                                                                   |

|     |          |         |     | 0: Transfer information is read out as 4 longwords. The transfer information is arranged as shown in figure 8.2 (normal address mode).                                                                   |

|     |          |         |     | 1: Transfer information is read out as 3 longwords. The transfer information is arranged as shown in figure 8.2 (short address mode).                                                                    |

|     |          |         |     | Note: Transfer in short address mode is only available<br>between on-chip peripheral modules and on-chip<br>RAM, because the higher-order 8 bits of the SAR<br>and DAR are considered to be all 1.       |

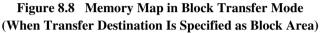

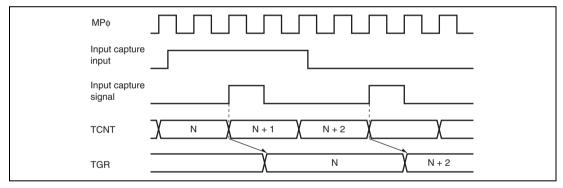

## **Input Capture Function:**

The TCNT value can be transferred to TGR on detection of the TIOC pin input edge.

Rising edge, falling edge, or both edges can be selected as the detected edge. For channels 0 and 1, it is also possible to specify another channel's counter input clock or compare match signal as the input capture source.

- Note: When another channel's counter input clock is used as the input capture input for channels 0 and 1, MP $\phi/1$  should not be selected as the counter input clock used for input capture input. Input capture will not be generated if MP $\phi/1$  is selected.

- Example of Input Capture Operation Setting Procedure Figure 10.10 shows an example of the input capture operation setting procedure.

Figure 10.10 Example of Input Capture Operation Setting Procedure

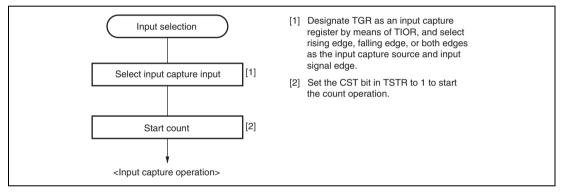

Note: This function must be used in combination with interrupt skipping. When interrupt skipping is disabled (the T3AEN and T4VEN bits in the timer interrupt skipping set register (TITCR) are cleared to 0 or the skipping count set bits (3ACOR and 4VCOR) in TITCR are cleared to 0), make sure that A/D converter start requests are not linked with interrupt skipping (clear the ITA3AE, ITA4VE, ITB3AE, and ITB4VE bits in the timer A/D converter start request control register (TADCR) to 0).

Figure 10.81 Example of A/D Converter Start Request Signal (TRG4AN) Operation Linked with Interrupt Skipping

| MP¢ _                   |           |

|-------------------------|-----------|

| TCNT input<br>clock     |           |

| TCNT                    | N X N + 1 |

| TGR _                   | Ν         |

| Compare<br>match signal |           |

| TIOC pin                | χ         |

## Figure 10.98 Output Compare Output Timing (Complementary PWM Mode/Reset Synchronous PWM Mode)

Input Capture Signal Timing: Figure 10.99 shows input capture signal timing.

Figure 10.99 Input Capture Input Signal Timing

## **13.5** Interrupt Source

The WDT has one interrupt source: the interval timer interrupt (ITI).

Table 13.3 shows this interrupt source. An interval timer interrupt (ITI) is generated when the interval timer overflow flag bit (IOVF) in the watchdog timer control status register (WTSCR) is set to 1.

The interrupt request is canceled by clearing the interrupt flag to 0.

#### Table 13.3 Interrupt Source

| Name | Interrupt Source         | Interrupt Enable Bit | Interrupt Flag Bit                  |

|------|--------------------------|----------------------|-------------------------------------|

| ITI  | Interval timer interrupt | _                    | Interval timer overflow flag (IOVF) |

## 13.6 Usage Note

#### 13.6.1 WTCNT Setting Value

If WTCNT is set to H'FF in interval timer mode, overflow does not occur when WTCNT changes from H'FF to H'00 after one cycle of count clock, but overflow occurs when WTCNT changes from H'FF to H'00 after 257 cycles of count clock.

If WTCNT is set to H'FF in watchdog timer mode, overflow occurs when WTCNT changes from H'FF to H'00 after one cycle of count clock.

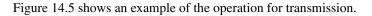

Figure 14.5 Example of Transmission in Asynchronous Mode (8-Bit Data, Parity, One Stop Bit)

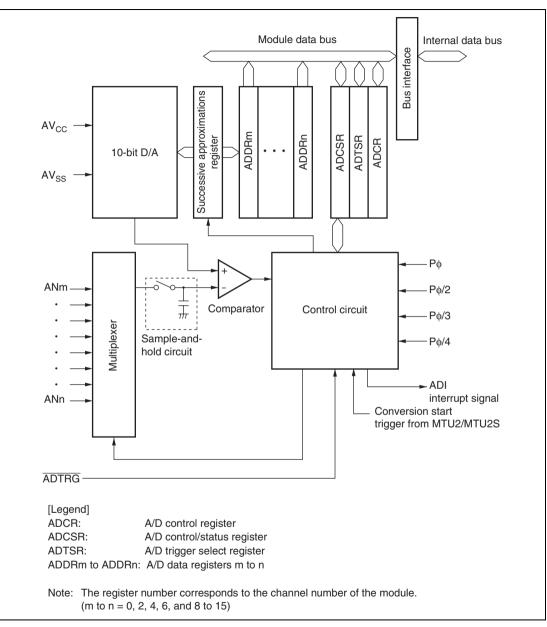

Figure 15.1 Block Diagram of A/D Converter (for One Module)

| Bit     | Bit Name    | Initial<br>Value | R/W | Description                                                                                                                                                                                                                  |

|---------|-------------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11 to 8 | TRG01S[3:0] | 0000             | R/W | A/D Trigger 0 Group 1 Select 3 to 0                                                                                                                                                                                          |

|         |             |                  |     | Select an external trigger, MTU2 trigger, or MTU2S trigger to start A/D conversion for group 1 when A/D module 0 is in 2-channel scan mode.                                                                                  |

|         |             |                  |     | 0000: External trigger pin (ADTRG) input                                                                                                                                                                                     |

|         |             |                  |     | 0001: TGRA input capture/compare match for each<br>MTU2 channel or TCNT_4 trough in<br>complementary PWM mode (TRGAN)                                                                                                        |

|         |             |                  |     | 0010: MTU2 CH0 compare match (TRG0N)                                                                                                                                                                                         |

|         |             |                  |     | 0011: MTU2 A/D conversion start request delaying<br>(TRG4AN)                                                                                                                                                                 |

|         |             |                  |     | 0100: MTU2 A/D conversion start request delaying<br>(TRG4BN)                                                                                                                                                                 |

|         |             |                  |     | 0101: TGRA input capture/compare match on each<br>MTU2S channel or TCNT_4 trough in<br>complementary PWM mode (TRGAN)                                                                                                        |

|         |             |                  |     | 0110: Setting prohibited                                                                                                                                                                                                     |

|         |             |                  |     | 0111: MTU2S A/D conversion start request delaying<br>(TRG4AN)                                                                                                                                                                |

|         |             |                  |     | 1000: MTU2S A/D conversion start request delaying<br>(TRG4BN)                                                                                                                                                                |

|         |             |                  |     | 1001: Setting prohibited                                                                                                                                                                                                     |

|         |             |                  |     | 101x: Setting prohibited                                                                                                                                                                                                     |

|         |             |                  |     | 11xx: Setting prohibited                                                                                                                                                                                                     |

|         |             |                  |     | When switching the selector, first clear the ADST bit in the A/D control register (ADCR) to 0.                                                                                                                               |

|         |             |                  |     | Specify different trigger sources for the group 0 and<br>group 1 conversion requests so that a group 0<br>conversion request is not generated simultaneously<br>with a group 1 conversion request in 2-channel scan<br>mode. |

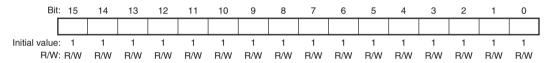

## 16.2.3 Compare Match Counter (CMCNT)

CMCNT is a 16-bit register used as an up-counter. When the counter input clock is selected with bits CKS1 and CKS0 in CMCSR and the STR bit in CMSTR is set to 1, CMCNT starts counting using the selected clock.

When the value in CMCNT and the value in compare match constant register (CMCOR) match, CMCNT is cleared to H'0000 and the CMF flag in CMCSR is set to 1.

| Bit: 15          | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|                  |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Initial value: 0 | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W: R/W         | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

The initial value of CMCNT is H'0000.

## 16.2.4 Compare Match Constant Register (CMCOR)

CMCOR is a 16-bit register that sets the interval up to a compare match with CMCNT.

The initial value of CMCOR is H'FFFF.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                       |

|-----|----------|------------------|-----|-------------------------------------------------------------------|

| 3   | _        | 0                | R   | Reserved                                                          |

|     |          |                  |     | This bit is always read as 0. The write value should always be 0. |

| 2   | PB4MD2   | 0                | R/W | PB4 Mode                                                          |

| 1   | PB4MD1   | 0                | R/W | Select the function of the                                        |

| 0   | PB4MD0   | 0                | R/W | PB4/A18/IRQ2/POE4/TIC5US pin.                                     |

|     |          |                  |     | 000: PB4 I/O (port)                                               |

|     |          |                  |     | 001: IRQ2 input (INTC)                                            |

|     |          |                  |     | 011: TIC5US input (MTU2S)                                         |

|     |          |                  |     | 101: A18 output (BSC)*                                            |

|     |          |                  |     | 111: POE4 input (POE)                                             |

|     |          |                  |     | Other than above: Setting prohibited                              |

Note: \* This function is enabled only in the on-chip ROM enabled/disabled external-extension mode. Do not set 1 in single-chip mode.

## • Port B Control Register L1 (PBCRL1)

| Bit:           | 15 | 14         | 13         | 12         | 11 | 10         | 9          | 8          | 7 | 6          | 5          | 4          | 3 | 2          | 1          | 0          |

|----------------|----|------------|------------|------------|----|------------|------------|------------|---|------------|------------|------------|---|------------|------------|------------|

|                | -  | PB3<br>MD2 | PB3<br>MD1 | PB3<br>MD0 | -  | PB2<br>MD2 | PB2<br>MD1 | PB2<br>MD0 | - | PB1<br>MD2 | PB1<br>MD1 | PB1<br>MD0 | - | PB0<br>MD2 | PB0<br>MD1 | PB0<br>MD0 |

| Initial value: | 0  | 0*         | 0          | 0*         | 0  | 0*         | 0          | 0*         | 0 | 0          | 0          | 0          | 0 | 0          | 0          | 0          |

| R/W:           | R  | R/W        | R/W        | R/W        | R  | R/W        | R/W        | R/W        | R | R/W        | R/W        | R/W        | R | R/W        | R/W        | R/W        |

Note: \* The initial value is 1 in the on-chip ROM disabled external-extension mode.

|     |          | Initial                 |     |                                                                   |

|-----|----------|-------------------------|-----|-------------------------------------------------------------------|

| Bit | Bit Name | Value                   | R/W | Description                                                       |

| 15  | —        | 0                       | R   | Reserved                                                          |

|     |          |                         |     | This bit is always read as 0. The write value should always be 0. |

| 14  | PB3MD2   | <b>0</b> * <sup>1</sup> | R/W | PB3 Mode                                                          |

| 13  | PB3MD1   | 0                       | R/W | Select the function of the PB3/A17/IRQ1/POE1/TIC5V                |

| 12  | PB3MD0   | <b>0</b> * <sup>1</sup> | R/W | pin.                                                              |

|     |          |                         |     | 000: PB3 I/O (port)                                               |

|     |          |                         |     | 001: IRQ1 input (INTC)                                            |

|     |          |                         |     | 010: POE1 input (POE)                                             |

|     |          |                         |     | 011: TIC5V input (MTU2)                                           |

|     |          |                         |     | 101: A17 output (BSC)* <sup>2</sup>                               |

|     |          |                         |     | Other than above: Setting prohibited                              |

#### • PBDRH

| Bit           | : 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2          | 1          | 0          |

|---------------|------|----|----|----|----|----|---|---|---|---|---|---|---|------------|------------|------------|

|               | -    | -  | -  | -  | -  | -  | - | - | - | - | - | - | - | PB18<br>DR | PB17<br>DR | PB16<br>DR |

| Initial value | : 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0          | 0          | 0          |

| R/W           | : R  | R  | R  | R  | R  | R  | R | R | R | R | R | R | R | R/W        | R/W        | R/W        |

| Bit     | Bit Name | Initial<br>Value | R/W | Description                                                          |

|---------|----------|------------------|-----|----------------------------------------------------------------------|

| 15 to 3 | _        | All 0            | R   | Reserved                                                             |

|         |          |                  |     | These bits are always read as 0. The write value should always be 0. |

| 2       | PB18DR   | 0                | R/W | See table 18.4.                                                      |

| 1       | PB17DR   | 0                | R/W | _                                                                    |

| 0       | PB16DR   | 0                | R/W |                                                                      |

#### • PBDRL (SH7146)

| Bit:           | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5         | 4         | 3         | 2         | 1 | 0 |

|----------------|----|----|----|----|----|----|---|---|---|---|-----------|-----------|-----------|-----------|---|---|

| [              | -  | -  | -  | -  | -  | -  | - | - | - | - | PB5<br>DR | PB4<br>DR | PB3<br>DR | PB2<br>DR | - | - |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0         | 0         | 0         | 0         | 0 | 0 |

| R/W:           | R  | R  | R  | R  | R  | R  | R | R | R | R | R/W       | R/W       | R/W       | R/W       | R | R |

| Bit     | Bit Name | Initial<br>Value | R/W | Description                                                          |

|---------|----------|------------------|-----|----------------------------------------------------------------------|

| 15 to 6 |          | All 0            | R   | Reserved                                                             |

|         |          |                  |     | These bits are always read as 0. The write value should always be 0. |

| 5       | PB5DR    | 0                | R/W | See table 18.4.                                                      |

| 4       | PB4DR    | 0                | R/W | _                                                                    |

| 3       | PB3DR    | 0                | R/W | _                                                                    |

| 2       | PB2DR    | 0                | R/W | _                                                                    |

| 1, 0    |          | All 0            | R   | Reserved                                                             |

|         |          |                  |     | These bits are always read as 0. The write value should always be 0. |

| Block Name          | RAMS                                                                                                                  | RAM2                                                                                                                                                                                                                                                                                | RAM1                                                                                                                                                                                                                                                                                                                 | RAM0                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAM area (4 kbytes) | 0                                                                                                                     | х                                                                                                                                                                                                                                                                                   | х                                                                                                                                                                                                                                                                                                                    | х                                                                                                                                                                                                                                                                                                                                                                                    |

| EB0 (4 kbytes)      | 1                                                                                                                     | 0                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                    |

| EB1 (4 kbytes)      | 1                                                                                                                     | 0                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                    |

| EB2 (4 kbytes)      | 1                                                                                                                     | 0                                                                                                                                                                                                                                                                                   | 1                                                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                    |

| EB3 (4 kbytes)      | 1                                                                                                                     | 0                                                                                                                                                                                                                                                                                   | 1                                                                                                                                                                                                                                                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                    |

| EB4 (4 kbytes)      | 1                                                                                                                     | 1                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                    |

| EB5 (4 kbytes)      | 1                                                                                                                     | 1                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                    |

| EB6 (4 kbytes)      | 1                                                                                                                     | 1                                                                                                                                                                                                                                                                                   | 1                                                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                    |

| EB7 (4 kbytes)      | 1                                                                                                                     | 1                                                                                                                                                                                                                                                                                   | 1                                                                                                                                                                                                                                                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                    |

|                     | RAM area (4 kbytes)EB0 (4 kbytes)EB1 (4 kbytes)EB2 (4 kbytes)EB3 (4 kbytes)EB4 (4 kbytes)EB5 (4 kbytes)EB6 (4 kbytes) | RAM area (4 kbytes)       0         EB0 (4 kbytes)       1         EB1 (4 kbytes)       1         EB2 (4 kbytes)       1         EB3 (4 kbytes)       1         EB4 (4 kbytes)       1         EB5 (4 kbytes)       1         EB5 (4 kbytes)       1         EB6 (4 kbytes)       1 | RAM area (4 kbytes)       0       x         EB0 (4 kbytes)       1       0         EB1 (4 kbytes)       1       0         EB2 (4 kbytes)       1       0         EB3 (4 kbytes)       1       0         EB4 (4 kbytes)       1       1         EB5 (4 kbytes)       1       1         EB6 (4 kbytes)       1       1 | RAM area (4 kbytes)       0       x       x         EB0 (4 kbytes)       1       0       0         EB1 (4 kbytes)       1       0       0         EB2 (4 kbytes)       1       0       1         EB3 (4 kbytes)       1       0       1         EB4 (4 kbytes)       1       1       0         EB5 (4 kbytes)       1       1       0         EB6 (4 kbytes)       1       1       1 |

## Table 19.7 Overlapping of RAM Area and User MAT Area

Note: x: Don't care.

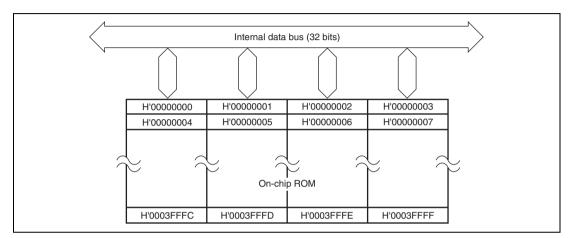

# Section 20 Masked ROM

This LSI is available with 256 kbytes of on-chip masked ROM. The on-chip ROM is connected to the CPU and data transfer controller (DTC) through a 32-bit data bus (figure 20.1). The CPU and DTC can access the on-chip ROM in 8, 16, and 32-bit widths. Data in the on-chip ROM can always be accessed from the CPU in one cycle.

Figure 20.1 Masked ROM Block Diagram

The operating mode determines whether the on-chip ROM is valid or not. The operating mode is selected using mode-setting pins FWE, MD1, and MD0. If you are using the on-chip ROM, select mode 2 or mode 3; if you are not, select mode 0 or 1. The on-chip ROM is allocated to addresses H'00000000 to H'0003FFFF of memory area 0.

# Section 22 Power-Down Modes

This LSI supports the following power-down modes: sleep mode, software standby mode, deep software standby mode, and module standby mode.

## 22.1 Features

• Supports sleep mode, software standby mode, module standby mode, and deep software standby mode.

### 22.1.1 Types of Power-Down Modes

This LSI has the following power-down modes.

- Sleep mode

- Software standby mode

- Deep software standby mode

- Module standby mode

Table 22.1 shows the methods to make a transition from the program execution state, as well as the CPU and peripheral module states in each mode and the procedures for canceling each mode.

#### Table 22.1 States of Power-Down Modes

|                             |                                                                                                               |       |       | S               | tate                                                |                                  |    |                                                                                                       |

|-----------------------------|---------------------------------------------------------------------------------------------------------------|-------|-------|-----------------|-----------------------------------------------------|----------------------------------|----|-------------------------------------------------------------------------------------------------------|

| Mode                        | Transition Method                                                                                             | CPG   | CPU   | CPU<br>Register | On-Chip<br>Memory                                   | On-Chip<br>Peripheral<br>Modules | Ca | Inceling Procedure                                                                                    |

| Sleep                       | Execute SLEEP<br>instruction with STBY<br>bit in STBCR1<br>cleared to 0.                                      | Runs  | Halts | Held            | Runs                                                | Run                              | •  | Reset                                                                                                 |

| Software<br>standby         | Execute SLEEP<br>instruction with STBY<br>bit in STBCR1 and<br>STBYMD bit in<br>STBCR6 set to 1.              | Halts | Halts | Held            | Halts<br>(contents<br>retained)                     | Halt                             | •  | Interrupt by NMI or<br>IRQ<br>Power-on reset by<br>the RES pin                                        |

| Deep<br>software<br>standby | Execute SLEEP<br>instruction with STBY<br>bit in STBCR1 set to<br>1 and STBYMD bit in<br>STBCR6 cleared to 0. | Halts | Halts | Undefined       | Halts<br>(contents<br>undefined)                    | Halt                             | •  | Power-on reset by the RES pin                                                                         |

| Module<br>standby           | Set MSTP bits in<br>STBCR2 to STBCR5<br>to 1.                                                                 |       | Runs  |                 | Specified<br>module halts<br>(contents<br>retained) | halts                            | •  | Clear MSTP bit to 0<br>Power-on reset (for<br>modules whose<br>MSTP bit has an<br>initial value of 0) |

Note: For details on the states of on-chip peripheral module registers in each mode, refer to section 23.3, Register States in Each Operating Mode. For details on the pin states in each mode, refer to appendix A, Pin States.

| Stack states after exception handling |   |

|---------------------------------------|---|

| ends                                  | , |

| Status register (SR)17                |   |

| System control instructions 42        |   |

# Т

| Target pins and conditions for high- |

|--------------------------------------|

| impedance control 516                |

| The address map for the operating    |

| modes                                |

| Transfer information read skip       |

| function                             |

| Transfer information writeback skip  |

| function                             |

| Trap instructions                    |

|                                      |

## U

| User boot mode78 | 5 |

|------------------|---|

|------------------|---|

| User break controller (UBC) | .117  |

|-----------------------------|-------|

| User break interrupt        | . 105 |

| User MAT                    | .742  |

| User program mode           | .776  |

| Using interval timer mode   | . 531 |

| Using watchdog timer mode   | . 530 |

## V

| Vector numbers and vector table address |  |

|-----------------------------------------|--|

| offsets75                               |  |

| Vector-base register (VBR)18            |  |

## W

| Wait between access cycles | . 223 |

|----------------------------|-------|

| Watchdog timer (WDT)       | . 523 |