Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 5184                                                        |

| Number of Logic Elements/Cells | 51840                                                       |

| Total RAM Bits                 | 442368                                                      |

| Number of I/O                  | 488                                                         |

| Number of Gates                | 2392000                                                     |

| Voltage - Supply               | 2.375V ~ 2.625V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 652-BBGA                                                    |

| Supplier Device Package        | 652-BGA (45x45)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep20k1500cb652c9 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# ...and More Features

- Low-power operation design

- 1.8-V supply voltage (see Table 2)

- Copper interconnect reduces power consumption

- MultiVolt™ I/O support for 1.8-V, 2.5-V, and 3.3-V interfaces

- ESBs offering programmable power-saving mode

- Flexible clock management circuitry with up to four phase-locked loops (PLLs)

- Built-in low-skew clock tree

- Up to eight global clock signals

- ClockLock<sup>TM</sup> feature reducing clock delay and skew

- ClockBoost<sup>TM</sup> feature providing clock multiplication and division

- ClockShift<sup>™</sup> feature providing programmable clock phase and delay shifting

- Powerful I/O features

- Compliant with peripheral component interconnect Special Interest Group (PCI SIG) *PCI Local Bus Specification*, *Revision 2.2* for 3.3-V operation at 33 or 66 MHz and 32 or 64 bits

- Support for high-speed external memories, including DDR synchronous dynamic RAM (SDRAM) and ZBT static RAM (SRAM)

- 16 input and 16 output LVDS channels

- Direct connection from I/O pins to local interconnect providing fast  $t_{CO}$  and  $t_{SU}$  times for complex logic

- MultiVolt I/O support for 1.8-V, 2.5-V, and 3.3-V interfaces

- Programmable clamp to V<sub>CCIO</sub>

- Individual tri-state output enable control for each pin

- Programmable output slew-rate control to reduce switching noise

- Support for advanced I/O standards, including low-voltage differential signaling (LVDS), LVPECL, PCI-X, AGP, CTT, SSTL-3 and SSTL-2, GTL+, and HSTL Class I

- Supports hot-socketing operation

- Pull-up on I/O pins before and during configuration

| Table 2. APEX 20KC Supply Voltages                          |                                |  |  |  |

|-------------------------------------------------------------|--------------------------------|--|--|--|

| Feature                                                     | Voltage                        |  |  |  |

| Internal supply voltage (V <sub>CCINT</sub> )               | 1.8 V                          |  |  |  |

| MultiVolt I/O interface voltage levels (V <sub>CCIO</sub> ) | 1.8 V, 2.5 V, 3.3 V, 5.0 V (1) |  |  |  |

#### Note:

(1) APEX 20KC devices can be 5.0-V tolerant by using an external resistor.

| Table 7. APEX 20KC Device Fea | Table 7. APEX 20KC Device Features (Part 2 of 2)                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Feature                       | APEX 20KC Devices                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| I/O standard support          | 1.8-V, 2.5-V, 3.3-V, 5.0-V I/O 3.3-V PCI and PCI-X 3.3-V AGP CTT GTL+ LVCMOS LVTTL True-LVDS <sup>TM</sup> and LVPECL data pins (in EP20K400C and larger devices) LVDS and LVPECL clock pins (in all devices) LVDS and LVPECL data pins up to 156 Mbps (in all devices) HSTL Class I PCI-X SSTL-2 Class I and II SSTL-3 Class I and II |  |  |  |  |  |

| Memory support                | CAM Dual-port RAM FIFO RAM ROM                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

All APEX 20KC devices are reconfigurable and are 100% tested prior to shipment. As a result, test vectors do not have to be generated for fault-coverage purposes. Instead, the designer can focus on simulation and design verification. In addition, the designer does not need to manage inventories of different application-specific integrated circuit (ASIC) designs; APEX 20KC devices can be configured on the board for the specific functionality required.

APEX 20KC devices are configured at system power-up with data stored in an Altera serial configuration device or provided by a system controller. Altera offers in-system programmability (ISP)-capable EPC16, EPC2, and EPC1 configuration devices, which configure APEX 20KC devices via a serial data stream. Moreover, APEX 20KC devices contain an optimized interface that permits microprocessors to configure APEX 20KC devices serially or in parallel, and synchronously or asynchronously. The interface also enables microprocessors to treat APEX 20KC devices as memory and configure the device by writing to a virtual memory location, making reconfiguration easy.

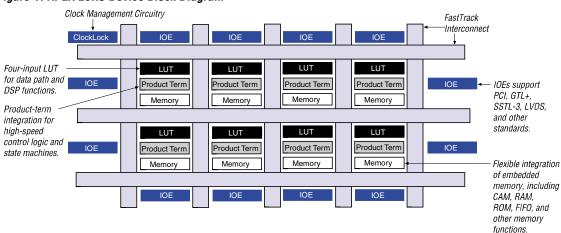

The ESB can implement a variety of memory functions, including CAM, RAM, dual-port RAM, ROM, and FIFO functions. Embedding the memory directly into the die improves performance and reduces die area compared to distributed-RAM implementations. Moreover, the abundance of cascadable ESBs allows APEX 20KC devices to implement multiple wide memory blocks for high-density designs. The ESB's high speed ensures it can implement small memory blocks without any speed penalty. Additionally, designers can use the ESBs to create as many different-sized memory blocks as the system requires. Figure 1 shows an overview of the APEX 20KC device.

Figure 1. APEX 20KC Device Block Diagram

APEX 20KC devices provide four dedicated clock pins and four dedicated input pins that drive register control inputs. These signals ensure efficient distribution of high-speed, low-skew control signals, which use dedicated routing channels to provide short delays and low skews. Four of the dedicated inputs drive four global signals. These four global signals can also be driven by internal logic, providing an ideal solution for a clock divider or internally generated asynchronous clear signals with high fan-out. The dedicated clock pins featured on the APEX 20KC devices can also feed logic. The devices also feature ClockLock and ClockBoost clock management circuitry.

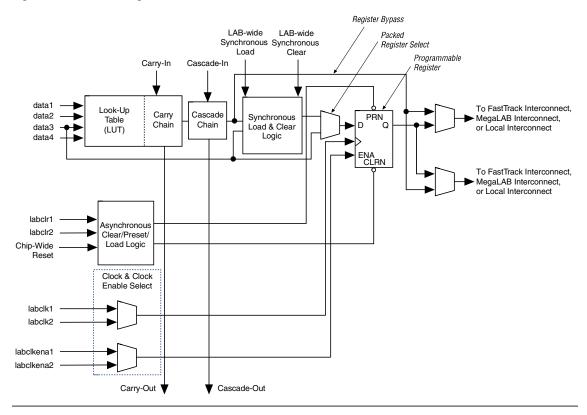

Figure 5. APEX 20KC Logic Element

Each LE's programmable register can be configured for D, T, JK, or SR operation. The register's clock and clear control signals can be driven by global signals, general-purpose I/O pins, or any internal logic. For combinatorial functions, the register is bypassed and the output of the LUT drives the outputs of the LE.

Each LE has two outputs that drive the local, MegaLAB, or FastTrack interconnect routing structure. Each output can be driven independently by the LUT's or register's output. For example, the LUT can drive one output while the register drives the other output. This feature, called register packing, improves device utilization because the register and the LUT can be used for unrelated functions. The LE can also drive out registered and unregistered versions of the LUT output.

Register a1 LUT b1 Carry Chain LE1 a2 Register ► s2 LUT b2 Carry Chain LE2 Register LUT an b*n* Carry Chain LE*n* Register ➤ Carry-Out LUT Carry Chain LE*n* + 1

Figure 6. APEX 20KC Carry Chain

The programmable register also supports an asynchronous clear function. Within the ESB, two asynchronous clears are generated from global signals and the local interconnect. Each macrocell can either choose between the two asynchronous clear signals or choose to not be cleared. Either of the two clear signals can be inverted within the ESB. Figure 15 shows the ESB control logic when implementing product-terms.

Dedicated Clocks Global Signals Local Interconnect Local Interconnect Local Interconnect Local Interconnect CLR1 CLK2 CLKENA2 CLK1 CLKENA1 CLR2

Figure 15. ESB Product-Term Mode Control Logic

# Parallel Expanders

Parallel expanders are unused product terms that can be allocated to a neighboring macrocell to implement fast, complex logic functions. Parallel expanders allow up to 32 product terms to feed the macrocell OR logic directly, with two product terms provided by the macrocell and 30 parallel expanders provided by the neighboring macrocells in the ESB.

The Quartus II Compiler can allocate up to 15 sets of up to two parallel expanders per set to the macrocells automatically. Each set of two parallel expanders incurs a small, incremental timing delay. Figure 16 shows the APEX 20KC parallel expanders.

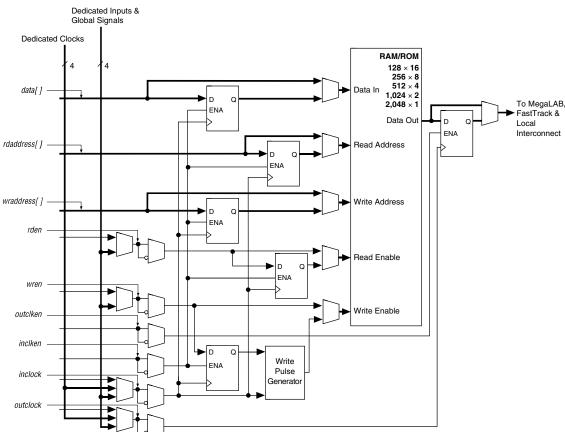

## Input/Output Clock Mode

The input/output clock mode contains two clocks. One clock controls all registers for inputs into the ESB: data input, WE, RE, read address, and write address. The other clock controls the ESB data output registers. The ESB also supports clock enable and asynchronous clear signals; these signals also control the reading and writing of registers independently. Input/output clock mode is commonly used for applications where the reads and writes occur at the same system frequency, but require different clock enable signals for the input and output registers. Figure 21 shows the ESB in input/output clock mode.

Figure 21. ESB in Input/Output Clock Mode Note (1)

#### Note:

(1) All registers can be cleared asynchronously by ESB local interconnect signals, global signals, or the chip-wide reset.

For more information on APEX 20KC devices and CAM, see *Application Note 119 (Implementing High-Speed Search Applications with APEX CAM)*.

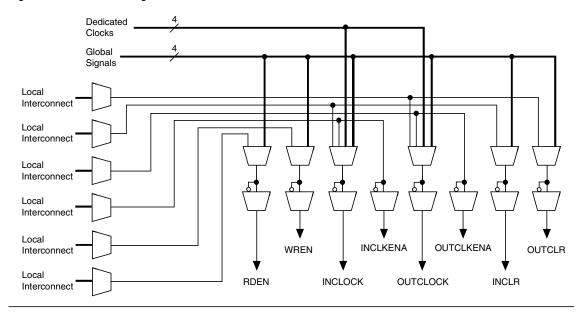

# **Driving Signals to the ESB**

ESBs provide flexible options for driving control signals. Different clocks can be used for the ESB inputs and outputs. Registers can be inserted independently on the data input, data output, read address, write address, WE, and RE signals. The global signals and the local interconnect can drive the WE and RE signals. The global signals, dedicated clock pins, and local interconnect can drive the ESB clock signals. Because the LEs drive the local interconnect, the LEs can control the WE and RE signals and the ESB clock, clock enable, and asynchronous clear signals. Figure 24 shows the ESB control signal generation logic.

Figure 24. ESB Control Signal Generation

An ESB is fed by the local interconnect, which is driven by adjacent LEs (for high-speed connection to the ESB) or the MegaLAB interconnect. The ESB can drive the local, MegaLAB, or FastTrack interconnect routing structure to drive LEs and IOEs in the same MegaLAB structure or anywhere in the device.

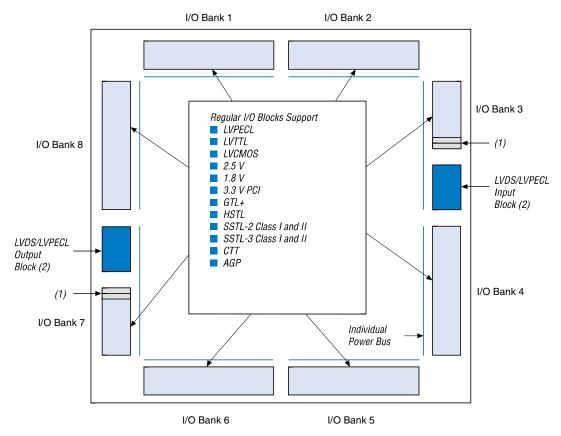

Figure 28. APEX 20KC I/O Banks

#### Notes:

- (1) Any I/O pin within two pads of the LVDS pins can only be used as an input to maintain an acceptable noise level on the V<sub>CCIO</sub> plane. No output pin can be placed within two pads of LVDS pins unless separated by a power or ground pin. Use the **Show Pads** view in the Quartus II software's Floor Plan Editor to locate these pads. The Quartus II software will give an error message for illegal output or bidirectional pin placement next to the LVDS pin.

- (2) If the LVDS input and output blocks are not used for LVDS, they can support all of the I/O standards and can be used as input, output, or bidirectional pins with  $V_{\rm CCIO}$  set to 3.3 V, 2.5 V, or 1.8 V.

# **Power Sequencing & Hot Socketing**

Because APEX 20KC devices can be used in a mixed-voltage environment, they have been designed specifically to tolerate any possible power-up sequence. Therefore, the  $V_{CCIO}$  and  $V_{CCINT}$  power supplies may be powered in any order.

The APEX 20KC device instruction register length is 10 bits. The APEX 20KC device USERCODE register length is 32 bits. Tables 14 and 15 show the boundary-scan register length and device IDCODE information for APEX 20KC devices.

| Table 14. APEX 20KC Boundary-Scan Register Length |       |  |  |  |  |

|---------------------------------------------------|-------|--|--|--|--|

| Device Boundary-Scan Register Lengt               |       |  |  |  |  |

| EP20K100C                                         | 774   |  |  |  |  |

| EP20K200C                                         | 1,164 |  |  |  |  |

| EP20K400C                                         | 1,506 |  |  |  |  |

| EP20K600C                                         | 1,806 |  |  |  |  |

| EP20K1000C                                        | 2,190 |  |  |  |  |

| EP20K1500C                                        | 2,502 |  |  |  |  |

| Table 15. 32-Bit            | Table 15. 32-Bit APEX 20KC Device IDCODE |                       |                                    |           |  |  |  |  |

|-----------------------------|------------------------------------------|-----------------------|------------------------------------|-----------|--|--|--|--|

| Device IDCODE (32 Bits) (1) |                                          |                       |                                    |           |  |  |  |  |

|                             | Version<br>(4 Bits)                      | Part Number (16 Bits) | Manufacturer<br>Identity (11 Bits) | 1 (1 Bit) |  |  |  |  |

| EP20K100C                   | 0000                                     | 1000 0001 0000 0000   | 000 0110 1110                      | 1         |  |  |  |  |

| EP20K200C                   | 0000                                     | 1000 0010 0000 0000   | 000 0110 1110                      | 1         |  |  |  |  |

| EP20K400C                   | 0000                                     | 1000 0100 0000 0000   | 000 0110 1110                      | 1         |  |  |  |  |

| EP20K600C                   | 0000                                     | 1000 0110 0000 0000   | 000 0110 1110                      | 1         |  |  |  |  |

| EP20K1000C                  | 0000                                     | 1001 0000 0000 0000   | 000 0110 1110                      | 1         |  |  |  |  |

| EP20K1500C                  | 0000                                     | 1001 0101 0000 0000   | 000 0110 1110                      | 1         |  |  |  |  |

#### Notes:

- (1) The most significant bit (MSB) is on the left.

- (2) The IDCODE's least significant bit (LSB) is always 1.

Figure 30 shows the timing requirements for the JTAG signals.

| Table 22. LV      | Table 22. LVCMOS I/O Specifications |                                                               |                         |                         |       |  |  |  |  |

|-------------------|-------------------------------------|---------------------------------------------------------------|-------------------------|-------------------------|-------|--|--|--|--|

| Symbol            | Parameter                           | Conditions                                                    | Minimum                 | Maximum                 | Units |  |  |  |  |

| V <sub>CCIO</sub> | Power supply voltage range          |                                                               | 3.0                     | 3.6                     | V     |  |  |  |  |

| V <sub>IH</sub>   | High-level input voltage            |                                                               | 2.0                     | V <sub>CCIO</sub> + 0.3 | V     |  |  |  |  |

| V <sub>IL</sub>   | Low-level input voltage             |                                                               | -0.3                    | 0.8                     | V     |  |  |  |  |

| I <sub>I</sub>    | Input pin leakage current           | V <sub>IN</sub> = 0 V or 3.3 V                                | -10                     | 10                      | μΑ    |  |  |  |  |

| V <sub>OH</sub>   | High-level output voltage           | $V_{CCIO} = 3.0 \text{ V}$<br>$I_{OH} = -0.1 \text{ mA } (1)$ | V <sub>CCIO</sub> - 0.2 |                         | V     |  |  |  |  |

| V <sub>OL</sub>   | Low-level output voltage            | V <sub>CCIO</sub> = 3.0 V<br>I <sub>OL</sub> = 0.1 mA (2)     |                         | 0.2                     | V     |  |  |  |  |

| Table 23. 2.5-V I/O Specifications |                           |                                 |         |                         |       |  |  |

|------------------------------------|---------------------------|---------------------------------|---------|-------------------------|-------|--|--|

| Symbol                             | Parameter                 | Conditions                      | Minimum | Maximum                 | Units |  |  |

| V <sub>CCIO</sub>                  | Output supply voltage     |                                 | 2.375   | 2.625                   | V     |  |  |

| V <sub>IH</sub>                    | High-level input voltage  |                                 | 1.7     | V <sub>CCIO</sub> + 0.3 | V     |  |  |

| V <sub>IL</sub>                    | Low-level input voltage   |                                 | -0.3    | 0.7                     | V     |  |  |

| I <sub>I</sub>                     | Input pin leakage current | V <sub>IN</sub> = 0 V or 3.3 V  | -10     | 10                      | μΑ    |  |  |

| V <sub>OH</sub>                    | High-level output         | $I_{OH} = -0.1 \text{ mA } (1)$ | 2.1     |                         | V     |  |  |

|                                    | voltage                   | $I_{OH} = -1 \text{ mA } (1)$   | 2.0     |                         | V     |  |  |

|                                    |                           | $I_{OH} = -2 \text{ mA } (1)$   | 1.7     |                         | V     |  |  |

| V <sub>OL</sub>                    | Low-level output          | I <sub>OL</sub> = 0.1 mA (2)    |         | 0.2                     | V     |  |  |

|                                    | voltage                   | I <sub>OL</sub> = 1 mA (2)      |         | 0.4                     | V     |  |  |

|                                    |                           | I <sub>OL</sub> = 2 mA (2)      |         | 0.7                     | V     |  |  |

| Table 28. GTL+ I/O Specifications |                          |                             |                        |         |                        |       |  |

|-----------------------------------|--------------------------|-----------------------------|------------------------|---------|------------------------|-------|--|

| Symbol                            | Parameter                | Conditions                  | Minimum                | Typical | Maximum                | Units |  |

| V <sub>TT</sub>                   | Termination voltage      |                             | 1.35                   | 1.5     | 1.65                   | V     |  |

| $V_{REF}$                         | Reference voltage        |                             | 0.88                   | 1.0     | 1.12                   | V     |  |

| V <sub>IH</sub>                   | High-level input voltage |                             | V <sub>REF</sub> + 0.1 |         |                        | V     |  |

| V <sub>IL</sub>                   | Low-level input voltage  |                             |                        |         | V <sub>REF</sub> – 0.1 | V     |  |

| V <sub>OL</sub>                   | Low-level output voltage | I <sub>OL</sub> = 36 mA (2) |                        |         | 0.65                   | V     |  |

| Table 29. SS      | Table 29. SSTL-2 Class I Specifications |                                |                         |                  |                         |       |  |  |

|-------------------|-----------------------------------------|--------------------------------|-------------------------|------------------|-------------------------|-------|--|--|

| Symbol            | Parameter                               | Conditions                     | Minimum                 | Typical          | Maximum                 | Units |  |  |

| V <sub>CCIO</sub> | I/O supply voltage                      |                                | 2.375                   | 2.5              | 2.625                   | ٧     |  |  |

| V <sub>TT</sub>   | Termination voltage                     |                                | V <sub>REF</sub> - 0.04 | V <sub>REF</sub> | V <sub>REF</sub> + 0.04 | V     |  |  |

| V <sub>REF</sub>  | Reference voltage                       |                                | 1.15                    | 1.25             | 1.35                    | ٧     |  |  |

| V <sub>IH</sub>   | High-level input voltage                |                                | V <sub>REF</sub> + 0.18 |                  | V <sub>CCIO</sub> + 0.3 | V     |  |  |

| V <sub>IL</sub>   | Low-level input voltage                 |                                | -0.3                    |                  | V <sub>REF</sub> – 0.18 | V     |  |  |

| V <sub>OH</sub>   | High-level output voltage               | $I_{OH} = -7.6 \text{ mA} (1)$ | V <sub>TT</sub> + 0.57  |                  |                         | V     |  |  |

| V <sub>OL</sub>   | Low-level output voltage                | I <sub>OL</sub> = 7.6 mA (2)   |                         |                  | V <sub>TT</sub> – 0.57  | V     |  |  |

Figure 33 shows the  $f_{M\!A\!X}$  timing model for APEX 20KC devices.

Figure 33.  $f_{MAX}$  Timing Model LE <sup>t</sup>su Routing Delay  $^{t}_{H}$ <sup>t</sup> F1—4 <sup>t</sup>co <sup>t</sup> F5—20 <sup>t</sup> LUT t F20+ ESB <sup>t</sup>ESBARC ESBSRC <sup>t</sup>ESBAWC <sup>t</sup>ESBSWC <sup>t</sup>ESBWASU ESBWDSU <sup>t</sup>ESBSRASU <sup>t</sup>ESBWESU <sup>t</sup>ESBDATASU <sup>t</sup>ESBWADDRSU <sup>t</sup>.ESBRADDRSU <sup>t</sup>ESBDATACO1 <sup>t</sup>ESBDATACO2 <sup>t</sup>ESBDD <sup>t</sup>PD

Figure 34 shows the timing model for bidirectional I/O pin timing.

<sup>t</sup>PTERMSU <sup>t</sup>PTERMCO

| Table 42. APEX            | 20KC External Bidirectional Timing Parameters Note (1)                             |            |

|---------------------------|------------------------------------------------------------------------------------|------------|

| Symbol                    | Parameter                                                                          | Condition  |

| t <sub>INSUBIDIR</sub>    | Setup time for bidirectional pins with global clock at LAB-adjacent input register |            |

| t <sub>INHBIDIR</sub>     | Hold time for bidirectional pins with global clock at LAB-adjacent input register  |            |

| <sup>t</sup> OUTCOBIDIR   | Clock-to-output delay for bidirectional pins with global clock at IOE register     | C1 = 35 pF |

| t <sub>XZBIDIR</sub>      | Synchronous output enable register to output buffer disable delay                  | C1 = 35 pF |

| t <sub>ZXBIDIR</sub>      | Synchronous output enable register to output buffer enable delay                   | C1 = 35 pF |

| <sup>t</sup> INSUBIDIRPLL | Setup time for bidirectional pins with PLL clock at LAB-adjacent input register    |            |

| t <sub>INHBIDIRPLL</sub>  | Hold time for bidirectional pins with PLL clock at LAB-adjacent input register     |            |

| †OUTCOBIDIRPLL            | Clock-to-output delay for bidirectional pins with PLL clock at IOE register        | C1 = 35 pF |

| t <sub>XZBIDIRPLL</sub>   | Synchronous output enable register to output buffer disable delay with PLL         | C1 = 35 pF |

| t <sub>ZXBIDIRPLL</sub>   | Synchronous output enable register to output buffer enable delay with PLL          | C1 = 35 pF |

Note to tables:

(1) These timing parameters are sample-tested only.

| Table 48. EP20K100C External Bidirectional Timing Parameters |        |          |                          |     |                    |     |      |

|--------------------------------------------------------------|--------|----------|--------------------------|-----|--------------------|-----|------|

| Symbol                                                       | -7 Spe | ed Grade | Grade -8 Speed Grade (2) |     | -9 Speed Grade (2) |     | Unit |

|                                                              | Min    | Max      | Min                      | Max | Min                | Max |      |

| t <sub>INSUBIDIR</sub>                                       | 1.9    |          |                          |     |                    |     | ns   |

| t <sub>INHBIDIR</sub>                                        | 0.0    |          |                          |     |                    |     | ns   |

| t <sub>OUTCOBIDIR</sub>                                      | 2.0    | 5.0      |                          |     |                    |     | ns   |

| t <sub>XZBIDIR</sub>                                         |        | 7.1      |                          |     |                    |     | ns   |

| t <sub>ZXBIDIR</sub>                                         |        | 7.1      |                          |     |                    |     | ns   |

| t <sub>INSUBIDIRPLL</sub>                                    | 3.9    |          |                          |     |                    |     | ns   |

| t <sub>INHBIDIRPLL</sub>                                     | 0.0    |          |                          |     |                    |     | ns   |

| †OUTCOBIDIRPLL                                               | 0.5    | 2.1      |                          |     |                    |     | ns   |

| t <sub>XZBIDIRPLL</sub>                                      |        | 4.2      |                          |     |                    |     | ns   |

| t <sub>ZXBIDIRPLL</sub>                                      |        | 4.2      |                          |     |                    |     | ns   |

| Table 49. EP20K200C f <sub>MAX</sub> LE Timing Parameters Note (1) |                                            |     |     |     |          |      |    |  |

|--------------------------------------------------------------------|--------------------------------------------|-----|-----|-----|----------|------|----|--|

| Symbol                                                             | ymbol -7 Speed Grade -8 Speed Grade (2) -9 |     |     |     | -9 Speed | Unit |    |  |

|                                                                    | Min                                        | Max | Min | Max | Min      | Max  |    |  |

| $t_{SU}$                                                           | 0.3                                        |     |     |     |          |      | ns |  |

| t <sub>H</sub>                                                     | 0.3                                        |     |     |     |          |      | ns |  |

| $t_{CO}$                                                           |                                            | 0.3 |     |     |          |      | ns |  |

| $t_{LUT}$                                                          |                                            | 0.7 |     |     |          |      | ns |  |

| Table 54. EP20K200C External Bidirectional Timing Parameters |         |         |          |           |          |                    |    |  |  |  |

|--------------------------------------------------------------|---------|---------|----------|-----------|----------|--------------------|----|--|--|--|

| Symbol                                                       | -7 Spee | d Grade | -8 Speed | Grade (2) | -9 Speed | -9 Speed Grade (2) |    |  |  |  |

|                                                              | Min     | Max     | Min      | Max       | Min      | Max                |    |  |  |  |

| t <sub>INSUBIDIR</sub>                                       | 2.0     |         |          |           |          |                    | ns |  |  |  |

| t <sub>INHBIDIR</sub>                                        | 0.0     |         |          |           |          |                    | ns |  |  |  |

| toutcobidir                                                  | 2.0     | 5.0     |          |           |          |                    | ns |  |  |  |

| t <sub>XZBIDIR</sub>                                         |         | 7.1     |          |           |          |                    | ns |  |  |  |

| t <sub>ZXBIDIR</sub>                                         |         | 7.1     |          |           |          |                    | ns |  |  |  |

| t <sub>INSUBIDIRPLL</sub>                                    | 3.9     |         |          |           |          |                    | ns |  |  |  |

| t <sub>INHBIDIRPLL</sub>                                     | 0.0     |         |          |           |          |                    | ns |  |  |  |

| t <sub>OUTCOBIDIRPLL</sub>                                   | 0.5     | 2.1     |          |           |          |                    | ns |  |  |  |

| t <sub>XZBIDIRPLL</sub>                                      |         | 4.2     |          |           |          |                    | ns |  |  |  |

| t <sub>ZXBIDIRPLL</sub>                                      |         | 4.2     |          |           |          |                    | ns |  |  |  |

| Table 55. EP20K400C f <sub>MAX</sub> LE Timing Parameters Note (1) |         |         |          |           |                    |     |      |  |  |

|--------------------------------------------------------------------|---------|---------|----------|-----------|--------------------|-----|------|--|--|

| Symbol                                                             | -7 Spee | d Grade | -8 Speed | Grade (2) | -9 Speed Grade (2) |     | Unit |  |  |

|                                                                    | Min     | Max     | Min      | Max       | Min                | Max |      |  |  |

| $t_{SU}$                                                           | 0.3     |         |          |           |                    |     | ns   |  |  |

| t <sub>H</sub>                                                     | 0.3     |         |          |           |                    |     | ns   |  |  |

| $t_{CO}$                                                           |         | 0.3     |          |           |                    |     | ns   |  |  |

| $t_{LUT}$                                                          |         | 0.6     |          |           |                    |     | ns   |  |  |

| Table 56. EP20K400C f <sub>MAX</sub> ESB Timing Parameters   Note (1) |         |         |          |           |          |           |      |  |  |

|-----------------------------------------------------------------------|---------|---------|----------|-----------|----------|-----------|------|--|--|

| Symbol                                                                | -7 Spee | d Grade | -8 Speed | Grade (2) | -9 Speed | Grade (2) | Unit |  |  |

|                                                                       | Min     | Max     | Min      | Max       | Min      | Max       | 1    |  |  |

| t <sub>ESBARC</sub>                                                   |         | 1.3     |          |           |          |           | ns   |  |  |

| t <sub>ESBSRC</sub>                                                   |         | 2.3     |          |           |          |           | ns   |  |  |

| t <sub>ESBAWC</sub>                                                   |         | 2.9     |          |           |          |           | ns   |  |  |

| t <sub>ESBSWC</sub>                                                   |         | 2.7     |          |           |          |           | ns   |  |  |

| t <sub>ESBWASU</sub>                                                  | 0.4     |         |          |           |          |           | ns   |  |  |

| t <sub>ESBWAH</sub>                                                   | 0.4     |         |          |           |          |           | ns   |  |  |

| t <sub>ESBWDSU</sub>                                                  | 0.6     |         |          |           |          |           | ns   |  |  |

| t <sub>ESBWDH</sub>                                                   | 0.4     |         |          |           |          |           | ns   |  |  |

| t <sub>ESBRASU</sub>                                                  | 1.3     |         |          |           |          |           | ns   |  |  |

| t <sub>ESBRAH</sub>                                                   | 0.0     |         |          |           |          |           | ns   |  |  |

| t <sub>ESBWESU</sub>                                                  | 2.0     |         |          |           |          |           | ns   |  |  |

| t <sub>ESBDATASU</sub>                                                | 0.0     |         |          |           |          |           | ns   |  |  |

| t <sub>ESBWADDRSU</sub>                                               | 0.1     |         |          |           |          |           | ns   |  |  |

| t <sub>ESBRADDRSU</sub>                                               | 0.1     |         |          |           |          |           | ns   |  |  |

| t <sub>ESBDATACO1</sub>                                               |         | 1.0     |          |           |          |           | ns   |  |  |

| t <sub>ESBDATACO2</sub>                                               |         | 2.0     |          |           |          |           | ns   |  |  |

| t <sub>ESBDD</sub>                                                    |         | 2.4     |          |           |          |           | ns   |  |  |

| t <sub>PD</sub>                                                       |         | 1.4     |          |           |          |           | ns   |  |  |

| t <sub>PTERMSU</sub>                                                  | 0.9     |         |          |           |          |           | ns   |  |  |

| t <sub>PTERMCO</sub>                                                  |         | 1.0     |          |           |          |           | ns   |  |  |

| Table 57. EP20K400C f <sub>MAX</sub> Routing Delays Note (1) |         |         |          |                     |     |           |      |  |  |

|--------------------------------------------------------------|---------|---------|----------|---------------------|-----|-----------|------|--|--|

| Symbol                                                       | -7 Spee | d Grade | -8 Speed | ed Grade (2) -9 Spe |     | Grade (2) | Unit |  |  |

|                                                              | Min     | Max     | Min      | Max                 | Min | Max       |      |  |  |

| t <sub>F1-4</sub>                                            | 0.2     |         |          |                     |     |           | ns   |  |  |

| t <sub>F5-20</sub>                                           | 0.9     |         |          |                     |     |           | ns   |  |  |

| t <sub>F20+</sub>                                            | 2.2     |         |          |                     |     |           | ns   |  |  |

| Table 78. EP20K1500C External Bidirectional Timing Parameters |         |          |          |           |                    |     |      |  |  |  |

|---------------------------------------------------------------|---------|----------|----------|-----------|--------------------|-----|------|--|--|--|

| Symbol                                                        | -7 Spee | ed Grade | -8 Speed | Grade (2) | -9 Speed Grade (2) |     | Unit |  |  |  |

|                                                               | Min     | Max      | Min      | Max       | Min                | Max | 1    |  |  |  |

| t <sub>INSUBIDIR</sub>                                        | 2.6     |          |          |           |                    |     | ns   |  |  |  |

| t <sub>INHBIDIR</sub>                                         | 0.0     |          |          |           |                    |     | ns   |  |  |  |

| t <sub>OUTCOBIDIR</sub>                                       | 2.0     | 5.0      |          |           |                    |     | ns   |  |  |  |

| t <sub>XZBIDIR</sub>                                          |         | 7.1      |          |           |                    |     | ns   |  |  |  |

| t <sub>ZXBIDIR</sub>                                          |         | 7.1      |          |           |                    |     | ns   |  |  |  |

| t <sub>INSUBIDIRPLL</sub>                                     | 3.9     |          |          |           |                    |     | ns   |  |  |  |

| t <sub>INHBIDIRPLL</sub>                                      | 0.0     |          |          |           |                    |     | ns   |  |  |  |

| t <sub>OUTCOBIDIRPLL</sub>                                    | 0.5     | 2.1      |          |           |                    |     | ns   |  |  |  |

| t <sub>XZBIDIRPLL</sub>                                       |         | 4.2      |          |           |                    |     | ns   |  |  |  |

| t <sub>ZXBIDIRPLL</sub>                                       |         | 4.2      |          |           |                    |     | ns   |  |  |  |

#### Notes to tables:

- (1) Timing information is preliminary. Final timing information will be released in a future version of this data sheet.(2) Timing information for these devices will be released in a future version of this data sheet.

Tables 79 and 80 show selectable I/O standard input and output delays for APEX 20KC devices. If you select an I/O standard input or output delay other than LVCMOS, add the delay for the selected speed grade to the LVCMOS value.

| Table 79. Selectable I/O Standard Input Delays |         |         |          |           |          |           |      |  |  |

|------------------------------------------------|---------|---------|----------|-----------|----------|-----------|------|--|--|

| Symbol                                         | -7 Spee | d Grade | -8 Speed | Grade (1) | -9 Speed | Grade (1) | Unit |  |  |

|                                                | Min     | Max     | Min      | Max       | Min      | Max       | Min  |  |  |

| LVCMOS                                         |         | 0.0     |          |           |          |           | ns   |  |  |

| LVTTL                                          |         | 0.0     |          |           |          |           | ns   |  |  |

| 2.5 V                                          |         | 0.1     |          |           |          |           | ns   |  |  |

| 1.8 V                                          |         | 0.5     |          |           |          |           | ns   |  |  |

| PCI                                            |         | 0.4     |          |           |          |           | ns   |  |  |

| GTL+                                           |         | -0.3    |          |           |          |           | ns   |  |  |

| SSTL-3 Class I                                 |         | -0.4    |          |           |          |           | ns   |  |  |

| SSTL-3 Class II                                |         | -0.4    |          |           |          |           | ns   |  |  |

| SSTL-2 Class I                                 |         | -0.3    |          |           |          |           | ns   |  |  |

| SSTL-2 Class II                                |         | -0.3    |          |           |          |           | ns   |  |  |

| LVDS                                           |         | -0.2    |          |           |          |           | ns   |  |  |

| СТТ                                            |         | -0.3    |          |           |          |           | ns   |  |  |

| AGP                                            |         | 0.0     |          |           |          |           | ns   |  |  |

| Table 80. Selectable I/O Standard Output Delays |         |         |          |           |          |           |      |  |  |

|-------------------------------------------------|---------|---------|----------|-----------|----------|-----------|------|--|--|

| Symbol                                          | -7 Spee | d Grade | -8 Speed | Grade (1) | -9 Speed | Grade (1) | Unit |  |  |

|                                                 | Min     | Max     | Min      | Max       | Min      | Max       | Min  |  |  |

| LVCMOS                                          |         | 0.0     |          |           |          |           | ns   |  |  |

| LVTTL                                           |         | 0.0     |          |           |          |           | ns   |  |  |

| 2.5 V                                           |         | 0.5     |          |           |          |           | ns   |  |  |

| 1.8 V                                           |         | 1.7     |          |           |          |           | ns   |  |  |

| PCI                                             |         | -0.2    |          |           |          |           | ns   |  |  |

| GTL+                                            |         | -0.4    |          |           |          |           | ns   |  |  |

| SSTL-3 Class I                                  |         | -0.1    |          |           |          |           | ns   |  |  |

| SSTL-3 Class II                                 |         | -0.6    |          |           |          |           | ns   |  |  |

| SSTL-2 Class I                                  |         | 0.0     |          |           |          |           | ns   |  |  |

| SSTL-2 Class II                                 |         | -0.4    |          |           |          |           | ns   |  |  |

| LVDS                                            |         | -0.8    |          |           |          |           | ns   |  |  |

| CTT                                             |         | -0.2    |          |           |          |           | ns   |  |  |

| AGP                                             |         | -0.4    |          |           |          |           | ns   |  |  |

#### Note to tables:

$(1) \quad \mbox{Timing information will be released in a future version of this data sheet.}$

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 http://www.altera.com Applications Hotline: (800) 800-EPLD Customer Marketing: (408) 544-7104 Literature Services: lit\_req@altera.com Copyright © 2001 Altera Corporation. All rights reserved. AMPP, Altera, APEX 20K, APEX 20KC, APEX 20KE, ByteBlasterMV, ClockBoost, ClockLock, ClockShift, FastRow, FastTrack, FineLine BGA, MasterBlaster, MegaCore, MegaLAB, MultiCore, MultiVolt, NativeLink, Quartus, Quartus II, SignalTap, True-LVDS, Turbo Bit, and specific device designations are trademarks and/or service marks of Altera Corporation in the United States and other countries. Altera acknowledges the trademarks of other organizations for their respective products or services mentioned in this document. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right

rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.