Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 36                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 363 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 14x8b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 44-QFN (8x8)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f707-e-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0   | Device Overview                                                              | 11   |

|-------|------------------------------------------------------------------------------|------|

| 2.0   | Memory Organization                                                          | . 17 |

| 3.0   | Resets                                                                       | . 28 |

| 4.0   | Interrupts                                                                   |      |

| 5.0   | Low Dropout (LDO) Voltage Regulator                                          | . 47 |

| 6.0   | I/O Ports                                                                    | -    |

| 7.0   | Oscillator Module                                                            |      |

| 8.0   | Device Configuration                                                         |      |

| 9.0   | Analog-to-Digital Converter (ADC) Module                                     |      |

| 10.0  | Fixed Voltage Reference                                                      |      |

| 11.0  | Digital-to-Analog Converter (DAC) Module                                     |      |

| 12.0  | Timer0 Module                                                                |      |

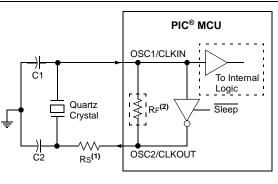

| 13.0  | Timer1/3 Modules with Gate Control                                           |      |

| 14.0  | TimerA/B Modules                                                             |      |

| 15.0  | Timer2 Module                                                                |      |

| 16.0  | Capacitive Sensing Module                                                    |      |

| 17.0  | Capture/Compare/PWM (CCP) Module                                             |      |

| 18.0  | Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) |      |

| 19.0  | SSP Module Overview                                                          |      |

|       | Program Memory Read                                                          |      |

| 21.0  | Power-Down Mode (Sleep)                                                      |      |

| 22.0  | In-Circuit Serial Programming™ (ICSP™)                                       |      |

| 23.0  | Instruction Set Summary                                                      |      |

| 24.0  | Development Support.                                                         |      |

| 25.0  | Electrical Specifications                                                    |      |

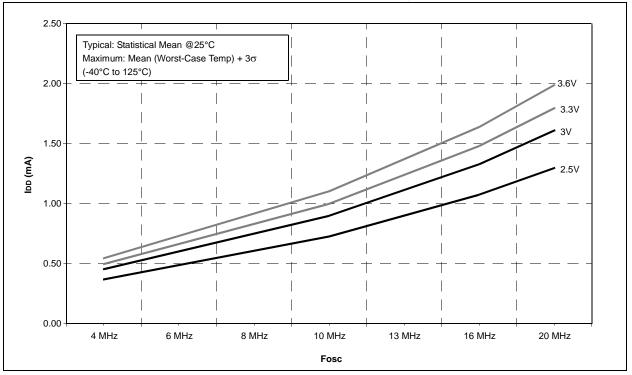

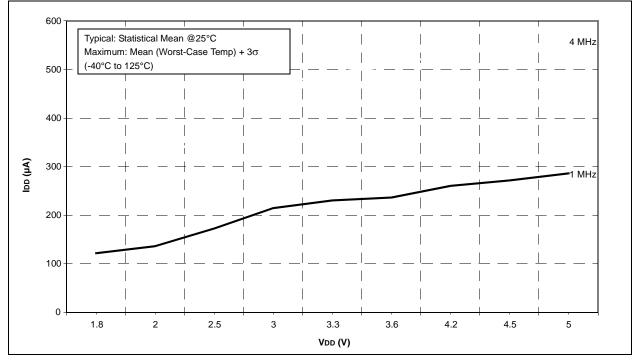

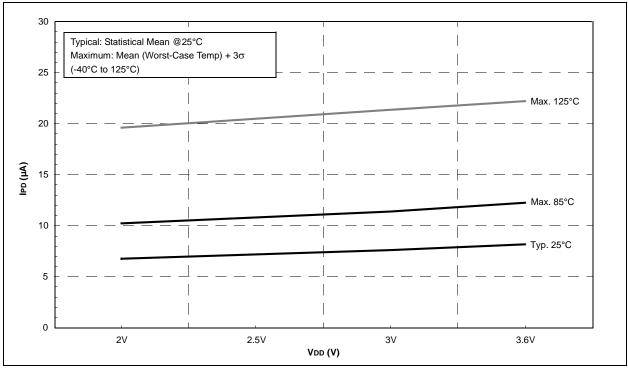

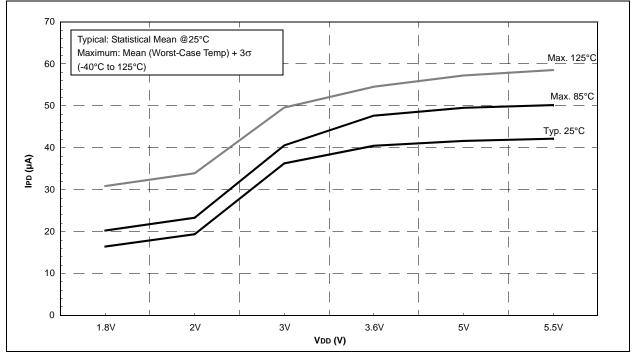

| 26.0  | DC and AC Characteristics Graphs and Charts                                  |      |

| 27.0  | Packaging Information                                                        |      |

|       | ndix A: Data Sheet Revision History                                          |      |

|       | ndix B: Migrating From Other PIC <sup>®</sup> Devices                        |      |

|       | /icrochip Website                                                            |      |

|       | omer Change Notification Service                                             |      |

|       | omer Support                                                                 |      |

| Produ | uct Identification System                                                    | 266  |

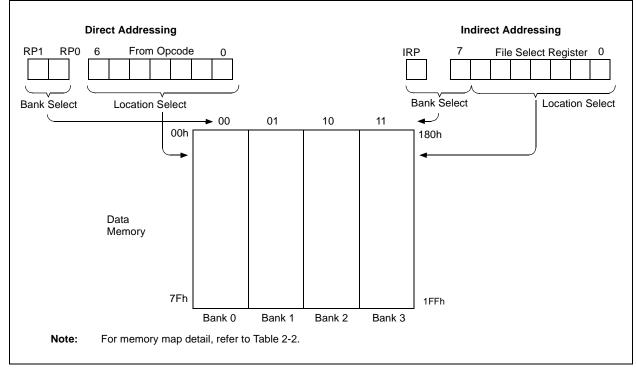

#### 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no operation (although Status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit of the STATUS register, as shown in Figure 2-3.

A simple program to clear RAM location 020h-02Fh using indirect addressing is shown in Example 2-2.

#### EXAMPLE 2-2: INDIRECT ADDRESSING

|      | MOVLW<br>MOVWF<br>BANKISEL | 020h<br>FSR<br>020h | ;initialize pointer<br>;to RAM |

|------|----------------------------|---------------------|--------------------------------|

| NEXT | CLRF                       | INDF                | clear INDF register;           |

|      | INCF                       | FSR                 | ;inc pointer                   |

|      | BTFSS                      | FSR,4               | ;all done?                     |

|      | GOTO                       | NEXT                | ;no clear next                 |

| CONT | INUE                       |                     | ;yes continue                  |

|      |                            |                     |                                |

#### FIGURE 2-3: DIRECT/INDIRECT ADDRESSING

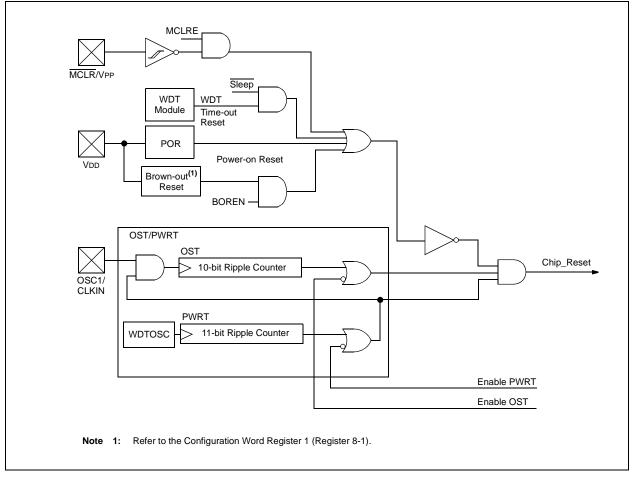

# 3.0 RESETS

The PIC16(L)F707 differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) WDT Reset during normal operation

- c) WDT Reset during Sleep

- d) MCLR Reset during normal operation

- e) MCLR Reset during Sleep

- f) Brown-out Reset (BOR)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- Power-on Reset (POR)

- MCLR Reset

- MCLR Reset during Sleep

- WDT Reset

- Brown-out Reset (BOR)

Most registers are not affected by a WDT wake-up since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different Reset situations, as indicated in Table 3-3. These bits are used in software to determine the nature of the Reset.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 3-1.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See **Section 25.0** "**Electrical Specifications**" for pulse width specifications.

#### FIGURE 3-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

| Register | Address | Power-on Reset/<br>Brown-out Reset <sup>(1)</sup> | MCLR Reset/<br>WDT Reset | Wake-up from Sleep through<br>Interrupt/Time-out |

|----------|---------|---------------------------------------------------|--------------------------|--------------------------------------------------|

| TBCON    | 111h    | 0-00 0000                                         | 0-00 0000                | u-uu uuuu                                        |

| TMRB     | 112h    | 0000 0000                                         | 0000 0000                | uuuu uuuu                                        |

| DACCON0  | 113h    | 000- 00                                           | 000- 00                  | uuu- uu                                          |

| DACCON1  | 114h    | 0 0000                                            | 0 0000                   | u uuuu                                           |

| ANSELA   | 185h    | 1111 1111                                         | 1111 1111                | uuuu uuuu                                        |

| ANSELB   | 186h    | 1111 1111                                         | 1111 1111                | uuuu uuuu                                        |

| ANSELC   | 187h    | 1111 1111                                         | 1111 1111                | uuuu uuuu                                        |

| ANSELD   | 188h    | 1111 1111                                         | 1111 1111                | uuuu uuuu                                        |

| ANSELE   | 189h    | 111                                               | 111                      | uuu                                              |

| PMCON1   | 18Ch    | 10                                                | 10                       | uu                                               |

#### TABLE 3-5: INITIALIZATION CONDITION FOR REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

- 2: One or more bits in INTCON and/or PIR1 and PIR2 will be affected (to cause wake-up).

- **3:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

- 4: See Table 3-2 for Reset value for specific condition.

- **5:** If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

#### TABLE 3-6: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets <sup>(1)</sup> |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|----------------------|------------------------------------------------|

| STATUS | IRP   | RP1   | RP0   | TO    | PD    | Z     | DC    | С     | 0001 1xxx            | 000q quuu                                      |

| PCON   | _     | _     | _     | _     | _     | _     | POR   | BOR   | dd                   | uu                                             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition. Shaded cells are not used by Resets.

Note 1: Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

### 6.2 PORTA and TRISA Registers

PORTA is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 6-3). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 6-1 shows how to initialize PORTA.

Reading the PORTA register (Register 6-2) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch.

The TRISA register (Register 6-3) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the

#### REGISTER 6-2: PORTA: PORTA REGISTER

TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

| Note: | The ANSELA register must be initialized     |

|-------|---------------------------------------------|

|       | to configure an analog channel as a digital |

|       | input. Pins configured as analog inputs     |

|       | will read '0'.                              |

| EXAMPLE 6-1:                                                                                              | INITIALIZING PORTA                                                                                          |

|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| BANKSEL PORTA<br>CLRF PORTA<br>BANKSEL ANSELA<br>CLRF ANSELA<br>BANKSEL TRISA<br>MOVLW OCh<br>MOVWF TRISA | ;<br>;Init PORTA<br>;<br>;digital I/O<br>;<br>;Set RA<3:2> as inputs<br>;and set RA<7:4,1:0><br>;as outputs |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| RA7   | RA6   | RA5   | RA4   | RA3   | RA2   | RA1   | RA0   |

| bit 7 |       |       |       |       |       |       | bit 0 |

|       |       |       |       |       |       |       |       |

| Legena.           |                  |                                |                    |

|-------------------|------------------|--------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as | ʻO'                |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared           | x = Bit is unknown |

bit 7-0 **RA<7:0>**: PORTA I/O Pin bits

1 = Port pin is > VIH

0 = Port pin is < VIL

#### REGISTER 6-3: TRISA: PORTA TRI-STATE REGISTER

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 |

| bit 7  | •      |        |        | •      |        |        | bit 0  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 7-0

l egend.

TRISA<7:0>: PORTA Tri-State Control bits

1 = PORTA pin configured as an input (tri-stated)

0 = PORTA pin configured as an output

# 7.6 External Clock Modes

#### 7.6.1 OSCILLATOR START-UP TIMER (OST)

If the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations on the OSC1 pin before the device is released from Reset. This occurs following a Power-on Reset (POR) and when the Power-up Timer (PWRT) has expired (if configured), or a wake-up from Sleep. During this time, the program counter does not increment and program execution is suspended. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module.

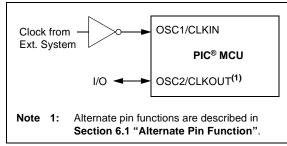

#### 7.6.2 EC MODE

The External Clock (EC) mode allows an externally generated logic level as the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input and the OSC2 is available for general purpose I/O. Figure 7-2 shows the pin connections for EC mode.

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### FIGURE 7-2: EXTERNAL CLOCK (EC) MODE OPERATION

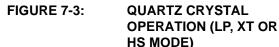

#### 7.6.3 LP, XT, HS MODES

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 7-3). The mode selects a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

LP Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is best suited to drive resonators with a low drive level specification, for example, tuning fork type crystals.

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 7-3 and Figure 7-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

**Note 1:** A series resistor (Rs) may be required for quartz crystals with low drive level.

2: The value of RF varies with the Oscillator mode selected.

Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- 2: Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

### REGISTER 10-1: FVRCON: FIXED VOLTAGE REFERENCE REGISTER

| R-q                                                                         | R/W-0/0                                                                                                                                                                              | R/W-0/0          | R/W-0/0       | R/W-0/0                   | R/W-0/0                | R/W-0/0                     | R/W-0/0               |  |  |

|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|---------------------------|------------------------|-----------------------------|-----------------------|--|--|

| FVRRDY <sup>(1)</sup>                                                       | FVREN                                                                                                                                                                                | _                | _             | CDAFVR1 <sup>(2)</sup>    | CDAFVR0 <sup>(2)</sup> | ADFVR1 <sup>(2)</sup>       | ADFVR0 <sup>(2)</sup> |  |  |

| bit 7                                                                       | 1                                                                                                                                                                                    |                  |               |                           |                        |                             | bit 0                 |  |  |

|                                                                             |                                                                                                                                                                                      |                  |               |                           |                        |                             |                       |  |  |

| Legend:                                                                     |                                                                                                                                                                                      |                  |               |                           |                        |                             |                       |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'        |                                                                                                                                                                                      |                  |               |                           |                        |                             |                       |  |  |

| -n = Value at P                                                             | OR                                                                                                                                                                                   | '1' = Bit is set |               | '0' = Bit is clea         | ared                   | x = Bit is unkr             | nown                  |  |  |

| q = Value depe                                                              | ends on condition                                                                                                                                                                    | on               |               |                           |                        |                             |                       |  |  |

|                                                                             |                                                                                                                                                                                      |                  |               |                           |                        |                             |                       |  |  |

| bit 7                                                                       | FVRRDY: Fix                                                                                                                                                                          | ed Voltage Refe  | erence Read   | y Flag bit <sup>(1)</sup> |                        |                             |                       |  |  |

|                                                                             |                                                                                                                                                                                      | 0                | •             | ot active or stable       | e                      |                             |                       |  |  |

|                                                                             |                                                                                                                                                                                      | tage Reference   |               | ,                         |                        |                             |                       |  |  |

| bit 6                                                                       |                                                                                                                                                                                      | d Voltage Refer  |               | bit                       |                        |                             |                       |  |  |

|                                                                             |                                                                                                                                                                                      | tage Reference   |               |                           |                        |                             |                       |  |  |

|                                                                             | 1 = Fixed Vol                                                                                                                                                                        | tage Reference   | e is enabled  |                           |                        |                             |                       |  |  |

| bit 5-4                                                                     | Reserved: Re                                                                                                                                                                         | ead as '0'. Mair | tain these bi | ts clear                  |                        |                             |                       |  |  |

| bit 3-2                                                                     | CDAFVR<1:0                                                                                                                                                                           | >: Cap Sense     | and D/A Con   | verter Fixed Vol          | tage Reference         | Selection bit <sup>(2</sup> |                       |  |  |

|                                                                             | 00 = CSM an                                                                                                                                                                          | d D/A Converte   | r Fixed Volta | ige Reference P           | eripheral output       | is off.                     |                       |  |  |

|                                                                             |                                                                                                                                                                                      |                  |               | ige Reference P           | • •                    | •                           |                       |  |  |

|                                                                             |                                                                                                                                                                                      |                  |               | ige Reference P           | •                      | •                           |                       |  |  |

|                                                                             |                                                                                                                                                                                      |                  |               | ige Reference P           |                        | is 4x (4.096V)              | )                     |  |  |

| bit 1-0                                                                     |                                                                                                                                                                                      |                  |               | ge Reference S            |                        |                             |                       |  |  |

|                                                                             |                                                                                                                                                                                      |                  | •             | ence Peripheral           |                        |                             |                       |  |  |

| 01 = A/D Converter Fixed Voltage Reference Peripheral output is 1x (1.024V) |                                                                                                                                                                                      |                  |               |                           |                        |                             |                       |  |  |

|                                                                             | <ul> <li>10 = A/D Converter Fixed Voltage Reference Peripheral output is 2x (2.048V)</li> <li>11 = A/D Converter Fixed Voltage Reference Peripheral output is 4x (4.096V)</li> </ul> |                  |               |                           |                        |                             |                       |  |  |

|                                                                             |                                                                                                                                                                                      |                  | maye relete   | fice renpuela             | 001pul 15 4x (4.t      | (30 V)                      |                       |  |  |

| Note 1: FVF                                                                 | RDY is always                                                                                                                                                                        | 1' on PIC16F     | 707 devices.  |                           |                        |                             |                       |  |  |

2: Fixed Voltage Reference output cannot exceed VDD.

#### TABLE 10-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Name   | Bit 7  | Bit 6 | Bit 5    | Bit 4    | Bit 3   | Bit 2   | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|--------|-------|----------|----------|---------|---------|--------|--------|----------------------|---------------------------------|

| FVRCON | FVRRDY | FVREN | Reserved | Reserved | CDAFVR1 | CDAFVR0 | ADFVR1 | ADFVR0 | d000 0000            | d000 0000                       |

Legend: Shaded cells are not used by the voltage reference module.

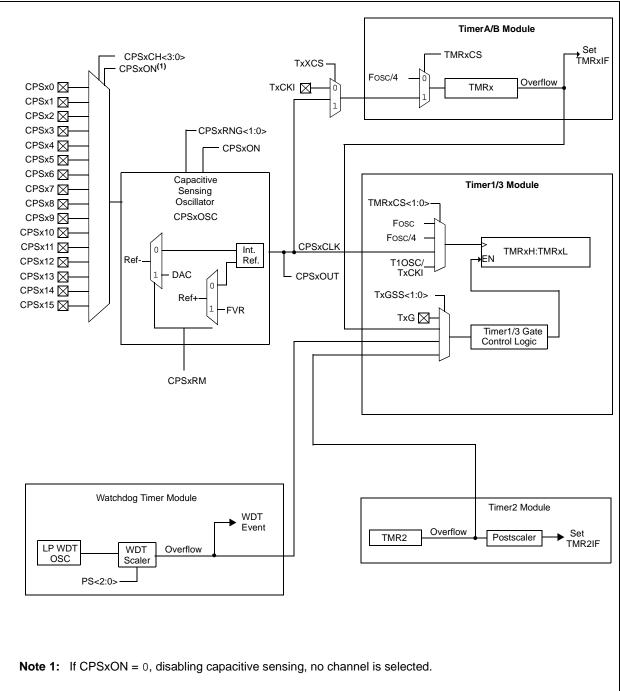

# TABLE 13-1:CPSOSC/TIMERASSOCIATION

| Period<br>Measurement | Cap Sense<br>Oscillator | Divider Timer<br>(Gate Source) |

|-----------------------|-------------------------|--------------------------------|

| Timer1                | CPS A                   | TimerA                         |

| Timer3                | CPS B                   | TimerB                         |

# 13.8 Timer1/3 Operation During Sleep

Timer1/3 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMRxON bit of the TxCON register must be set

- TMRxIE bit of the PIEx register must be set

- · PEIE bit of the INTCON register must be set

- TxSYNC bit of the TxCON register must be set

- TMRxCS bits of the TxCON register must be configured

- T1OSCEN bit of the T1CON register must be configured

- TMRxGIE bit of the TxGCON register must be configured

The device will wake-up on an overflow and execute the next instructions. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine (0004h).

# 13.9 CCP Capture/Compare Time Base (Timer1 Only)

The CCP module uses the TMR1H:TMR1L register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPR1H:CCPR1L register pair on a configured event.

In Compare mode, an event is triggered when the value CCPR1H:CCPR1L register pair matches the value in the TMR1H:TMR1L register pair. This event can be a Special Event Trigger.

For more information, see Section 17.0 "Capture/ Compare/PWM (CCP) Module".

# 13.10 CCP Special Event Trigger (Timer1 only)

When the CCP is configured to trigger a special event, the trigger will clear the TMR1H:TMR1L register pair. This special event does not cause a Timer1 interrupt. The CCP module may still be configured to generate a CCP interrupt.

In this mode of operation, the CCPR1H:CCPR1L register pair becomes the period register for Timer1.

Timer1 should be synchronized to the FOSC/4 to utilize the Special Event Trigger. Asynchronous operation of Timer1 can cause a Special Event Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with a Special Event Trigger from the CCP, the write will take precedence.

For more information, see Section 17.2.4 "Special Event Trigger".

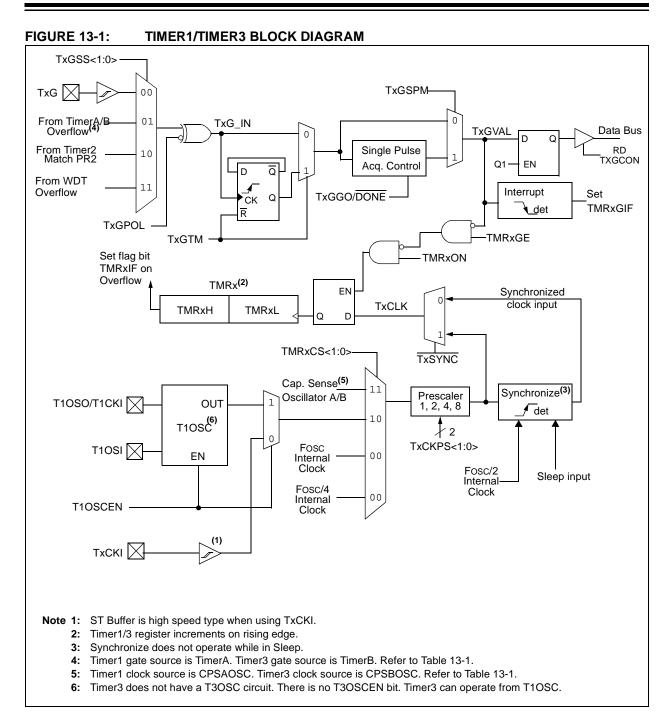

#### FIGURE 13-2: TIMER1/TIMER3 INCREMENTING EDGE

2: In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge of the clock.

|                  | 1. 12001      |                 |                                      |                  |                  |                 |         |

|------------------|---------------|-----------------|--------------------------------------|------------------|------------------|-----------------|---------|

| R/W-0/0          | U-0           | R/W-0/0         | R/W-0/0                              | R/W-0/0          | R/W-0/0          | R/W-0/0         | R/W-0/0 |

| TMRxON           | _             | TMRxCS          | TMRxSE                               | TMRxPSA          | TMRxPS2          | TMRxPS1         | TMRxPS0 |

| bit 7            |               |                 |                                      |                  |                  |                 | bit C   |

|                  |               |                 |                                      |                  |                  |                 |         |

| Legend:          |               |                 |                                      |                  |                  |                 |         |

| R = Readable b   | it            | W = Writable    | e bit                                | U = Unimpler     | mented bit, read | d as '0'        |         |

| -n = Value at PC | DR            | '1' = Bit is se | et                                   | '0' = Bit is cle | ared             | x = Bit is unki | nown    |

|                  |               |                 |                                      |                  |                  |                 |         |

| bit 7            | TMRxON: Tim   | nerA/TimerB     | On/Off Control                       | bit              |                  |                 |         |

|                  | 1 = Timerx is |                 |                                      |                  |                  |                 |         |

|                  | 0 = Timerx is |                 |                                      |                  |                  |                 |         |

| bit 6            | Unimplement   | ted: Read as    | '0'                                  |                  |                  |                 |         |

|                  |               |                 | urce Select bit                      |                  |                  |                 |         |

|                  |               |                 | n or CPSxOSC                         | •                |                  |                 |         |

|                  |               |                 | le clock (Fosc/                      | 4)               |                  |                 |         |

|                  | TMRxSE: TM    |                 | 0                                    |                  |                  |                 |         |

|                  |               | 0               | ow transition on<br>gh transition on | •                |                  |                 |         |

|                  | TMRxPSA: P    |                 |                                      | ·                |                  |                 |         |

|                  | 1 = Prescaler | is disabled.    | c<br>Fimer clock inp                 | ut bypasses pro  | escaler.         |                 |         |

|                  | 0 = Prescaler | is enabled. T   | imer clock inpu                      | ut comes from t  | he prescaler ou  | utput.          |         |

| bit 2-0          | TMRxPS<2:0    | >: Prescaler    | Rate Select bit                      | S                |                  |                 |         |

|                  | BIT           | ALUE TMRx       | RATE                                 |                  |                  |                 |         |

|                  | 0             | 00 1::          | 2                                    |                  |                  |                 |         |

|                  |               |                 |                                      |                  |                  |                 |         |

|                  | 01            | 10 1:           | 8                                    |                  |                  |                 |         |

# REGISTER 14-1: TxCON: TIMERA/TIMERB CONTROL REGISTER

# TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH TIMERA/B

1 : 16 1 : 32

1:64

1:128

1:256

011

100

101 110

111

| Name     | Bit 7   | Bit 6                  | Bit 5  | Bit 4     | Bit 3          | Bit 2    | Bit 1   | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|----------|---------|------------------------|--------|-----------|----------------|----------|---------|--------|----------------------|---------------------------------|

| CPSACON0 | CPSAON  | CPSARM                 | -      | _         | CPSARNG1       | CPSARNG0 | CPSAOUT | TAXCS  | 00 0000              | 00 0000                         |

| CPSBCON0 | CPSBON  | CPSBRM                 | _      | _         | CPSBRNG1       | CPSBRNG0 | CPSBOUT | TBXCS  | 00 0000              | 00 0000                         |

| PIE2     | TMR3GIE | TMR3IE                 | TMRBIE | TMRAIE    | —              | _        | _       | CCP2IE | 00000                | 00000                           |

| PIR2     | TMR3GIF | TMR3IF                 | TMRBIF | TMRAIF    | —              | _        | _       | CCP2IF | 00000                | 00000                           |

| TACON    | TMRAON  | _                      | TACS   | TASE      | TAPSA          | TAPS2    | TAPS1   | TAPS0  | 0-00 0000            | 0-00 0000                       |

| TBCON    | TMRBON  | _                      | TBCS   | TBSE      | TBPSA          | TBPS2    | TBPS1   | TBPS0  | 0-00 0000            | 0-00 0000                       |

| TMRA     |         |                        |        | TimerA Mo | odule Register |          |         |        | 0000 0000            | 0000 0000                       |

| TMRB     |         | TimerB Module Register |        |           |                |          |         |        | 0000 0000            | 0000 0000                       |

| TRISA    | TRISA7  | TRISA6                 | TRISA5 | TRISA4    | TRISA3         | TRISA2   | TRISA1  | TRISA0 | 1111 1111            | 1111 1111                       |

| TRISC    | TRISC7  | TRISC6                 | TRISC5 | TRISC4    | TRISC3         | TRISC2   | TRISC1  | TRISC0 | 1111 1111            | 1111 1111                       |

Legend: -= Unimplemented locations, read as '0'. Shaded cells are not used by the TimerA/B modules.

| U-0          | R/W-0                                          | R/W-0            | R/W-0          | R/W-0             | R/W-0           | R/W-0           | R/W-0   |  |  |  |  |

|--------------|------------------------------------------------|------------------|----------------|-------------------|-----------------|-----------------|---------|--|--|--|--|

| _            | TOUTPS3                                        | TOUTPS2          | TOUTPS1        | TOUTPS0           | TMR2ON          | T2CKPS1         | T2CKPS0 |  |  |  |  |

| bit 7        |                                                |                  |                |                   |                 |                 | bit C   |  |  |  |  |

|              |                                                |                  |                |                   |                 |                 |         |  |  |  |  |

| Legend:      |                                                |                  |                |                   |                 |                 |         |  |  |  |  |

| R = Readal   | ble bit                                        | W = Writable     | bit            | U = Unimplen      | nented bit, rea | d as '0'        |         |  |  |  |  |

| -n = Value a | at POR                                         | '1' = Bit is set |                | '0' = Bit is clea | ared            | x = Bit is unkr | nown    |  |  |  |  |

|              |                                                |                  |                |                   |                 |                 |         |  |  |  |  |

| bit 7        | Unimplemen                                     | ted: Read as '   | 0'             |                   |                 |                 |         |  |  |  |  |

| bit 6-3      | TOUTPS<3:0                                     | )>: Timer2 Outp  | out Postscaler | Select bits       |                 |                 |         |  |  |  |  |

|              | 0000 = 1:1 P                                   | ostscaler        |                |                   |                 |                 |         |  |  |  |  |

|              | 0001 = 1:2 P                                   | ostscaler        |                |                   |                 |                 |         |  |  |  |  |

|              | 0010 = 1:3 P                                   |                  |                |                   |                 |                 |         |  |  |  |  |

|              | 0011 = 1:4 P                                   |                  |                |                   |                 |                 |         |  |  |  |  |

|              | 0100 = 1:5 P                                   |                  |                |                   |                 |                 |         |  |  |  |  |

|              | 0101 = 1:6 Postscaler<br>0110 = 1:7 Postscaler |                  |                |                   |                 |                 |         |  |  |  |  |

|              | 0110 = 1.7 P<br>0111 = 1.8 P                   |                  |                |                   |                 |                 |         |  |  |  |  |

|              | 1000 = 1.9 P                                   |                  |                |                   |                 |                 |         |  |  |  |  |

|              | 1000 = 1.91<br>1001 = 1.10                     |                  |                |                   |                 |                 |         |  |  |  |  |

|              | 1000 = 1:10                                    |                  |                |                   |                 |                 |         |  |  |  |  |

|              | 1011 = 1:12                                    |                  |                |                   |                 |                 |         |  |  |  |  |

|              | 1100 <b>= 1:13</b>                             | Postscaler       |                |                   |                 |                 |         |  |  |  |  |

|              | 1101 <b>= 1:14</b>                             | Postscaler       |                |                   |                 |                 |         |  |  |  |  |

|              | 1110 <b>= 1:15</b>                             |                  |                |                   |                 |                 |         |  |  |  |  |

|              | 1111 <b>= 1:16</b>                             | Postscaler       |                |                   |                 |                 |         |  |  |  |  |

| bit 2        | TMR2ON: Tir                                    | mer2 On bit      |                |                   |                 |                 |         |  |  |  |  |

|              | 1 = Timer2 is                                  | s on             |                |                   |                 |                 |         |  |  |  |  |

|              | 0 = Timer2 is                                  | soff             |                |                   |                 |                 |         |  |  |  |  |

| bit 1-0      | T2CKPS<1:0                                     | >: Timer2 Cloc   | k Prescale Se  | lect bits         |                 |                 |         |  |  |  |  |

|              | 00 = Prescale                                  | er is 1          |                |                   |                 |                 |         |  |  |  |  |

|              | 01 = Prescale                                  | er is 4          |                |                   |                 |                 |         |  |  |  |  |

|              | 1x = Prescale                                  | er is 16         |                |                   |                 |                 |         |  |  |  |  |

# REGISTER 15-1: T2CON: TIMER2 CONTROL REGISTER

| TABLE 15-1: | SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2 |

|-------------|---------------------------------------------|

|-------------|---------------------------------------------|

| Name    | Bit 7                                                    | Bit 6 | Bit 5  | Bit 4        | Bit 3           | Bit 2          | Bit 1  | Bit 0        | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|----------------------------------------------------------|-------|--------|--------------|-----------------|----------------|--------|--------------|----------------------|---------------------------------|

| INTCON  | GIE                                                      | PEIE  | TMR0IE | INTE         | RBIE            | TMR0IF         | INTF   | RBIF         | 0000 000x            | 0000 000x                       |

| PIE1    | TMR1GIE                                                  | ADIE  | RCIE   | TXIE         | SSPIE           | CCP1IE         | TMR2IE | TMR1IE       | 0000 0000            | 0000 0000                       |

| PIR1    | TMR1GIF                                                  | ADIF  | RCIF   | TXIF         | SSPIF           | CCP1IF         | TMR2IF | TMR1IF       | 0000 0000            | 0000 0000                       |

| PR2     |                                                          |       | Т      | imer2 Module | Period Regis    | ter            |        |              | 1111 1111            | 1111 1111                       |

| TMR2    |                                                          |       |        | 0000 0000    | 0000 0000       |                |        |              |                      |                                 |

| T2CON   | - TOUTPS3 TOUTPS2 TOUTPS1 TOUTPS0 TMR2ON T2CKPS1 T2CKPS0 |       |        |              |                 |                |        |              | -000 0000            | -000 0000                       |

| Logondu | مبامير                                                   |       | and u  |              | l read as (o) ( | Shadad aalla a |        | r Timor2 mod | lula                 |                                 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for Timer2 module.

#### 17.3.2 PWM PERIOD

The PWM period is specified by the PR2 register of Timer2. The PWM period can be calculated using the formula of Equation 17-1.

### EQUATION 17-1: PWM PERIOD

$PWM Period = [(PR2) + 1] \bullet 4 \bullet Tosc \bullet$ (TMR2 Prescale Value)

**Note:** Tosc = 1/Fosc

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCPx pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is latched from CCPRxL into CCPRxH.

| Note: | The    | Timer2    | postscaler   | (refer   | to |

|-------|--------|-----------|--------------|----------|----|

|       |        |           | Timer2 Ope   |          |    |

|       | used   | in the de | etermination | of the P | WM |

|       | freque |           |              |          |    |

### 17.3.3 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to multiple registers: CCPRxL register and DCxB<1:0> bits of the CCPxCON register. The CCPRxL contains the eight MSbs and the DCxB<1:0> bits of the CCPxCON register contain the two LSbs. CCPRxL and DCxB<1:0> bits of the CCPxCON register can be written to at any time. The duty cycle value is not latched into CCPRxH until after the period completes (i.e., a match between PR2 and TMR2 registers occurs). While using the PWM, the CCPRxH register is read-only.

Equation 17-2 is used to calculate the PWM pulse width.

Equation 17-3 is used to calculate the PWM duty cycle ratio.

## EQUATION 17-2: PULSE WIDTH

Pulse Width =

$$(CCPRxL:CCPxCON < 5:4>)$$

•

TOSC • (TMR2 Prescale Value)

Note: Tosc = 1/Fosc

# EQUATION 17-3: DUTY CYCLE RATIO

Duty Cycle Ratio =  $\frac{(CCPRxL:CCPxCON < 5:4>)}{4(PR2 + 1)}$

The CCPRxH register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (Fosc), or 2 bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH and 2-bit latch, then the CCPx pin is cleared (refer to Figure 17-3).

#### 17.3.4 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 17-4.

#### EQUATION 17-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2 + 1)]}{\log(2)}$$

bits

Note: If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

### TABLE 17-5: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 17-6: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

#### 17.3.5 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 17.3.6 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency (FOSC). Any changes in the system clock frequency will result in changes to the PWM frequency. Refer to **Section 7.0** "**Oscillator Module**" for additional details.

#### 17.3.7 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

#### 17.3.8 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Disable the PWM pin (CCPx) output driver(s) by setting the associated TRIS bit(s).

- 2. Load the PR2 register with the PWM period value.

- Configure the CCP module for the PWM mode by loading the CCPxCON register with the appropriate values.

- 4. Load the CCPRxL register and the DCxBx bits of the CCPxCON register, with the PWM duty cycle value.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register. See Note below.

- Configure the T2CKPS bits of the T2CON register with the Timer2 prescale value.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

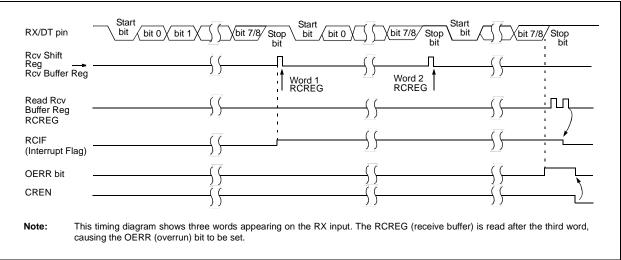

#### TABLE 18-2: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Name   | Bit 7   | Bit 6  | Bit 5  | Bit 4      | Bit 3      | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|---------|--------|--------|------------|------------|--------|--------|--------|----------------------|---------------------------------|

| ANSELC | ANSC7   | ANSC6  | ANSC5  | —          | —          | ANSC2  | ANSC1  | ANSC0  | 111111               | 111111                          |

| INTCON | GIE     | PEIE   | TMR0IE | INTE       | RBIE       | TMR0IF | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE | ADIE   | RCIE   | TXIE       | SSPIE      | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF | ADIF   | RCIF   | TXIF       | SSPIF      | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCREG  |         |        | AUSA   | ART Receiv | e Data Reg | jister |        |        | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN    | RX9    | SREN   | CREN       | ADDEN      | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| SPBRG  | BRG7    | BRG6   | BRG5   | BRG4       | BRG3       | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |

| TRISC  | TRISC7  | TRISC6 | TRISC5 | TRISC4     | TRISC3     | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXSTA  | CSRC    | TX9    | TXEN   | SYNC       | _          | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for asynchronous reception.

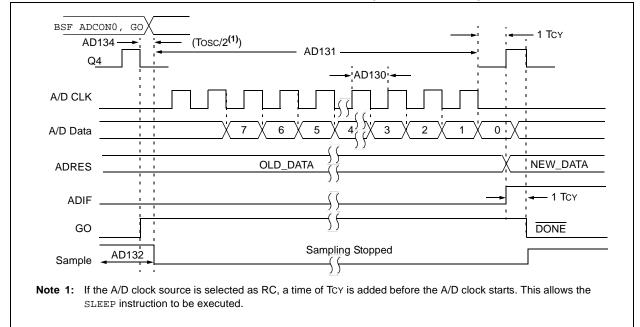

#### TABLE 25-8: PIC16F707 A/D CONVERSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)         Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                                                                 |      |      |      |       |                                        |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------|------|------|------|-------|----------------------------------------|--|--|--|--|

| Param<br>No.                                                                                                                  | Sym. | Characteristic                                                  | Min. | Тур† | Max. | Units | Conditions                             |  |  |  |  |

| AD130*                                                                                                                        | Tad  | A/D Clock Period                                                | 1.0  | _    | 9.0  | μS    | Tosc-based                             |  |  |  |  |

|                                                                                                                               |      | A/D Internal RC Oscillator<br>Period                            | 1.0  | 2.0  | 6.0  | μS    | ADCS<1:0> = 11 (ADRC mode)             |  |  |  |  |

| AD131                                                                                                                         | TCNV | Conversion Time (not including Acquisition Time) <sup>(1)</sup> |      | 10.5 | -    | TAD   | Set GO/DONE bit to conversion complete |  |  |  |  |

| AD132*                                                                                                                        | TACQ | Acquisition Time                                                |      | 1.0  | —    | μS    |                                        |  |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The ADRES register may be read on the following TCY cycle.

#### FIGURE 25-12: PIC16F707 A/D CONVERSION TIMING (NORMAL MODE)

#### FIGURE 26-34: PIC16LF707 BOR IPD vs. VDD

40-Lead UQFN (5x5x0.5 mm) PIN 1-PIN 1-PIN 1-PIC 16F707 -I/MV @3 10033K1

|                                                                                                                       | Ourstand and sittle information                          |  |  |

|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|

| : XXX                                                                                                                 |                                                          |  |  |

| Y                                                                                                                     | Year code (last digit of calendar year)                  |  |  |

| YY                                                                                                                    | Year code (last 2 digits of calendar year)               |  |  |

| WW                                                                                                                    | Week code (week of January 1 is week '01')               |  |  |

| NNN                                                                                                                   | Alphanumeric traceability code                           |  |  |

| (e3)                                                                                                                  | Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn) |  |  |

| * This package is Pb-free. The Pb-free JEDEC <sup>®</sup> designator ( $_{(e3)}$ )                                    |                                                          |  |  |

|                                                                                                                       | can be found on the outer packaging for this package.    |  |  |

|                                                                                                                       |                                                          |  |  |

| In the event the full Microchip part number cannot be marked on one line, it will                                     |                                                          |  |  |

| be carried over to the next line, thus limiting the number of available characters for customer-specific information. |                                                          |  |  |

|                                                                                                                       | In the eve                                               |  |  |

\* Standard PICmicro<sup>®</sup> device marking consists of Microchip part number, year code, week code and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

# APPENDIX A: DATA SHEET REVISION HISTORY

# Revision A (4/2010)

Original release of this data sheet.

# Revision B (4/2011)

Updated the data sheet to new format; Added 40-Pin UQFN diagram; Updated Table 1 and Table 25-5; Added 40-Lead UQFN Package Marking Information and Package Details; Other minor corrections.

# **Revision C (12/2015)**

Updated the data sheet to the new format. Updated the first chapter of the data sheet to include the Memory section. Updated the Package Details for 44-Lead QFN and 40-Lead UQFN. Other minor corrections.

# APPENDIX B: MIGRATING FROM OTHER PIC<sup>®</sup> DEVICES

This discusses some of the issues in migrating from other  $PIC^{\textcircled{B}}$  devices to the PIC16F707 family of devices.

**Note:** This device has been designed to perform to the parameters of its data sheet. It has been tested to an electrical specification designed to determine its conformance with these parameters. Due to process differences in the manufacture of this device, this device may have different performance characteristics than its earlier version. These differences may cause this device to perform differently in your application than the earlier version of this device.

**Note:** The user should verify that the device oscillator starts and performs as expected. Adjusting the loading capacitor values and/or the oscillator mode may be required.

# B.1 PIC16F77 to PIC16F707

#### TABLE B-1: FEATURE COMPARISON

| Feature                               | PIC16F77 | PIC16F707           |

|---------------------------------------|----------|---------------------|

| Max. Operating Speed                  | 20 MHz   | 20 MHz              |

| Max. Program<br>Memory (Words)        | 8K       | 8K                  |

| Max. SRAM (Bytes)                     | 368      | 363                 |

| A/D Resolution                        | 8-bit    | 8-bit               |

| Timers (8/16-bit)                     | 2/1      | 4/2                 |

| Oscillator Modes                      | 4        | 8                   |

| Brown-out Reset                       | Y        | Y                   |

| Internal Pull-ups                     | RB<7:0>  | RB<7:0>             |

| Interrupt-on-change                   | RB<7:4>  | RB<7:0>             |

| Comparator                            | 0        | 0                   |

| USART                                 | Y        | Y                   |

| Extended WDT                          | N        | N                   |

| Software Control<br>Option of WDT/BOR | N        | Ν                   |

| INTOSC Frequencies                    | None     | 500 kHz -<br>16 MHz |

| Clock Switching                       | Ν        | N                   |