Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 36                                                                      |

| Program Memory Size        | 14KB (8K x 14)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 363 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                             |

| Data Converters            | A/D 14x8b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                |

| Supplier Device Package    | 40-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f707-i-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

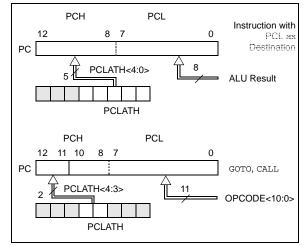

### 2.3 PCL and PCLATH

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 2-2 shows the two situations for the loading of the PC. The upper example in Figure 2-2 shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in Figure 2-2 shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

FIGURE 2-2: LOADING OF PC IN DIFFERENT SITUATIONS

### 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to Application Note AN556, *"Implementing a Table Read"* (DS00556).

### 2.3.2 STACK

All devices have an 8-level x 13-bit wide hardware stack (refer to Figure 2-1). The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth PUSH overwrites the value that was stored from the first PUSH. The tenth PUSH overwrites the second PUSH (and so on).

| Note 1: | There are no Status bits to indicate Stack |

|---------|--------------------------------------------|

|         | Overflow or Stack Underflow conditions.    |

2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

# 2.4 Program Memory Paging

All devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper two bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is POPed off the stack. Therefore, manipulation of the PCLATH<4:3> bits is not required for the RETURN instructions (which POPs the address from the stack).

| Note: | The contents of the PCLATH register are    |

|-------|--------------------------------------------|

|       | unchanged after a RETURN or RETFIE         |

|       | instruction is executed. The user must     |

|       | rewrite the contents of the PCLATH regis-  |

|       | ter for any subsequent subroutine calls or |

|       | GOTO instructions.                         |

Example 2-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the Interrupt Service Routine (if interrupts are used).

#### EXAMPLE 2-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

|         | ORG 500 | h       |                     |

|---------|---------|---------|---------------------|

|         | PAGESEL | SUB_P1  | ;Select page 1      |

|         |         |         | ;(800h-FFFh)        |

|         | CALL    | SUB1_P1 | ;Call subroutine in |

|         | :       |         | ;page 1 (800h-FFFh) |

|         | :       |         |                     |

|         | ORG     | 900h    | ;page 1 (800h-FFFh) |

| SUB1_P1 |         |         |                     |

|         | :       |         | ;called subroutine  |

|         |         |         | ;page 1 (800h-FFFh) |

|         | :       |         |                     |

|         | RETURN  |         | ;return to          |

|         |         |         | ;Call subroutine    |

|         |         |         | ;in page 0          |

|         |         |         | ;(000h-7FFh)        |

|         |         |         |                     |

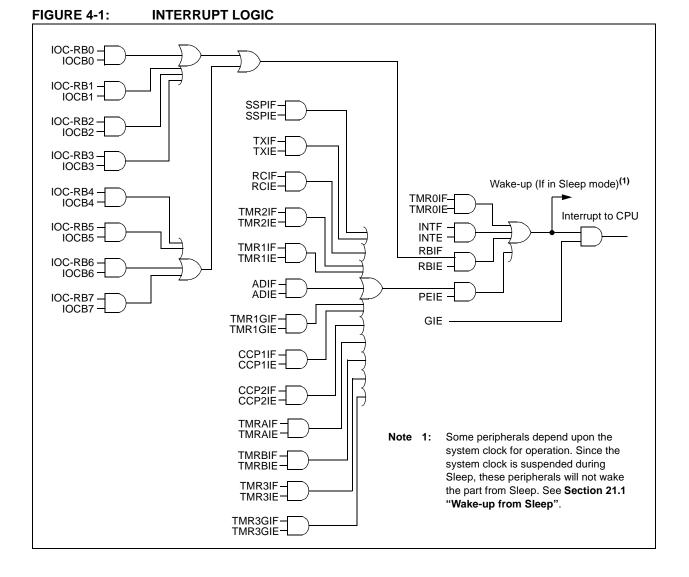

# 4.0 INTERRUPTS

The PIC16(L)F707 device family features an interruptible core, allowing certain events to preempt normal program flow. An Interrupt Service Routine (ISR) is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

The PIC16F707 family has 16 interrupt sources, differentiated by corresponding interrupt enable and flag bits:

- Timer0 Overflow Interrupt

- External Edge Detect on INT Pin Interrupt

- PORTB Change Interrupt

- Timer1 Gate Interrupt

- A/D Conversion Complete Interrupt

- AUSART Receive Interrupt

- AUSART Transmit Interrupt

- SSP Event Interrupt

- CCP1 Event Interrupt

- Timer2 Match with PR2 Interrupt

- Timer1 Overflow Interrupt

- CCP2 Event Interrupt

- TimerA Overflow Interrupt

- TimerB Overflow Interrupt

- Timer3 Overflow Interrupt

- Timer3 Gate Interrupt

A block diagram of the interrupt logic is shown in Figure 4-1.

| R/W-1        | R/W-1              | R/W-1                                                | R/W-1          | R/W-1            | R/W-1           | R/W-1           | R/W-1 |  |  |  |  |

|--------------|--------------------|------------------------------------------------------|----------------|------------------|-----------------|-----------------|-------|--|--|--|--|

| RBPU         | INTEDG             | TMR0CS                                               | TMR0SE         | PSA              | PS2             | PS1             | PS0   |  |  |  |  |

| bit 7        |                    |                                                      |                |                  |                 |                 | bit ( |  |  |  |  |

|              |                    |                                                      |                |                  |                 |                 |       |  |  |  |  |

| Legend:      |                    |                                                      |                |                  |                 |                 |       |  |  |  |  |

| R = Readab   | le bit             | W = Writable                                         | bit            | U = Unimpler     | nented bit, rea | d as '0'        |       |  |  |  |  |

| -n = Value a | t POR              | '1' = Bit is set                                     |                | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |  |  |  |  |

|              |                    |                                                      |                |                  |                 |                 |       |  |  |  |  |

| bit 7        | RBPU: POR          | TB Pull-up Enal                                      | ble bit        |                  |                 |                 |       |  |  |  |  |

|              |                    | oull-ups are disa                                    |                |                  |                 |                 |       |  |  |  |  |

|              | 0 <b>= PORTB</b> p | oull-ups are ena                                     | bled by indivi | dual PORT late   | h values        |                 |       |  |  |  |  |

| bit 6        | INTEDG: Inte       | errupt Edge Sel                                      | ect bit        |                  |                 |                 |       |  |  |  |  |

|              | 1 = Interrupt      | on rising edge                                       | of INT pin     |                  |                 |                 |       |  |  |  |  |

|              | 0 = Interrupt      | 0 = Interrupt on falling edge of INT pin             |                |                  |                 |                 |       |  |  |  |  |

| bit 5        | TMROCS: TA         | IR0 Clock Sou                                        | ce Select bit  |                  |                 |                 |       |  |  |  |  |

|              | 1 = Transitior     | 1 = Transition on T0CKI pin                          |                |                  |                 |                 |       |  |  |  |  |

|              |                    | 0 = Internal instruction cycle clock (Fosc/4)        |                |                  |                 |                 |       |  |  |  |  |

| bit 4        | TMR0SE: TM         | TMR0SE: TMR0 Source Edge Select bit                  |                |                  |                 |                 |       |  |  |  |  |

|              | 1 = Incremen       | 1 = Increment on high-to-low transition on TOCKI pin |                |                  |                 |                 |       |  |  |  |  |

|              |                    | 0 = Increment on low-to-high transition on TOCKI pin |                |                  |                 |                 |       |  |  |  |  |

| bit 3        | PSA: Presca        | ler Assignment                                       | bit            |                  |                 |                 |       |  |  |  |  |

|              |                    | is assigned to                                       |                |                  |                 |                 |       |  |  |  |  |

|              |                    | r is assigned to                                     |                | odule            |                 |                 |       |  |  |  |  |

| bit 2-0      |                    | escaler Rate Se                                      |                |                  |                 |                 |       |  |  |  |  |

|              | BIT                | VALUE TMR0 R                                         | ATE WDT RA     | TE               |                 |                 |       |  |  |  |  |

|              |                    | 000 1:2                                              | 1:1            |                  |                 |                 |       |  |  |  |  |

|              | (                  | 1:4                                                  | 1:2            |                  |                 |                 |       |  |  |  |  |

|              | (                  | 1:8                                                  | 1:4            |                  |                 |                 |       |  |  |  |  |

|              |                    | 1:16                                                 |                |                  |                 |                 |       |  |  |  |  |

|              | -                  | 1:32                                                 | _              |                  |                 |                 |       |  |  |  |  |

|              |                    | 1:64                                                 |                |                  |                 |                 |       |  |  |  |  |

|              | 1                  | 1:12 1:12                                            |                |                  |                 |                 |       |  |  |  |  |

# REGISTER 12-1: OPTION\_REG: OPTION REGISTER

#### TABLE 12-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER0

| Name       | Bit 7  | Bit 6                  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------|--------|------------------------|--------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON     | GIE    | PEIE                   | TMR0IE | INTE   | RBIE   | TMR0IF | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| OPTION_REG | RBPU   | INTEDG                 | TMR0CS | TMR0SE | PSA    | PS2    | PS1    | PS0    | 1111 1111            | 1111 1111                       |

| TMR0       |        | Timer0 Module Register |        |        |        |        |        |        | xxxx xxxx            | uuuu uuuu                       |

| TRISA      | TRISA7 | TRISA6                 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111            | 1111 1111                       |

- = Unimplemented locations, read as '0'. Shaded cells are not used by the Timer0 module. Legend:

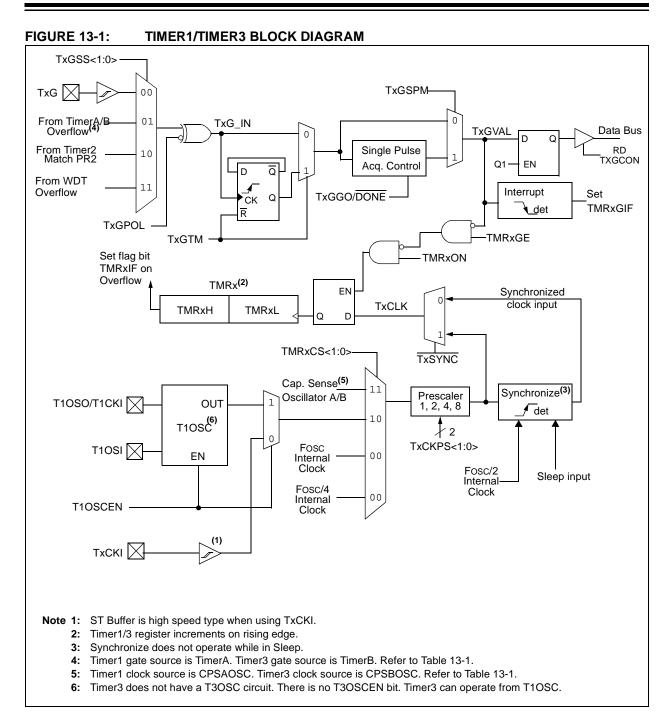

# TABLE 13-1:CPSOSC/TIMERASSOCIATION

| Period<br>Measurement | Cap Sense<br>Oscillator | Divider Timer<br>(Gate Source) |  |

|-----------------------|-------------------------|--------------------------------|--|

| Timer1                | CPS A                   | TimerA                         |  |

| Timer3                | CPS B                   | TimerB                         |  |

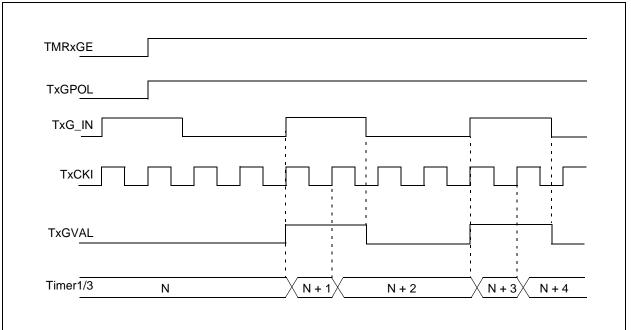

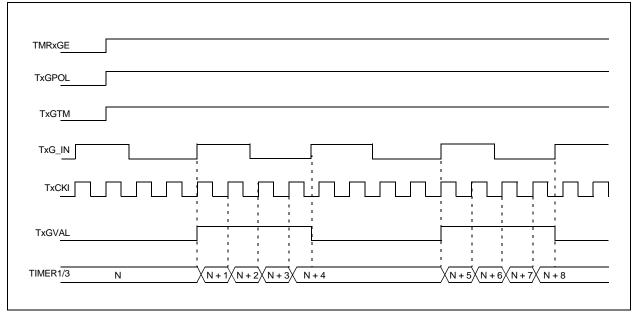

#### FIGURE 13-4: TIMER1/TIMER3 GATE TOGGLE MODE

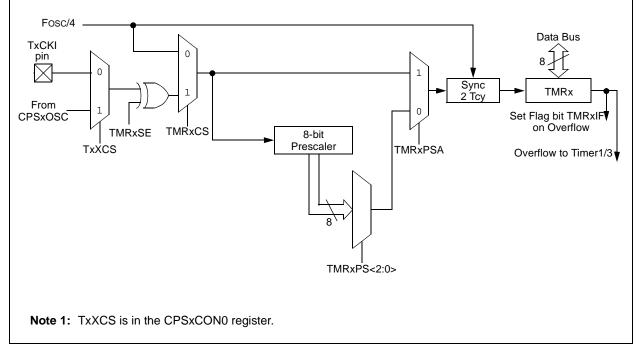

### 14.0 TIMERA/B MODULES

TimerA and TimerB are two more Timer0-type modules. Timers A and B are available as general-purpose timers/counters, and are closely integrated with the capacitive sensing modules.

The TimerA/B modules incorporate the following features:

- 8-bit timer/counter register (TMRx)

- 8-bit prescaler

- · Programmable internal or external clock source

- Programmable external clock edge selection

- Interrupt on overflow

- TMRA can be used to gate Timer1

- TMRB can be used to gate Timer3

Figure 14-1 is a block diagram of the TimerA/TimerB modules.

#### 18.1.2.1 Enabling the Receiver

The AUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other AUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCSTA register enables the receiver circuitry of the AUSART. Clearing the SYNC bit of the TXSTA register configures the AUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the AUSART and automatically configures the RX/DT I/O pin as an input.

| Note 1: | When the SPEN bit is set, the TX/CK I/O     |

|---------|---------------------------------------------|

|         | pin is automatically configured as an out-  |

|         | put, regardless of the state of the corre-  |

|         | sponding TRIS bit and whether or not the    |

|         | AUSART transmitter is enabled. The          |

|         | PORT latch is disconnected from the out-    |

|         | put driver so it is not possible to use the |

|         | TX/CK pin as a general purpose output.      |

| э.      | The corresponding ANCEL bit must be         |

2: The corresponding ANSEL bit must be cleared for the RX/DT port pin to ensure proper AUSART functionality.

#### 18.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. Refer to Section 18.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the AUSART receive FIFO and the RCIF interrupt flag bit of the PIR1 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCREG register.

| Note: |         |      |         | ) is overrun, i |          |       |

|-------|---------|------|---------|-----------------|----------|-------|

|       | charact | ers  | will be | received unti   | l the ov | errun |

|       |         |      | -       | cleared.        |          |       |

|       | Sectior | n 18 | .1.2.5  | "Receive        | Ove      | errun |

|       | Error"  | for  | more    | information     | on ov    | errun |

|       | errors. |      |         |                 |          |       |

#### 18.1.2.3 Receive Interrupts

The RCIF interrupt flag bit of the PIR1 register is set whenever the AUSART receiver is enabled and there is an unread character in the receive FIFO. The RCIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCIF interrupts are enabled by setting all of the following bits:

- RCIE, Receive Interrupt Enable bit of the PIE1

register

- PEIE, Peripheral Interrupt Enable bit of the INTCON register

- GIE, Global Interrupt Enable bit of the INTCON register

The RCIF interrupt flag bit of the PIR1 register will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

#### 18.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCSTA register which resets the AUSART. Clearing the CREN bit of the RCSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

Note: If all receive characters in the receive FIFO have framing errors, repeated reads of the RCREG will not clear the FERR bit.

#### 18.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCSTA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCSTA register or by setting the AUSART by clearing the SPEN bit of the RCSTA register.

#### 18.1.2.6 Receiving 9-bit Characters

The AUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the AUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

#### 18.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCIF interrupt bit of the PIR1 register. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

#### 18.1.2.8 Asynchronous Reception Set-up:

- Initialize the SPBRG register and the BRGH bit to achieve the desired baud rate (refer to Section 18.2 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Enable reception by setting the CREN bit.

- 6. The RCIF interrupt flag bit of the PIR1 register will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE bit of the PIE1 register was also set.

- 7. Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 8. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register.

- 9. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

This mode would typically be used in RS-485 systems. To set up an asynchronous reception with address detect enable:

- Initialize the SPBRG register and the BRGH bit to achieve the desired baud rate (refer to Section 18.2 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. Enable 9-bit reception by setting the RX9 bit.

- 5. Enable address detection by setting the ADDEN bit.

- 6. Enable reception by setting the CREN bit.

- The RCIF interrupt flag bit of the PIR1 register will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit of the PIE1 register was also set.

- 8. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

| R/W-0         | R/W-0                                         | R/W-0                               | R/W-0         | U-0              | R/W-0           | R-1             | R/W-0 |  |  |

|---------------|-----------------------------------------------|-------------------------------------|---------------|------------------|-----------------|-----------------|-------|--|--|

| CSRC          | TX9                                           | TXEN <sup>(1)</sup>                 | SYNC          |                  | BRGH            | TRMT            | TX9D  |  |  |

| bit 7         | ·                                             |                                     |               |                  |                 | ·               | bit 0 |  |  |

|               |                                               |                                     |               |                  |                 |                 |       |  |  |

| Legend:       |                                               |                                     |               |                  |                 |                 |       |  |  |

| R = Readable  |                                               | W = Writable I                      | DIt           | •                | mented bit, rea |                 |       |  |  |

| -n = Value at | PUR                                           | '1' = Bit is set                    |               | '0' = Bit is cle | eared           | x = Bit is unkr | IOWN  |  |  |

| bit 7         | CSRC: Cloc                                    | k Source Select                     | bit           |                  |                 |                 |       |  |  |

|               | <u>Asynchronou</u>                            | <u>us mode</u> :                    |               |                  |                 |                 |       |  |  |

|               | Don't care                                    |                                     |               |                  |                 |                 |       |  |  |

|               | Synchronous                                   |                                     |               |                  |                 |                 |       |  |  |

|               |                                               | mode (clock ger<br>node (clock from |               |                  | i)              |                 |       |  |  |

| bit 6         |                                               | ansmit Enable b                     |               | 100)             |                 |                 |       |  |  |

| Sit 0         |                                               | 9-bit transmissi                    |               |                  |                 |                 |       |  |  |

|               | 0 = Selects 8-bit transmission                |                                     |               |                  |                 |                 |       |  |  |

| bit 5         | TXEN: Transmit Enable bit <sup>(1)</sup>      |                                     |               |                  |                 |                 |       |  |  |

|               | 1 = Transmit enabled                          |                                     |               |                  |                 |                 |       |  |  |

|               | 0 = Transmi                                   |                                     |               |                  |                 |                 |       |  |  |

| bit 4         |                                               | ART Mode Sele                       | ct bit        |                  |                 |                 |       |  |  |

|               | 1 = Synchronous mode<br>0 = Asynchronous mode |                                     |               |                  |                 |                 |       |  |  |

| bit 3         |                                               | nted: Read as '(                    | )'            |                  |                 |                 |       |  |  |

| bit 2         | BRGH: High                                    | Baud Rate Sele                      | ect bit       |                  |                 |                 |       |  |  |

|               | Asynchronou                                   |                                     |               |                  |                 |                 |       |  |  |

|               | 1 = High sp                                   |                                     |               |                  |                 |                 |       |  |  |

|               | 0 = Low spectrum                              |                                     |               |                  |                 |                 |       |  |  |

|               | <u>Synchronous</u><br>Unused in th            |                                     |               |                  |                 |                 |       |  |  |

| bit 1         |                                               | smit Shift Registe                  | er Status bit |                  |                 |                 |       |  |  |

|               | 1 = TSR err                                   | -                                   |               |                  |                 |                 |       |  |  |

|               | 0 = TSR full                                  | l                                   |               |                  |                 |                 |       |  |  |

| bit 0         |                                               | bit of Transmit                     |               |                  |                 |                 |       |  |  |

|               | Can be addr                                   | ess/data bit or a                   | parity bit.   |                  |                 |                 |       |  |  |

|               |                                               |                                     |               |                  |                 |                 |       |  |  |

### REGISTER 18-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER

# 20.0 PROGRAM MEMORY READ

The Flash Program Memory is readable during normal operation over the full VDD range of the device. To read data from program memory, five Special Function Registers (SFRs) are used:

- PMCON1

- PMDATL

- PMDATH

- PMADRL

- PMADRH

The value written to the PMADRH:PMADRL register pair determines which program memory location is read. The read operation will be initiated by setting the RD bit of the PMCON1 register. The program memory flash controller takes two instructions to complete the read. As a consequence, after the RD bit has been set, the next two instructions will be ignored. To avoid conflict with program execution, it is recommended that the two instructions following the setting of the RD bit are NOP. When the read completes, the result is placed in the PMDATLH:PMDATL register pair. Refer to Example 20-1 for sample code.

Note: Code-protect does not effect the CPU from performing a read operation on the program memory. For more information, refer to Section 8.2 "Code Protection".

| Required | BANKSEL<br>MOVF<br>MOVF<br>MOVF<br>BANKSEL<br>BSF<br>NOP<br>NOP<br>BANKSEL<br>MOVF | PMADRL<br>MS_PROG_ADDR,<br>PMADRH<br>LS_PROG_ADDR,<br>PMADRL<br>PMCON1<br>PMCON1, RD<br>PMDATL<br>PMDATL | ;<br>W;<br>;MS Byte of Program Address to read<br>W;<br>;LS Byte of Program Address to read<br>;<br>;Initiate Read<br>;Any instructions here are ignored as program<br>;memory is read in second cycle after BSF<br>; |

|----------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sequ     | NOP                                                                                | PMDATL<br>PMDATL, W<br>LOWPMBYTE<br>PMDATH, W<br>HIGHPMBYTE                                              |                                                                                                                                                                                                                       |

|          | MOVWP                                                                              | RIGHPMBITE                                                                                               | /                                                                                                                                                                                                                     |

#### EXAMPLE 20-1: PROGRAM MEMORY READ

| RETFIE           | Return from Interrupt                                                                                                                                                                                              |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] RETFIE                                                                                                                                                                                                   |

| Operands:        | None                                                                                                                                                                                                               |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                                                                                                            |

| Status Affected: | None                                                                                                                                                                                                               |

| Description:     | Return from Interrupt. Stack is<br>POPed and Top-of-Stack (TOS) is<br>loaded in the PC. Interrupts are<br>enabled by setting Global<br>Interrupt Enable bit, GIE<br>(INTCON<7>). This is a 2-cycle<br>instruction. |

| Words:           | 1                                                                                                                                                                                                                  |

| Cycles:          | 2                                                                                                                                                                                                                  |

| Example:         | RETFIE                                                                                                                                                                                                             |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                             |

| RETLW            | Return with literal in W                                                                                                                                                                                                        |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                                                                        |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                                                             |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                                                                                                                                                    |

| Status Affected: | None                                                                                                                                                                                                                            |

| Description:     | The W register is loaded with the<br>8-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a 2-cycle instruction.                                                   |

| Words:           | 1                                                                                                                                                                                                                               |

| Cycles:          | 2                                                                                                                                                                                                                               |

| Example:         | CALL TABLE;W contains table                                                                                                                                                                                                     |

| TABLE            | <pre>;offset value<br/>;W now has table value<br/>ADDWF PC ;W = offset<br/>RETLW k1 ;Begin table<br/>RETLW k2 ;<br/>RETLW kn ; End of table<br/>Before Instruction<br/>W = 0x07<br/>After Instruction<br/>W = value of k8</pre> |

| RETURN           | Return from Subroutine                                                                                                                                                                                                          |

| Syntax:          | [label] RETURN                                                                                                                                                                                                                  |

| Operands:        | None                                                                                                                                                                                                                            |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                                                                                            |

| Status Affected: | None                                                                                                                                                                                                                            |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a 2-cycle instruc-<br>tion.                                                                      |

### 24.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 24.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline

assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

#### 24.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

### 24.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 25.5 Thermal Considerations

| Param<br>No. | Sym       | Characteristic                         | Тур  | Units | Conditions                                               |

|--------------|-----------|----------------------------------------|------|-------|----------------------------------------------------------|

| TH01         | θJA       | Thermal Resistance Junction to Ambient | 47.2 | °C/W  | 40-pin PDIP package                                      |

|              |           |                                        | 46   | °C/W  | 44-pin TQFP package                                      |

|              |           |                                        | 24.4 | °C/W  | 44-pin QFN 8x8mm package                                 |

|              |           |                                        | TBD  | °C/W  | 40-pin UQFN 5x5mm package                                |

| TH02         | θJC       | Thermal Resistance Junction to Case    | 24.7 | °C/W  | 40-pin PDIP package                                      |

|              |           |                                        | 14.5 | °C/W  | 44-pin TQFP package                                      |

|              |           | -                                      | 20   | °C/W  | 44-pin QFN 8x8mm package                                 |

|              |           | -                                      | TBD  | °C/W  | 40-pin UQFN 5x5mm package                                |

| TH03         | TJMAX     | Maximum Junction Temperature           | 150  | °C    |                                                          |

| TH04         | PD        | Power Dissipation                      | _    | W     | PD = PINTERNAL + PI/O                                    |

| TH05         | PINTERNAL | Internal Power Dissipation             | _    | W     | $PINTERNAL = IDD \times VDD^{(1)}$                       |

| TH06         | Pi/o      | I/O Power Dissipation                  | _    | W     | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |

| TH07         | Pder      | Derated Power                          | _    | W     | Pder = PDmax (Tj - Ta)/θja <sup>(2, 3)</sup>             |

**Note 1:** IDD is current to run the chip alone without driving any load on the output pins.

**2:** TA = Ambient Temperature

**3:** T<sub>J</sub> = Junction Temperature

#### FIGURE 25-11: CAPTURE/COMPARE/PWM TIMINGS (CCP)

#### TABLE 25-6: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP)

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                      |                |                       |      |      |       |                                 |

|----------------------------------------------------------------------------------------------------------------------|------|----------------------|----------------|-----------------------|------|------|-------|---------------------------------|

| Param<br>No.                                                                                                         | Sym. | Characteris          | stic           | Min.                  | Тур† | Max. | Units | Conditions                      |

| CC01*                                                                                                                | TccL | CCPx Input Low Time  | No Prescaler   | 0.5Tcy + 20           | —    | —    | ns    |                                 |

|                                                                                                                      |      |                      | With Prescaler | 20                    | _    | _    | ns    |                                 |

| CC02*                                                                                                                | TccH | CCPx Input High Time | No Prescaler   | 0.5Tcy + 20           | _    | _    | ns    |                                 |

|                                                                                                                      |      |                      | With Prescaler | 20                    |      |      | ns    |                                 |

| CC03*                                                                                                                | TccP | CCPx Input Period    |                | <u>3Tcy + 40</u><br>N | _    | _    | ns    | N = prescale value (1, 4 or 16) |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

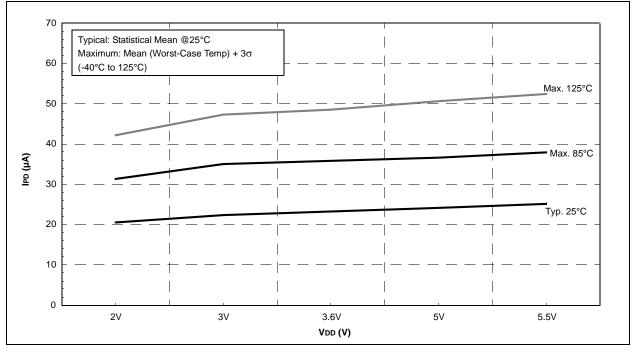

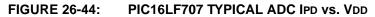

#### TABLE 25-7: PIC16F707 A/D CONVERTER (ADC) CHARACTERISTICS

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                                                   |      |      |      |       |                                                                     |

|----------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------|------|------|------|-------|---------------------------------------------------------------------|

| Param<br>No.                                                                                                         | Sym. | Characteristic                                    | Min. | Тур† | Max. | Units | Conditions                                                          |

| AD01                                                                                                                 | NR   | Resolution                                        | _    | _    | 8    | bit   |                                                                     |

| AD02                                                                                                                 | EIL  | Integral Error                                    | _    | _    | ±1.7 | LSb   | VREF = 3.0V                                                         |

| AD03                                                                                                                 | Edl  | Differential Error                                | —    | _    | ±1   | LSb   | No missing codes<br>VREF = 3.0V                                     |

| AD04                                                                                                                 | EOFF | Offset Error                                      | _    | _    | ±2.2 | LSb   | VREF = 3.0V                                                         |

| AD05                                                                                                                 | Egn  | Gain Error                                        | —    | _    | ±1.5 | LSb   | VREF = 3.0V                                                         |

| AD06                                                                                                                 | Vref | Reference Voltage <sup>(3)</sup>                  | 1.8  | _    | Vdd  | V     |                                                                     |

| AD07                                                                                                                 | VAIN | Full-Scale Range                                  | Vss  | _    | VREF | V     |                                                                     |

| AD08                                                                                                                 | Zain | Recommended Impedance of<br>Analog Voltage Source | _    | _    | 50   | kΩ    | Can go higher if external 0.01µF capacitor is present on input pin. |

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Total Absolute Error includes integral, differential, offset and gain errors.

2: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

**3:** When ADC is off, it will not consume any current other than leakage current. The power-down current specification includes any such leakage from the ADC module.

40-Lead UQFN (5x5x0.5 mm) PIN 1-PIN 1-PIN 1-PIC 16F707 -I/MV @3 10033K1

|                                                                                                                       | Ourstand and sittle information                                         |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|

| : XXX                                                                                                                 |                                                                         |  |  |  |  |

| Y                                                                                                                     | Year code (last digit of calendar year)                                 |  |  |  |  |

| YY                                                                                                                    | Year code (last 2 digits of calendar year)                              |  |  |  |  |

| WW                                                                                                                    | Week code (week of January 1 is week '01')                              |  |  |  |  |

| NNN                                                                                                                   | Alphanumeric traceability code                                          |  |  |  |  |

| (e3)                                                                                                                  | Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)                |  |  |  |  |

| *                                                                                                                     | This package is Pb-free. The Pb-free JEDEC <sup>®</sup> designator (e3) |  |  |  |  |

|                                                                                                                       | can be found on the outer packaging for this package.                   |  |  |  |  |

|                                                                                                                       |                                                                         |  |  |  |  |

| In the event the full Microchip part number cannot be marked on one line, it will                                     |                                                                         |  |  |  |  |

| be carried over to the next line, thus limiting the number of available characters for customer-specific information. |                                                                         |  |  |  |  |

|                                                                                                                       | In the eve                                                              |  |  |  |  |

\* Standard PICmicro<sup>®</sup> device marking consists of Microchip part number, year code, week code and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.                 | IXI <sup>(1)</sup> X     /XX     XX       Tape and Reel     Temperature     Package     Pat       Option     Range | <u>XX</u><br>ærn | Examples:<br>a) PIC16F707-E/P 301 = Extended Temp., PDIP<br>package, QTP pattern #301<br>b) PIC16F707-I/ML = Industrial Temp., QFN pack-               |

|--------------------------|--------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device:                  | PIC16F707, PIC16(L)F707 <sup>(1)</sup>                                                                             |                  | age                                                                                                                                                    |

| Tape and Reel<br>Option: | Blank = Standard packaging (tube or tray)<br>T = Tape and Reel <sup>(1)</sup>                                      |                  |                                                                                                                                                        |

| Temperature<br>Range:    | I = $-40^{\circ}$ C to $+85^{\circ}$ C (Industrial)<br>E = $-40^{\circ}$ C to $+125^{\circ}$ C (Extended)          |                  |                                                                                                                                                        |

| Package:                 | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                               |                  | Note 1: Tape and Reel identifier only appears in the<br>catalog part number description. This identi-<br>fier is used for ordering purposes and is not |

| Pattern:                 | QTP, SQTP, Code or Special Requirements (blank otherwise)                                                          |                  | printed on the device package. Check with your Microchip Sales Office for package availability with the Tape and Reel option.                          |

|                          |                                                                                                                    |                  |                                                                                                                                                        |