Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I²C, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 36                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 363 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 14x8b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

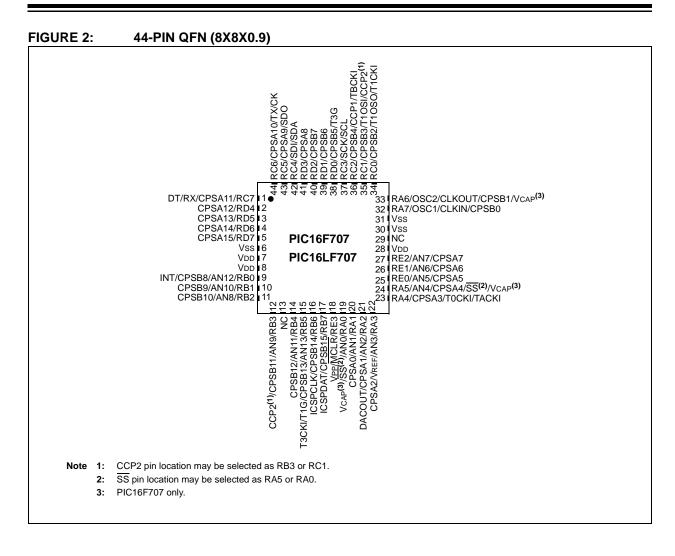

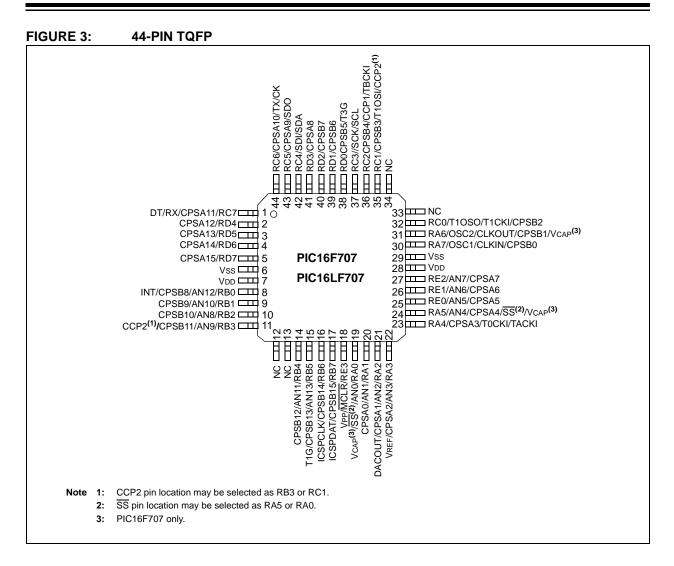

| Package / Case             | 44-TQFP                                                                  |

| Supplier Device Package    | 44-TQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f707-i-pt |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0   | Device Overview                                                              | 11   |

|-------|------------------------------------------------------------------------------|------|

| 2.0   | Memory Organization                                                          | . 17 |

| 3.0   | Resets                                                                       | . 28 |

| 4.0   | Interrupts                                                                   |      |

| 5.0   | Low Dropout (LDO) Voltage Regulator                                          | . 47 |

| 6.0   | I/O Ports                                                                    | -    |

| 7.0   | Oscillator Module                                                            |      |

| 8.0   | Device Configuration                                                         |      |

| 9.0   | Analog-to-Digital Converter (ADC) Module                                     |      |

| 10.0  | Fixed Voltage Reference                                                      |      |

| 11.0  | Digital-to-Analog Converter (DAC) Module                                     |      |

| 12.0  | Timer0 Module                                                                |      |

| 13.0  | Timer1/3 Modules with Gate Control                                           |      |

| 14.0  | TimerA/B Modules                                                             |      |

| 15.0  | Timer2 Module                                                                |      |

| 16.0  | Capacitive Sensing Module                                                    |      |

| 17.0  | Capture/Compare/PWM (CCP) Module                                             |      |

| 18.0  | Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) |      |

| 19.0  | SSP Module Overview                                                          |      |

|       | Program Memory Read                                                          |      |

| 21.0  | Power-Down Mode (Sleep)                                                      |      |

| 22.0  | In-Circuit Serial Programming™ (ICSP™)                                       |      |

| 23.0  | Instruction Set Summary                                                      |      |

| 24.0  | Development Support.                                                         |      |

| 25.0  | Electrical Specifications                                                    |      |

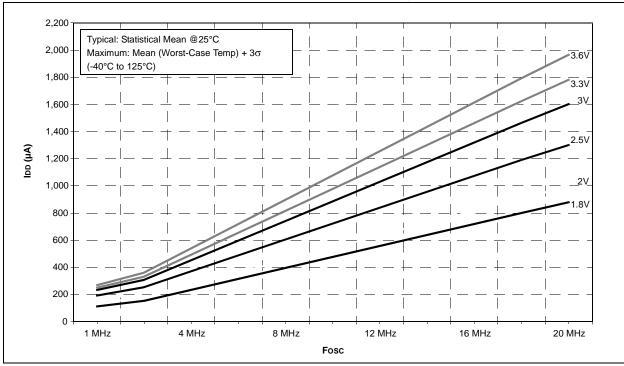

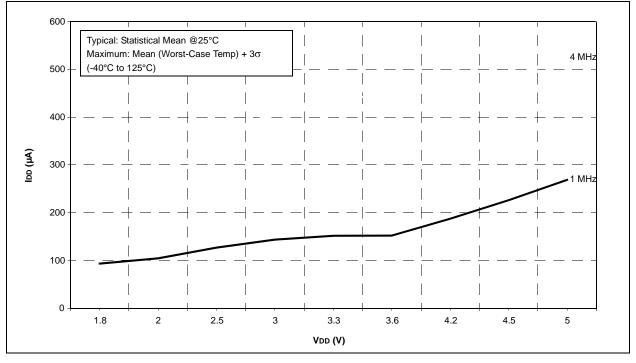

| 26.0  | DC and AC Characteristics Graphs and Charts                                  |      |

| 27.0  | Packaging Information                                                        |      |

|       | ndix A: Data Sheet Revision History                                          |      |

|       | ndix B: Migrating From Other PIC <sup>®</sup> Devices                        |      |

|       | /icrochip Website                                                            |      |

|       | omer Change Notification Service                                             |      |

|       | omer Support                                                                 |      |

| Produ | uct Identification System                                                    | 266  |

## TABLE 1-1: PIC16(L)F707 PINOUT DESCRIPTION (CONTINUED)

| Name             | Function | Input<br>Type    | Output<br>Type | Description                         |

|------------------|----------|------------------|----------------|-------------------------------------|

| RC4/SDI/SDA      | RC4      | ST               | CMOS           | General purpose I/O.                |

|                  | SDI      | ST               |                | SPI data input.                     |

|                  | SDA      | l <sup>2</sup> C | OD             | I <sup>2</sup> C data input/output. |

| RC5/SDO/CPSA9    | RC5      | ST               | CMOS           | General purpose I/O.                |

|                  | SDO      | _                | CMOS           | SPI data output.                    |

|                  | CPSA9    | AN               | _              | Capacitive sensing A input 9.       |

| RC6/TX/CK/CPSA10 | RC6      | ST               | CMOS           | General purpose I/O.                |

|                  | ТХ       | _                | CMOS           | USART asynchronous transmit.        |

|                  | СК       | ST               | CMOS           | USART synchronous clock.            |

|                  | CPSA10   | AN               | —              | Capacitive sensing A input 10.      |

| RC7/RX/DT/CPSA11 | RC7      | ST               | CMOS           | General purpose I/O.                |

|                  | RX       | ST               | _              | USART asynchronous input.           |

|                  | DT       | ST               | CMOS           | USART synchronous data.             |

|                  | CPSA11   | AN               | _              | Capacitive sensing A input 11.      |

| RD0/CPSB5/T3G    | RD0      | ST               | CMOS           | General purpose I/O.                |

|                  | CPSB5    | AN               | —              | Capacitive sensing B input 5.       |

|                  | T3G      | ST               | _              | Timer3 Gate input.                  |

| RD1/CPSB6        | RD1      | ST               | CMOS           | General purpose I/O.                |

|                  | CPSB6    | AN               | _              | Capacitive sensing B input 6.       |

| RD2/CPSB7        | RD2      | ST               | CMOS           | General purpose I/O.                |

|                  | CPSB7    | AN               | _              | Capacitive sensing B input 7.       |

| RD3/CPSA8        | RD3      | ST               | CMOS           | General purpose I/O.                |

|                  | CPSA8    | AN               | _              | Capacitive sensing A input 8.       |

| RD4/CPSA12       | RD4      | ST               | CMOS           | General purpose I/O.                |

|                  | CPSA12   | AN               |                | Capacitive sensing A input 12.      |

| RD5/CPSA13       | RD5      | ST               | CMOS           | General purpose I/O.                |

|                  | CPSA13   | AN               | _              | Capacitive sensing A input 13.      |

| RD6/CPSA14       | RD6      | ST               | CMOS           | General purpose I/O.                |

|                  | CPSA14   | AN               |                | Capacitive sensing A input 14.      |

| RD7/CPSA15       | RD7      | ST               |                | General purpose I/O.                |

|                  |          |                  | CMOS           |                                     |

|                  | CPSA15   | AN               | —              | Capacitive sensing A input 15.      |

| RE0/AN5/CPSA5    | REO      | ST               | CMOS           | General purpose I/O.                |

|                  | AN5      | AN               | —              | A/D Channel 5 input.                |

|                  | CPSA5    | AN               | -              | Capacitive sensing A input 5.       |

| RE1/AN6/CPSA6    | RE1      | ST               | CMOS           | General purpose I/O.                |

|                  | AN6      | AN               | _              | A/D Channel 6 input.                |

|                  | CPSA6    | AN               | -              | Capacitive sensing A input 6.       |

| RE2/AN7/CPSA7    | RE2      | ST               | CMOS           | General purpose I/O.                |

|                  | AN7      | AN               | _              | A/D Channel 7 input.                |

|                  | CPSA7    |                  | _              | Capacitive sensing A input 7.       |

| RE3/MCLR/Vpp     | RE3      | TTL              |                | General purpose input.              |

|                  | MCLR     | ST               | —              | Master Clear with internal pull-up. |

| N/               | VPP      | HV               | —              | Programming voltage.                |

| VDD              | Vdd      | Power            | —              | Positive supply.                    |

## 3.6 Time-out Sequence

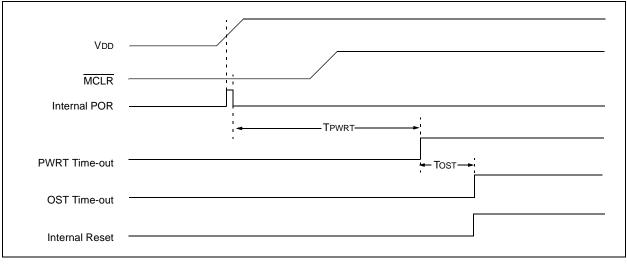

On power-up, the time-out sequence is as follows: first, PWRT time-out is invoked after POR has expired, then OST is activated after the PWRT time-out has expired. The total time-out will vary based on oscillator configuration and  $\overrightarrow{PWRTE}$  bit status. For example, in EC mode with  $\overrightarrow{PWRTE}$  bit = 1 (PWRT disabled), there will be no time-out at all. Figure 3-5, Figure 3-6 and Figure 3-7 depict time-out sequences.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then, bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (see Figure 3-6). This is useful for testing purposes or to synchronize more than one PIC16(L)F707 device operating in parallel.

Table 3-2 shows the Reset conditions for some special registers.

## 3.7 Power Control (PCON) Register

The Power Control (PCON) register has two Status bits to indicate what type of Reset that last occurred.

Bit 0 is  $\overrightarrow{BOR}$  (Brown-out Reset).  $\overrightarrow{BOR}$  is unknown on Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if  $\overrightarrow{BOR} = 0$ , indicating that a brown-out has occurred. The  $\overrightarrow{BOR}$ Status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (BOREN<1:0> = 00 in the Configuration Word register).

Bit 1 is POR (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent Reset, if POR is '0', it will indicate that a Power-on Reset has occurred (i.e., VDD may have gone too low).

For more information, see Section 3.5 "Brown-Out Reset (BOR)".

| Oscillator Configuration | Powe                   | er-up            | Brown-o                | Wake-up from |             |

|--------------------------|------------------------|------------------|------------------------|--------------|-------------|

|                          | <b>PWRTE</b> = 0       | <b>PWRTE</b> = 1 | <b>PWRTE</b> = 0       | PWRTE = 1    | Sleep       |

| XT, HS, LP               | TPWRT + 1024 •<br>Tosc | 1024 • Tosc      | TPWRT + 1024 •<br>Tosc | 1024 • Tosc  | 1024 • Tosc |

| RC, EC, INTOSC           | TPWRT                  |                  | TPWRT                  | _            | —           |

#### TABLE 3-4: TIME-OUT IN VARIOUS SITUATIONS

### FIGURE 3-5: TIME-OUT SEQUENCE ON POWER-UP (DELAYED MCLR): CASE 1

| TABLE 3-5: | INITIALIZATION CONDITION FOR REGISTERS (CONTINUED) |                                                   |                          |                                                  |  |  |  |  |  |  |

|------------|----------------------------------------------------|---------------------------------------------------|--------------------------|--------------------------------------------------|--|--|--|--|--|--|

| Register   | Address                                            | Power-on Reset/<br>Brown-out Reset <sup>(1)</sup> | MCLR Reset/<br>WDT Reset | Wake-up from Sleep through<br>Interrupt/Time-out |  |  |  |  |  |  |

| ADCON0     | 1Fh                                                | 00 0000                                           | 00 0000                  | uu uuuu                                          |  |  |  |  |  |  |

| OPTION_REG | 81h/181h                                           | 1111 1111                                         | 1111 1111                | uuuu uuuu                                        |  |  |  |  |  |  |

| TRISA      | 85h                                                | 1111 1111                                         | 1111 1111                | uuuu uuuu                                        |  |  |  |  |  |  |

| TRISB      | 86h                                                | 1111 1111                                         | 1111 1111                | uuuu uuuu                                        |  |  |  |  |  |  |

| TRISC      | 87h                                                | 1111 1111                                         | 1111 1111                | uuuu uuuu                                        |  |  |  |  |  |  |

| TRISD      | 88h                                                | 1111 1111                                         | 1111 1111                | uuuu uuuu                                        |  |  |  |  |  |  |

| TRISE      | 89h                                                | 1111                                              | 1111                     | uuuu                                             |  |  |  |  |  |  |

| PIE1       | 8Ch                                                | 0000 0000                                         | 0000 0000                | uuuu uuuu                                        |  |  |  |  |  |  |

| PIE2       | 8Dh                                                | 00000                                             | 00000                    | uuuuu                                            |  |  |  |  |  |  |

| PCON       | 8Eh                                                | dd                                                | uu <sup>(1,5)</sup>      |                                                  |  |  |  |  |  |  |

| T1GCON     | 8Fh                                                | 0000 0x00                                         | uuuu uxuu                | uuuu uxuu                                        |  |  |  |  |  |  |

| OSCCON     | 90h                                                | 10 qq                                             | 10 qq                    | uu qq                                            |  |  |  |  |  |  |

| OSCTUNE    | 91h                                                | 00 0000                                           | uu uuuu                  | uu uuuu                                          |  |  |  |  |  |  |

| PR2        | 92h                                                | 1111 1111                                         | 1111 1111                | uuuu uuuu                                        |  |  |  |  |  |  |

| SSPADD     | 93h                                                | 0000 0000                                         | 0000 0000                | uuuu uuuu                                        |  |  |  |  |  |  |

| SSPMSK     | 93h                                                | 1111 1111                                         | 1111 1111                | uuuu uuuu                                        |  |  |  |  |  |  |

| SSPSTAT    | 94h                                                | 0000 0000                                         | 0000 0000                | uuuu uuuu                                        |  |  |  |  |  |  |

| WPUB       | 95h                                                | 1111 1111                                         | 1111 1111                | uuuu uuuu                                        |  |  |  |  |  |  |

| IOCB       | 96h                                                | 0000 0000                                         | 0000 0000                | uuuu uuuu                                        |  |  |  |  |  |  |

| T3CON      | 97h                                                | 0000 -0-0                                         | 0000 -0-0                | uuuu -u-u                                        |  |  |  |  |  |  |

| TXSTA      | 98h                                                | 0000 -010                                         | 0000 -010                | uuuu -uuu                                        |  |  |  |  |  |  |

| SPBRG      | 99h                                                | 0000 0000                                         | 0000 0000                | uuuu uuuu                                        |  |  |  |  |  |  |

| TMR3L      | 9Ah                                                | XXXX XXXX                                         | uuuu uuuu                | uuuu uuuu                                        |  |  |  |  |  |  |

| TMR3H      | 9Bh                                                | XXXX XXXX                                         | սսսս սսսս                | uuuu uuuu                                        |  |  |  |  |  |  |

| APFCON     | 9Ch                                                | 00                                                | 00                       | uu                                               |  |  |  |  |  |  |

| FVRCON     | 9Dh                                                | q000 0000                                         | q000 0000                | q000 0000                                        |  |  |  |  |  |  |

| ADCON1     | 9Fh                                                | -00000                                            | -00000                   | -uuuuu                                           |  |  |  |  |  |  |

| TACON      | 105h                                               | 0-00 0000                                         | 0-00 0000                | u-uu uuuu                                        |  |  |  |  |  |  |

| CPSBCON0   | 106h                                               | 00 0000                                           | 00 0000                  | uu uuuu                                          |  |  |  |  |  |  |

| CPSBCON1   | 107h                                               | 0000                                              | 0000                     | uuuu                                             |  |  |  |  |  |  |

| CPSACON0   | 108h                                               | 00 0000                                           | 00 0000                  | uu uuuu                                          |  |  |  |  |  |  |

| CPSACON1   | 109h                                               | 0000                                              | 0000                     | uuuu                                             |  |  |  |  |  |  |

| PMDATL     | 10Ch                                               | xxxx xxxx                                         | XXXX XXXX                | นนนน นนนน                                        |  |  |  |  |  |  |

| PMADRL     | 10Dh                                               | xxxx xxxx                                         | XXXX XXXX                | นนนน นนนน                                        |  |  |  |  |  |  |

| PMDATH     | 10Eh                                               | xx xxxx                                           | xx xxxx                  | uu uuuu                                          |  |  |  |  |  |  |

| PMADRH     | 10Fh                                               | x xxxx                                            | x xxxx                   | u uuuu                                           |  |  |  |  |  |  |

| TMRA       | 110h                                               | 0000 0000                                         | 0000 0000                | uuuu uuuu                                        |  |  |  |  |  |  |

## TABLE 3-5: INITIALIZATION CONDITION FOR REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON and/or PIR1 and PIR2 will be affected (to cause wake-up).

**3:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 3-2 for Reset value for specific condition.

5: If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

## 7.6 External Clock Modes

#### 7.6.1 OSCILLATOR START-UP TIMER (OST)

If the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations on the OSC1 pin before the device is released from Reset. This occurs following a Power-on Reset (POR) and when the Power-up Timer (PWRT) has expired (if configured), or a wake-up from Sleep. During this time, the program counter does not increment and program execution is suspended. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module.

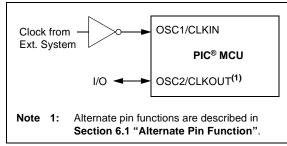

#### 7.6.2 EC MODE

The External Clock (EC) mode allows an externally generated logic level as the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input and the OSC2 is available for general purpose I/O. Figure 7-2 shows the pin connections for EC mode.

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### FIGURE 7-2: EXTERNAL CLOCK (EC) MODE OPERATION

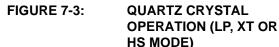

### 7.6.3 LP, XT, HS MODES

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 7-3). The mode selects a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

LP Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is best suited to drive resonators with a low drive level specification, for example, tuning fork type crystals.

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 7-3 and Figure 7-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

**Note 1:** A series resistor (Rs) may be required for quartz crystals with low drive level.

2: The value of RF varies with the Oscillator mode selected.

Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- 2: Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

| R/W-1        | R/W-1              | R/W-1                   | R/W-1           | R/W-1            | R/W-1           | R/W-1           | R/W-1 |  |  |  |

|--------------|--------------------|-------------------------|-----------------|------------------|-----------------|-----------------|-------|--|--|--|

| RBPU         | INTEDG             | TMR0CS                  | TMR0SE          | PSA              | PS2             | PS1             | PS0   |  |  |  |

| bit 7        |                    |                         |                 |                  |                 |                 | bit ( |  |  |  |

|              |                    |                         |                 |                  |                 |                 |       |  |  |  |

| Legend:      |                    |                         |                 |                  |                 |                 |       |  |  |  |

| R = Readab   | le bit             | W = Writable            | bit             | U = Unimpler     | nented bit, rea | d as '0'        |       |  |  |  |

| -n = Value a | t POR              | '1' = Bit is set        |                 | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |  |  |  |

|              |                    |                         |                 |                  |                 |                 |       |  |  |  |

| bit 7        | RBPU: POR          | TB Pull-up Enal         | ble bit         |                  |                 |                 |       |  |  |  |

|              |                    | oull-ups are disa       |                 |                  |                 |                 |       |  |  |  |

|              | 0 <b>= PORTB</b> p | oull-ups are ena        | bled by indivi  | dual PORT late   | h values        |                 |       |  |  |  |

| bit 6        | INTEDG: Inte       | errupt Edge Sel         | ect bit         |                  |                 |                 |       |  |  |  |

|              | 1 = Interrupt      | on rising edge          | of INT pin      |                  |                 |                 |       |  |  |  |

|              | 0 = Interrupt      | on falling edge         | of INT pin      |                  |                 |                 |       |  |  |  |

| bit 5        | TMROCS: TA         | IR0 Clock Sou           | ce Select bit   |                  |                 |                 |       |  |  |  |

|              | 1 = Transitior     | Transition on T0CKI pin |                 |                  |                 |                 |       |  |  |  |

|              |                    | nstruction cycle        | clock (Fosc/    | 4)               |                 |                 |       |  |  |  |

| bit 4        | TMR0SE: TM         | IR0 Source Ed           | ge Select bit   |                  |                 |                 |       |  |  |  |

|              | 1 = Incremen       | t on high-to-lov        | v transition on | T0CKI pin        |                 |                 |       |  |  |  |

|              |                    | t on low-to-high        |                 |                  |                 |                 |       |  |  |  |

| bit 3        | PSA: Presca        | ler Assignment          | bit             |                  |                 |                 |       |  |  |  |

|              |                    | is assigned to          |                 |                  |                 |                 |       |  |  |  |

|              |                    | r is assigned to        |                 | odule            |                 |                 |       |  |  |  |

| bit 2-0      |                    | escaler Rate Se         |                 |                  |                 |                 |       |  |  |  |

|              | BIT                | VALUE TMR0 R            | ATE WDT RA      | TE               |                 |                 |       |  |  |  |

|              |                    | 000 1:2                 | 1:1             |                  |                 |                 |       |  |  |  |

|              | (                  | 1:4                     | 1:2             |                  |                 |                 |       |  |  |  |

|              | (                  | 1:8                     | 1:4             |                  |                 |                 |       |  |  |  |

|              |                    | 1:16                    |                 |                  |                 |                 |       |  |  |  |

|              | -                  | 1:32                    | _               |                  |                 |                 |       |  |  |  |

|              |                    | 1:64                    |                 |                  |                 |                 |       |  |  |  |

|              | 1                  | 1:12 1:12               |                 |                  |                 |                 |       |  |  |  |

## REGISTER 12-1: OPTION\_REG: OPTION REGISTER

#### TABLE 12-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER0

| Name       | Bit 7                  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------|------------------------|--------|--------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON     | GIE                    | PEIE   | TMR0IE | INTE   | RBIE   | TMR0IF | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| OPTION_REG | RBPU                   | INTEDG | TMR0CS | TMR0SE | PSA    | PS2    | PS1    | PS0    | 1111 1111            | 1111 1111                       |

| TMR0       | Timer0 Module Register |        |        |        |        |        |        |        |                      | uuuu uuuu                       |

| TRISA      | TRISA7                 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111            | 1111 1111                       |

- = Unimplemented locations, read as '0'. Shaded cells are not used by the Timer0 module. Legend:

| U-0          | R/W-0                        | R/W-0            | R/W-0          | R/W-0             | R/W-0           | R/W-0           | R/W-0   |

|--------------|------------------------------|------------------|----------------|-------------------|-----------------|-----------------|---------|

| _            | TOUTPS3                      | TOUTPS2          | TOUTPS1        | TOUTPS0           | TMR2ON          | T2CKPS1         | T2CKPS0 |

| bit 7        |                              |                  |                |                   |                 |                 | bit C   |

|              |                              |                  |                |                   |                 |                 |         |

| Legend:      |                              |                  |                |                   |                 |                 |         |

| R = Readal   | ble bit                      | W = Writable     | bit            | U = Unimplen      | nented bit, rea | d as '0'        |         |

| -n = Value a | at POR                       | '1' = Bit is set |                | '0' = Bit is clea | ared            | x = Bit is unkr | nown    |

|              |                              |                  |                |                   |                 |                 |         |

| bit 7        | Unimplemen                   | ted: Read as '   | 0'             |                   |                 |                 |         |

| bit 6-3      | TOUTPS<3:0                   | )>: Timer2 Outp  | out Postscaler | Select bits       |                 |                 |         |

|              | 0000 = 1:1 P                 | ostscaler        |                |                   |                 |                 |         |

|              | 0001 = 1:2 P                 | ostscaler        |                |                   |                 |                 |         |

|              | 0010 = 1:3 P                 |                  |                |                   |                 |                 |         |

|              | 0011 = 1:4 P                 |                  |                |                   |                 |                 |         |

|              | 0100 = 1:5 P                 |                  |                |                   |                 |                 |         |

|              | 0101 = 1:6 P                 |                  |                |                   |                 |                 |         |

|              | 0110 = 1:7 P<br>0111 = 1:8 P |                  |                |                   |                 |                 |         |

|              | 1000 = 1:9 P                 |                  |                |                   |                 |                 |         |

|              | 1000 = 1.91<br>1001 = 1.10   |                  |                |                   |                 |                 |         |

|              | 1010 = 1:11                  |                  |                |                   |                 |                 |         |

|              | 1011 = 1:12                  |                  |                |                   |                 |                 |         |

|              | 1100 <b>= 1:13</b>           | Postscaler       |                |                   |                 |                 |         |

|              | 1101 <b>= 1:14</b>           | Postscaler       |                |                   |                 |                 |         |

|              | 1110 <b>= 1:15</b>           |                  |                |                   |                 |                 |         |

|              | 1111 <b>= 1:16</b>           | Postscaler       |                |                   |                 |                 |         |

| bit 2        | TMR2ON: Tir                  | mer2 On bit      |                |                   |                 |                 |         |

|              | 1 = Timer2 is                | s on             |                |                   |                 |                 |         |

|              | 0 = Timer2 is                | soff             |                |                   |                 |                 |         |

| bit 1-0      | T2CKPS<1:0                   | >: Timer2 Cloc   | k Prescale Se  | lect bits         |                 |                 |         |

|              | 00 = Prescale                | er is 1          |                |                   |                 |                 |         |

|              | 01 = Prescale                | er is 4          |                |                   |                 |                 |         |

|              | 1x = Prescale                | er is 16         |                |                   |                 |                 |         |

## REGISTER 15-1: T2CON: TIMER2 CONTROL REGISTER

| TABLE 15-1: | SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2 |

|-------------|---------------------------------------------|

|-------------|---------------------------------------------|

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4        | Bit 3        | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|---------|---------|---------|--------------|--------------|--------|---------|---------|----------------------|---------------------------------|

| INTCON  | GIE     | PEIE    | TMR0IE  | INTE         | RBIE         | TMR0IF | INTF    | RBIF    | 0000 000x            | 0000 000x                       |

| PIE1    | TMR1GIE | ADIE    | RCIE    | TXIE         | SSPIE        | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                       |

| PIR1    | TMR1GIF | ADIF    | RCIF    | TXIF         | SSPIF        | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                       |

| PR2     |         |         | Т       | imer2 Module | Period Regis | ter    |         |         | 1111 1111            | 1111 1111                       |

| TMR2    |         |         |         | 0000 0000    | 0000 0000    |        |         |         |                      |                                 |

| T2CON   | _       | TOUTPS3 | TOUTPS2 | TOUTPS1      | TOUTPS0      | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                       |

| Logondu |         |         |         |              |              |        |         |         |                      |                                 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for Timer2 module.

## 16.1 Analog MUX

Each capacitive sensing module can monitor up to 16 inputs, providing 32 capacitive sensing inputs in total. The capacitive sensing inputs are defined as CPSA<15:0> for capacitive sensing module A, and CPSB<15:0> for capacitive sensing module B. To determine if a frequency change has occurred the use must:

- Select the appropriate CPS pin by setting the CPSxCH<3:0> bits of the CPSxCON1 register.

- Set the corresponding ANSEL bit.

- Set the corresponding TRIS bit.

- Run the software algorithm.

Selection of the CPSx pin while the module is enabled will cause the capacitive sensing oscillator to be on the CPSx pin. Failure to set the corresponding ANSEL and TRIS bits can cause the capacitive sensing oscillator to stop, leading to false frequency readings.

## 16.2 Capacitive Sensing Oscillator

The capacitive sensing oscillator consists of a constant current source and a constant current sink, to produce a triangle waveform. The CPSxOUT bit of the CPSxCON0 register shows the status of the capacitive sensing oscillator, whether it is sinking or sourcing current. The oscillator is designed to drive a capacitive load (single PCB pad) and at the same time, be a clock source to either TimerA/B or Timer1/3. The oscillator has three different current settings as defined by CPSxRNG<1:0> of the CPSxCON0 register. The different current settings for the oscillator serve two purposes:

- Maximize the number of counts in a timer for a fixed time base.

- Maximize the count differential in the timer during a change in frequency.

## 16.3 Voltage References

The capacitive sensing oscillator uses voltage references to provide two voltage thresholds for oscillation. The upper voltage threshold is referred to as Ref+ and the lower voltage threshold is referred to as Ref-.

The user can elect to use Fixed Voltage References, which are internal to the capacitive sensing oscillator, or variable voltage references, which are supplied by the Fixed Voltage Reference (FVR) module and the Digital-to-Analog Converter (DAC) module.

When the Fixed Voltage References are used, the Vss voltage determines the lower threshold level (Ref-) and the VDD voltage determines the upper threshold level (Ref+).

When the variable voltage references are used, the DAC voltage determines the lower threshold level (Ref-) and the FVR voltage determines the upper threshold level (Ref+). An advantage of using these reference sources is that oscillation frequency remains constant with changes in VDD.

Different oscillation frequencies can be obtained through the use of these variable voltage references. The more the upper voltage reference level is lowered and the more the lower voltage reference level is raised, the higher the capacitive sensing oscillator frequency becomes.

Selection between the voltage references is controlled by the CPSxRM bit of the CPSxCON0 register. Setting this bit selects the variable voltage references and clearing this bit selects the Fixed Voltage References.

Please see Section 10.0 "Fixed Voltage Reference" and Section 11.0 "Digital-to-Analog Converter (DAC) Module" for more information on configuring the variable voltage levels.

- 6. Enable PWM output pin:

- Wait until Timer2 overflows, TMR2IF bit of the PIR1 register is set. See the Note below.

- Enable the PWM pin (CCPx) output driver(s) by clearing the associated TRIS bit(s).

- **Note:** In order to send a complete duty cycle and period on the first PWM output, the above steps must be included in the setup sequence. If it is not critical to start with a complete PWM signal on the first output, then step 6 may be ignored.

### TABLE 17-7: SUMMARY OF REGISTERS ASSOCIATED WITH PWM

| Name    | Bit 7                  | Bit 6   | Bit 5     | Bit 4       | Bit 3           | Bit 2     | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|------------------------|---------|-----------|-------------|-----------------|-----------|---------|---------|----------------------|---------------------------------|

| ANSELB  | ANSB7                  | ANSB6   | ANSB5     | ANSB4       | ANSB3           | ANSB2     | ANSB1   | ANSB0   | 1111 1111            | 1111 1111                       |

| ANSELC  | ANSC7                  | ANSC6   | ANSC5     |             | _               | ANSC2     | ANSC1   | ANSC0   | 111111               | 111111                          |

| APFCON  | _                      | _       | _         | _           | _               | _         | SSSEL   | CCP2SEL | 00                   | 00                              |

| CCP1CON | _                      | _       | DC1B1     | DC1B0       | CCP1M3          | CCP1M2    | CCP1M1  | CCP1M0  | 00 0000              | 00 0000                         |

| CCP2CON | _                      | _       | DC2B1     | DC2B0       | CCP2M3          | CCP2M2    | CCP2M1  | CCP2M0  | 00 0000              | 00 0000                         |

| CCPRxL  |                        |         | Capture/0 | Compare/PWN | /I Register X L | ow Byte   |         |         | xxxx xxxx            | uuuu uuuu                       |

| CCPRxH  |                        |         | Capture/C | Compare/PWN | /I Register X H | ligh Byte |         |         | xxxx xxxx            | uuuu uuuu                       |

| PR2     |                        |         |           | Timer2 Peri | od Register     |           |         |         | 1111 1111            | 1111 1111                       |

| T2CON   | _                      | TOUTPS3 | TOUTPS2   | TOUTPS1     | TOUTPS0         | TMR2ON    | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                       |

| TMR2    | Timer2 Module Register |         |           |             |                 |           |         |         | 0000 0000            | 0000 0000                       |

| TRISB   | TRISB7                 | TRISB6  | TRISB5    | TRISB4      | TRISB3          | TRISB2    | TRISB1  | TRISB0  | 1111 1111            | 1111 1111                       |

| TRISC   | TRISC7                 | TRISC6  | TRISC5    | TRISC4      | TRISC3          | TRISC2    | TRISC1  | TRISC0  | 1111 1111            | 1111 1111                       |

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the PWM.

#### 18.1.2.1 Enabling the Receiver

The AUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other AUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCSTA register enables the receiver circuitry of the AUSART. Clearing the SYNC bit of the TXSTA register configures the AUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the AUSART and automatically configures the RX/DT I/O pin as an input.

| Note 1: | When the SPEN bit is set, the TX/CK I/O     |

|---------|---------------------------------------------|

|         | pin is automatically configured as an out-  |

|         | put, regardless of the state of the corre-  |

|         | sponding TRIS bit and whether or not the    |

|         | AUSART transmitter is enabled. The          |

|         | PORT latch is disconnected from the out-    |

|         | put driver so it is not possible to use the |

|         | TX/CK pin as a general purpose output.      |

| 0.      | The corresponding ANCEL bit must be         |

2: The corresponding ANSEL bit must be cleared for the RX/DT port pin to ensure proper AUSART functionality.

#### 18.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. Refer to Section 18.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the AUSART receive FIFO and the RCIF interrupt flag bit of the PIR1 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCREG register.

| ſ | Note: | If the receive FIFO is overrun, no additional |     |        |             |       |        |  |  |

|---|-------|-----------------------------------------------|-----|--------|-------------|-------|--------|--|--|

|   |       | characters will be received until the overrun |     |        |             |       |        |  |  |

|   |       |                                               |     | -      | cleared.    |       |        |  |  |

|   |       | Section                                       | 18  | .1.2.5 | "Receive    | Ov    | errun  |  |  |

|   |       | Error"                                        | for | more   | information | on ov | /errun |  |  |

|   |       | errors.                                       |     |        |             |       |        |  |  |

#### 18.1.2.3 Receive Interrupts

The RCIF interrupt flag bit of the PIR1 register is set whenever the AUSART receiver is enabled and there is an unread character in the receive FIFO. The RCIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCIF interrupts are enabled by setting all of the following bits:

- RCIE, Receive Interrupt Enable bit of the PIE1

register

- PEIE, Peripheral Interrupt Enable bit of the INTCON register

- GIE, Global Interrupt Enable bit of the INTCON register

The RCIF interrupt flag bit of the PIR1 register will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

#### 18.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCSTA register which resets the AUSART. Clearing the CREN bit of the RCSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

Note: If all receive characters in the receive FIFO have framing errors, repeated reads of the RCREG will not clear the FERR bit.

| R/W-0         | R/W-0                             | R/W-0                            | R/W-0                 | R/W-0            | R-0                                  | R-0               | R-x           |

|---------------|-----------------------------------|----------------------------------|-----------------------|------------------|--------------------------------------|-------------------|---------------|

| SPEN          | RX9                               | SREN                             | CREN                  | ADDEN            | FERR                                 | OERR              | RX9D          |

| bit 7         |                                   |                                  |                       |                  |                                      |                   | bit (         |

|               |                                   |                                  |                       |                  |                                      |                   |               |

| Legend:       |                                   |                                  |                       |                  |                                      |                   |               |

| R = Readable  |                                   | W = Writable                     |                       | -                | mented bit, read                     |                   |               |

| -n = Value at | POR                               | '1' = Bit is set                 | t                     | '0' = Bit is cle | ared                                 | x = Bit is unkn   | own           |

| h:+ 7         | SPEN: Serial                      | Dent Enchle h                    | :(1)                  |                  |                                      |                   |               |

| bit 7         |                                   |                                  |                       | T and TX/CK n    | ins as serial por                    | t nins)           |               |

|               |                                   | rt disabled (be                  |                       |                  |                                      | t pins)           |               |

| bit 6         | <b>RX9:</b> 9-bit Re              | ceive Enable b                   | oit                   |                  |                                      |                   |               |

|               | 1 = Selects 9                     | -bit reception                   |                       |                  |                                      |                   |               |

|               | 0 = Selects 8                     | •                                |                       |                  |                                      |                   |               |

| bit 5         | -                                 | Receive Enal                     | ole bit               |                  |                                      |                   |               |

|               | Asynchronous                      | <u>s mode</u> :                  |                       |                  |                                      |                   |               |

|               | Don't care                        | mode – Maste                     | vr.                   |                  |                                      |                   |               |

|               | 1 = Enables                       |                                  | <u>11</u> .           |                  |                                      |                   |               |

|               |                                   | single receive                   |                       |                  |                                      |                   |               |

|               |                                   | ared after rece                  |                       | ete.             |                                      |                   |               |

|               |                                   | mode – Slave                     | <u>.</u>              |                  |                                      |                   |               |

| L:4 4         | Don't care                        | D                                | En abla bit           |                  |                                      |                   |               |

| bit 4         |                                   | nuous Receive                    | Enable bit            |                  |                                      |                   |               |

|               | Asynchronous                      |                                  |                       |                  |                                      |                   |               |

|               | 0 = Disables                      |                                  |                       |                  |                                      |                   |               |

|               | Synchronous                       | mode:                            |                       |                  |                                      |                   |               |

|               |                                   | continuous rec<br>continuous rec |                       | ble bit CREN is  | cleared (CREN                        | l overrides SRE   | EN)           |

| bit 3         | ADDEN: Add                        | ress Detect Er                   | able bit              |                  |                                      |                   |               |

|               |                                   | <u>s mode 9-bit (F</u>           |                       |                  |                                      |                   |               |

|               | 0 = Disables                      |                                  | tion, all bytes       |                  | d the receive bu<br>nd ninth bit can |                   |               |

|               | Don't care                        |                                  |                       |                  |                                      |                   |               |

|               | <u>Synchronous</u>                |                                  |                       |                  |                                      |                   |               |

|               | Must be set to                    |                                  |                       |                  |                                      |                   |               |

| bit 2         | FERR: Framin                      | -                                | un alota al las curas |                  |                                      |                   |               |

|               | 1 = Framing 0 = No framing 0      |                                  | ipdated by rea        | ading RCREG I    | egister and reco                     | eive next valid i | oyte)         |

| bit 1         | OERR: Overr                       | un Error bit                     |                       |                  |                                      |                   |               |

|               | 1 = Overrun = 0<br>0 = No overrun | •                                | leared by clea        | aring bit CREN)  | )                                    |                   |               |

| bit 0         | RX9D: Ninth I                     | oit of Received                  | l Data                |                  |                                      |                   |               |

|               | This can be a                     | ddress/data bi                   | t or a parity bi      | t and must be o  | calculated by us                     | er firmware.      |               |

|               | he AUSART m<br>RISx = 1.          | odule automa                     | tically change        | es the pin fro   | m tri-state to c                     | drive as neede    | ed. Configure |

## REGISTER 18-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER

© 2010-2015 Microchip Technology Inc.

|              | DC C   | HARACTERISTICS                                | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature -40°C $\le$ TA $\le$ +85°C for industrial} \\ \ -40°C $\le$ TA $\le$ +125°C for extended \end{array}$ |      |      |       |                                                                         |  |  |

|--------------|--------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-------------------------------------------------------------------------|--|--|

| Param<br>No. | Sym.   | Characteristic                                | Min.                                                                                                                                                                                                                  | Тур† | Max. | Units | Conditions                                                              |  |  |

| D130         | Ep     | Cell Endurance                                | 100                                                                                                                                                                                                                   | 1k   | —    | E/W   | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |  |

| D131         |        | VDD for Read                                  | Vmin                                                                                                                                                                                                                  | —    | —    | V     |                                                                         |  |  |

|              |        | Voltage on MCLR/VPP during<br>Erase/Program   | 8.0                                                                                                                                                                                                                   | —    | 9.0  | V     | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |  |

|              |        | VDD for Bulk Erase                            | 2.7                                                                                                                                                                                                                   | 3    | —    | V     | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |  |

| D132         | Vpew   | VDD for Write or Row Erase                    | 2.7                                                                                                                                                                                                                   | -    | —    | V     | VMIN = Minimum operating voltage<br>VMAX = Maximum operating<br>voltage |  |  |

|              | IPPPGM | Current on MCLR/VPP during<br>Erase/Write     | _                                                                                                                                                                                                                     | _    | 5.0  | mA    | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |  |

|              | IDDPGM | Current on VDD during Erase/<br>Write         | _                                                                                                                                                                                                                     |      | 5.0  | mA    | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |  |

| D133         | TPEW   | Erase/Write cycle time                        | -                                                                                                                                                                                                                     |      | 2.8  | ms    | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |  |  |

| D134         | TRETD  | Characteristic Retention                      | 40                                                                                                                                                                                                                    | —    | -    | Year  | Provided no other specifications are violated                           |  |  |

|              |        | VCAP Capacitor Charging                       |                                                                                                                                                                                                                       | ·    | •    |       | •                                                                       |  |  |

| D135         |        | Charging current                              | _                                                                                                                                                                                                                     | 200  |      | μΑ    |                                                                         |  |  |

| D135A        |        | Source/sink capability when charging complete | _                                                                                                                                                                                                                     | 0.0  | —    | mA    |                                                                         |  |  |

## 25.4 DC Characteristics: PIC16(L)F707-I/E (Continued)

**Legend:** TBD = To Be Determined

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

**3:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: Including OSC2 in CLKOUT mode.

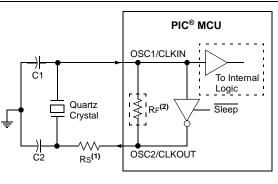

#### TABLE 25-8: PIC16F707 A/D CONVERSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                                                                 |      |      |      |       |                                        |

|----------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------|------|------|------|-------|----------------------------------------|

| Param<br>No.                                                                                                         | Sym. | Characteristic                                                  | Min. | Тур† | Max. | Units | Conditions                             |

| AD130*                                                                                                               | Tad  | A/D Clock Period                                                | 1.0  | _    | 9.0  | μS    | Tosc-based                             |

|                                                                                                                      |      | A/D Internal RC Oscillator<br>Period                            | 1.0  | 2.0  | 6.0  | μS    | ADCS<1:0> = 11 (ADRC mode)             |

| AD131                                                                                                                | TCNV | Conversion Time (not including Acquisition Time) <sup>(1)</sup> |      | 10.5 | -    | TAD   | Set GO/DONE bit to conversion complete |

| AD132*                                                                                                               | TACQ | Acquisition Time                                                |      | 1.0  | —    | μS    |                                        |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The ADRES register may be read on the following TCY cycle.

#### FIGURE 25-12: PIC16F707 A/D CONVERSION TIMING (NORMAL MODE)

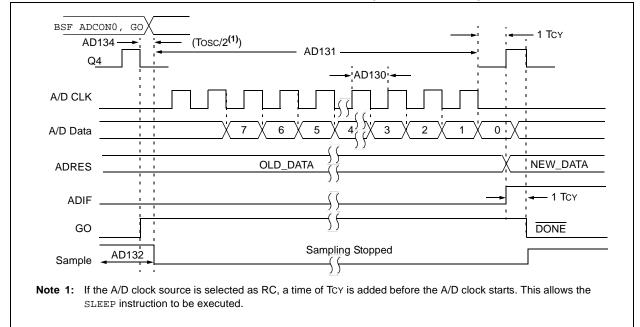

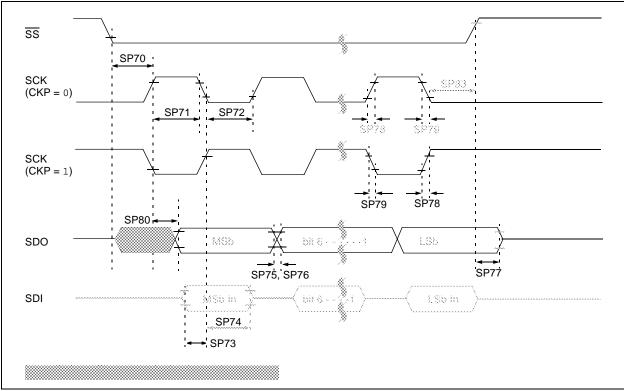

## FIGURE 25-17: SPI MASTER MODE TIMING (CKE = 1, SMP = 1)

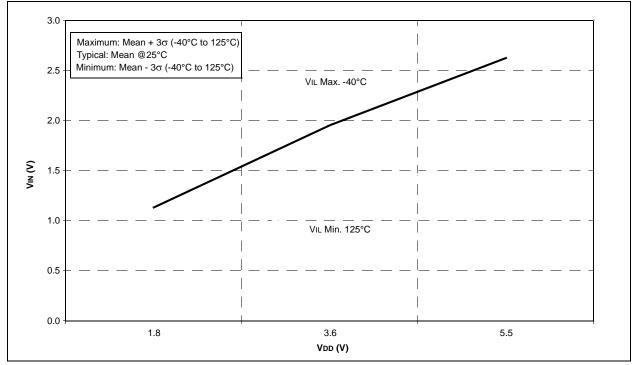

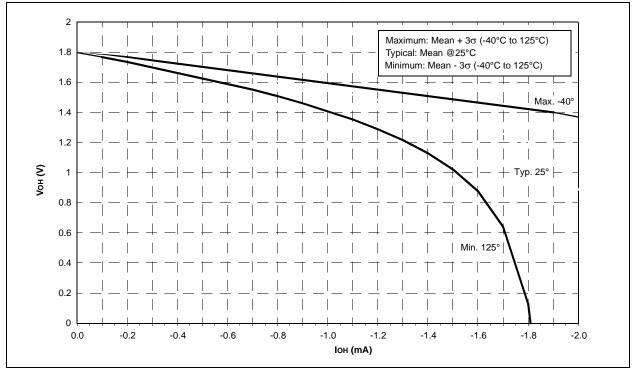

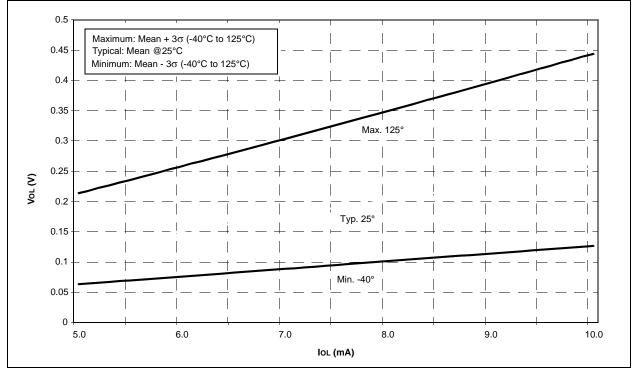

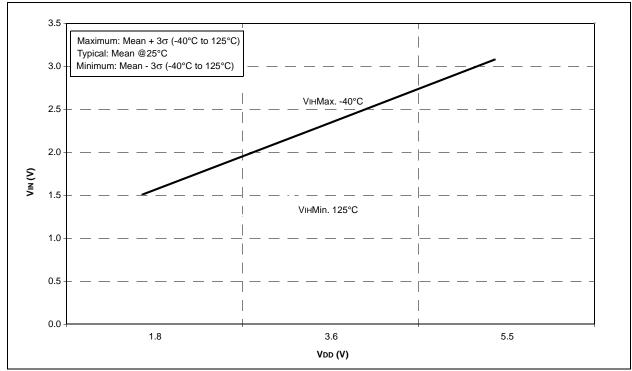

FIGURE 26-50: SCHMITT TRIGGER INPUT THRESHOLD VIN vs. VDD OVER TEMPERATURE

FIGURE 26-51: SCHMITT TRIGGER INPUT THRESHOLD VIN vs. VDD OVER TEMPERATURE