Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 363 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 14x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

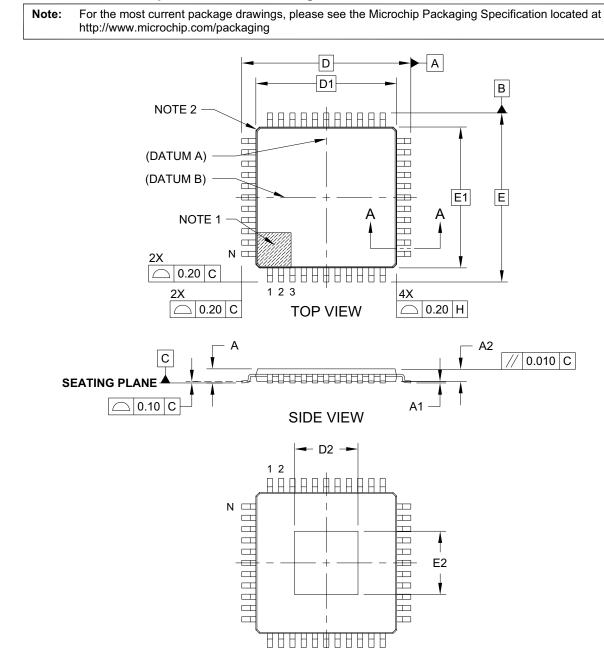

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf707-e-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 1-1: PIC16(L)F707 PINOUT DESCRIPTION

| Name Eurotion '           |        | Output<br>Type | Description |                                                                                                   |

|---------------------------|--------|----------------|-------------|---------------------------------------------------------------------------------------------------|

| RA0/AN0/SS/Vcap           | RA0    | TTL            | CMOS        | General purpose I/O.                                                                              |

|                           | AN0    | AN             | —           | A/D Channel 0 input.                                                                              |

|                           | SS     | ST             | —           | Slave Select input.                                                                               |

|                           | VCAP   | Power          | Power       | Filter capacitor for Voltage Regulator (PIC16F only).                                             |

| RA1/AN1/CPSA0             | RA1    | TTL            | CMOS        | General purpose I/O.                                                                              |

|                           | AN1    | AN             | —           | A/D Channel 1 input.                                                                              |

|                           | CPSA0  | AN             |             | Capacitive sensing A input 0.                                                                     |

| RA2/AN2/CPSA1/DACOUT      | RA2    | TTL            | CMOS        | General purpose I/O.                                                                              |

|                           | AN2    | AN             | —           | A/D Channel 2 input.                                                                              |

|                           | CPSA1  | AN             |             | Capacitive sensing A input 1.                                                                     |

|                           | DACOUT | _              | AN          | Voltage Reference Output.                                                                         |

| RA3/AN3/VREF/CPSA2        | RA3    | TTL            | CMOS        | General purpose I/O.                                                                              |

|                           | AN3    | AN             | _           | A/D Channel 3 input.                                                                              |

|                           | VREF   | AN             | —           | A/D Voltage Reference input.                                                                      |

|                           | CPSA2  | AN             | _           | Capacitive sensing A input 2.                                                                     |

| RA4/CPSA3/T0CKI/TACKI     | RA4    | TTL            | CMOS        | General purpose I/O.                                                                              |

|                           | CPSA3  | AN             | —           | Capacitive sensing A input 3.                                                                     |

|                           | TOCKI  | ST             | —           | Timer0 clock input.                                                                               |

|                           | TACKI  | ST             | _           | TimerA clock input.                                                                               |

| RA5/AN4/CPSA4/SS/Vcap     | RA5    | TTL            | CMOS        | General purpose I/O.                                                                              |

|                           | AN4    | AN             | —           | A/D Channel 4 input.                                                                              |

|                           | CPSA4  | AN             | _           | Capacitive sensing A input 4.                                                                     |

|                           | SS     | ST             | _           | Slave Select input.                                                                               |

|                           | VCAP   | Power          | Power       | Filter capacitor for Voltage Regulator (PIC16F only).                                             |

| RA6/OSC2/CLKOUT/VCAP/ RA6 |        | TTL            | CMOS        | General purpose I/O.                                                                              |

| CPSB1                     | OSC2   | _              | XTAL        | Crystal/Resonator (LP, XT, HS modes).                                                             |

|                           | CLKOUT | _              | CMOS        | Fosc/4 output.                                                                                    |

|                           | VCAP   | Power          | Power       | Filter capacitor for Voltage Regulator (PIC16F only).                                             |

|                           | CPSB1  | AN             |             | Capacitive sensing B input 1.                                                                     |

| RA7/OSC1/CLKIN/CPSB0      | RA7    | TTL            | CMOS        | General purpose I/O.                                                                              |

|                           | OSC1   | XTAL           |             | Crystal/Resonator (LP, XT, HS modes).                                                             |

|                           | CLKIN  | CMOS           |             | External clock input (EC mode).                                                                   |

|                           | CLKIN  | ST             |             | RC oscillator connection (RC mode).                                                               |

|                           | CPSB0  | AN             | _           | Capacitive sensing B input 0.                                                                     |

| RB0/AN12/CPSB8/INT        | RB0    | TTL            | CMOS        | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up. |

|                           | AN12   | AN             | —           | A/D Channel 12 input.                                                                             |

|                           | CPSB8  | AN             | —           | Capacitive sensing B input 8.                                                                     |

|                           | INT    | ST             | —           | External interrupt.                                                                               |

| RB1/AN10/CPSB9            | RB1    | TTL            | CMOS        | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up. |

|                           | AN10   | AN             | —           | A/D Channel 10 input.                                                                             |

|                           | CPSB9  | AN             | 1           | Capacitive sensing B input 9.                                                                     |

## TABLE 1-1: PIC16(L)F707 PINOUT DESCRIPTION (CONTINUED)

| Name             | Function | Input<br>Type    | Output<br>Type | Description                         |

|------------------|----------|------------------|----------------|-------------------------------------|

| RC4/SDI/SDA      | RC4      | ST               | CMOS           | General purpose I/O.                |

|                  | SDI      | ST               |                | SPI data input.                     |

|                  | SDA      | l <sup>2</sup> C | OD             | I <sup>2</sup> C data input/output. |

| RC5/SDO/CPSA9    | RC5      | ST               | CMOS           | General purpose I/O.                |

|                  | SDO      | _                | CMOS           | SPI data output.                    |

|                  | CPSA9    | AN               | _              | Capacitive sensing A input 9.       |

| RC6/TX/CK/CPSA10 | RC6      | ST               | CMOS           | General purpose I/O.                |

|                  | ТХ       | _                | CMOS           | USART asynchronous transmit.        |

|                  | СК       | ST               | CMOS           | USART synchronous clock.            |

|                  | CPSA10   | AN               | —              | Capacitive sensing A input 10.      |

| RC7/RX/DT/CPSA11 | RC7      | ST               | CMOS           | General purpose I/O.                |

|                  | RX       | ST               | _              | USART asynchronous input.           |

|                  | DT       | ST               | CMOS           | USART synchronous data.             |

|                  | CPSA11   | AN               | _              | Capacitive sensing A input 11.      |

| RD0/CPSB5/T3G    | RD0      | ST               | CMOS           | General purpose I/O.                |

|                  | CPSB5    | AN               | —              | Capacitive sensing B input 5.       |

|                  | T3G      | ST               | _              | Timer3 Gate input.                  |

| RD1/CPSB6        | RD1      | ST               | CMOS           | General purpose I/O.                |

|                  | CPSB6    | AN               | _              | Capacitive sensing B input 6.       |

| RD2/CPSB7        | RD2      | ST               | CMOS           | General purpose I/O.                |

|                  | CPSB7    | AN               | _              | Capacitive sensing B input 7.       |

| RD3/CPSA8        | RD3      | ST               | CMOS           | General purpose I/O.                |

|                  | CPSA8    | AN               | _              | Capacitive sensing A input 8.       |

| RD4/CPSA12       | RD4      | ST               | CMOS           | General purpose I/O.                |

|                  | CPSA12   | AN               |                | Capacitive sensing A input 12.      |

| RD5/CPSA13       | RD5      | ST               | CMOS           | General purpose I/O.                |

|                  | CPSA13   | AN               | _              | Capacitive sensing A input 13.      |

| RD6/CPSA14       | RD6      | ST               | CMOS           | General purpose I/O.                |

|                  | CPSA14   | AN               |                | Capacitive sensing A input 14.      |

| RD7/CPSA15       | RD7      | ST               |                | General purpose I/O.                |

|                  |          |                  | CMOS           |                                     |

|                  | CPSA15   | AN               | —              | Capacitive sensing A input 15.      |

| RE0/AN5/CPSA5    | REO      | ST               | CMOS           | General purpose I/O.                |

|                  | AN5      | AN               | —              | A/D Channel 5 input.                |

|                  | CPSA5    | AN               | -              | Capacitive sensing A input 5.       |

| RE1/AN6/CPSA6    | RE1      | ST               | CMOS           | General purpose I/O.                |

|                  | AN6      | AN               | _              | A/D Channel 6 input.                |

|                  | CPSA6    | AN               | -              | Capacitive sensing A input 6.       |

| RE2/AN7/CPSA7    | RE2      | ST               | CMOS           | General purpose I/O.                |

|                  | AN7      | AN               | _              | A/D Channel 7 input.                |

|                  | CPSA7    |                  | _              | Capacitive sensing A input 7.       |

| RE3/MCLR/Vpp     | RE3      | TTL              |                | General purpose input.              |

|                  | MCLR     | ST               | —              | Master Clear with internal pull-up. |

| N/               | VPP      | HV               | —              | Programming voltage.                |

| VDD              | Vdd      | Power            | —              | Positive supply.                    |

## 2.2.2.1 STATUS Register

The STATUS register, shown in Register 2-1, contains:

- the arithmetic status of the ALU

- · the Reset status

R/W-0

• the bank select bits for data memory (SRAM)

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to Section 23.0 "Instruction Set Summary").

| Note 1: | The C and DC bits operate as Borrow         |

|---------|---------------------------------------------|

|         | and Digit Borrow out bits, respectively, in |

|         | subtraction.                                |

R/W-x

R/W-x

R/W-x

#### REGISTER 2-1: STATUS: STATUS REGISTER

R/W-0

R-1

R-1

R/W-0

| IRP          | RP1                | RP0                             | TO                | PD                 | Z                          | DC <sup>(1)</sup>     | C <sup>(1)</sup> |

|--------------|--------------------|---------------------------------|-------------------|--------------------|----------------------------|-----------------------|------------------|

| bit 7        | ·                  | •                               | ·                 |                    |                            |                       | bit (            |

| Legend:      |                    |                                 |                   |                    |                            |                       |                  |

| R = Readab   | ole bit            | W = Writable                    | bit               | U = Unimpler       | mented bit, rea            | d as '0'              |                  |

| -n = Value a | t POR              | '1' = Bit is se                 | t                 | '0' = Bit is cle   | ared                       | x = Bit is unkn       | own              |

|              |                    |                                 |                   |                    |                            |                       |                  |

| bit 7        |                    |                                 | oit (used for inc | direct addressi    | ng)                        |                       |                  |

|              |                    | (100h-1FFh)                     |                   |                    |                            |                       |                  |

| bit 6-5      | 0 = Bank 0, 1      | . ,                             | laat bita (uaad   | for direct odd     | (accient)                  |                       |                  |

| 010-0        | 00 = Bank 0 (      | •                               | elect bits (used  | for direct add     | lessing)                   |                       |                  |

|              | 00 = Bank 0        |                                 |                   |                    |                            |                       |                  |

|              | 10 = Bank 2        |                                 |                   |                    |                            |                       |                  |

|              | 11 = Bank 3        | · ,                             |                   |                    |                            |                       |                  |

| bit 4        | TO: Time-out bit   |                                 |                   |                    |                            |                       |                  |

|              |                    |                                 |                   | SLEEP instruc      | tion                       |                       |                  |

|              |                    | me-out occurre                  | ed                |                    |                            |                       |                  |

| bit 3        | PD: Power-de       |                                 |                   |                    |                            |                       |                  |

|              |                    | er-up or by the tion of the SLE |                   |                    |                            |                       |                  |

| bit 2        | <b>Z:</b> Zero bit |                                 |                   |                    |                            |                       |                  |

|              |                    | t of an arithme                 | tic or logic ope  | eration is zero    |                            |                       |                  |

|              |                    |                                 |                   | eration is not ze  | ero                        |                       |                  |

| bit 1        | DC: Digit Car      | ry/Digit Borrov                 | bit (ADDWF, A     | .DDLW,SUBLW,       | SUBWF instruc              | tions) <sup>(1)</sup> |                  |

|              | 1 = A carry-o      | ut from the 4th                 | low-order bit     | of the result oc   | curred                     |                       |                  |

|              | •                  | out from the 41                 |                   |                    |                            |                       |                  |

| bit 0        | -                  | -                               |                   |                    | instructions) <sup>(</sup> | 1)                    |                  |

|              |                    |                                 |                   | oit of the result  |                            |                       |                  |

|              | 0 = No carry-      | out from the M                  | lost Significant  | bit of the resu    | It occurred                |                       |                  |

|              | or Borrow, the po  | •                               |                   |                    | •                          |                       |                  |

| S            | econd operand. F   | or rotate (RRF,                 | RLF) instruction  | ons, this bit is l | oaded with eith            | er the high-orde      | r or low-orde    |

bit of the source register.

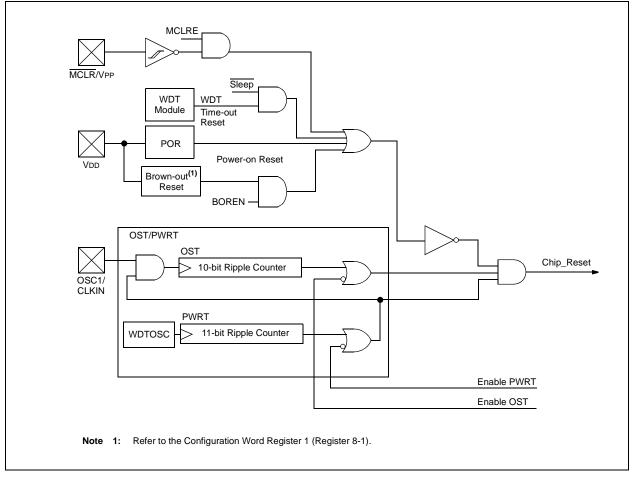

## 3.0 RESETS

The PIC16(L)F707 differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) WDT Reset during normal operation

- c) WDT Reset during Sleep

- d) MCLR Reset during normal operation

- e) MCLR Reset during Sleep

- f) Brown-out Reset (BOR)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- Power-on Reset (POR)

- MCLR Reset

- MCLR Reset during Sleep

- WDT Reset

- Brown-out Reset (BOR)

Most registers are not affected by a WDT wake-up since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different Reset situations, as indicated in Table 3-3. These bits are used in software to determine the nature of the Reset.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 3-1.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See **Section 25.0** "**Electrical Specifications**" for pulse width specifications.

#### FIGURE 3-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

## 12.1 Timer0 Operation

The Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

#### 12.1.1 8-BIT TIMER MODE

The Timer0 module will increment every instruction cycle, if used without a prescaler. 8-bit Timer mode is selected by clearing the TMR0CS bit of the OPTION register.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

| Note: | The value written to the TMR0 register   |

|-------|------------------------------------------|

|       | can be adjusted, in order to account for |

|       | the two instruction cycle delay when     |

|       | TMR0 is written.                         |

#### 12.1.2 8-BIT COUNTER MODE

In 8-bit Counter mode, the Timer0 module will increment on every rising or falling edge of the T0CKI pin. 8-bit Counter mode using the T0CKI pin is selected by setting the TMR0CS bit of the OPTION register to '1'.

The rising or falling transition of the incrementing edge for either input source is determined by the TMR0SE bit in the OPTION register.

#### 12.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A single software programmable prescaler is available for use with either Timer0 or the Watchdog Timer (WDT), but not both simultaneously. The prescaler assignment is controlled by the PSA bit of the OPTION register. To assign the prescaler to Timer0, the PSA bit must be cleared to a '0'.

There are eight prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be assigned to the WDT module.

The prescaler is not readable or writable. When the prescaler is enabled or assigned to the Timer0 module, all instructions writing to the TMR0 register will clear the prescaler.

Note: When the prescaler is assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

#### 12.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The TMR0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The TMR0IF bit can only be cleared in software. The Timer0 interrupt enable is the TMR0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |  |  |  |

|-------|-----------------------------------------|--|--|--|

|       | processor from Sleep since the timer is |  |  |  |

|       | frozen during Sleep.                    |  |  |  |

#### 12.1.5 USING TIMER0 WITH AN EXTERNAL CLOCK

When Timer0 is in Counter mode, the synchronization of the T0CKI input and the Timer0 register is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, the high and low periods of the external clock source must meet the timing requirements as shown in **Section 25.0 "Electrical Specifications"**.

#### 12.1.6 TIMER ENABLE

Operation of Timer0 is always enabled and the module will operate according to the settings of the OPTION register.

#### 12.1.7 OPERATION DURING SLEEP

Timer0 cannot operate while the processor is in Sleep mode. The contents of the TMR0 register will remain unchanged while the processor is in Sleep mode.

| FIGURE 13-6:           | TIMER1/TIMER3 GATE                      | SINGLE-PULSE AND TOGGLE COMBINED MODE                |

|------------------------|-----------------------------------------|------------------------------------------------------|

| TMRxGE                 |                                         |                                                      |

| TxGPOL                 |                                         |                                                      |

| TxGSPM                 |                                         |                                                      |

| TxGTM                  |                                         |                                                      |

| TxGG <u>O/</u><br>DONE | ← Set by software<br>Counting enabled   | Cleared by hardware on<br>falling edge of TxGVAL     |

| TxG_IN                 | rising edge of TxC                      |                                                      |

| ТхСКІ                  |                                         |                                                      |

| TxGVAL                 |                                         |                                                      |

| TIMER 1/3              | Ν                                       | N + 1 N + 2 N + 3 N + 4                              |

| TMRxGIF                | <ul> <li>Cleared by software</li> </ul> | Set by hardware on Cleared by falling edge of TxGVAL |

### 16.4 Power Modes

The capacitive sensing oscillator can operate in one of seven different power modes. The power modes are separated into two ranges; the low range and the high range.

When the oscillator's low range is selected, the fixed internal voltage references of the capacitive sensing oscillator are being used. When the oscillator's high range is selected, the variable voltage references supplied by the FVR and DAC modules are being used. Selection between the voltage references is controlled by the CPSxRM bit of the CPSxCON0 register. See **Section 16.3 "Voltage References"** for more information.

Within each range there are three distinct power modes; Low, Medium and High. Current consumption is dependent upon the range and mode selected. Selecting power modes within each range is accomplished by configuring the CPSxRNG <1:0> bits in the CPSxCON0 register. See Table 16-2 for proper power mode selection.

The remaining mode is a Noise Detection mode that resides within the high range. The Noise Detection mode is unique in that it disables the sinking and sourcing of current on the analog pin but leaves the rest of the oscillator circuitry active. This reduces the oscillation frequency on the analog pin to zero and also greatly reduces the current consumed by the oscillator module.

When noise is introduced onto the pin, the oscillator is driven at the frequency determined by the noise. This produces a detectable signal at the comparator output, indicating the presence of activity on the pin.

Figure 16-2 shows a more detailed drawing of the current sources and comparators associated with the oscillator.

| CPSxRM | Range | CPSxRNG<1:0> | Mode            | Nominal Current <sup>(1)</sup> |

|--------|-------|--------------|-----------------|--------------------------------|

|        |       | 00           | Off             | 0.0 µA                         |

| 0      | Low   | 01           | Low             | 0.1 µA                         |

|        |       | 10           | Medium          | 1.2 µA                         |

|        |       | 11           | High            | 18 µA                          |

|        |       | 00           | Noise Detection | 0.0 µA                         |

| 1      | High  | 01           | Low             | 9 µA                           |

|        |       | 10           | Medium          | 30 µA                          |

|        |       | 11           | High            | 100 µA                         |

TABLE 16-2: POWER MODE SELECTION

Note: See Section 25.0 "Electrical Specifications" for more information.

## 16.5 Timer Resources

To measure the change in frequency of the capacitive sensing oscillator, a fixed time base is required. For the period of the fixed time base, the capacitive sensing oscillator is used to clock either TimerA/B or Timer1/3 (for CPSA/B, respectively). The frequency of the capacitive sensing oscillator is equal to the number of counts in the timer divided by the period of the fixed time base.

## 16.6 Fixed Time Base

To measure the frequency of the capacitive sensing oscillator, a fixed time base is required. Any timer resource or software loop can be used to establish the fixed time base. It is up to the end user to determine the method in which the fixed time base is generated.

**Note:** The fixed time base can not be generated by the timer resource that the capacitive sensing oscillator is clocking.

| R/W-0/0          | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                            | U-0                                                                                                                                                                                    | U-0                                                                                                      | R/W-0/0                                                                                                       | R/W-0/0                                                                                                                | R-0/0                                               | R/W-0/0     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------|

| CPSxON           | CPSxRM                                                                                                                                                                                                                                                                                                                                                                                                             | _                                                                                                                                                                                      | _                                                                                                        | CPSxRNG1                                                                                                      | CPSxRNG0                                                                                                               | CPSxOUT                                             | TxXCS       |

| bit 7            |                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                        |                                                                                                          |                                                                                                               |                                                                                                                        |                                                     | bit (       |

| Legend:          |                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                        |                                                                                                          |                                                                                                               |                                                                                                                        |                                                     |             |

| R = Readable     | e bit                                                                                                                                                                                                                                                                                                                                                                                                              | W = Writable                                                                                                                                                                           | bit                                                                                                      | U = Unimpler                                                                                                  | mented bit, read                                                                                                       | as '0'                                              |             |

| u = bit is unch  | nanged                                                                                                                                                                                                                                                                                                                                                                                                             | x = Bit is unkr                                                                                                                                                                        | iown                                                                                                     | -n/n = Value a                                                                                                | at POR and BOI                                                                                                         | R/Value at all of                                   | ther Resets |

| '1' = Bit is set |                                                                                                                                                                                                                                                                                                                                                                                                                    | '0' = Bit is clea                                                                                                                                                                      | ared                                                                                                     |                                                                                                               |                                                                                                                        |                                                     |             |

| bit 7<br>bit 6   | 1 = Capacitiv<br>0 = Capacitiv                                                                                                                                                                                                                                                                                                                                                                                     | apacitive Sensir<br>ve sensing mod<br>ve sensing mod<br>apacitive Sensir                                                                                                               | ule is enable<br>ule is disable                                                                          | ed<br>ed                                                                                                      |                                                                                                                        |                                                     |             |

|                  | <b>CPSxRM:</b> Capacitive Sensing Reference Mode bit<br>1 = Capacitive sensing module is in high range. DAC and FVR provide oscillator voltage reference<br>0 = Capacitive sensing module is in low range. Internal oscillator voltage references are used.                                                                                                                                                        |                                                                                                                                                                                        |                                                                                                          |                                                                                                               |                                                                                                                        |                                                     |             |

| bit 5-4          | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                        |                                                                                                          |                                                                                                               |                                                                                                                        |                                                     |             |

| bit 3-2          | If CPSxRM =<br>11 = Oscillate<br>10 = Oscillate<br>01 = Oscillate<br>00 = Oscillate<br>If CPSxRM =<br>11 = Oscillate<br>10 = Oscillate<br>01 = Oscillate<br>00 = Oscillate                                                                                                                                                                                                                                         | <u>0</u> (low range):<br>or is in high ran<br>or is in medium<br>or is off.<br><u>1</u> (high range):<br>or is in high ran<br>or is in medium<br>or is in low rangor<br>is on; Noise D | ge: Charge/c<br>range. Char<br>e. Charge/d<br>ge: Charge/c<br>range. Char<br>e. Charge/d<br>etection mod | ge/discharge cu<br>scharge curren<br>lischarge currer<br>ge/discharge cu<br>scharge curren<br>de; No charge/d | s<br>Irrent is nominally 1<br>irrent is nominally 0.<br>It is nominally 1<br>Irrent is nominally 9<br>Iischarge curren | lly 1.2 μΑ.<br>1 μΑ.<br>00 μΑ.<br>Ily 30 μΑ.<br>μΑ. |             |

| bit 1            | <b>CPSxOUT:</b> Capacitive Sensing Oscillator Status bit<br>1 = Oscillator is sourcing current (Current flowing out of the pin)<br>0 = Oscillator is sinking current (Current flowing into the pin)                                                                                                                                                                                                                |                                                                                                                                                                                        |                                                                                                          |                                                                                                               |                                                                                                                        |                                                     |             |

| bit O            | TxXCS: TimerA/B External Clock Source Select bit         If TMRxCS = 1:         The TxXCS bit controls which clock external to the core/TimerA/B module supplies TimerA/B:         1 = TimerA/B clock source is the capacitive sensing oscillator         0 = TimerA/B clock source is the TxCKI pin         If TMRxCS = 0:         TimerA/B clock source is controlled by the core/TimerA/B module and is Fosc/4. |                                                                                                                                                                                        |                                                                                                          |                                                                                                               |                                                                                                                        |                                                     |             |

## REGISTER 16-1: CPSxCON0: CAPACITIVE SENSING CONTROL REGISTER 0

## 17.0 CAPTURE/COMPARE/PWM (CCP) MODULE

The Capture/Compare/PWM module is a peripheral which allows the user to time and control different events. In Capture mode, the peripheral allows the timing of the duration of an event. The Compare mode allows the user to trigger an external event when a predetermined amount of time has expired. The PWM mode can generate a pulse-width modulated signal of varying frequency and duty cycle.

The timer resources used by the module are shown in Table 17-2.

Additional information on CCP modules is available in Application Note AN594, *Using the CCP Modules* (DS00594).

#### TABLE 17-1: CCP MODE – TIMER RESOURCES REQUIRED

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

**Note:** Timer3 has no connection to either CCP.

| CCP1 Mode | CCP2 Mode | Interaction                                                                                                  |

|-----------|-----------|--------------------------------------------------------------------------------------------------------------|

| Capture   | Capture   | Same TMR1 time base                                                                                          |

| Capture   | Compare   | Same TMR1 time base <sup>(1, 2)</sup>                                                                        |

| Compare   | Compare   | Same TMR1 time base <sup>(1, 2)</sup>                                                                        |

| PWM       | PWM       | The PWMs will have the same frequency and update rate (TMR2 interrupt).<br>The rising edges will be aligned. |

| PWM       | Capture   | None                                                                                                         |

| PWM       | Compare   | None                                                                                                         |

## TABLE 17-2: INTERACTION OF TWO CCP MODULES

**Note 1:** If CCP2 is configured as a Special Event Trigger, CCP1 will clear Timer1, affecting the value captured on the CCP2 pin.

**2:** If CCP1 is in Capture mode and CCP2 is configured as a Special Event Trigger, CCP2 will clear Timer1, affecting the value captured on the CCP1 pin.

| Note: | CCPRx   | and      | CCPx      | throughout  | this |

|-------|---------|----------|-----------|-------------|------|

|       | documer | nt refer | to CCP    | R1 or CCPR2 | and  |

|       | CCP1 or | CCP2     | 2, respec | tively.     |      |

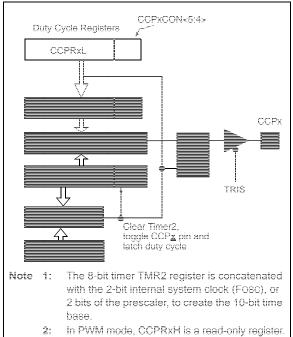

## 17.3 PWM Mode

The PWM mode generates a pulse-width modulated signal on the CCPx pin. The duty cycle, period and resolution are determined by the following registers:

- PR2

- T2CON

- CCPRxL

- CCPxCON

In Pulse-Width Modulation (PWM) mode, the CCP module produces up to a 10-bit resolution PWM output on the CCPx pin.

Figure 17-3 shows a simplified block diagram of PWM operation.

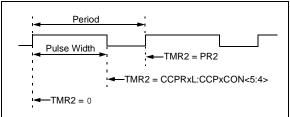

Figure 17-4 shows a typical waveform of the PWM signal.

For a step-by-step procedure on how to set up the CCP module for PWM operation, refer to **Section 17.3.8** "Setup for PWM Operation".

FIGURE 17-3: SIMPLIFIED PWM BLOCK DIAGRAM

The PWM output (Figure 17-4) has a time base (period) and a time that the output stays high (duty cycle).

FIGURE 17-4: CCP PWM OUTPUT

## 17.3.1 CCPX PIN CONFIGURATION

In PWM mode, the CCPx pin is multiplexed with the PORT data latch. The user must configure the CCPx pin as an output by clearing the associated TRIS bit.

Either RC1 or RB3 can be selected as the CCP2 pin. Refer to **Section 6.1 "Alternate Pin Function"** for more information.

Note: Clearing the CCPxCON register will relinquish CCPx control of the CCPx pin.

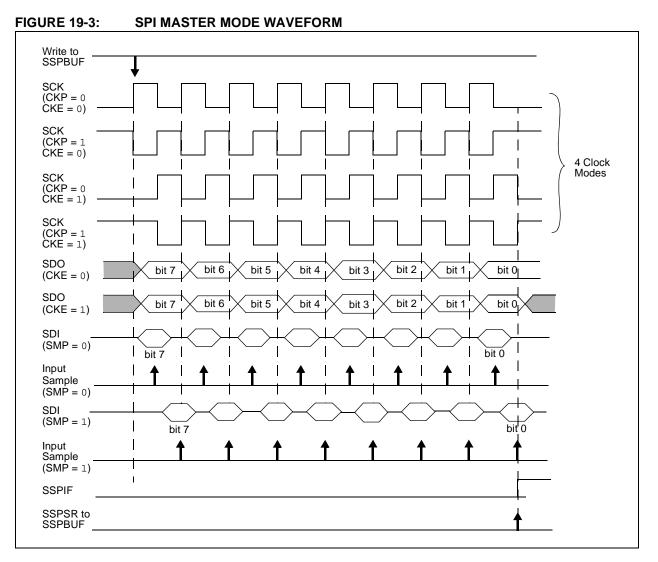

#### 19.1.1.3 Master Mode Setup

In Master mode, the data is transmitted/received as soon as the SSPBUF register is loaded with a byte value. If the master is only going to receive, SDO output could be disabled (programmed and used as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate.

When initializing SPI Master mode operation, several options need to be specified. This is accomplished by programming the appropriate control bits in the SSPCON and SSPSTAT registers. These control bits allow the following to be specified:

- · SCK as clock output

- Idle state of SCK (CKP bit)

- Data input sample phase (SMP bit)

- Output data on rising/falling edge of SCK (CKE bit)

- · Clock bit rate

In Master mode, the SPI clock rate (bit rate) is user selectable to be one of the following:

- Fosc/4 (or TCY)

- Fosc/16 (or 4 TCY)

- Fosc/64 (or 16 TCY)

- (Timer2 output)/2

This allows a maximum data rate of 5 Mbps (at Fosc = 20 MHz).

Figure 19-3 shows the waveforms for Master mode. The clock polarity is selected by appropriately programming the CKP bit of the SSPCON register. When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The sample time of the input data is shown based on the state of the SMP bit and can occur at the middle or end of the data output time. The time when the SSPBUF is loaded with the received data is shown.

#### 19.1.1.4 Sleep in Master Mode

In Master mode, all module clocks are halted and the transmission/reception will remain in their current state, paused, until the device wakes from Sleep. After the device wakes up from Sleep, the module will continue to transmit/receive data.

#### EXAMPLE 19-1: LOADING THE SSPBUF (SSPSR) REGISTER

|      | BANKSEL | SSPSTAT     | ;                                           |

|------|---------|-------------|---------------------------------------------|

| LOOP | BTFSS   | SSPSTAT, BF | ;Has data been received(transmit complete)? |

|      | GOTO    | LOOP        | ;No                                         |

|      | BANKSEL | SSPBUF      | ;                                           |

|      | MOVF    | SSPBUF, W   | ;WREG reg = contents of SSPBUF              |

|      | MOVWF   | RXDATA      | ;Save in user RAM, if data is meaningful    |

|      | MOVF    | TXDATA, W   | ;W reg = contents of TXDATA                 |

|      | MOVWF   | SSPBUF      | ;New data to xmit                           |

|      |         |             |                                             |

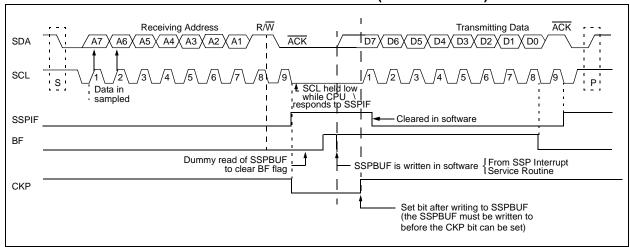

#### 19.2.6 TRANSMISSION

When the R/W bit of the received address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set and the slave will respond to the master by reading out data. After the address match, an ACK pulse is generated by the slave hardware and the SCL pin is held low (clock is automatically stretched) until the slave is ready to respond. See **Section 19.2.7 "Clock Stretching"**. The data the slave will transmit must be loaded into the SSPBUF register, which sets the BF bit. The SCL line is released by setting the CKP bit of the SSPCON register.

An SSP interrupt is generated for each transferred data byte. The SSPIF flag bit of the PIR1 register initiates an SSP interrupt, and must be cleared by software before the next byte is transmitted. The BF bit of the SSPSTAT register is cleared on the falling edge of the eighth received clock pulse. The SSPIF flag bit is set on the falling edge of the ninth clock pulse. Following the eighth falling clock edge, control of the SDA line is released back to the master so that the master can acknowledge or not acknowledge the response. If the master sends a not acknowledge, the slave's transmission is complete and the slave must monitor for the next Start condition. If the master acknowledges, control of the bus is returned to the slave to transmit another byte of data. Just as with the previous byte, the clock is stretched by the slave, data must be loaded into the SSPBUF and CKP must be set to release the clock line (SCL).

| MOVF             | Move f                                                                                                                                                                                                                                                                               |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] MOVF f,d                                                                                                                                                                                                                                                                     |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                      |

| Operation:       | (f) $\rightarrow$ (dest)                                                                                                                                                                                                                                                             |

| Status Affected: | Z                                                                                                                                                                                                                                                                                    |

| Description:     | The contents of register f is<br>moved to a destination dependent<br>upon the status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register f<br>itself. $d = 1$ is useful to test a file<br>register since status flag Z is<br>affected. |

| Words:           | 1                                                                                                                                                                                                                                                                                    |

| Cycles:          | 1                                                                                                                                                                                                                                                                                    |

| Example:         | MOVF FSR, 0                                                                                                                                                                                                                                                                          |

|                  | After Instruction<br>W = value in FSR<br>register<br>Z = 1                                                                                                                                                                                                                           |

| MOVWF            | Move W to f                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------|

| Syntax:          | [label] MOVWF f                                                                                   |

| Operands:        | $0 \le f \le 127$                                                                                 |

| Operation:       | $(W) \rightarrow (f)$                                                                             |

| Status Affected: | None                                                                                              |

| Description:     | Move data from W register to register 'f'.                                                        |

| Words:           | 1                                                                                                 |

| Cycles:          | 1                                                                                                 |

| Example:         | MOVW OPTION<br>F                                                                                  |

|                  | Before Instruction<br>OPTION = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION = 0x4F<br>W = 0x4F |

| MOVLW            | Move literal to W                                                                         |  |  |  |

|------------------|-------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                         |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                       |  |  |  |

| Status Affected: | None                                                                                      |  |  |  |

| Description:     | The 8-bit literal 'k' is loaded into W register. The "don't cares" will assemble as '0's. |  |  |  |

| Words:           | 1                                                                                         |  |  |  |

| Cycles:          | 1                                                                                         |  |  |  |

| Example:         | MOVLW 0x5A                                                                                |  |  |  |

|                  | After Instruction<br>W = 0x5A                                                             |  |  |  |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

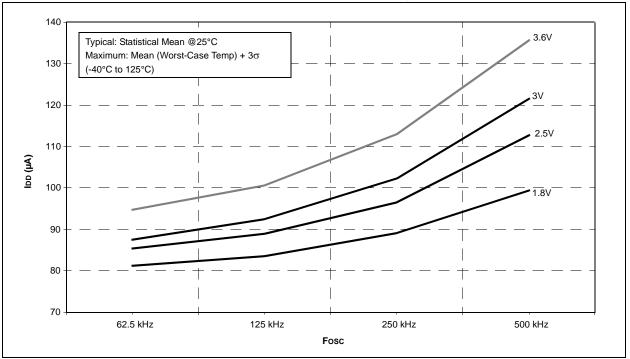

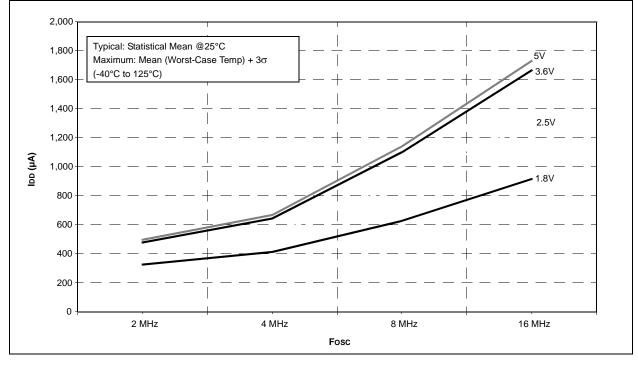

## 25.4 DC Characteristics: PIC16(L)F707-I/E

|              | DC CI | HARACTERISTICS                       | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature -40°C \leq TA \leq +85°C for industrial} \\ \ -40°C \leq TA \leq +125°C for extended \end{array}$ |      |          |       |                                                                         |  |  |

|--------------|-------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-------|-------------------------------------------------------------------------|--|--|

| Param<br>No. | Sym.  | Characteristic                       | Min.                                                                                                                                                                                                              | Тур† | Max.     | Units | Conditions                                                              |  |  |

|              | VIL   | Input Low Voltage                    |                                                                                                                                                                                                                   |      |          |       |                                                                         |  |  |

|              |       | I/O PORT:                            |                                                                                                                                                                                                                   |      |          |       |                                                                         |  |  |

| D030         |       | with TTL buffer                      | —                                                                                                                                                                                                                 | _    | 0.8      | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                        |  |  |

| D030A        |       |                                      | —                                                                                                                                                                                                                 | _    | 0.15 Vdd | V     | $1.8V \leq V\text{DD} \leq 4.5V$                                        |  |  |

| D031         |       | with Schmitt Trigger buffer          | —                                                                                                                                                                                                                 | _    | 0.2 Vdd  | V     | $2.0V \leq V \text{DD} \leq 5.5 \text{V}$                               |  |  |

|              |       | with I <sup>2</sup> C levels         | —                                                                                                                                                                                                                 | _    | 0.3 Vdd  | V     |                                                                         |  |  |

| D032         |       | MCLR, OSC1 (RC mode) <sup>(1)</sup>  |                                                                                                                                                                                                                   | _    | 0.2 Vdd  | V     |                                                                         |  |  |

| D033A        |       | OSC1 (HS mode)                       |                                                                                                                                                                                                                   | _    | 0.3 Vdd  | V     |                                                                         |  |  |

|              | VIH   | Input High Voltage                   |                                                                                                                                                                                                                   |      |          |       | •                                                                       |  |  |

|              |       | I/O ports:                           |                                                                                                                                                                                                                   | _    | _        |       |                                                                         |  |  |

| D040         |       | with TTL buffer                      | 2.0                                                                                                                                                                                                               | _    | _        | V     | $4.5V \le VDD \le 5.5V$                                                 |  |  |

| D040A        |       |                                      | 0.25 VDD+<br>0.8                                                                                                                                                                                                  | —    | -        | V     | $1.8V \leq VDD \leq 4.5V$                                               |  |  |

| D041         |       | with Schmitt Trigger buffer          | 0.8 Vdd                                                                                                                                                                                                           | —    | —        | V     | $2.0V \le V\text{DD} \le 5.5V$                                          |  |  |

|              |       | with I <sup>2</sup> C levels         | 0.7 Vdd                                                                                                                                                                                                           | —    | —        | V     |                                                                         |  |  |

| D042         |       | MCLR                                 | 0.8 Vdd                                                                                                                                                                                                           | _    | _        | V     |                                                                         |  |  |

| D043A        |       | OSC1 (HS mode)                       | 0.7 Vdd                                                                                                                                                                                                           | —    | —        | V     |                                                                         |  |  |

| D043B        |       | OSC1 (RC mode)                       | 0.9 Vdd                                                                                                                                                                                                           | _    | —        | V     | (Note 1)                                                                |  |  |

|              | lı∟   | Input Leakage Current <sup>(2)</sup> |                                                                                                                                                                                                                   |      | •        | •     |                                                                         |  |  |

| D060         |       | I/O ports                            | —                                                                                                                                                                                                                 | ± 5  | ± 125    | nA    | Vss $\leq$ VPIN $\leq$ VDD, Pin at high-<br>impedance, 85°C             |  |  |

|              |       |                                      |                                                                                                                                                                                                                   | ± 5  | ± 1000   | nA    | 125°C                                                                   |  |  |

| D061         |       | MCLR <sup>(3)</sup>                  | —                                                                                                                                                                                                                 | ± 50 | ± 200    | nA    | $Vss \leq V \text{PIN} \leq V \text{DD},  85^\circ C$                   |  |  |

|              | IPUR  | PORTB Weak Pull-up Current           |                                                                                                                                                                                                                   |      |          |       |                                                                         |  |  |

| D070*        |       |                                      | 25                                                                                                                                                                                                                | 100  | 200      |       | VDD = 3.3V, VPIN = VSS                                                  |  |  |

|              |       |                                      | 25                                                                                                                                                                                                                | 140  | 300      | μΑ    | VDD = 5.0V, VPIN = VSS                                                  |  |  |

|              | Vol   | Output Low Voltage <sup>(4)</sup>    | 1                                                                                                                                                                                                                 |      | 1        |       |                                                                         |  |  |

| D080         |       | I/O ports                            | _                                                                                                                                                                                                                 | —    | 0.6      | V     | IOL = 8mA, VDD = 5V<br>IOL = 6mA, VDD = 3.3V<br>IOL = 1.8mA, VDD = 1.8V |  |  |

|              | Voh   | Output High Voltage <sup>(4)</sup>   |                                                                                                                                                                                                                   |      |          |       |                                                                         |  |  |

| D090         |       | I/O ports                            | Vdd - 0.7                                                                                                                                                                                                         | _    | _        | V     | IOH = 3.5mA, VDD = 5V<br>IOH = 3mA, VDD = 3.3V<br>IOH = 1mA, VDD = 1.8V |  |  |

|              |       | Capacitive Loading Specs on          | Output Pins                                                                                                                                                                                                       |      |          | 1     |                                                                         |  |  |

| D101*        | COSC2 |                                      | _                                                                                                                                                                                                                 | _    | 15       | pF    | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1  |  |  |

| D101A*       | Сю    | All I/O pins                         | _                                                                                                                                                                                                                 | _    | 50       | pF    |                                                                         |  |  |

|              |       | Program Flash Memory                 | 1                                                                                                                                                                                                                 |      |          | F.    | I                                                                       |  |  |

Legend: TBD = To Be Determined

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: Including OSC2 in CLKOUT mode.

## TABLE 25-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER,<br/>AND BROWN-OUT RESET PARAMETERS

| Standard Operating Conditions (unless otherwise stated)<br>Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |        |                                                             |              |            |              |          |                                                |

|--------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------------------------|--------------|------------|--------------|----------|------------------------------------------------|

| Param<br>No.                                                                                                             | Sym.   | Characteristic                                              | Min.         | Тур†       | Max.         | Units    | Conditions                                     |

| 30                                                                                                                       | ТмсL   | MCLR Pulse Width (low)                                      | 2<br>5       |            |              | μS<br>μS | VDD = 3.3-5V, -40°C to +85°C<br>VDD = 3.3-5V   |

| 31                                                                                                                       | TWDTLP | Low Power Watchdog Timer Time-<br>out Period (No Prescaler) | 10           | 18         | 27           | ms       | VDD = 3.3V-5V                                  |

| 32                                                                                                                       | Tost   | Oscillator Start-up Timer Period <sup>(1),</sup><br>(2)     | —            | 1024       | _            | Tosc     | (Note 3)                                       |

| 33*                                                                                                                      | TPWRT  | Power-up Timer Period,<br>PWRTE = 0                         | 40           | 65         | 140          | ms       |                                                |

| 34*                                                                                                                      | Tioz   | I/O high-impedance from MCLR<br>Low or Watchdog Timer Reset | —            | _          | 2.0          | μS       |                                                |

| 35                                                                                                                       | VBOR   | Brown-out Reset Voltage                                     | 2.38<br>1.80 | 2.5<br>1.9 | 2.73<br>2.11 | V        | BORV=2.5V<br>BORV=1.9V                         |

| 36*                                                                                                                      | VHYST  | Brown-out Reset Hysteresis                                  | 0            | 25         | 50           | mV       | -40°C to +85°C                                 |