Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 36                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 363 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                              |

| Data Converters            | A/D 14x8b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf707-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABL | E 1:        | 40          | 40/44-PIN ALLOCATION TABLE FOR PIC16F707/PIC16LF707 |              |       |     |     |            |        |     |        |     |           |         |       |

|------|-------------|-------------|-----------------------------------------------------|--------------|-------|-----|-----|------------|--------|-----|--------|-----|-----------|---------|-------|

| Q    | 40-Pin PDIP | 40-Pin UQFN | 44-Pin TQFP                                         | 44-Pin QFN   | ANSEL | A/D | DAC | Cap Sensor | Timers | ССР | AUSART | SSP | Interrupt | Pull-up | Basic |

| Vdd  | 11, 32      | 7,<br>26    | 7, 28                                               | 7, 8, 28     |       | _   |     |            | —      | —   | _      |     |           | —       | Vdd   |

| Vss  | 12, 31      | 6,<br>27    | 6, 29                                               | 6, 30,<br>31 |       | _   |     |            | _      | —   | _      | _   |           | _       | Vss   |

**Note 1:** Pull-up activated only with external MCLR configuration.

2: RC1 is the default pin location for CCP2. RB3 may be selected by changing the CCP2SEL bit in the APFCON register.

3: RA5 is the default pin location for SS. RA0 may be selected by changing the SSSEL bit in the APFCON register.

4: PIC16F707 only. VCAP functionality is selectable by the VCAPEN bits in Configuration Word 2.

# TABLE 1-1: PIC16(L)F707 PINOUT DESCRIPTION

| Name                  | Function | Input<br>Type | Output<br>Type | Description                                                                                       |  |  |  |

|-----------------------|----------|---------------|----------------|---------------------------------------------------------------------------------------------------|--|--|--|

| RA0/AN0/SS/Vcap       | RA0      | TTL           | CMOS           | General purpose I/O.                                                                              |  |  |  |

|                       | AN0      | AN            | —              | A/D Channel 0 input.                                                                              |  |  |  |

|                       | SS       | ST            | —              | Slave Select input.                                                                               |  |  |  |

|                       | VCAP     | Power         | Power          | Filter capacitor for Voltage Regulator (PIC16F only).                                             |  |  |  |

| RA1/AN1/CPSA0         | RA1      | TTL           | CMOS           | General purpose I/O.                                                                              |  |  |  |

|                       | AN1      | AN            | —              | A/D Channel 1 input.                                                                              |  |  |  |

|                       | CPSA0    | AN            |                | Capacitive sensing A input 0.                                                                     |  |  |  |

| RA2/AN2/CPSA1/DACOUT  | RA2      | TTL           | CMOS           | General purpose I/O.                                                                              |  |  |  |

|                       | AN2      | AN            | —              | A/D Channel 2 input.                                                                              |  |  |  |

|                       | CPSA1    | AN            |                | Capacitive sensing A input 1.                                                                     |  |  |  |

|                       | DACOUT   | _             | AN             | Voltage Reference Output.                                                                         |  |  |  |

| RA3/AN3/VREF/CPSA2    | RA3      | TTL           | CMOS           | General purpose I/O.                                                                              |  |  |  |

|                       | AN3      | AN            | _              | A/D Channel 3 input.                                                                              |  |  |  |

|                       | VREF     | AN            | —              | A/D Voltage Reference input.                                                                      |  |  |  |

|                       | CPSA2    | AN            | _              | Capacitive sensing A input 2.                                                                     |  |  |  |

| RA4/CPSA3/T0CKI/TACKI | RA4      | TTL           | CMOS           | General purpose I/O.                                                                              |  |  |  |

|                       | CPSA3    | AN            | —              | Capacitive sensing A input 3.                                                                     |  |  |  |

|                       | TOCKI    | ST            | —              | Timer0 clock input.                                                                               |  |  |  |

|                       | TACKI    | ST            | _              | TimerA clock input.                                                                               |  |  |  |

| RA5/AN4/CPSA4/SS/VCAP | RA5      | TTL           | CMOS           | General purpose I/O.                                                                              |  |  |  |

|                       | AN4      | AN            | —              | A/D Channel 4 input.                                                                              |  |  |  |

|                       | CPSA4    | AN            | _              | Capacitive sensing A input 4.                                                                     |  |  |  |

|                       | SS       | ST            | _              | Slave Select input.                                                                               |  |  |  |

|                       | VCAP     | Power         | Power          | Filter capacitor for Voltage Regulator (PIC16F only).                                             |  |  |  |

| RA6/OSC2/CLKOUT/VCAP/ | RA6      | TTL           | CMOS           | General purpose I/O.                                                                              |  |  |  |

| CPSB1                 | OSC2     | _             | XTAL           | Crystal/Resonator (LP, XT, HS modes).                                                             |  |  |  |

|                       | CLKOUT   | _             | CMOS           | Fosc/4 output.                                                                                    |  |  |  |

|                       | VCAP     | Power         | Power          | Filter capacitor for Voltage Regulator (PIC16F only).                                             |  |  |  |

|                       | CPSB1    | AN            |                | Capacitive sensing B input 1.                                                                     |  |  |  |

| RA7/OSC1/CLKIN/CPSB0  | RA7      | TTL           | CMOS           | General purpose I/O.                                                                              |  |  |  |

|                       | OSC1     | XTAL          |                | Crystal/Resonator (LP, XT, HS modes).                                                             |  |  |  |

|                       | CLKIN    | CMOS          |                | External clock input (EC mode).                                                                   |  |  |  |

|                       | CLKIN    | ST            |                | RC oscillator connection (RC mode).                                                               |  |  |  |

|                       | CPSB0    | AN            | _              | Capacitive sensing B input 0.                                                                     |  |  |  |

| RB0/AN12/CPSB8/INT    | RB0      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up. |  |  |  |

|                       | AN12     | AN            | —              | A/D Channel 12 input.                                                                             |  |  |  |

|                       | CPSB8    | AN            | —              | Capacitive sensing B input 8.                                                                     |  |  |  |

|                       | INT      | ST            | —              | External interrupt.                                                                               |  |  |  |

| RB1/AN10/CPSB9        | RB1      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up. |  |  |  |

|                       | AN10     | AN            | —              | A/D Channel 10 input.                                                                             |  |  |  |

|                       | CPSB9    | AN            | 1              | Capacitive sensing B input 9.                                                                     |  |  |  |

### 6.5 PORTD and TRISD Registers

PORTD is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISD (Register 6-14). Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 6-4 shows how to initialize PORTD.

Reading the PORTD register (Register 6-13) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch.

The TRISD register (Register 6-14) controls the PORTD pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISD register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### EXAMPLE 6-4: INITIALIZING PORTD

| BANKSEL PORTD  | ;                           |

|----------------|-----------------------------|

| CLRF PORTD     | ;Init PORTD                 |

| BANKSEL ANSELD |                             |

| CLRF ANSELD    | ;Make PORTD digital         |

| BANKSEL TRISD  | ;                           |

| MOVLW B'000011 | .00' ;Set RD<3:2> as inputs |

| MOVWF TRISD    | ;and set RD<7:4,1:0>        |

|                | ;as outputs                 |

|                |                             |

### 6.5.1 ANSELD REGISTER

The ANSELD register (Register 6-15) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELD bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELD bits has no affect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

**Note:** The ANSELD register must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'.

### REGISTER 6-13: PORTD: PORTD REGISTER

| R/W-x | R/W-x          | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|-------|----------------|-------|-------|-------|-------|-------|-------|

| RD7   | D7 RD6 RD5 RD4 |       | RD4   | RD3   | RD2   | RD1   | RD0   |

| bit 7 |                |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0

RD<7:0>: PORTD General Purpose I/O Pin bits

1 = Port pin is > VIH

0 = Port pin is < VIL

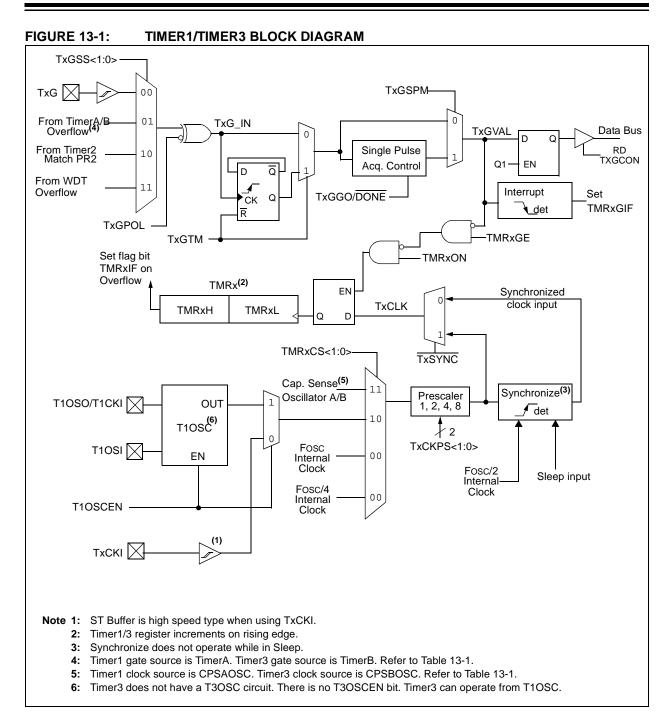

# TABLE 13-1:CPSOSC/TIMERASSOCIATION

| Period<br>Measurement | Cap Sense<br>Oscillator | Divider Timer<br>(Gate Source) |  |  |

|-----------------------|-------------------------|--------------------------------|--|--|

| Timer1                | CPS A                   | TimerA                         |  |  |

| Timer3                | CPS B                   | TimerB                         |  |  |

| U-0               | R/W-0                                          | R/W-0                  | R/W-0          | R/W-0             | R/W-0           | R/W-0           | R/W-0   |  |  |  |  |  |

|-------------------|------------------------------------------------|------------------------|----------------|-------------------|-----------------|-----------------|---------|--|--|--|--|--|

| _                 | TOUTPS3                                        | TOUTPS2                | TOUTPS1        | TOUTPS0           | TMR2ON          | T2CKPS1         | T2CKPS0 |  |  |  |  |  |

| bit 7             |                                                |                        |                |                   |                 |                 | bit C   |  |  |  |  |  |

|                   |                                                |                        |                |                   |                 |                 |         |  |  |  |  |  |

| Legend:           |                                                |                        |                |                   |                 |                 |         |  |  |  |  |  |

| R = Readal        | ble bit                                        | W = Writable           | bit            | U = Unimplen      | nented bit, rea | d as '0'        |         |  |  |  |  |  |

| -n = Value at POR |                                                | '1' = Bit is set       |                | '0' = Bit is clea | ared            | x = Bit is unkr | nown    |  |  |  |  |  |

|                   |                                                |                        |                |                   |                 |                 |         |  |  |  |  |  |

| bit 7             | Unimplemen                                     | ted: Read as '         | 0'             |                   |                 |                 |         |  |  |  |  |  |

| bit 6-3           | TOUTPS<3:0                                     | )>: Timer2 Outp        | out Postscaler | Select bits       |                 |                 |         |  |  |  |  |  |

|                   | 0000 = 1:1 P                                   | ostscaler              |                |                   |                 |                 |         |  |  |  |  |  |

|                   | 0001 = 1:2 P                                   | ostscaler              |                |                   |                 |                 |         |  |  |  |  |  |

|                   | 0010 = 1:3 P                                   |                        |                |                   |                 |                 |         |  |  |  |  |  |

|                   |                                                | 0011 = 1:4 Postscaler  |                |                   |                 |                 |         |  |  |  |  |  |

|                   |                                                | 0100 = 1.5 Postscaler  |                |                   |                 |                 |         |  |  |  |  |  |

|                   | 0101 = 1:6  Postscaler                         |                        |                |                   |                 |                 |         |  |  |  |  |  |

|                   | 0110 = 1:7 Postscaler<br>0111 = 1:8 Postscaler |                        |                |                   |                 |                 |         |  |  |  |  |  |

|                   | 1000 = 1.9 P                                   |                        |                |                   |                 |                 |         |  |  |  |  |  |

|                   |                                                | = 1.9 Postscaler       |                |                   |                 |                 |         |  |  |  |  |  |

|                   |                                                | 1001 = 1.10 Postscaler |                |                   |                 |                 |         |  |  |  |  |  |

|                   |                                                | 1010 = 1.11 Postscaler |                |                   |                 |                 |         |  |  |  |  |  |

|                   | 1100 <b>= 1:13</b>                             | Postscaler             |                |                   |                 |                 |         |  |  |  |  |  |

|                   | 1101 <b>= 1:14</b>                             | Postscaler             |                |                   |                 |                 |         |  |  |  |  |  |

|                   | 1110 <b>= 1:15</b>                             |                        |                |                   |                 |                 |         |  |  |  |  |  |

|                   | 1111 <b>= 1:16</b>                             | 1111 = 1:16 Postscaler |                |                   |                 |                 |         |  |  |  |  |  |

| bit 2             | TMR2ON: Tir                                    | TMR2ON: Timer2 On bit  |                |                   |                 |                 |         |  |  |  |  |  |

|                   | 1 = Timer2 is                                  | 1 = Timer2 is on       |                |                   |                 |                 |         |  |  |  |  |  |

|                   | 0 = Timer2 is                                  | soff                   |                |                   |                 |                 |         |  |  |  |  |  |

| bit 1-0           | T2CKPS<1:0                                     | >: Timer2 Cloc         | k Prescale Se  | lect bits         |                 |                 |         |  |  |  |  |  |

|                   | 00 = Prescale                                  | er is 1                |                |                   |                 |                 |         |  |  |  |  |  |

|                   | 01 = Prescale                                  | er is 4                |                |                   |                 |                 |         |  |  |  |  |  |

|                   | 1x = Prescale                                  | er is 16               |                |                   |                 |                 |         |  |  |  |  |  |

### REGISTER 15-1: T2CON: TIMER2 CONTROL REGISTER

| TABLE 15-1: | SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2 |

|-------------|---------------------------------------------|

|-------------|---------------------------------------------|

| Name    | Bit 7                                        | Bit 6   | Bit 5   | Bit 4        | Bit 3        | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |  |

|---------|----------------------------------------------|---------|---------|--------------|--------------|--------|---------|---------|----------------------|---------------------------------|--|

| INTCON  | GIE                                          | PEIE    | TMR0IE  | INTE         | RBIE         | TMR0IF | INTF    | RBIF    | 0000 000x            | 0000 000x                       |  |

| PIE1    | TMR1GIE                                      | ADIE    | RCIE    | TXIE         | SSPIE        | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                       |  |

| PIR1    | TMR1GIF                                      | ADIF    | RCIF    | TXIF         | SSPIF        | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                       |  |

| PR2     |                                              |         | Т       | imer2 Module | Period Regis | ter    |         |         | 1111 1111            | 1111 1111                       |  |

| TMR2    | Holding Register for the 8-bit TMR2 Register |         |         |              |              |        |         |         |                      | 0000 0000                       |  |

| T2CON   | _                                            | TOUTPS3 | TOUTPS2 | TOUTPS1      | TOUTPS0      | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                       |  |

| Logondu |                                              |         |         |              |              |        |         |         |                      |                                 |  |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for Timer2 module.

| U-0                | U-0                                                                                                                                                                     | R/W-0                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                      | R/W-0            | R/W-0                                                                                       | R/W-0                                                                       | R/W-0         |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------|

| _                  | —                                                                                                                                                                       | DCxB1                                                                                                                                                                                                                                                      | DCxB0                                                                                                                                                                                                      | CCPxM3           | CCPxM2                                                                                      | CCPxM1                                                                      | CCPxM0        |

| bit 7              | · · · · · · · · · · · · · · · · · · ·                                                                                                                                   |                                                                                                                                                                                                                                                            |                                                                                                                                                                                                            |                  | ·                                                                                           | •<br>                                                                       | bit (         |

| Legend:            |                                                                                                                                                                         |                                                                                                                                                                                                                                                            |                                                                                                                                                                                                            |                  |                                                                                             |                                                                             |               |

| R = Readable       | e bit                                                                                                                                                                   | W = Writable                                                                                                                                                                                                                                               | bit                                                                                                                                                                                                        | U = Unimpler     | nented bit, rea                                                                             | d as '0'                                                                    |               |

| -n = Value at      | POR                                                                                                                                                                     | '1' = Bit is set                                                                                                                                                                                                                                           |                                                                                                                                                                                                            | '0' = Bit is cle | ared                                                                                        | x = Bit is unki                                                             | nown          |

| bit 7-6<br>bit 5-4 | Unimplement                                                                                                                                                             |                                                                                                                                                                                                                                                            |                                                                                                                                                                                                            |                  |                                                                                             |                                                                             |               |

|                    | DCxB<1:0>: F<br>Capture mode<br>Unused<br>Compare mode<br>Unused<br><u>PWM mode:</u><br>These bits are                                                                  | 2:<br>le:                                                                                                                                                                                                                                                  | Ū                                                                                                                                                                                                          | luty cycle. The  | eight MSbs are                                                                              | e found in CCP                                                              | RxL.          |

| bit 3-0            | 0001 = Unuse<br>0010 = Comp<br>0011 = Unuse<br>0100 = Captu<br>0101 = Captu<br>0110 = Captu<br>0111 = Captu<br>1000 = Comp<br>1001 = Comp<br>1010 = Comp<br>1010 = Comp | ure/Compare/F<br>ed (reserved)<br>pare mode, tog<br>ed (reserved)<br>ure mode, even<br>ure mode, even<br>ure mode, even<br>pare mode, even<br>pare mode, set<br>pare mode, cle<br>pare mode, gen<br>a par is unaffect<br>pare mode, trig<br>v/D conversion | WM off (reset<br>gle output on<br>y falling edge<br>y rising edge<br>y 4th rising ed<br>y 16th rising ed<br>y 16th rising ed<br>output on ma<br>ar output on m<br>herate softwar<br>ted)<br>ger special ev |                  | bit of the PIR:<br>t of the PIRx re<br>bit of the PIRx<br>hatch (CCPxIF<br>it of the PIRx r | gister is set)<br>register is set)<br>bit is set of the<br>register is set. | PIRx register |

### REGISTER 17-1: CCPxCON: CCPx CONTROL REGISTER

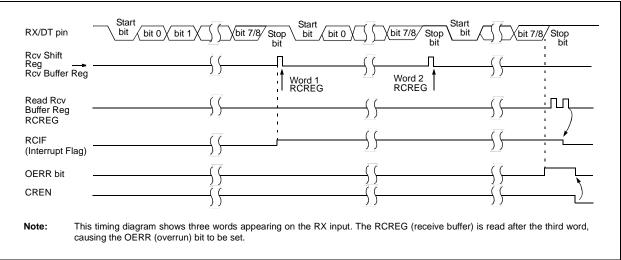

### TABLE 18-2: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Name   | Bit 7   | Bit 6  | Bit 5  | Bit 4      | Bit 3      | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|---------|--------|--------|------------|------------|--------|--------|--------|----------------------|---------------------------------|

| ANSELC | ANSC7   | ANSC6  | ANSC5  | —          | —          | ANSC2  | ANSC1  | ANSC0  | 111111               | 111111                          |

| INTCON | GIE     | PEIE   | TMR0IE | INTE       | RBIE       | TMR0IF | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE | ADIE   | RCIE   | TXIE       | SSPIE      | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF | ADIF   | RCIF   | TXIF       | SSPIF      | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCREG  |         |        | AUSA   | ART Receiv | e Data Reg | jister |        |        | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN    | RX9    | SREN   | CREN       | ADDEN      | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| SPBRG  | BRG7    | BRG6   | BRG5   | BRG4       | BRG3       | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |

| TRISC  | TRISC7  | TRISC6 | TRISC5 | TRISC4     | TRISC3     | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXSTA  | CSRC    | TX9    | TXEN   | SYNC       | _          | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for asynchronous reception.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in TXREG register.

- 3. The TXIF bit will not be set.

- 4. After the first character has been shifted out of TSR, the TXREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- 5. If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 18.3.2.2 Synchronous Slave Transmission Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the CREN and SREN bits.

- 3. If using interrupts, ensure that the GIE and PEIE bits of the INTCON register are set and set the TXIE bit.

- 4. If 9-bit transmission is desired, set the TX9 bit.

- 5. Enable transmission by setting the TXEN bit.

- 6. Verify address detection is disabled by clearing the ADDEN bit of the RCSTA register.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant eight bits to the TXREG register.

| Name   | Bit 7                         | Bit 6  | Bit 5  | Bit 4  | Bit 3     | Bit 2     | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------------------------------|--------|--------|--------|-----------|-----------|--------|--------|----------------------|---------------------------------|

| ANSELC | ANSC7                         | ANSC6  | ANSC5  | _      | —         | ANSC2     | ANSC1  | ANSC0  | 111111               | 111111                          |

| INTCON | GIE                           | PEIE   | TMR0IE | INTE   | RBIE      | TMR0IF    | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE                       | ADIE   | RCIE   | TXIE   | SSPIE     | CCP1IE    | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF                       | ADIF   | RCIF   | TXIF   | SSPIF     | CCP1IF    | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN                          | RX9    | SREN   | CREN   | ADDEN     | FERR      | OERR   | RX9D   | 0000 000X            | 0000 000x                       |

| TRISC  | TRISC7                        | TRISC6 | TRISC5 | TRISC4 | TRISC3    | TRISC2    | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXREG  | AUSART Transmit Data Register |        |        |        | 0000 0000 | 0000 0000 |        |        |                      |                                 |

| TXSTA  | CSRC                          | TX9    | TXEN   | SYNC   | —         | BRGH      | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

### TABLE 18-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for synchronous slave transmission.

### 18.3.2.3 AUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section 18.3.1.4 "Synchronous Master Reception"), with the following exceptions:

- Sleep

- CREN bit is always set, therefore the receiver is never Idle

- SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RCREG register. If the RCIE interrupt enable bit of the PIE1 register is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector. 18.3.2.4 Synchronous Slave Reception Setup:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 3. If 9-bit reception is desired, set the RX9 bit.

- 4. Verify address detection is disabled by clearing the ADDEN bit of the RCSTA register.

- 5. Set the CREN bit to enable reception.

- The RCIF bit of the PIR1 register will be set when reception is complete. An interrupt will be generated if the RCIE bit of the PIE1 register was set.

- 7. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCSTA register.

- 8. Retrieve the eight Least Significant bits from the receive FIFO by reading the RCREG register.

- 9. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register.

# REGISTER 19-2: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (SPI MODE)

| R/W-0             | R/W-0                                                                        | R-0                       | R-0            | R-0                  | R-0            | R-0                | R-0   |  |  |  |

|-------------------|------------------------------------------------------------------------------|---------------------------|----------------|----------------------|----------------|--------------------|-------|--|--|--|

| SMP               | CKE                                                                          | D/A                       | Р              | S                    | R/W            | UA                 | BF    |  |  |  |

| bit 7             |                                                                              |                           |                |                      |                |                    | bit ( |  |  |  |

| Legend:           |                                                                              |                           |                |                      |                |                    |       |  |  |  |

| R = Readabl       | le bit                                                                       | W = Writable              | bit            | U = Unimpler         | mented bit, re | ad as '0'          |       |  |  |  |

| -n = Value at POR |                                                                              | '1' = Bit is set          |                | '0' = Bit is cleared |                | x = Bit is unknown |       |  |  |  |

| bit 7             | SMP: SPI D                                                                   | Data Input Sampl          | e Phase bit    |                      |                |                    |       |  |  |  |

|                   | SPI Master                                                                   |                           |                |                      |                |                    |       |  |  |  |

|                   |                                                                              | ata sampled at er         | nd of data out | tput time            |                |                    |       |  |  |  |

|                   |                                                                              | ata sampled at m          | iddle of data  | output time          |                |                    |       |  |  |  |

|                   | <u>SPI Slave mode:</u><br>SMP must be cleared when SPI is used in Slave mode |                           |                |                      |                |                    |       |  |  |  |

| L:1 0             |                                                                              |                           |                | n Slave mode         |                |                    |       |  |  |  |

| bit 6             | CKE: SPI Clock Edge Select bit                                               |                           |                |                      |                |                    |       |  |  |  |

|                   | <u>SPI mode, CKP = 0:</u><br>1 = Data stable on rising edge of SCK           |                           |                |                      |                |                    |       |  |  |  |

|                   | 0 = Data stable on falling edge of SCK                                       |                           |                |                      |                |                    |       |  |  |  |

|                   | SPI mode, CKP = 1:                                                           |                           |                |                      |                |                    |       |  |  |  |

|                   | 1 = Data stable on falling edge of SCK                                       |                           |                |                      |                |                    |       |  |  |  |

|                   | _                                                                            | able on rising edg        | ge of SCK      |                      |                |                    |       |  |  |  |

| bit 5             | D/A: Data/Address bit<br>Used in I <sup>2</sup> C mode only.                 |                           |                |                      |                |                    |       |  |  |  |

|                   |                                                                              | mode only.                |                |                      |                |                    |       |  |  |  |

| bit 4             | P: Stop bit                                                                  |                           |                |                      |                |                    |       |  |  |  |

| 1 1 0             | Used in I <sup>2</sup> C                                                     | mode only.                |                |                      |                |                    |       |  |  |  |

| bit 3             | <b>S:</b> Start bit                                                          |                           |                |                      |                |                    |       |  |  |  |

| h 11 O            |                                                                              | Used in $I^2C$ mode only. |                |                      |                |                    |       |  |  |  |

| bit 2             | <b>R/W:</b> Read/Write Information bit                                       |                           |                |                      |                |                    |       |  |  |  |

| L:1. 4            | Used in I <sup>2</sup> C mode only.<br><b>UA:</b> Update Address bit         |                           |                |                      |                |                    |       |  |  |  |

| bit 1             | UA: Update<br>Used in I <sup>2</sup> C                                       |                           |                |                      |                |                    |       |  |  |  |

| <b>h</b> :+ 0     |                                                                              | ,                         |                |                      |                |                    |       |  |  |  |

| bit 0             |                                                                              | Full Status bit           |                |                      |                |                    |       |  |  |  |

|                   | 1 = Receive<br>0 = Receive                                                   | e complete, SSPI          | BUF IS TUIL    |                      |                |                    |       |  |  |  |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                             |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                              |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next<br>instruction is discarded and a NOP<br>is executed instead, making this a<br>2-cycle instruction. |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                                  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] CLRWDT                                                                                                                                                        |  |  |  |  |

| Operands:        | None                                                                                                                                                                  |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow \underline{WDT} \text{ prescaler,} \\ 1 \rightarrow \underline{TO} \\ 1 \rightarrow \overline{PD} \end{array}$ |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                                |  |  |  |  |

| Description:     | CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT.<br>Status bits TO and PD are set.                                        |  |  |  |  |

| CALL             | Call Subroutine                                                                                                                                                                                                                             |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                     |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                        |  |  |  |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                                                                            |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                        |  |  |  |

| Description:     | Call Subroutine. First, return<br>address (PC + 1) is pushed onto<br>the stack. The eleven-bit<br>immediate address is loaded into<br>PC bits <10:0>. The upper bits of<br>the PC are loaded from PCLATH.<br>CALL is a 2-cycle instruction. |  |  |  |

| COMF             | Complement f                                                                                                                                                   |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] COMF f,d                                                                                                                                             |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                     |  |  |  |

| Status Affected: | Z                                                                                                                                                              |  |  |  |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is '0', the<br>result is stored in W. If 'd' is '1',<br>the result is stored back in<br>register 'f'. |  |  |  |

| CLRF             | Clear f                                                               |  |  |

|------------------|-----------------------------------------------------------------------|--|--|

| Syntax:          | [label] CLRF f                                                        |  |  |

| Operands:        | $0 \le f \le 127$                                                     |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |  |  |

| Status Affected: | Z                                                                     |  |  |

| Description:     | The contents of register 'f' are<br>cleared and the Z bit is set.     |  |  |

| DECF             | Decrement f                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] DECF f,d                                                                                                                                |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                 |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                               |

| Status Affected: | Z                                                                                                                                                 |

| Description:     | Decrement register 'f'. If 'd' is '0',<br>the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |

| CLRW             | Clear W                                                                                    |  |  |  |

|------------------|--------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] CLRW                                                                               |  |  |  |

| Operands:        | None                                                                                       |  |  |  |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow (\text{W}) \\ 1 \rightarrow \text{Z} \end{array}$ |  |  |  |

| Status Affected: | Z                                                                                          |  |  |  |

| Description:     | W register is cleared. Zero bit (Z) is set.                                                |  |  |  |

# 24.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

### 24.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- Multiple configurations

- · Simultaneous debugging sessions

- File History and Bug Tracking:

- Local file history feature

- Built-in support for Bugzilla issue tracker

# 25.6 Timing Parameter Symbology

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| 2. TPp0 |                                       |     |                |  |

|---------|---------------------------------------|-----|----------------|--|

| т       |                                       |     |                |  |

| F       | Frequency                             | Т   | Time           |  |

| Lowerc  | case letters (pp) and their meanings: |     |                |  |

| рр      |                                       |     |                |  |

| сс      | CCP1                                  | OSC | OSC1           |  |

| ck      | CLKOUT                                | rd  | RD             |  |

| cs      | CS                                    | rw  | RD or WR       |  |

| di      | SDI                                   | sc  | SCK            |  |

| do      | SDO                                   | SS  | SS             |  |

| dt      | Data in                               | tO  | TOCKI          |  |

| io      | I/O PORT                              | t1  | T1CKI          |  |

| mc      | MCLR                                  | wr  | WR             |  |

| Upperc  | case letters and their meanings:      |     |                |  |

| S       |                                       |     |                |  |

| F       | Fall                                  | Р   | Period         |  |

| н       | High                                  | R   | Rise           |  |

| I       | Invalid (High-impedance)              | V   | Valid          |  |

| L       | Low                                   | Z   | High-impedance |  |

### FIGURE 25-2: LOAD CONDITIONS

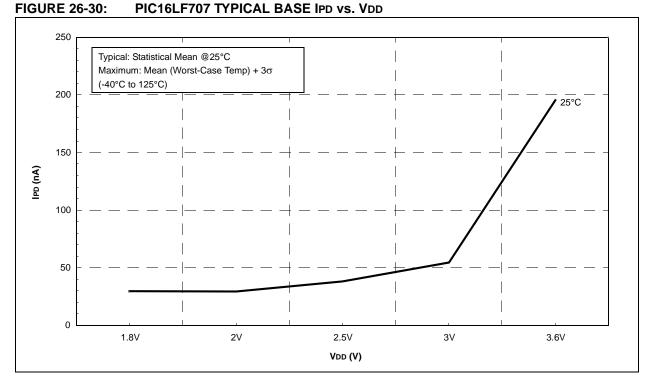

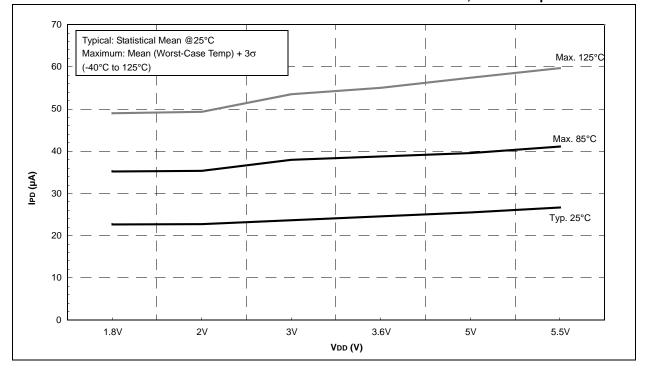

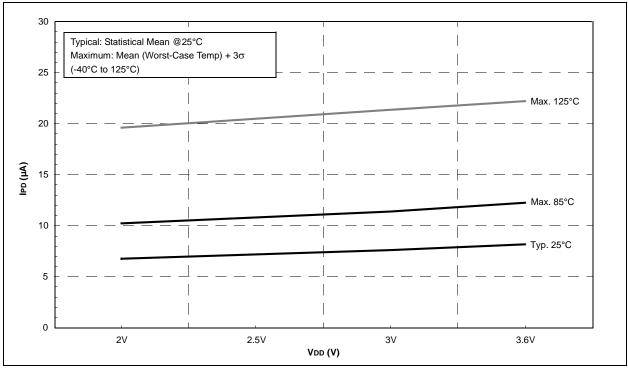

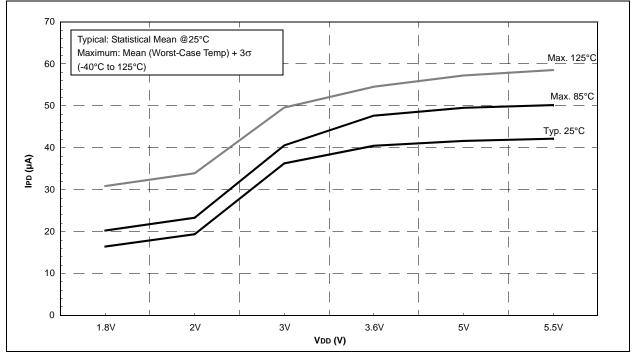

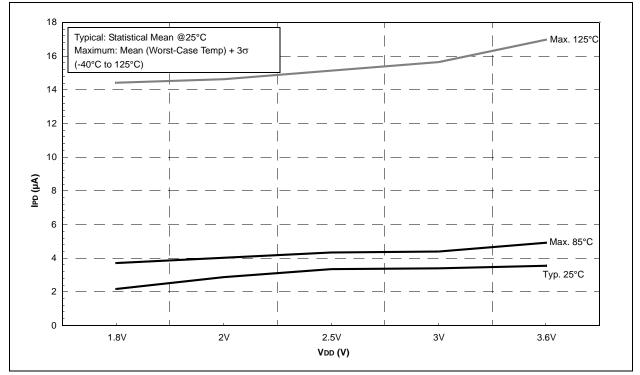

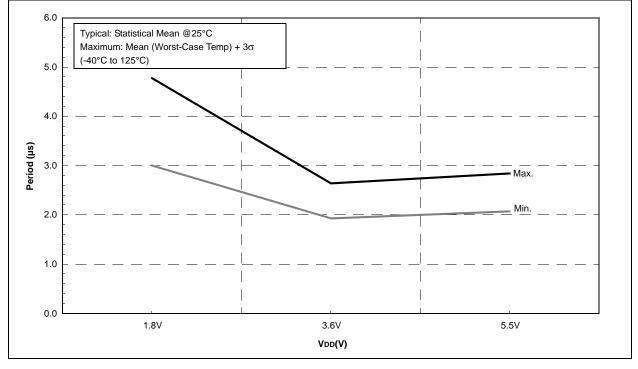

### FIGURE 26-34: PIC16LF707 BOR IPD vs. VDD

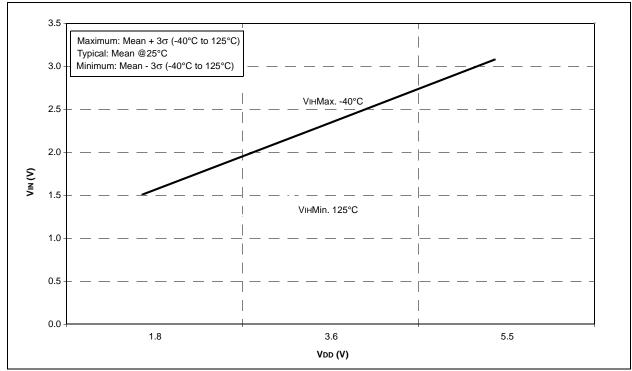

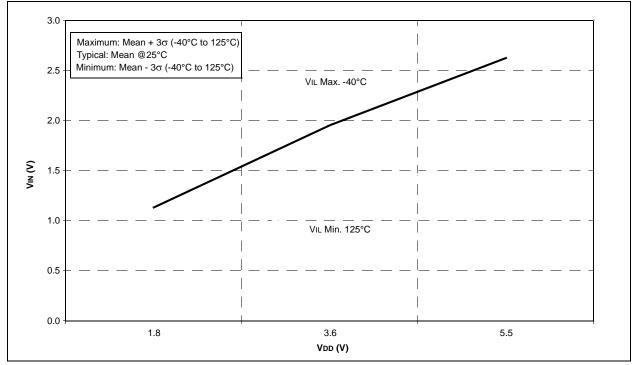

FIGURE 26-50: SCHMITT TRIGGER INPUT THRESHOLD VIN vs. VDD OVER TEMPERATURE

FIGURE 26-51: SCHMITT TRIGGER INPUT THRESHOLD VIN vs. VDD OVER TEMPERATURE

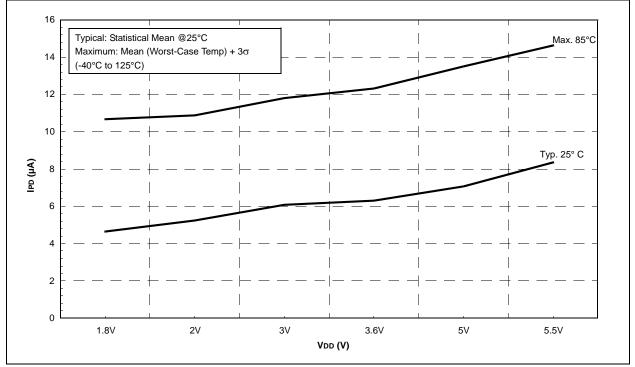

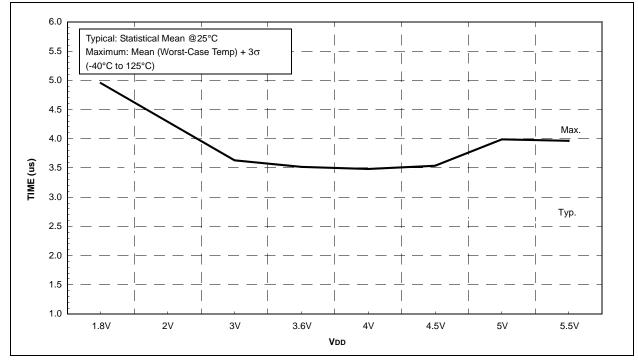

### FIGURE 26-60: PIC16F707 HFINTOSC WAKE-UP FROM SLEEP START-UP TIME

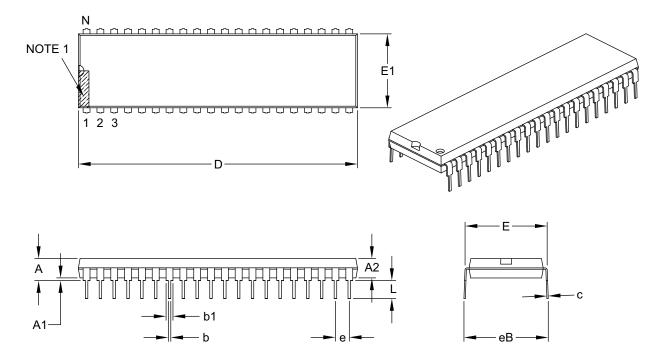

## 27.2 Package Details

The following sections give the technical details of the packages.

# 40-Lead Plastic Dual In-Line (P) – 600 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units      |       | INCHES   |       |

|----------------------------|------------|-------|----------|-------|

| Dimensi                    | ion Limits | MIN   | NOM      | MAX   |

| Number of Pins             | Ν          |       | 40       |       |

| Pitch                      | е          |       | .100 BSC |       |

| Top to Seating Plane       | Α          | _     | -        | .250  |

| Molded Package Thickness   | A2         | .125  | -        | .195  |

| Base to Seating Plane      | A1         | .015  | -        | -     |

| Shoulder to Shoulder Width | Е          | .590  | -        | .625  |

| Molded Package Width       | E1         | .485  | -        | .580  |

| Overall Length             | D          | 1.980 | -        | 2.095 |

| Tip to Seating Plane       | L          | .115  | -        | .200  |

| Lead Thickness             | С          | .008  | -        | .015  |

| Upper Lead Width           | b1         | .030  | -        | .070  |

| Lower Lead Width           | b          | .014  | -        | .023  |

| Overall Row Spacing §      | eB         | -     | -        | .700  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-016B