Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| 2010                       |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 363 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 14x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf707-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                         |            |        | -                                                                                                 | -            | -             | •                | -                 |               |           |                       |                                 |

|-------------------------|------------|--------|---------------------------------------------------------------------------------------------------|--------------|---------------|------------------|-------------------|---------------|-----------|-----------------------|---------------------------------|

| Address                 | Name       | Bit 7  | Bit 6                                                                                             | Bit 5        | Bit 4         | Bit 3            | Bit 2             | Bit 1         | Bit 0     | Value on:<br>POR, BOR | Value on all<br>other<br>Resets |

| Bank 3                  |            |        |                                                                                                   |              |               |                  |                   |               |           |                       |                                 |

| 180h <sup>(2)</sup>     | INDF       | Addres | sing this loca                                                                                    | tion uses co | ntents of FSF | R to address da  | ata memory (no    | ot a physical | register) | xxxx xxxx             | xxxx xxxx                       |

| 181h                    | OPTION_REG | RBPU   | RBPU         INTEDG         TMR0CS         TMR0SE         PSA         PS2         PS1         PS0 |              |               |                  |                   |               | 1111 1111 | 1111 1111             |                                 |

| 182h <sup>(2)</sup>     | PCL        |        |                                                                                                   | Progra       | n Counter (P  | C) Least Signi   | ficant Byte       |               |           | 0000 0000             | 0000 0000                       |

| 183h <sup>(2)</sup>     | STATUS     | IRP    | RP1                                                                                               | RP0          | TO            | PD               | Z                 | DC            | С         | 0001 1xxx             | 000q quuu                       |

| 184h <sup>(2)</sup>     | FSR        |        | Indirect Data Memory Address Pointer                                                              |              |               |                  |                   |               |           | xxxx xxxx             | uuuu uuuu                       |

| 185h                    | ANSELA     | ANSA7  | ANSA6                                                                                             | ANSA5        | ANSA4         | ANSA3            | ANSA2             | ANSA1         | ANSA0     | 1111 1111             | 1111 1111                       |

| 186h                    | ANSELB     | ANSB7  | ANSB6                                                                                             | ANSB5        | ANSB4         | ANSB3            | ANSB2             | ANSB1         | ANSB0     | 1111 1111             | 1111 1111                       |

| 187h                    | ANSELC     | ANSC7  | ANSC6                                                                                             | ANSC5        | _             | _                | ANSC2             | ANSC1         | ANSC0     | 111111                | 111111                          |

| 188h                    | ANSELD     | ANSD7  | ANSD6                                                                                             | ANSD5        | ANSD4         | ANSD3            | ANSD2             | ANSD1         | ANSD0     | 1111 1111             | 1111 1111                       |

| 189h                    | ANSELE     | _      | _                                                                                                 | _            | _             | _                | ANSE2             | ANSE1         | ANSE0     | 111                   | 111                             |

| 18Ah <sup>(1),(2)</sup> | PCLATH     | _      | _                                                                                                 | _            | Write I       | Buffer for the u | oper 5 bits of th | ne Program C  | Counter   | 0 0000                | 0 0000                          |

| 18Bh <sup>(2)</sup>     | INTCON     | GIE    | PEIE                                                                                              | TMR0IE       | INTE          | RBIE             | TMR0IF            | INTF          | RBIF      | 0000 000x             | 0000 000u                       |

| 18Ch                    | PMCON1     | _      | —                                                                                                 | —            | _             | —                | —                 | _             | RD        | 10                    | 10                              |

| 18Dh                    | —          |        |                                                                                                   |              | Re            | eserved          |                   |               |           | _                     | —                               |

| 18Eh                    | —          |        |                                                                                                   |              | Re            | eserved          |                   |               |           | _                     | _                               |

| 18Fh                    | —          |        |                                                                                                   |              | Re            | eserved          |                   |               |           | _                     | _                               |

| 1 · · · · · ·           |            |        |                                                                                                   |              |               |                  |                   |               |           |                       |                                 |

**TABLE 2-2:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', x = reserved. Shaded locations are unimplemented, read as '0'.

Note

1:

The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter.

2:

These registers can be addressed from any bank.

3:

Accessible only when SSPM<3:0> = 1001.

## 2.2.2.2 OPTION Register

The OPTION register, shown in Register 2-2, is a readable and writable register, which contains various control bits to configure:

- Timer0/WDT prescaler

- External RB0/INT interrupt

- Timer0

- Weak pull-ups on PORTB

Note: To achieve a 1:1 prescaler assignment for Timer0, assign the prescaler to the WDT by setting PSA bit of the OPTION register to '1'. Refer to Section 13.3 "Timer1/3 Prescaler".

## REGISTER 2-2: OPTION\_REG: OPTION REGISTER

| R/W-1 | R/W-1 | R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 |  |

|-------|-------|-------|--------|-------|-------|-------|-------|--|

| RBPU  |       |       | TMR0SE | PSA   | PS2   | PS1   | PS0   |  |

| bit 7 | ·     |       |        |       |       |       | bit 0 |  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | RBPU: PORTB Pul                                 | I-up Enable bi                                                                                                       | t                                                    |                         |     |  |  |  |  |  |  |

|---------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------------------------|-----|--|--|--|--|--|--|

|         | 1 = PORTB pull-up<br>0 = PORTB pull-up          |                                                                                                                      |                                                      | bits in the WPUB regist | ter |  |  |  |  |  |  |

| bit 6   | INTEDG: Interrupt                               | INTEDG: Interrupt Edge Select bit                                                                                    |                                                      |                         |     |  |  |  |  |  |  |

|         | 1 = Interrupt on risi<br>0 = Interrupt on falli |                                                                                                                      |                                                      |                         |     |  |  |  |  |  |  |

| bit 5   | TMR0CS: Timer0 Clock Source Select bit          |                                                                                                                      |                                                      |                         |     |  |  |  |  |  |  |

|         | 1 = Transition on R<br>0 = Internal instruct    |                                                                                                                      | k (Fosc/4)                                           |                         |     |  |  |  |  |  |  |

| bit 4   | TMR0SE: Timer0 Source Edge Select bit           |                                                                                                                      |                                                      |                         |     |  |  |  |  |  |  |

|         |                                                 | 1 = Increment on high-to-low transition on RA4/T0CKI pin<br>0 = Increment on low-to-high transition on RA4/T0CKI pin |                                                      |                         |     |  |  |  |  |  |  |

| bit 3   | PSA: Prescaler Ass                              | signment bit                                                                                                         |                                                      |                         |     |  |  |  |  |  |  |

|         | 1 = Prescaler is ass<br>0 = Prescaler is ass    | •                                                                                                                    |                                                      | e                       |     |  |  |  |  |  |  |

| bit 2-0 | PS<2:0>: Prescale                               | r Rate Select b                                                                                                      | oits                                                 |                         |     |  |  |  |  |  |  |

|         | Bit Value                                       | Timer0 Rate                                                                                                          | WDT Rate                                             |                         |     |  |  |  |  |  |  |

|         | 000<br>001<br>010<br>011<br>100<br>101          | 1 : 2<br>1 : 4<br>1 : 8<br>1 : 16<br>1 : 32<br>1 : 64                                                                | 1 : 1<br>1 : 2<br>1 : 4<br>1 : 8<br>1 : 16<br>1 : 32 |                         |     |  |  |  |  |  |  |

|         | 110<br>111                                      | 1 : 128<br>1 : 256                                                                                                   | 1 : 64<br>1 : 128                                    |                         |     |  |  |  |  |  |  |

|         |                                                 | 1.200                                                                                                                | 1.120                                                |                         |     |  |  |  |  |  |  |

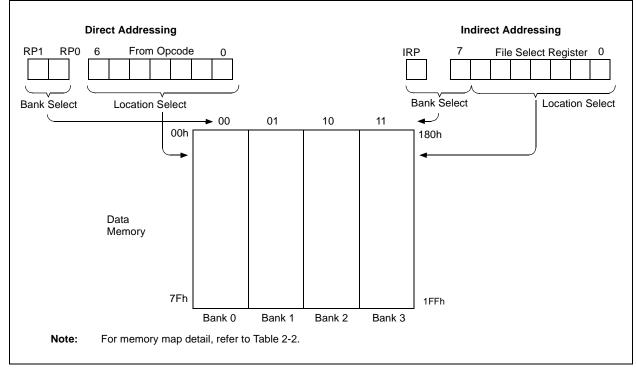

### 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no operation (although Status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit of the STATUS register, as shown in Figure 2-3.

A simple program to clear RAM location 020h-02Fh using indirect addressing is shown in Example 2-2.

### EXAMPLE 2-2: INDIRECT ADDRESSING

|      | MOVLW<br>MOVWF<br>BANKISEL | 020h<br>FSR<br>020h | ;initialize pointer<br>;to RAM |

|------|----------------------------|---------------------|--------------------------------|

| NEXT | CLRF                       | INDF                | clear INDF register;           |

|      | INCF                       | FSR                 | ;inc pointer                   |

|      | BTFSS                      | FSR,4               | ;all done?                     |

|      | GOTO                       | NEXT                | ;no clear next                 |

| CONT | INUE                       |                     | ;yes continue                  |

|      |                            |                     |                                |

### FIGURE 2-3: DIRECT/INDIRECT ADDRESSING

### 4.5.5 PIR2 REGISTER

The PIR2 register contains the interrupt flag bits, as shown in Register 4-5.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### REGISTER 4-5: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

| R/W-0   | R/W-0  | R/W-0  | R/W-0  | U-0 | U-0 | U-0 | R/W-0  |

|---------|--------|--------|--------|-----|-----|-----|--------|

| TMR3GIF | TMR3IF | TMRBIF | TMRAIF | —   | —   |     | CCP2IF |

| bit 7   |        |        |        |     |     |     | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | TMR3GIF: Timer3 Gate Interrupt Flag bit                                          |

|---------|----------------------------------------------------------------------------------|

|         |                                                                                  |

|         | 1 = Timer3 gate is inactive<br>0 = Timer3 gate is active                         |

| h:+ C   |                                                                                  |

| bit 6   | TMR3IF: Timer3 Overflow Interrupt Flag bit                                       |

|         | 1 = Timer3 register overflowed (must be cleared in software)                     |

|         | 0 = Timer3 register did not overflow                                             |

| bit 5   | TMRBIF: TimerB Overflow Interrupt Flag bit                                       |

|         | <ol> <li>TimerB register has overflowed (must be cleared in software)</li> </ol> |

|         | 0 = TimerB register did not overflow                                             |

| bit 4   | TMRAIF: TimerA Overflow Interrupt Flag bit                                       |

|         | <ol> <li>TimerA register has overflowed (must be cleared in software)</li> </ol> |

|         | 0 = TimerA register did not overflow                                             |

| bit 3-1 | Unimplemented: Read as '0'                                                       |

| bit 0   | CCP2IF: CCP2 Interrupt Flag bit                                                  |

|         | Capture Mode                                                                     |

|         | 1 = A Timer1 register capture occurred (must be cleared in software)             |

|         | 0 = No Timer1 register capture occurred                                          |

|         | Compare Mode                                                                     |

|         | 1 = A Timer1 register compare match occurred (must be cleared in software)       |

|         | 0 = No Timer1 register compare match occurred                                    |

|         | <u>PWM Mode</u>                                                                  |

|         | Unused in this mode                                                              |

|         |                                                                                  |

## 6.3.4.4 RB3/AN9/CPSB11/CCP2

These pins are configurable to function as one of the following:

- General purpose I/O

- Analog input for the ADC

- Capacitive sensing input

- Capture 2 input, Compare 2 output, and PWM2 output

Note: CCP2 pin location may be selected as RB3 or RC1.

## 6.3.4.5 RB4/AN11/CPSB12

These pins are configurable to function as one of the following:

- General purpose I/O

- Analog input for the ADC

- Capacitive sensing input

## 6.3.4.6 RB5/AN13/CPSB13/T1G/T3CKI

These pins are configurable to function as one of the following:

- General purpose I/O

- Analog input for the ADC

- · Capacitive sensing input

- Timer1 gate input

- Timer3 clock input

## 6.3.4.7 RB6/ICSPCLK/CPSB14

These pins are configurable to function as one of the following:

- General purpose I/O

- In-Circuit Serial Programming clock

- Capacitive sensing input

## 6.3.4.8 RB7/ICSPDAT/CPSB15

These pins are configurable to function as one of the following:

- General purpose I/O

- In-Circuit Serial Programming data

- Capacitive sensing input

| ABLE 6-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB |         |                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                              |                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|------------------------------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit 7                                                | Bit 6   | Bit 5                                                                                                                                                                                                                                                                                                                                                                                                                  | Bit 4                                                                                                                                                        | Bit 3                                                                                                                                                                                                                   | Bit 2                                                                                                                                                                                                                                                                                                              | Bit 1                                                                                                                                                                                                                                                                                                                                   | Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                            | Value on<br>POR, BOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Value on all<br>other<br>Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| —                                                    | —       | CHS3                                                                                                                                                                                                                                                                                                                                                                                                                   | CHS2                                                                                                                                                         | CHS1                                                                                                                                                                                                                    | CHS0                                                                                                                                                                                                                                                                                                               | GO/DONE                                                                                                                                                                                                                                                                                                                                 | ADON                                                                                                                                                                                                                                                                                                                                                                                                                             | 00 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 00 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| ANSB7                                                | ANSB6   | ANSB5                                                                                                                                                                                                                                                                                                                                                                                                                  | ANSB4                                                                                                                                                        | ANSB3                                                                                                                                                                                                                   | ANSB2                                                                                                                                                                                                                                                                                                              | ANSB1                                                                                                                                                                                                                                                                                                                                   | ANSB0                                                                                                                                                                                                                                                                                                                                                                                                                            | 1111 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1111 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| _                                                    | _       | _                                                                                                                                                                                                                                                                                                                                                                                                                      | _                                                                                                                                                            | _                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                  | SSSEL                                                                                                                                                                                                                                                                                                                                   | CCP2SEL                                                                                                                                                                                                                                                                                                                                                                                                                          | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| _                                                    | _       | DC2B1                                                                                                                                                                                                                                                                                                                                                                                                                  | DC2B0                                                                                                                                                        | CCP2M3                                                                                                                                                                                                                  | CCP2M2                                                                                                                                                                                                                                                                                                             | CCP2M1                                                                                                                                                                                                                                                                                                                                  | CCP2M0                                                                                                                                                                                                                                                                                                                                                                                                                           | 00 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 00 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| CPSBON                                               | CPSBRM  | _                                                                                                                                                                                                                                                                                                                                                                                                                      | _                                                                                                                                                            | CPSBRNG1                                                                                                                                                                                                                | CPSBRNG0                                                                                                                                                                                                                                                                                                           | CPSBOUT                                                                                                                                                                                                                                                                                                                                 | TBXCS                                                                                                                                                                                                                                                                                                                                                                                                                            | 00 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 00 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| _                                                    | _       | _                                                                                                                                                                                                                                                                                                                                                                                                                      | _                                                                                                                                                            | CPSBCH3                                                                                                                                                                                                                 | CPSBCH2                                                                                                                                                                                                                                                                                                            | CPSBCH1                                                                                                                                                                                                                                                                                                                                 | CPSBCH0                                                                                                                                                                                                                                                                                                                                                                                                                          | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| GIE                                                  | PEIE    | TMR0IE                                                                                                                                                                                                                                                                                                                                                                                                                 | INTE                                                                                                                                                         | RBIE                                                                                                                                                                                                                    | TMR0IF                                                                                                                                                                                                                                                                                                             | INTF                                                                                                                                                                                                                                                                                                                                    | RBIF                                                                                                                                                                                                                                                                                                                                                                                                                             | 0000 000x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0000 000x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| IOCB7                                                | IOCB6   | IOCB5                                                                                                                                                                                                                                                                                                                                                                                                                  | IOCB4                                                                                                                                                        | IOCB3                                                                                                                                                                                                                   | IOCB2                                                                                                                                                                                                                                                                                                              | IOCB1                                                                                                                                                                                                                                                                                                                                   | IOCB0                                                                                                                                                                                                                                                                                                                                                                                                                            | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| RBPU                                                 | INTEDG  | TMR0CS                                                                                                                                                                                                                                                                                                                                                                                                                 | TMR0SE                                                                                                                                                       | PSA                                                                                                                                                                                                                     | PS2                                                                                                                                                                                                                                                                                                                | PS1                                                                                                                                                                                                                                                                                                                                     | PS0                                                                                                                                                                                                                                                                                                                                                                                                                              | 1111 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1111 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| RB7                                                  | RB6     | RB5                                                                                                                                                                                                                                                                                                                                                                                                                    | RB4                                                                                                                                                          | RB3                                                                                                                                                                                                                     | RB2                                                                                                                                                                                                                                                                                                                | RB1                                                                                                                                                                                                                                                                                                                                     | RB0                                                                                                                                                                                                                                                                                                                                                                                                                              | xxxx xxxx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | xxxx xxxx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| TMR3CS1                                              | TMR3CS0 | T3CKPS1                                                                                                                                                                                                                                                                                                                                                                                                                | T3CKPS0                                                                                                                                                      | —                                                                                                                                                                                                                       | T3SYNC                                                                                                                                                                                                                                                                                                             | —                                                                                                                                                                                                                                                                                                                                       | TMR3ON                                                                                                                                                                                                                                                                                                                                                                                                                           | 0000 -0-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0000 -0-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| TMR1GE                                               | T1GPOL  | T1GTM                                                                                                                                                                                                                                                                                                                                                                                                                  | T1GSPM                                                                                                                                                       | T <u>1GGO</u> /<br>DONE                                                                                                                                                                                                 | T1GVAL                                                                                                                                                                                                                                                                                                             | T1GSS1                                                                                                                                                                                                                                                                                                                                  | T1GSS0                                                                                                                                                                                                                                                                                                                                                                                                                           | 00x0 0x00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | uuuu uxuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| TRISB7                                               | TRISB6  | TRISB5                                                                                                                                                                                                                                                                                                                                                                                                                 | TRISB4                                                                                                                                                       | TRISB3                                                                                                                                                                                                                  | TRISB2                                                                                                                                                                                                                                                                                                             | TRISB1                                                                                                                                                                                                                                                                                                                                  | TRISB0                                                                                                                                                                                                                                                                                                                                                                                                                           | 1111 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1111 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| WPUB7                                                | WPUB6   | WPUB5                                                                                                                                                                                                                                                                                                                                                                                                                  | WPUB4                                                                                                                                                        | WPUB3                                                                                                                                                                                                                   | WPUB2                                                                                                                                                                                                                                                                                                              | WPUB1                                                                                                                                                                                                                                                                                                                                   | WPUB0                                                                                                                                                                                                                                                                                                                                                                                                                            | 1111 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1111 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|                                                      | Bit 7   | Bit 7         Bit 6           —         —           ANSB7         ANSB6           —         —           ANSB7         ANSB6           —         —           CPS         —           —         —           GIE         PEIE           IOCB7         IOCB6           RB7U         INTEDG           RB7U         INTEDG           TMR3CS1         TMR3CS0           TMR1GE         TIGPOL           TRISB7         TRISB6 | Bit 7Bit 6Bit 5CHS3ANSB7ANSB6ANSB5DC2B1CPSBONCPSBRMCPSBONCPSBRMGIEPEIETMR0IEIOCB7IOCB6IOCB5RB7RB6RB5TMR3CS1TMR3CS0T3CKPS1TMR1GET1GPOLT1GTMTRISB7TRISB6TRISB5 | Bit 7Bit 6Bit 5Bit 4CHS3CHS2ANSB7ANSB6ANSB5ANSB4CHS3CHS2ANSB7ANSB6ANSB5ANSB4DC2B1DC2B0CPSB0NCPSBRMGIEPEIETMR0IEINTEIOCB7IOCB6IOCB5IOCB4RB7RB6RB5RB4TMR3CS1TMR3CS0T3CKPS1TMR1GETIGPOLTIGTMTIGSPMTRISB7TRISB6TRISB5TRISB4 | Bit 7Bit 6Bit 5Bit 4Bit 3CHS3CHS2CHS1ANSB7ANSB6ANSB5ANSB4ANSB3DC2B1DC2B0CCP2M3CPSB0NCPSBRMCPSBRN61CPSBRN61CPSBRN61CPSBRN61CPSBCH3GIEPEIETMR0IEINTEIOCB7IOCB6IOCB5IOCB4IOCB3IOCB7IOCB6TMR0CSTMR0SEPSARB7RB6RB5RB4RB3TMR3CS1TMR3CS0T3CKPS1T3CKPS0TMR1GET1GPOLT1GTMT1GSPMT1GG0/<br>DONETRISB7TRISB6TRISB5TRISB4TRISB3 | Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2CHS3CHS2CHS1CHS0ANSB7ANSB6ANSB5ANSB4ANSB3ANSB2DC2B1DC2B0CCP2M3CCP2M2CPSB0NCPSBRMCPSBRNG1CPSBRNG0CPSBCH3CCP2M2GIEPEIETMR0IEINTERBIETMR0IFIOCB7IOCB6IOCB5IOCB4IOCB3IOCB2RB7RB6RB5RB4RB3RB2TMR3CS1TMR3CS0T3CKPS1T3CKPS0T3SYNCTMR1GET1GPOLT1GTMT1GSPMT1GGO/<br>DONET1GVALTRISB7TRISB6TRISB5TRISB4TRISB3TRISB2 | Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1CHS3CHS2CHS1CHS0GO/DONEANSB7ANSB6ANSB5ANSB4ANSB3ANSB2ANSB1SSELDC2B1DC2B0CCP2M3CCP2M2CCP2M1CPSBONCPSBRMCPSBRNG1CPSBRNG0CPSB0UTCPSBRNG1CPSBRNG0CPSB0UTCPSBCH3CPSBCH2CPSBCH1GIEPEIETMR0IEINTERBIETMR0IFINTFIOCB7IOCB6IOCB5IOCB4IOCB3IOCB2IOCB1RB7RB6RB5RB4RB3RB2RB1TMR3CS1TMR3CS0T3CKPS1T3CKPS0T3SYNCTMR1GET1GPOLT1GTMT1GSPMT1GG0/<br>DONET1GVALT1GSS1TRISB7TRISB6TRISB5TRISB4TRISB3TRISB2TRISB1 | Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0CHS3CHS2CHS1CHS0GO/DONEADONANSB7ANSB6ANSB5ANSB4ANSB3ANSB2ANSB1ANSB0SSELCCP2SELDC2B1DC2B0CCP2M3CCP2M2CCP2M1CCP2M0CPSBONCPSBRMCPSBRNG1CPSBRNG0CPSBOUTTBXCSCPSBCH3CPSBCH2CPSBCH1CPSBCH0GIEPEIETMR0IEINTERBIETMR0IFINTFRBIFIOCB7IOCB6IOCB5IOCB4IOCB3IOCB2IOCB1IOCB0RBFUINTEDGTMR0CSTMR0SEPSAPS2PS1PS0RB7RB6RB5RB4RB3RB2RB1RB0TMR3CS1TMR3CS0T3CKPS1T3CKP30T3SYNCTMR3ONTMR1GETIGPOLT1GTMT1GSPMT1GG0/<br>DONET1GVALT1GSS1T1GSS0TRISB7TRISB6TRISB5TRISB4TRISB3TRISB2TRISB1TRISB0 | Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0         Value on<br>POR, BOR             CHS3         CHS2         CHS1         CHS0         GO/DONE         ADON        00 0000           ANSB7         ANSB6         ANSB5         ANSB4         ANSB3         ANSB2         ANSB1         ANSB0         1111 1111               SSEL         CCP2SEL         00         0000               SSEL         CCP2SEL          -00         0000               SSEL         CCP2M2         CCP2M1         CCP2M0        00         0000              CPSBRNG1         CPSBRNG0         CPSBOUT         TBXCS         00<0000 |  |  |

# TABLE 6-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTB.

### 6.5.2.6 RD5/CPSA13

These pins are configurable to function as one of the following:

- General purpose I/O

- · Capacitive sensing input

### 6.5.2.7 RD6/CPSA14

These pins are configurable to function as one of the following:

- General purpose I/O

- Capacitive sensing input

### 6.5.2.8 RD7/CPSA15

These pins are configurable to function as one of the following:

- General purpose I/O

- · Capacitive sensing input

| IADLE 0-4 | ABLE 6-4: SUMMART OF REGISTERS ASSOCIATED WITH FORTD |        |        |        |                         |          |         |         |                      |                                 |  |  |

|-----------|------------------------------------------------------|--------|--------|--------|-------------------------|----------|---------|---------|----------------------|---------------------------------|--|--|

| Name      | Bit 7                                                | Bit 6  | Bit 5  | Bit 4  | Bit 3                   | Bit 2    | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |  |  |

| ANSELD    | ANSD7                                                | ANSD6  | ANSD5  | ANSD4  | ANSD3                   | ANSD2    | ANSD1   | ANSD0   | 1111 1111            | 1111 1111                       |  |  |

| CPSACON0  | CPSAON                                               | CPSARM | _      | _      | CPSARNG1                | CPSARNG0 | CPSAOUT | TAXCS   | 00 0000              | 00 0000                         |  |  |