Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| B-4-9-                     |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Details                    |                                                                            |

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 363 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 14x8b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf707t-i-pt |

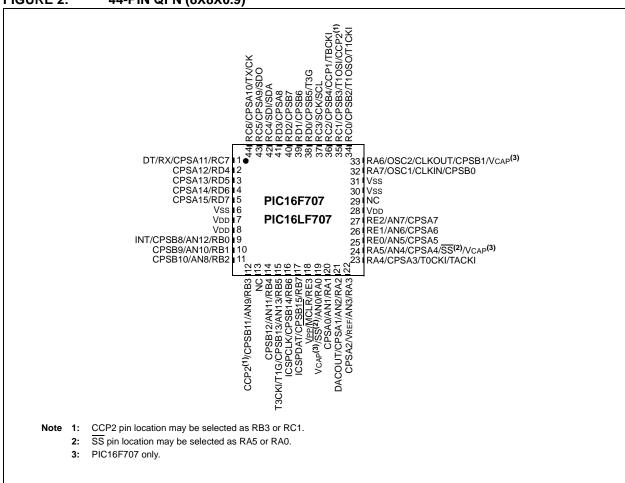

FIGURE 2: 44-PIN QFN (8X8X0.9)

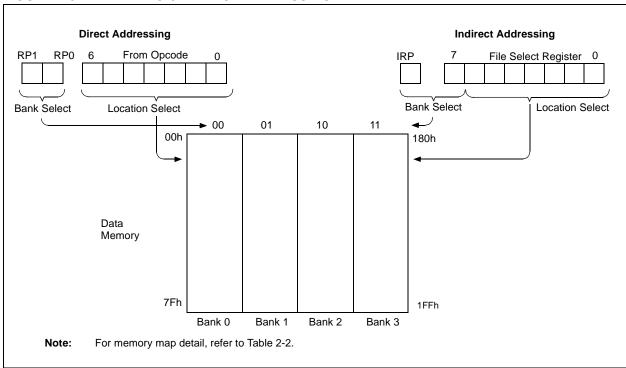

## 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no operation (although Status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit of the STATUS register, as shown in Figure 2-3.

A simple program to clear RAM location 020h-02Fh using indirect addressing is shown in Example 2-2.

### **EXAMPLE 2-2: INDIRECT ADDRESSING**

|      | MOVLW    | 020h  | ;initialize pointer  |

|------|----------|-------|----------------------|

|      | MOVWF    | FSR   | ;to RAM              |

|      | BANKISEL | 020h  |                      |

| NEXT | CLRF     | INDF  | clear INDF register; |

|      | INCF     | FSR   | ;inc pointer         |

|      | BTFSS    | FSR,4 | ;all done?           |

|      | GOTO     | NEXT  | ;no clear next       |

| CONT | INUE     |       | yes continue;        |

|      |          |       |                      |

|      |          |       |                      |

FIGURE 2-3: DIRECT/INDIRECT ADDRESSING

#### **6.0 I/O PORTS**

There are thirty-five general purpose I/O pins available. Depending on which peripherals are enabled, some or all of the pins may not be available as general purpose I/O. In general, when a peripheral is enabled, the associated pin may not be used as a general purpose I/O pin.

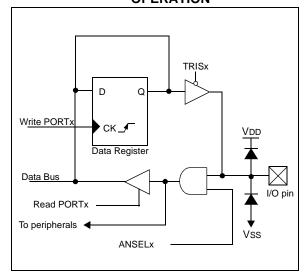

Each port has two registers for its operation. These registers are:

- TRISx registers (data direction register)

- PORTx registers (port read/write register)

Ports with analog functions also have an ANSELx register which can disable the digital input and save power. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 6-1.

## FIGURE 6-1: GENERIC I/O PORT OPERATION

#### 6.1 Alternate Pin Function

The Alternate Pin Function Control (APFCON) register is used to steer specific peripheral input and output functions between different pins. The APFCON register is shown in Register 6-1. For this device family, the following functions can be moved between different pins.

- SS (Slave Select)

- CCP2

#### REGISTER 6-1: APFCON: ALTERNATE PIN FUNCTION CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0   |

|-------|-----|-----|-----|-----|-----|-------|---------|

| _     | _   | _   | _   | _   | _   | SSSEL | CCP2SEL |

| bit 7 |     |     |     |     |     |       | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-2 **Unimplemented:** Read as '0'.

bit 1 SSSEL: SS Input Pin Selection bit

$0 = \overline{SS} \text{ function is on RA5/AN4/CPS7/\overline{SS}/VCAP}$   $1 = \overline{SS} \text{ function is on RA0/AN0/\overline{SS}/VCAP}$

bit 0 CCP2SEL: CCP2 Input/Output Pin Selection bit

0 = CCP2 function is on RC1/T1OSI/CCP2

1 = CCP2 function is on RB3/CCP2

## 6.6.2.4 RE3/MCLR/VPP

These pins are configurable to function as one of the following:

- General purpose input

- Master Clear Reset with weak pull-up

- Programming voltage reference input

### TABLE 6-5: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

| Name     | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3                 | Bit 2    | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|----------|--------|--------|-------|-------|-----------------------|----------|---------|---------|----------------------|---------------------------------|

| ADCON0   | _      | _      | CHS3  | CHS2  | CHS1                  | CHS0     | GO/DONE | ADON    | 00 0000              | 00 0000                         |

| ANSELE   | _      | _      | _     | _     | _                     | ANSE2    | ANSE1   | ANSE0   | 111                  | 111                             |

| CPSACON0 | CPSAON | CPSARM | _     | _     | CPSARNG1              | CPSARNG0 | CPSAOUT | TAXCS   | 00 0000              | 00 0000                         |

| CPSACON1 | _      | _      | _     | _     | CPSACH3               | CPSACH2  | CPSACH1 | CPSACH0 | 0000                 | 0000                            |

| PORTE    | _      | _      | _     | _     | RE3                   | RE2      | RE1     | RE0     | xxxx                 | xxxx                            |

| TRISE    | _      | _      | _     | _     | TRISE3 <sup>(1)</sup> | TRISE2   | TRISE1  | TRISE0  | 1111                 | 1111                            |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTE.

Note 1: This bit is always '1' as RE3 is input-only.

### 9.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- · Port configuration

- · Channel selection

- · ADC voltage reference selection

- · ADC conversion clock source

- · Interrupt control

- · Results formatting

### 9.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. Refer to **Section 6.0** "I/O Ports" for more information.

**Note:** Analog voltages on any pin that is defined as a digital input may cause the input buffer to conduct excess current.

#### 9.1.2 CHANNEL SELECTION

The CHS bits of the ADCON0 register determine which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion. Refer to **Section 9.2** "**ADC Operation**" for more information.

#### 9.1.3 ADC VOLTAGE REFERENCE

The ADREF bits of the ADCON1 register provides control of the positive voltage reference. The positive voltage reference can be either VDD, an external voltage source or the internal Fixed Voltage Reference. The negative voltage reference is always connected to the ground reference. See **Section 10.0 "Fixed Voltage Reference"** for more details on the Fixed Voltage Reference.

#### 9.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ADCON1 register. There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- · FRC (dedicated internal oscillator)

The time to complete one bit conversion is defined as TAD. One full 8-bit conversion requires 10 TAD periods as shown in Figure 9-2.

For correct conversion, the appropriate TAD specification must be met. Refer to the A/D conversion requirements in **Section 25.0** "**Electrical Specifications**" for more information. Table 9-1 gives examples of appropriate ADC clock selections.

Note: Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

TABLE 9-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

| ADC Clock                  | Period (TAD) |                             | Device Frequency (Fosc)     |                             |                             |                             |  |  |  |  |  |

|----------------------------|--------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|--|--|--|--|--|

| ADC Clock Source ADCS<2:0> |              | 20 MHz 16 MHz               |                             | 8 MHz                       | 4 MHz                       | 1 MHz                       |  |  |  |  |  |

| Fosc/2                     | 000          | 100 ns <sup>(2)</sup>       | 125 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 2.0 μs                      |  |  |  |  |  |

| Fosc/4                     | 100          | 200 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 1.0 μs                      | 4.0 μs                      |  |  |  |  |  |

| Fosc/8                     | 001          | 400 ns <sup>(2)</sup>       | 0.5 μs <sup>(2)</sup>       | 1.0 μs                      | 2.0 μs                      | 8.0 μs <sup>(3)</sup>       |  |  |  |  |  |

| Fosc/16                    | 101          | 800 ns                      | 1.0 μs                      | 2.0 μs                      | 4.0 μs                      | 16.0 μs <sup>(3)</sup>      |  |  |  |  |  |

| Fosc/32                    | 010          | 1.6 μs                      | 2.0 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 32.0 μs <sup>(3)</sup>      |  |  |  |  |  |

| Fosc/64                    | 110          | 3.2 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 16.0 μs <sup>(3)</sup>      | 64.0 μs <sup>(3)</sup>      |  |  |  |  |  |

| FRC                        | x11          | 1.0-6.0 μs <sup>(1,4)</sup> |  |  |  |  |  |

**Legend:** Shaded cells are outside of recommended range.

Note 1: The FRC source has a typical TAD time of 1.6  $\mu s$  for VDD.

- 2: These values violate the minimum required TAD time.

- 3: For faster conversion times, the selection of another clock source is recommended.

- **4:** When the device frequency is greater than 1 MHz, the FRC clock source is only recommended if the conversion will be performed during Sleep.

# 13.0 TIMER1/3 MODULES WITH GATE CONTROL

The Timer1 and Timer3 modules are 16-bit timers/counters with the following features:

- 16-bit timer/counter register pair (TMRxH:TMRxL)

- Programmable internal or external clock source

- 3-bit prescaler

- Dedicated LP oscillator circuit (Timer1 only)

- Synchronous or asynchronous operation

- Multiple Timer1/3 gate (count enable) sources

- · Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- Time base for the Capture/Compare function (Timer1 only)

- Special Event Trigger with CCP (Timer1 only)

- Selectable Gate Source Polarity

- · Gate Toggle mode

- Gate Single-pulse mode

- Gate Value Status

- · Gate Event Interrupt

Figure 13-1 is a block diagram of the Timer1/3 modules.

#### REGISTER 14-1: TxCON: TIMERA/TIMERB CONTROL REGISTER

| R/W-0/0 | R/W-0/0 U-0 R/W- |        | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|------------------|--------|---------|---------|---------|---------|---------|

| TMRxON  | _                | TMRxCS | TMRxSE  | TMRxPSA | TMRxPS2 | TMRxPS1 | TMRxPS0 |

| bit 7   |                  |        |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 TMRxON: TimerA/TimerB On/Off Control bit

1 = Timerx is enabled 0 = Timerx is disabled

bit 6 **Unimplemented:** Read as '0'

bit 5 TMRxCS: TMRx Clock Source Select bit

1 = Transition on TxCKI pin or CPSxOSC signal 0 = Internal instruction cycle clock (Fosc/4)

bit 4 TMRxSE: TMRx Source Edge Select bit

1 = Increment on high-to-low transition on TxCKI pin

0 = Increment on low-to-high transition on TxCKI pin

bit 3 TMRxPSA: Prescaler Assignment bit

1 = Prescaler is disabled. Timer clock input bypasses prescaler.

0 =Prescaler is enabled. Timer clock input comes from the prescaler output.

bit 2-0 TMRxPS<2:0>: Prescaler Rate Select bits

| BIT VALUE | TMRx RATE |

|-----------|-----------|

| 000       | 1:2       |

| 001       | 1:4       |

| 010       | 1:8       |

| 011       | 1:16      |

| 100       | 1:32      |

| 101       | 1:64      |

| 110       | 1:128     |

| 111       | 1:256     |

#### TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH TIMERA/B

| Name     | Bit 7                  | Bit 6  | Bit 5  | Bit 4     | Bit 3          | Bit 2    | Bit 1   | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|----------|------------------------|--------|--------|-----------|----------------|----------|---------|--------|----------------------|---------------------------------|

| CPSACON0 | CPSAON                 | CPSARM | _      | _         | CPSARNG1       | CPSARNG0 | CPSAOUT | TAXCS  | 00 0000              | 00 0000                         |

| CPSBCON0 | CPSBON                 | CPSBRM | ı      | _         | CPSBRNG1       | CPSBRNG0 | CPSBOUT | TBXCS  | 00 0000              | 00 0000                         |

| PIE2     | TMR3GIE                | TMR3IE | TMRBIE | TMRAIE    | _              | I        | _       | CCP2IE | 00000                | 00000                           |

| PIR2     | TMR3GIF                | TMR3IF | TMRBIF | TMRAIF    | _              | I        | _       | CCP2IF | 00000                | 00000                           |

| TACON    | TMRAON                 | _      | TACS   | TASE      | TAPSA          | TAPS2    | TAPS1   | TAPS0  | 0-00 0000            | 0-00 0000                       |

| TBCON    | TMRBON                 | _      | TBCS   | TBSE      | TBPSA          | TBPS2    | TBPS1   | TBPS0  | 0-00 0000            | 0-00 0000                       |

| TMRA     |                        |        |        | TimerA Mo | odule Register |          |         |        | 0000 0000            | 0000 0000                       |

| TMRB     | TimerB Module Register |        |        |           |                |          |         |        | 0000 0000            | 0000 0000                       |

| TRISA    | TRISA7                 | TRISA6 | TRISA5 | TRISA4    | TRISA3         | TRISA2   | TRISA1  | TRISA0 | 1111 1111            | 1111 1111                       |

| TRISC    | TRISC7                 | TRISC6 | TRISC5 | TRISC4    | TRISC3         | TRISC2   | TRISC1  | TRISC0 | 1111 1111            | 1111 1111                       |

**Legend:** — = Unimplemented locations, read as '0'. Shaded cells are not used by the TimerA/B modules.

#### REGISTER 15-1: T2CON: TIMER2 CONTROL REGISTER

| U-0   | R/W-0   | R/W-0           | R/W-0 | R/W-0          | R/W-0 | R/W-0   | R/W-0   |

|-------|---------|-----------------|-------|----------------|-------|---------|---------|

| _     | TOUTPS3 | TOUTPS2 TOUTPS1 |       | TOUTPS0 TMR2ON |       | T2CKPS1 | T2CKPS0 |

| bit 7 |         |                 |       |                |       |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 Unimplemented: Read as '0'

bit 6-3 TOUTPS<3:0>: Timer2 Output Postscaler Select bits

0000 = 1:1 Postscaler

0001 = 1:2 Postscaler

0010 = 1:3 Postscaler

0011 = 1:4 Postscaler

0100 = 1:5 Postscaler

0101 = 1:6 Postscaler

0110 = 1:7 Postscaler

0111 = 1:8 Postscaler

1000 = 1:9 Postscaler

1001 = 1:10 Postscaler 1010 = 1:11 Postscaler

1010 = 1.111 03130010

1011 = 1:12 Postscaler

1100 = 1:13 Postscaler 1101 = 1:14 Postscaler

1110 = 1:15 Postscaler

1110 = 1.15 Posiscale

1111 = 1:16 Postscaler

bit 2 TMR2ON: Timer2 On bit

1 = Timer2 is on

0 = Timer2 is off

bit 1-0 T2CKPS<1:0>: Timer2 Clock Prescale Select bits

00 = Prescaler is 1

01 = Prescaler is 4

1x = Prescaler is 16

#### TABLE 15-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2

| Name   | Bit 7                                        | Bit 6   | Bit 5   | Bit 4        | Bit 3        | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------------------------------------------|---------|---------|--------------|--------------|--------|---------|---------|----------------------|---------------------------------|

| INTCON | GIE                                          | PEIE    | TMR0IE  | INTE         | RBIE         | TMR0IF | INTF    | RBIF    | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE                                      | ADIE    | RCIE    | TXIE         | SSPIE        | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF                                      | ADIF    | RCIF    | TXIF         | SSPIF        | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                       |

| PR2    |                                              |         | Т       | imer2 Module | Period Regis | ter    |         |         | 1111 1111            | 1111 1111                       |

| TMR2   | Holding Register for the 8-bit TMR2 Register |         |         |              |              |        |         |         | 0000 0000            | 0000 0000                       |

| T2CON  | _                                            | TOUTPS3 | TOUTPS2 | TOUTPS1      | TOUTPS0      | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for Timer2 module.

TABLE 19-1: SUMMARY OF REGISTERS ASSOCIATED WITH SPI OPERATION

| Name    | Bit 7   | Bit 6   | Bit 5        | Bit 4          | Bit 3          | Bit 2       | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on all other Resets |

|---------|---------|---------|--------------|----------------|----------------|-------------|---------|---------|----------------------|---------------------------|

| ANSELA  | ANSA7   | ANSA6   | ANSA5        | ANSA4          | ANSA3          | ANSA2       | ANSA1   | ANSA0   | 1111 1111            | 1111 1111                 |

| APFCON  | _       | _       | _            | _              | _              | _           | SSSEL   | CCP2SEL | 00                   | 00                        |

| INTCON  | GIE     | PEIE    | TMR0IE       | INTE           | RBIE           | TMR0IF      | INTF    | RBIF    | 0000 000x            | 0000 000x                 |

| PIE1    | TMR1GIE | ADIE    | RCIE         | TXIE           | SSPIE          | CCP1IE      | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                 |

| PIR1    | TMR1GIF | ADIF    | RCIF         | TXIF           | SSPIF          | CCP1IF      | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                 |

| PR2     |         |         |              | Timer2 Per     | iod Register   |             |         |         | 1111 1111            | 1111 1111                 |

| SSPBUF  |         | Syı     | nchronous Se | erial Port Red | ceive Buffer/1 | ransmit Reg | ister   |         | xxxx xxxx            | uuuu uuuu                 |

| SSPCON  | WCOL    | SSPOV   | SSPEN        | CKP            | SSPM3          | SSPM2       | SSPM1   | SSPM0   | 0000 0000            | 0000 0000                 |

| SSPSTAT | SMP     | CKE     | D/A          | Р              | S              | R/W         | UA      | BF      | 0000 0000            | 0000 0000                 |

| TRISA   | TRISA7  | TRISA6  | TRISA5       | TRISA4         | TRISA3         | TRISA2      | TRISA1  | TRISA0  | 1111 1111            | 1111 1111                 |

| TRISC   | TRISC7  | TRISC6  | TRISC5       | TRISC4         | TRISC3         | TRISC2      | TRISC1  | TRISC0  | 1111 1111            | 1111 1111                 |

| T2CON   | _       | TOUTPS3 | TOUTPS2      | TOUTPS1        | TOUTPS0        | TMR2ON      | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                 |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in SPI mode.

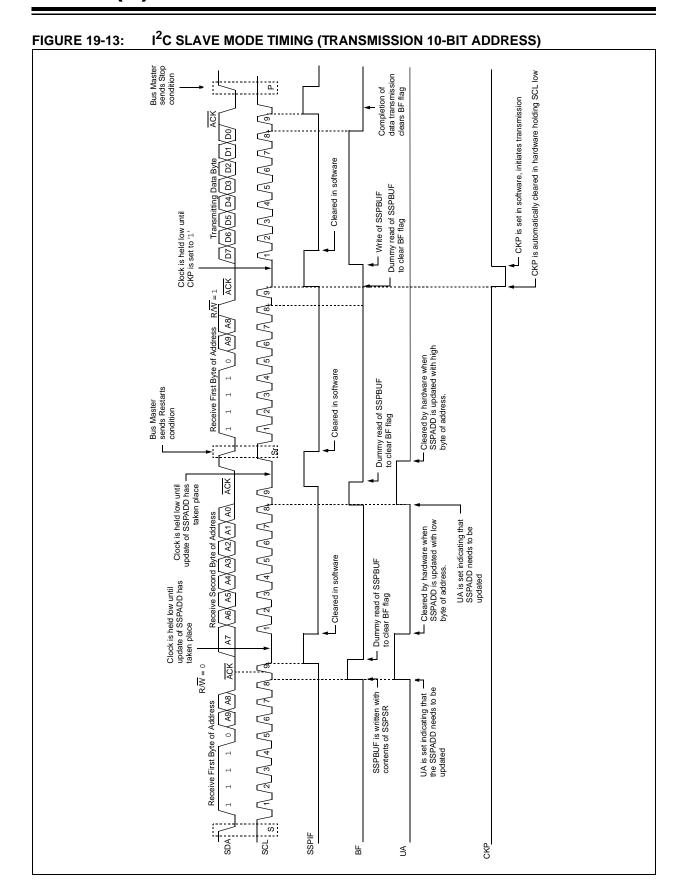

### 19.2 I<sup>2</sup>C Mode

The SSP module, in  $I^2C$  mode, implements all slave functions, except general call support. It provides interrupts on Start and Stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the  $I^2C$  Standard mode specifications:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- Start and Stop bit interrupts enabled to support firmware Master mode

- · Address masking

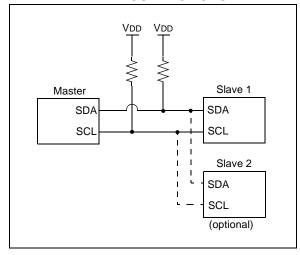

Two pins are used for data transfer; the SCL pin (clock line) and the SDA pin (data line). The user must configure the two pin's data direction bits as inputs in the appropriate TRIS register. Upon enabling  $\rm I^2C$  mode, the  $\rm I^2C$  slew rate limiters in the I/O pads are controlled by the SMP bit of the SSPSTAT register. The SSP module functions are enabled by setting the SSPEN bit of the SSPCON register.

Data is sampled on the rising edge and shifted out on the falling edge of the clock. This ensures that the SDA signal is valid during the SCL high time. The SCL clock input must have minimum high and low times for proper operation. Refer to Section 25.0 "Electrical Specifications".

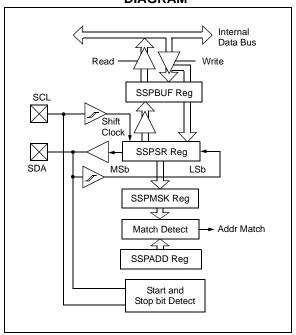

FIGURE 19-7: I<sup>2</sup>C MODE BLOCK DIAGRAM

## FIGURE 19-8: TYPICAL I<sup>2</sup>C CONNECTIONS

The SSP module has six registers for  $I^2C$  operation. They are:

- SSP Control (SSPCON) register

- · SSP Status (SSPSTAT) register

- · Serial Receive/Transmit Buffer (SSPBUF) register

- SSP Shift Register (SSPSR), not directly accessible

- SSP Address (SSPADD) register

- SSP Address Mask (SSPMSK) register

#### 19.2.1 HARDWARE SETUP

Selection of I<sup>2</sup>C mode, with the SSPEN bit of the SSPCON register set, forces the SCL and SDA pins to be open drain, provided these pins are programmed as inputs by setting the appropriate TRISC bits. The SSP module will override the input state with the output data, when required, such as for Acknowledge and slave-transmitter sequences.

**Note:** Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module.

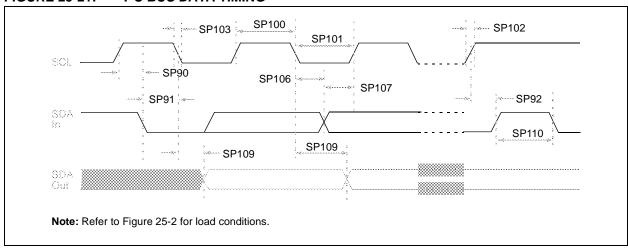

TABLE 25-12: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

| Param<br>No. | Symbol  | Characteristic  |              | Min. | Тур | Max. | Units | Conditions                   |

|--------------|---------|-----------------|--------------|------|-----|------|-------|------------------------------|

| SP90*        | Tsu:sta | Start condition | 100 kHz mode | 4700 | _   | _    | ns    | Only relevant for Repeated   |

|              |         | Setup time      | 400 kHz mode | 600  | _   | _    |       | Start condition              |

| SP91*        | THD:STA | Start condition | 100 kHz mode | 4000 | _   | _    | ns    | After this period, the first |

|              |         | Hold time       | 400 kHz mode | 600  | _   | _    |       | clock pulse is generated     |

| SP92*        | Tsu:sto | Stop condition  | 100 kHz mode | 4700 | _   | _    | ns    |                              |

|              |         | Setup time      | 400 kHz mode | 600  | _   | _    |       |                              |

| SP93         | THD:STO | Stop condition  | 100 kHz mode | 4000 | _   | _    | ns    |                              |

|              |         | Hold time       | 400 kHz mode | 600  | _   | _    |       |                              |

<sup>\*</sup> These parameters are characterized but not tested.

## FIGURE 25-21: I<sup>2</sup>C BUS DATA TIMING

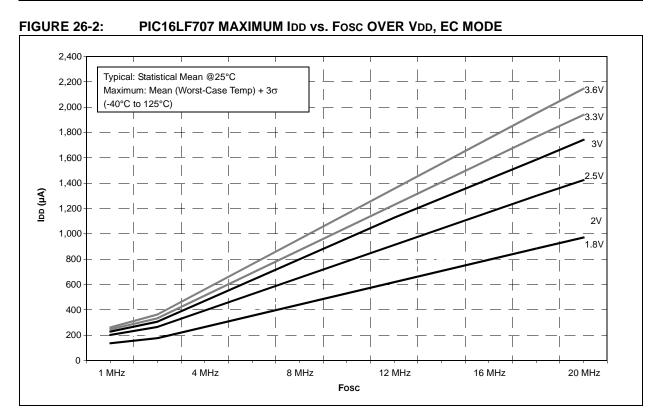

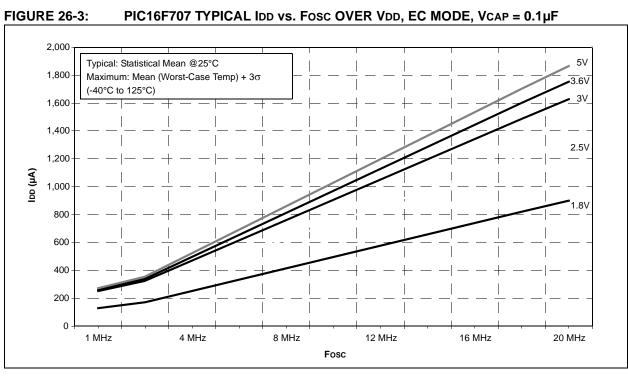

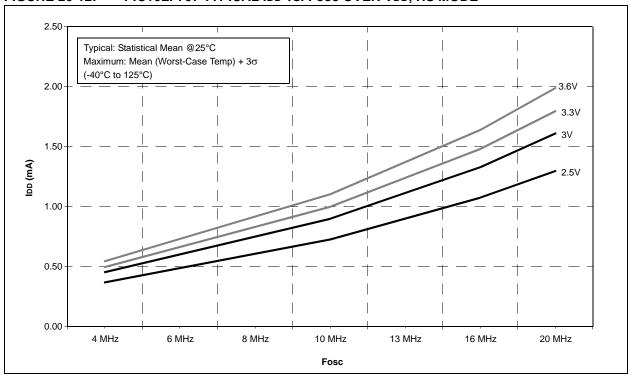

FIGURE 26-12: PIC16LF707 TYPICAL IDD vs. Fosc OVER VDD, HS MODE

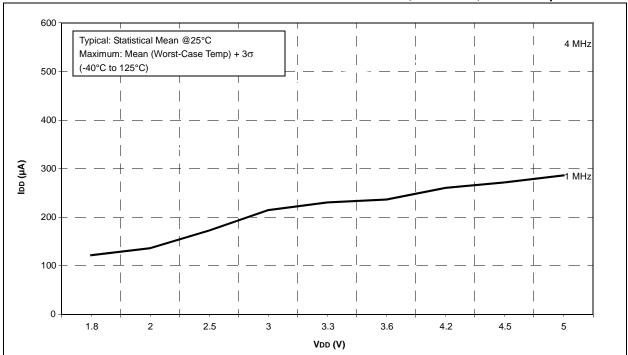

FIGURE 26-13: PIC16F707 MAXIMUM IDD vs. VDD OVER FOSC, XT MODE, VCAP = 0.1 µF

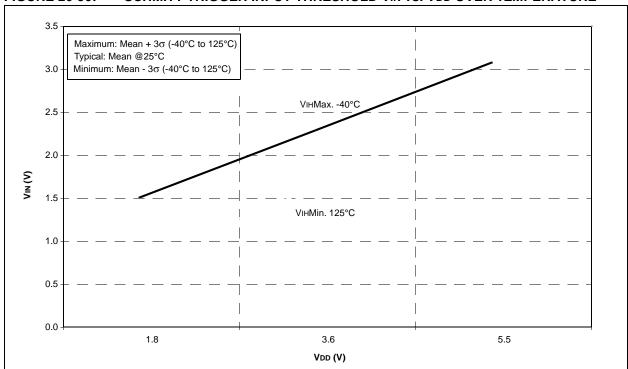

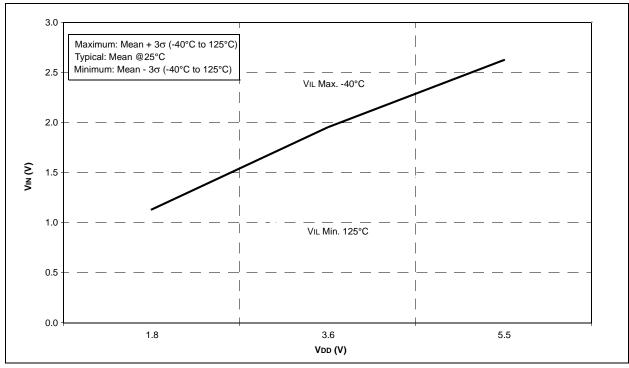

FIGURE 26-51: SCHMITT TRIGGER INPUT THRESHOLD VIN VS. VDD OVER TEMPERATURE

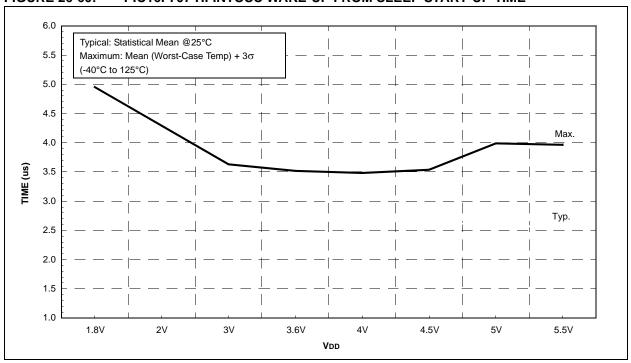

FIGURE 26-60: PIC16F707 HFINTOSC WAKE-UP FROM SLEEP START-UP TIME

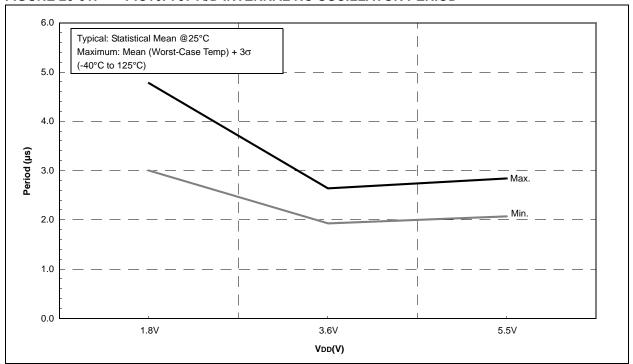

FIGURE 26-61: PIC16F707 A/D INTERNAL RC OSCILLATOR PERIOD

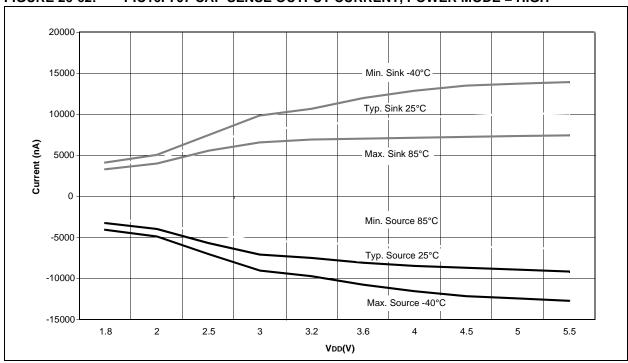

FIGURE 26-62: PIC16F707 CAP SENSE OUTPUT CURRENT, POWER MODE = HIGH

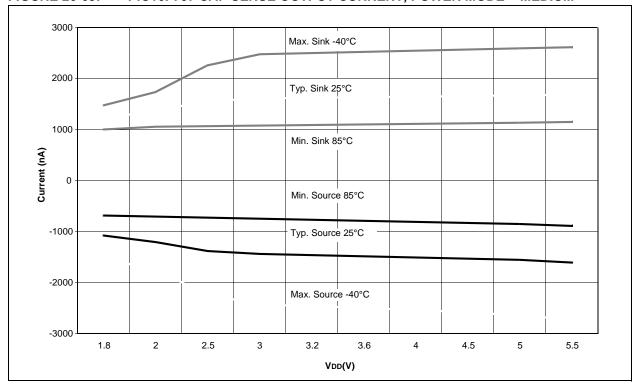

FIGURE 26-63: PIC16F707 CAP SENSE OUTPUT CURRENT, POWER MODE = MEDIUM

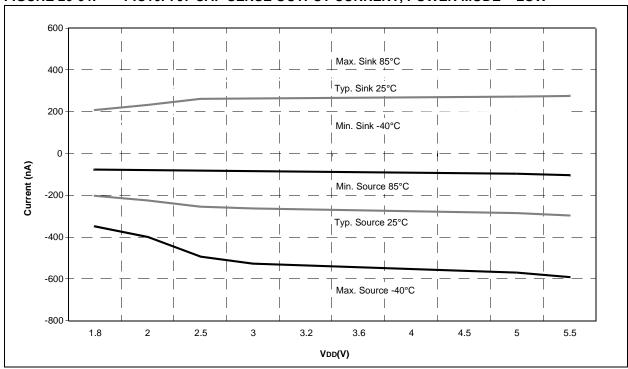

FIGURE 26-64: PIC16F707 CAP SENSE OUTPUT CURRENT, POWER MODE = LOW

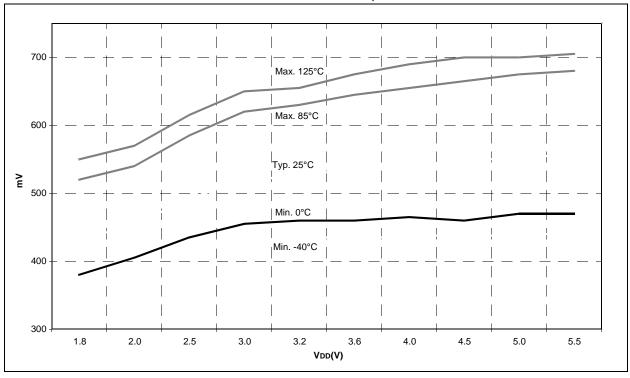

FIGURE 26-65: PIC16F707 CAP SENSOR HYSTERESIS, POWER MODE = HIGH

#### 27.0 PACKAGING INFORMATION

## 27.1 Package Marking Information

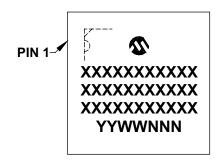

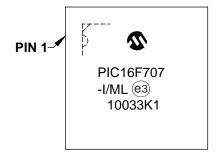

40-Lead PDIP (600 mil)

44-Lead QFN (8x8x0.9 mm)

Example

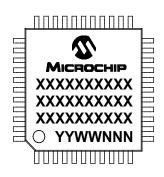

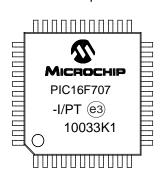

44-Lead TQFP (10x10x1 mm)

Example

Legend: XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

(e3) Pb-free JEDEC® designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC® designator ((e3))

can be found on the outer packaging for this package.

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

\* Standard PICmicro<sup>®</sup> device marking consists of Microchip part number, year code, week code and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.