Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, Motor Control PWM, PDR, POR, PVD, PWM, Temp Sensor, WDT          |

| Number of I/O              | 37                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 20K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 10x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f103cbt7 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 8 | <b>Revision history</b> |  | 5 |

|---|-------------------------|--|---|

|---|-------------------------|--|---|

# 2.3 Overview

# 2.3.1 ARM<sup>®</sup> Cortex<sup>TM</sup>-M3 core with embedded Flash and SRAM

The ARM Cortex<sup>™</sup>-M3 processor is the latest generation of ARM processors for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM Cortex<sup>™</sup>-M3 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The STM32F103xx performance line family having an embedded ARM core, is therefore compatible with all ARM tools and software.

*Figure 1* shows the general block diagram of the device family.

## 2.3.2 Embedded Flash memory

64 or 128 Kbytes of embedded Flash is available for storing programs and data.

## 2.3.3 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

## 2.3.4 Embedded SRAM

Twenty Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states.

## 2.3.5 Nested vectored interrupt controller (NVIC)

The STM32F103xx performance line embeds a nested vectored interrupt controller able to handle up to 43 maskable interrupt channels (not including the 16 interrupt lines of Cortex<sup>™</sup>-M3) and 16 priority levels.

- Closely coupled NVIC gives low-latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of *late arriving* higher priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

can also be seen as a complete general-purpose timer. The 4 independent channels can be used for

- Input capture

- Output compare

- PWM generation (edge- or center-aligned modes)

- One-pulse mode output

If configured as a general-purpose 16-bit timer, it has the same features as the TIMx timer. If configured as the 16-bit PWM generator, it has full modulation capability (0-100%).

In debug mode, the advanced-control timer counter can be frozen and the PWM outputs disabled to turn off any power switch driven by these outputs.

Many features are shared with those of the general-purpose TIM timers which have the same architecture. The advanced-control timer can therefore work together with the TIM timers via the Timer Link feature for synchronization or event chaining.

#### General-purpose timers (TIMx)

There are up to three synchronizable general-purpose timers embedded in the STM32F103xx performance line devices. These timers are based on a 16-bit auto-reload up/down counter, a 16-bit prescaler and feature 4 independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 12 input captures/output compares/PWMs on the largest packages.

The general-purpose timers can work together with the advanced-control timer via the Timer Link feature for synchronization or event chaining. Their counter can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs. They all have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

#### Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 40 kHz internal RC and as it operates independently of the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes. The counter can be frozen in debug mode.

#### Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

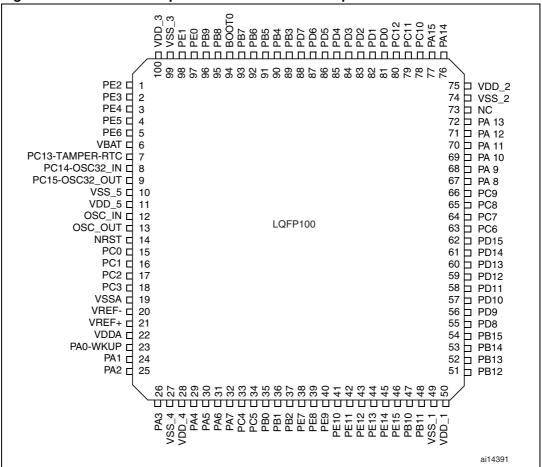

Figure 4. STM32F103xx performance line LQFP100 pinout

# Pinouts and pin description

|          |        | Pin               |        |         |          | y 51M32F103XX p                    |                     | (2)                        |                                                  | Alternate fu                                                                      | unctions |

|----------|--------|-------------------|--------|---------|----------|------------------------------------|---------------------|----------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------|----------|

| LFBGA100 | LQFP48 | TFBGA64           | LQFP64 | LQFP100 | VFQFPN36 | Pin name                           | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                                           | Remap    |

| A3       | -      |                   | -      | 1       | -        | PE2                                | I/O                 | FT                         | PE2                                              | TRACECK                                                                           |          |

| B3       | -      |                   | -      | 2       | -        | PE3                                | I/O                 | FT                         | PE3                                              | TRACED0                                                                           |          |

| C3       | -      |                   | -      | 3       | -        | PE4                                | I/O                 | FT                         | PE4                                              | TRACED1                                                                           |          |

| D3       | -      |                   | -      | 4       | -        | PE5                                | I/O                 | FT                         | PE5                                              | TRACED2                                                                           |          |

| E3       | -      |                   | -      | 5       | -        | PE6                                | I/O                 | FT                         | PE6                                              | TRACED3                                                                           |          |

| B2       | 1      | B2                | 1      | 6       | -        | V <sub>BAT</sub>                   | S                   |                            | V <sub>BAT</sub>                                 |                                                                                   |          |

| A2       | 2      | A2                | 2      | 7       | -        | PC13-TAMPER-<br>RTC <sup>(4)</sup> | I/O                 |                            | PC13 <sup>(5)</sup>                              | TAMPER-RTC                                                                        |          |

| A1       | 3      | A1                | 3      | 8       | -        | PC14-OSC32_IN <sup>(4)</sup>       | I/O                 |                            | PC14 <sup>(5)</sup>                              | OSC32_IN                                                                          |          |

| B1       | 4      | B1                | 4      | 9       | -        | PC15-<br>OSC32_OUT <sup>(4)</sup>  | I/O                 |                            | PC15 <sup>(5)</sup>                              | OSC32_OUT                                                                         |          |

| C2       | -      | -                 | -      | 10      | -        | V <sub>SS_5</sub>                  | S                   |                            | V <sub>SS_5</sub>                                |                                                                                   |          |

| D2       | -      | -                 | -      | 11      | -        | V <sub>DD_5</sub>                  | S                   |                            | $V_{DD_5}$                                       |                                                                                   |          |

| C1       | 5      | C1                | 5      | 12      | 2        | OSC_IN                             | I                   |                            | OSC_IN                                           |                                                                                   |          |

| D1       | 6      | D1                | 6      | 13      | 3        | OSC_OUT                            | 0                   |                            | OSC_OUT                                          |                                                                                   |          |

| E1       | 7      | E1                | 7      | 14      | 4        | NRST                               | I/O                 |                            | NRST                                             |                                                                                   |          |

| F1       | -      | E3                | 8      | 15      | -        | PC0                                | I/O                 |                            | PC0                                              | ADC12_IN10                                                                        |          |

| F2       | -      | E2                | 9      | 16      | -        | PC1                                | I/O                 |                            | PC1                                              | ADC12_IN11                                                                        |          |

| E2       | -      | F2                | 10     | 17      | -        | PC2                                | I/O                 |                            | PC2                                              | ADC12_IN12                                                                        |          |

| F3       | -      | _(6)              | 11     | 18      | -        | PC3                                | I/O                 |                            | PC3                                              | ADC12_IN13                                                                        |          |

| G1       | 8      | F1                | 12     | 19      | 5        | V <sub>SSA</sub>                   | S                   |                            | V <sub>SSA</sub>                                 |                                                                                   |          |

| H1       | -      | -                 | I      | 20      | -        | V <sub>REF-</sub>                  | S                   |                            | V <sub>REF-</sub>                                |                                                                                   |          |

| J1       | -      | G1 <sup>(6)</sup> | I      | 21      | -        | V <sub>REF+</sub>                  | S                   |                            | $V_{REF+}$                                       |                                                                                   |          |

| K1       | 9      | H1                | 13     | 22      | 6        | V <sub>DDA</sub>                   | S                   |                            | $V_{DDA}$                                        |                                                                                   |          |

| G2       | 10     | G2                | 14     | 23      | 7        | PA0-WKUP                           | I/O                 |                            | PA0                                              | WKUP/<br>USART2_CTS <sup>(7)</sup> /<br>ADC12_IN0/<br>TIM2_CH1_ETR <sup>(7)</sup> |          |

| H2       | 11     | H2                | 15     | 24      | 8        | PA1                                | I/O                 |                            | PA1                                              | USART2_RTS <sup>(7)</sup> /<br>ADC12_IN1/<br>TIM2_CH2 <sup>(7)</sup>              |          |

| J2       | 12     | F3                | 16     | 25      | 9        | PA2                                | I/O                 |                            | PA2                                              | USART2_TX <sup>(7)</sup> /<br>ADC12_IN2/<br>TIM2_CH3 <sup>(7)</sup>               |          |

## Table 5. Medium-density STM32F103xx pin definitions

|          |        | Pin     | IS     |         |          |                   |                     | (2)                        |                                                  | Alternate f                                                          | unctions  |

|----------|--------|---------|--------|---------|----------|-------------------|---------------------|----------------------------|--------------------------------------------------|----------------------------------------------------------------------|-----------|

| LFBGA100 | LQFP48 | TFBGA64 | LQFP64 | LQFP100 | VFQFPN36 | Pin name          | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                              | Remap     |

| K2       | 13     | G3      | 17     | 26      | 10       | PA3               | I/O                 |                            | PA3                                              | USART2_RX <sup>(7)</sup> /<br>ADC12_IN3/<br>TIM2_CH4 <sup>(7)</sup>  |           |

| E4       | -      | C2      | 18     | 27      | -        | V <sub>SS_4</sub> | S                   |                            | $V_{SS_4}$                                       |                                                                      |           |

| F4       | -      | D2      | 19     | 28      | -        | V <sub>DD_4</sub> | S                   |                            | V <sub>DD_4</sub>                                |                                                                      |           |

| G3       | 14     | НЗ      | 20     | 29      | 11       | PA4               | I/O                 |                            | PA4                                              | SPI1_NSS <sup>(7)</sup> /<br>USART2_CK <sup>(7)</sup> /<br>ADC12_IN4 |           |

| НЗ       | 15     | F4      | 21     | 30      | 12       | PA5               | I/O                 |                            | PA5                                              | SPI1_SCK <sup>(7)</sup> /<br>ADC12_IN5                               |           |

| JЗ       | 16     | G4      | 22     | 31      | 13       | PA6               | I/O                 |                            | PA6                                              | SPI1_MISO <sup>(7)</sup> /<br>ADC12_IN6/<br>TIM3_CH1 <sup>(7)</sup>  | TIM1_BKIN |

| КЗ       | 17     | H4      | 23     | 32      | 14       | PA7               | I/O                 |                            | PA7                                              | SPI1_MOSI <sup>(7)</sup> /<br>ADC12_IN7/<br>TIM3_CH2 <sup>(7)</sup>  | TIM1_CH1N |

| G4       | -      | H5      | 24     | 33      |          | PC4               | I/O                 |                            | PC4                                              | ADC12_IN14                                                           |           |

| H4       | -      | H6      | 25     | 34      |          | PC5               | I/O                 |                            | PC5                                              | ADC12_IN15                                                           |           |

| J4       | 18     | F5      | 26     | 35      | 15       | PB0               | I/O                 |                            | PB0                                              | ADC12_IN8/<br>TIM3_CH3 <sup>(7)</sup>                                | TIM1_CH2N |

| K4       | 19     | G5      | 27     | 36      | 16       | PB1               | I/O                 |                            | PB1                                              | ADC12_IN9/<br>TIM3_CH4 <sup>(7)</sup>                                | TIM1_CH3N |

| G5       | 20     | G6      | 28     | 37      | 17       | PB2               | I/O                 | FT                         | PB2/BOOT1                                        |                                                                      |           |

| H5       | -      | -       | -      | 38      | -        | PE7               | I/O                 | FT                         | PE7                                              |                                                                      | TIM1_ETR  |

| J5       | -      | -       | -      | 39      | -        | PE8               | I/O                 | FT                         | PE8                                              |                                                                      | TIM1_CH1N |

| K5       | -      | -       | -      | 40      | -        | PE9               | I/O                 | FT                         | PE9                                              |                                                                      | TIM1_CH1  |

| G6       | -      | -       | -      | 41      | -        | PE10              | I/O                 | FT                         | PE10                                             |                                                                      | TIM1_CH2N |

| H6       | -      | -       | -      | 42      | -        | PE11              | I/O                 | FT                         | PE11                                             |                                                                      | TIM1_CH2  |

| J6       | -      | -       | -      | 43      | -        | PE12              | I/O                 | FT                         | PE12                                             |                                                                      | TIM1_CH3N |

| K6       | -      | -       | -      | 44      | -        | PE13              | I/O                 | FT                         | PE13                                             |                                                                      | TIM1_CH3  |

| G7       | -      | •       | -      | 45      | -        | PE14              | I/O                 | FT                         | PE14                                             |                                                                      | TIM1_CH4  |

| H7       | -      | -       | -      | 46      | -        | PE15              | I/O                 | FT                         | PE15                                             |                                                                      | TIM1_BKIN |

| J7       | 21     | G7      | 29     | 47      | -        | PB10              | I/O                 | FT                         | PB10                                             | I2C2_SCL/<br>USART3_TX <sup>(7)</sup>                                | TIM2_CH3  |

| K7       | 22     | H7      | 30     | 48      | -        | PB11              | I/O                 | FT                         | PB11                                             | I2C2_SDA/<br>USART3_RX <sup>(7)</sup>                                | TIM2_CH4  |

| E7       | 23     | D6      | 31     | 49      | 18       | V <sub>SS_1</sub> | S                   |                            | $V_{SS_1}$                                       |                                                                      |           |

| Table 5. | Medium-density | y STM32F103xx | pin definitions | (continued) |  |

|----------|----------------|---------------|-----------------|-------------|--|

|----------|----------------|---------------|-----------------|-------------|--|

# 5.3.4 Embedded reference voltage

The parameters given in *Table 12* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

| Symbol                                | Parameter                                                           | Conditions                                                               | Min  | Тур  | Max                 | Unit |

|---------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------|------|------|---------------------|------|

| V <sub>REFINT</sub>                   | Internal reference voltage                                          | $-40 \ ^{\circ}\text{C} < \text{T}_{\text{A}} < +105 \ ^{\circ}\text{C}$ | 1.16 | 1.20 | 1.26                | V    |

|                                       | Internal reference voltage                                          | −40 °C < T <sub>A</sub> < +85 °C                                         | 1.16 | 1.20 | 1.24                | V    |

| T <sub>S_vrefint</sub> <sup>(1)</sup> | ADC sampling time when<br>reading the internal reference<br>voltage |                                                                          |      | 5.1  | 17.1 <sup>(2)</sup> | μs   |

Table 12. Embedded internal reference voltage

1. Shortest sampling time can be determined in the application by multiple iterations.

2. Guaranteed by design, not tested in production.

# 5.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 13: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to Dhrystone 2.1 code.

#### Maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load)

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time is adjusted to the f<sub>HCLK</sub> frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 48 MHz and 2 wait states above)

- Prefetch in ON (reminder: this bit must be set before clock setting and bus prescaling)

- When the peripherals are enabled  $f_{PCLK1} = f_{HCLK}/2$ ,  $f_{PCLK2} = f_{HCLK}$

The parameters given in *Table 13*, *Table 14* and *Table 15* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

#### Typical current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load).

- All peripherals are disabled except if it is explicitly mentioned.

- The Flash access time is adjusted to f<sub>HCLK</sub> frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 48 MHz and 2 wait states above).

- Ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in *Table 9*.

- Prefetch is ON (Reminder: this bit must be set before clock setting and bus prescaling)

- When the peripherals are enabled  $f_{PCLK1} = f_{HCLK}/4$ ,  $f_{PCLK2} = f_{HCLK}/2$ ,  $f_{ADCCLK} = f_{PCLK2}/4$

Table 17.Typical current consumption in Run mode, code with data processing<br/>running from Flash

|                 |           |                                 |                   | Ту                                        | p <sup>(1)</sup>         |      |

|-----------------|-----------|---------------------------------|-------------------|-------------------------------------------|--------------------------|------|

| Symbol          | Parameter | Conditions                      | f <sub>HCLK</sub> | All peripherals<br>enabled <sup>(2)</sup> | All peripherals disabled | Unit |

|                 |           |                                 | 72 MHz            | 36                                        | 27                       |      |

|                 |           |                                 | 48 MHz            | 24.2                                      | 18.6                     |      |

|                 |           |                                 | 36 MHz            | 19                                        | 14.8                     |      |

|                 |           |                                 | 24 MHz            | 12.9                                      | 10.1                     |      |

|                 |           |                                 | 16 MHz            | 9.3                                       | 7.4                      |      |

|                 |           | External clock <sup>(3)</sup>   | 8 MHz             | 5.5                                       | 4.6                      | mA   |

|                 |           |                                 | 4 MHz             | 3.3                                       | 2.8                      |      |

|                 |           | 2 MHz                           | 2.2               | 1.9                                       |                          |      |

|                 |           | irrent in                       | 1 MHz             | 1.6                                       | 1.45                     |      |

|                 |           |                                 | 500 kHz           | 1.3                                       | 1.25                     |      |

| 1               | Supply    |                                 | 1.08              | 1.06                                      |                          |      |

| I <sub>DD</sub> | Run mode  |                                 |                   | 64 MHz                                    | 31.4                     | 23.9 |

|                 |           |                                 | 48 MHz            | 23.5                                      | 17.9                     |      |

|                 |           |                                 | 36 MHz            | 18.3                                      | 14.1                     |      |

|                 |           | Running on high                 | 24 MHz            | 12.2                                      | 9.5                      |      |

|                 |           | speed internal RC               | 16 MHz            | 8.5                                       | 6.8                      |      |

|                 |           | (HSI), AHB<br>prescaler used to | 8 MHz             | 4.9                                       | 4                        | mA   |

|                 |           | reduce the                      | 4 MHz             | 2.7                                       | 2.2                      |      |

|                 |           | frequency                       | 2 MHz             | 1.6                                       | 1.4                      |      |

|                 |           |                                 | 1 MHz             | 1.02                                      | 0.9                      |      |

|                 |           |                                 | 500 kHz           | 0.73                                      | 0.67                     |      |

|                 |           |                                 | 125 kHz           | 0.5                                       | 0.48                     |      |

1. Typical values are measures at  $T_A$  = 25 °C,  $V_{DD}$  = 3.3 V.

2. Add an additional power consumption of 0.8 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

3. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

|                                     | Lon ponor mode nanoup                                  | lininge                                                                            |     |      |

|-------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------|-----|------|

| Symbol                              | Parameter                                              | Conditions                                                                         | Тур | Unit |

| t <sub>WUSLEEP</sub> <sup>(1)</sup> | Wakeup from Sleep mode                                 | Wakeup on HSI RC clock                                                             | 1.8 | μs   |

| twustop <sup>(1)</sup>              | Wakeup from Stop mode<br>(regulator in run mode)       | HSI RC wakeup time = 2 µs                                                          | 3.6 | 110  |

|                                     | Wakeup from Stop mode<br>(regulator in low power mode) | HSI RC wakeup time = 2 $\mu$ s, Regulator<br>wakeup from LP mode time = 5 $\mu$ s  | 5.4 | μs   |

| t <sub>WUSTDBY</sub> <sup>(1)</sup> | Wakeup from Standby mode                               | HSI RC wakeup time = 2 $\mu$ s, Regulator wakeup from power down time = 38 $\mu$ s | 50  | μs   |

Table 26. Low-power mode wakeup timings

1. The wakeup times are measured from the wakeup event to the point in which the user application code reads the first instruction.

# 5.3.8 PLL characteristics

The parameters given in *Table 27* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

| Symbol               | Parameter                      | Test conditions |                    | Unit |                    |      |

|----------------------|--------------------------------|-----------------|--------------------|------|--------------------|------|

|                      | Parameter                      | Test conditions | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

| 4                    | PLL input clock <sup>(2)</sup> |                 | 1                  | 8.0  | 25                 | MHz  |

| f <sub>PLL_IN</sub>  | PLL input clock duty cycle     |                 | 40                 |      | 60                 | %    |

| f <sub>PLL_OUT</sub> | PLL multiplier output clock    |                 | 16                 |      | 72                 | MHz  |

| t <sub>LOCK</sub>    | PLL lock time                  |                 |                    |      | 200                | μs   |

Table 27. PLL characteristics

1. Based on characterization, not tested in production.

2. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{\mathsf{PLL}\_\mathsf{OUT}}$ .

## 5.3.9 Memory characteristics

#### **Flash memory**

The characteristics are given at  $T_A = -40$  to 105 °C unless otherwise specified.

| Symbol             | Parameter               | Conditions                      | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |  |  |

|--------------------|-------------------------|---------------------------------|--------------------|------|--------------------|------|--|--|

| t <sub>prog</sub>  | 16-bit programming time | $T_A = -40$ to +105 °C          | 40                 | 52.5 | 70                 | μs   |  |  |

| t <sub>ERASE</sub> | Page (1 KB) erase time  | T <sub>A</sub> = -40 to +105 °C | 20                 |      | 40                 | ms   |  |  |

| t <sub>ME</sub>    | Mass erase time         | T <sub>A</sub> = -40 to +105 °C | 20                 |      | 40                 | ms   |  |  |

Table 28.

Flash memory characteristics

## 5.3.11 Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

Table 32. ESD absolute maximum ratings

| Symbol                | Ratings                                               | Conditions                                              | Class | Maximum value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|---------------------------------------------------------|-------|------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | $T_A = +25 \ ^{\circ}C$<br>conforming to<br>JESD22-A114 | 2     | 2000                         | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | $T_A = +25 \text{ °C}$<br>conforming to<br>JESD22-C101  | 11    | 500                          | v    |

1. Based on characterization results, not tested in production.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

#### Table 33.Electrical sensitivities

| Symbol | Parameter             | Conditions                            | Class      |

|--------|-----------------------|---------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +105$ °C conforming to JESD78A | II level A |

# 5.3.12 I/O port characteristics

# General input/output characteristics

Unless otherwise specified, the parameters given in *Table 34* are derived from tests performed under the conditions summarized in *Table 9*. All I/Os are CMOS and TTL compliant.

| Symbol           | Parameter                                                     | Conditions                                      | Min                               | Тур | Max                  | Unit |

|------------------|---------------------------------------------------------------|-------------------------------------------------|-----------------------------------|-----|----------------------|------|

| V <sub>IL</sub>  | Input low level voltage                                       |                                                 | -0.5                              |     | 0.8                  |      |

| V <sub>IH</sub>  | Standard IO input high level voltage                          | TTL ports                                       | 2                                 |     | V <sub>DD</sub> +0.5 | V    |

|                  | IO FT <sup>(1)</sup> input high level voltage                 |                                                 | 2                                 |     | 5.5V                 |      |

| V <sub>IL</sub>  | Input low level voltage                                       | CMOS porto                                      | -0.5                              |     | 0.35 V <sub>DD</sub> | v    |

| V <sub>IH</sub>  | Input high level voltage                                      | CMOS ports                                      | 0.65 V <sub>DD</sub>              |     | V <sub>DD</sub> +0.5 | v    |

| M                | Standard IO Schmitt trigger voltage hysteresis <sup>(2)</sup> |                                                 | 200                               |     |                      | mV   |

| V <sub>hys</sub> | IO FT Schmitt trigger voltage<br>hysteresis <sup>(2)</sup>    |                                                 | 5% V <sub>DD</sub> <sup>(3)</sup> |     |                      | mV   |

| I                | Input leakage current <sup>(4)</sup>                          | $V_{SS} \le V_{IN} \le V_{DD}$<br>Standard I/Os |                                   |     | ±1                   | μA   |

| l <sub>lkg</sub> | input leakage current V                                       | V <sub>IN</sub> = 5 V<br>I/O FT                 |                                   |     | 3                    | μΑ   |

| R <sub>PU</sub>  | Weak pull-up equivalent<br>resistor <sup>(5)</sup>            | $V_{IN} = V_{SS}$                               | 30                                | 40  | 50                   | kΩ   |

| R <sub>PD</sub>  | Weak pull-down equivalent<br>resistor <sup>(5)</sup>          | $V_{IN} = V_{DD}$                               | 30                                | 40  | 50                   | kΩ   |

| C <sub>IO</sub>  | I/O pin capacitance                                           |                                                 |                                   | 5   |                      | pF   |

Table 34. I/O static characteristics

1. FT = Five-volt tolerant.

2. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization, not tested in production.

- 3. With a minimum of 100 mV.

- 4. Leakage could be higher than max. if negative current is injected on adjacent pins.

- 5. Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This MOS/NMOS contribution to the series resistance is minimum (~10% order).

All I/Os are CMOS and TTL compliant (no software configuration required), their characteristics consider the most strict CMOS-technology or TTL parameters:

- For V<sub>IH</sub>:

- if V<sub>DD</sub> is in the [2.00 V 3.08 V] range: CMOS characteristics but TTL included

- if V<sub>DD</sub> is in the [3.08 V 3.60 V] range: TTL characteristics but CMOS included

- For V<sub>IL</sub>:

- if V<sub>DD</sub> is in the [2.00 V 2.28 V] range: TTL characteristics but CMOS included

- if V<sub>DD</sub> is in the [2.28 V 3.60 V] range: CMOS characteristics but TTL included

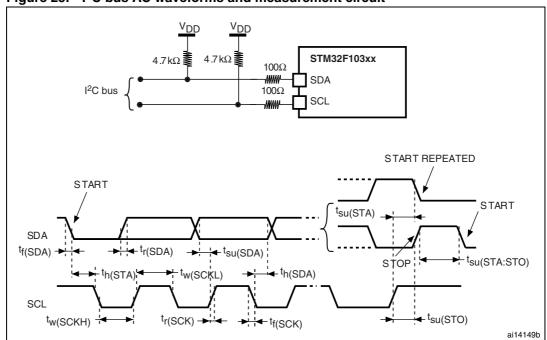

Figure 25. I<sup>2</sup>C bus AC waveforms and measurement circuit

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

# Table 40. SCL frequency $(f_{PCLK1} = 36 \text{ MHz.}, V_{DD} = 3.3 \text{ V})^{(1)(2)}$

| f ((tH=)               | I2C_CCR value                  |

|------------------------|--------------------------------|

| f <sub>SCL</sub> (kHz) | <b>R</b> <sub>P</sub> = 4.7 kΩ |

| 400                    | 0x801E                         |

| 300                    | 0x8028                         |

| 200                    | 0x803C                         |

| 100                    | 0x00B4                         |

| 50                     | 0x0168                         |

| 20                     | 0x0384                         |

1.  $R_P$  = External pull-up resistance,  $f_{SCL} = I^2C$  speed,

For speeds around 200 kHz, the tolerance on the achieved speed is of ±5%. For other speed ranges, the tolerance on the achieved speed ±2%. These variations depend on the accuracy of the external components used to design the application.

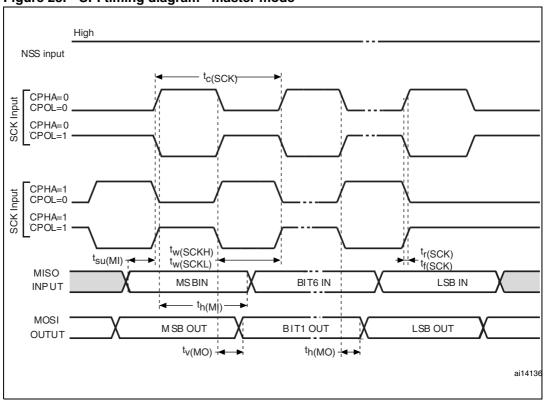

Figure 28. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}.$

## **USB** characteristics

The USB interface is USB-IF certified (Full Speed).

#### Table 42.USB startup time

| Symbol                              | Parameter                    | Max | Unit |

|-------------------------------------|------------------------------|-----|------|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB transceiver startup time | 1   | μs   |

1. Guaranteed by design, not tested in production.

## 5.3.17 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 45* are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 9*.

Note: It is recommended to perform a calibration after each power-up.

| Table 45.                        | ADC characteristics                       |                           | -                                                                          |                    |                    | 1                  |

|----------------------------------|-------------------------------------------|---------------------------|----------------------------------------------------------------------------|--------------------|--------------------|--------------------|

| Symbol                           | Parameter                                 | Conditions                | Min                                                                        | Тур                | Max                | Unit               |

| V <sub>DDA</sub>                 | Power supply                              |                           | 2.4                                                                        |                    | 3.6                | V                  |

| V <sub>REF+</sub>                | Positive reference voltage                |                           | 2.4                                                                        |                    | V <sub>DDA</sub>   | V                  |

| I <sub>VREF</sub>                | Current on the V <sub>REF</sub> input pin |                           |                                                                            | 160 <sup>(1)</sup> | 220 <sup>(1)</sup> | μA                 |

| f <sub>ADC</sub>                 | ADC clock frequency                       |                           | 0.6                                                                        |                    | 14                 | MHz                |

| f <sub>S</sub> <sup>(2)</sup>    | Sampling rate                             |                           | 0.05                                                                       |                    | 1                  | MHz                |

| £ (2)                            | External trigger frequency                | f <sub>ADC</sub> = 14 MHz |                                                                            |                    | 823                | kHz                |

| f <sub>TRIG</sub> <sup>(2)</sup> | External trigger frequency                |                           |                                                                            |                    | 17                 | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub> <sup>(3)</sup>  | Conversion voltage range                  |                           | 0 (V <sub>SSA</sub> or V <sub>REF-</sub><br>tied to ground)                |                    | V <sub>REF+</sub>  | V                  |

| R <sub>AIN</sub> <sup>(2)</sup>  | External input impedance                  |                           | See Equation 1 and Table 46                                                |                    |                    | kΩ                 |

| R <sub>ADC</sub> <sup>(2)</sup>  | Sampling switch resistance                |                           |                                                                            |                    | 1                  | kΩ                 |

| C <sub>ADC</sub> <sup>(2)</sup>  | Internal sample and hold capacitor        |                           |                                                                            |                    | 12                 | pF                 |

| + (2)                            | Calibration time                          | f <sub>ADC</sub> = 14 MHz | 5.9                                                                        |                    |                    | μs                 |

| t <sub>CAL</sub> <sup>(2)</sup>  | Calibration time                          |                           | 83                                                                         |                    |                    | 1/f <sub>ADC</sub> |

| t <sub>lat</sub> (2)             | Injection trigger conversion              | f <sub>ADC</sub> = 14 MHz |                                                                            |                    | 0.214              | μs                 |

| <sup>l</sup> lat` '              | latency                                   |                           |                                                                            |                    | 3 <sup>(4)</sup>   | 1/f <sub>ADC</sub> |

| t <sub>latr</sub> (2)            | Regular trigger conversion                | f <sub>ADC</sub> = 14 MHz |                                                                            |                    | 0.143              | μs                 |

| <sup>l</sup> latr` '             | latency                                   |                           |                                                                            |                    | 2 <sup>(4)</sup>   | 1/f <sub>ADC</sub> |

| ts <sup>(2)</sup>                | Sampling time                             | f <sub>ADC</sub> = 14 MHz | 0.107                                                                      |                    | 17.1               | μs                 |

| U                                | Samping une                               |                           | 1.5                                                                        |                    | 239.5              | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(2)</sup> | Power-up time                             |                           | 0                                                                          | 0                  | 1                  | μs                 |

|                                  | Total conversion time                     | f <sub>ADC</sub> = 14 MHz | 1                                                                          |                    | 18                 | μs                 |

| t <sub>CONV</sub> <sup>(2)</sup> | (including sampling time)                 |                           | 14 to 252 (t <sub>S</sub> for sampling +12.5 for successive approximation) |                    |                    | 1/f <sub>ADC</sub> |

Table 45.

ADC characteristics

1. Based on characterization, not tested in production.

2. Guaranteed by design, not tested in production.

4. For external triggers, a delay of 1/f<sub>PCLK2</sub> must be added to the latency specified in *Table 45*.

In devices delivered in VFQFPN and LQFP packages, V<sub>REF+</sub> is internally connected to V<sub>DDA</sub> and V<sub>REF-</sub> is internally connected to V<sub>SSA</sub>. Devices that come in the TFBGA64 package have a V<sub>REF+</sub> pin but no V<sub>REF-</sub> pin (V<sub>REF-</sub> is internally connected to V<sub>SSA</sub>), see *Table 5* and *Figure 6*.

#### Equation 1: R<sub>AIN</sub> max formula:

$$R_{AIN} < \frac{I_{S}}{f_{ADC} \times C_{ADC} \times ln(2^{N+2})} - R_{ADC}$$

The formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. Here N = 12 (from 12-bit resolution).

#### Table 46. $R_{AIN}$ max for $f_{ADC} = 14 \text{ MHz}^{(1)}$

| T <sub>s</sub> (cycles) | t <sub>S</sub> (μs) | R <sub>AIN</sub> max (kΩ) |

|-------------------------|---------------------|---------------------------|

| 1.5                     | 0.11                | 1.2                       |

| 7.5                     | 0.54                | 10                        |

| 13.5                    | 0.96                | 19                        |

| 28.5                    | 2.04                | 41                        |

| 41.5                    | 2.96                | 60                        |

| 55.5                    | 3.96                | 80                        |

| 71.5                    | 5.11                | 104                       |

| 239.5                   | 17.1                | 350                       |

1. Based on characterization, not tested in production.

# Table 47. ADC accuracy - limited test conditions<sup>(1) (2)</sup>

| Symbol | Parameter                    | Test conditions                                                   | Тур  | Max <sup>(3)</sup> | Unit |

|--------|------------------------------|-------------------------------------------------------------------|------|--------------------|------|

| ET     | Total unadjusted error       | f <sub>PCLK2</sub> = 56 MHz,                                      | ±1.3 | ±2                 |      |

| EO     | Offset error                 | $f_{ADC} = 14 \text{ MHz}, \text{ R}_{AIN} < 10 \text{ k}\Omega,$ | ±1   | ±1.5               |      |

| EG     | Gain error                   | V <sub>DDA</sub> = 3 V to 3.6 V<br>T₄ = 25 °C                     | ±0.5 | ±1.5               | LSB  |

| ED     | Differential linearity error | Measurements made after                                           | ±0.7 | ±1                 |      |

| EL     | Integral linearity error     | ADC calibration                                                   | ±0.8 | ±1.5               |      |

1. ADC DC accuracy values are measured after internal calibration.

ADC Accuracy vs. Negative Injection Current: Injecting negative current on any of the standard (non-robust) analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to standard analog pins which may potentially inject negative current. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in *Section 5.3.12* does not affect the ADC accuracy.

3. Based on characterization, not tested in production.

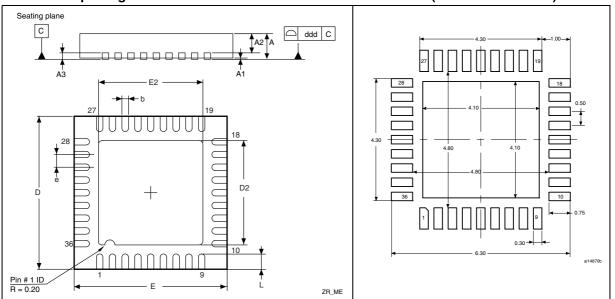

# 6 Package characteristics

# 6.1 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

1. Drawing is not to scale.

2. The back-side pad is not internally connected to the  $V_{SS}$  or  $V_{DD}$  power pads.

3. There is an exposed die pad on the underside of the VFQFPN package. It should be soldered to the PCB. All leads should also be soldered to the PCB.

| Symbol |       | millimeters |       | inches <sup>(1)</sup> |        |        |

|--------|-------|-------------|-------|-----------------------|--------|--------|

|        | Min   | Тур         | Max   | Min                   | Тур    | Max    |

| А      | 0.800 | 0.900       | 1.000 | 0.0315                | 0.0354 | 0.0394 |

| A1     |       | 0.020       | 0.050 |                       | 0.0008 | 0.0020 |

| A2     |       | 0.650       | 1.000 |                       | 0.0256 | 0.0394 |

| A3     |       | 0.250       |       |                       | 0.0098 |        |

| b      | 0.180 | 0.230       | 0.300 | 0.0071                | 0.0091 | 0.0118 |

| D      | 5.875 | 6.000       | 6.125 | 0.2313                | 0.2362 | 0.2411 |

| D2     | 1.750 | 3.700       | 4.250 | 0.0689                | 0.1457 | 0.1673 |

| E      | 5.875 | 6.000       | 6.125 | 0.2313                | 0.2362 | 0.2411 |

| E2     | 1.750 | 3.700       | 4.250 | 0.0689                | 0.1457 | 0.1673 |

| е      | 0.450 | 0.500       | 0.550 | 0.0177                | 0.0197 | 0.0217 |

| L      | 0.350 | 0.550       | 0.750 | 0.0138                | 0.0217 | 0.0295 |

| ddd    |       | 0.080       |       |                       | 0.0031 |        |

#### Table 50. VFQFPN36 6 x 6 mm, 0.5 mm pitch, package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

# Figure 35. Recommended footprint (dimensions in mm)<sup>(1)(2)(3)</sup>

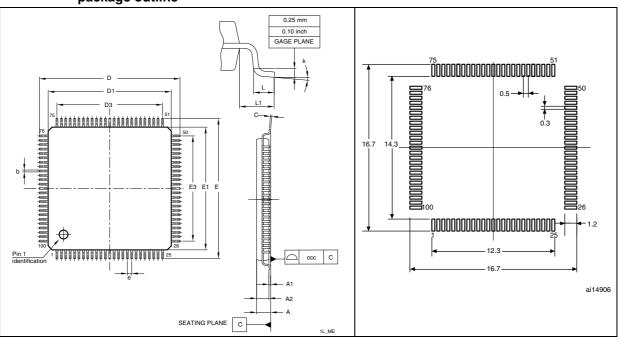

# Figure 38. LQFP100, 100-pin low-profile quad flat package outline<sup>(1)</sup>

1. Drawing is not to scale.

2. Dimensions are in millimeters.

#### Table 52. LQPF100, 100-pin low-profile quad flat package mechanical data

| O h l    | millimeters |      |      | inches <sup>(1)</sup> |        |        |  |

|----------|-------------|------|------|-----------------------|--------|--------|--|

| Symbol - | Тур         | Min  | Мах  | Тур                   | Min    | Мах    |  |

| А        |             |      | 1.6  |                       |        | 0.063  |  |

| A1       |             | 0.05 | 0.15 |                       | 0.002  | 0.0059 |  |

| A2       | 1.4         | 1.35 | 1.45 | 0.0551                | 0.0531 | 0.0571 |  |

| b        | 0.22        | 0.17 | 0.27 | 0.0087                | 0.0067 | 0.0106 |  |

| С        |             | 0.09 | 0.2  |                       | 0.0035 | 0.0079 |  |

| D        | 16          | 15.8 | 16.2 | 0.6299                | 0.622  | 0.6378 |  |

| D1       | 14          | 13.8 | 14.2 | 0.5512                | 0.5433 | 0.5591 |  |

| D3       | 12          |      |      | 0.4724                |        |        |  |

| Е        | 16          | 15.8 | 16.2 | 0.6299                | 0.622  | 0.6378 |  |

| E1       | 14          | 13.8 | 14.2 | 0.5512                | 0.5433 | 0.5591 |  |

| E3       | 12          |      |      | 0.4724                |        |        |  |

| е        | 0.5         |      |      | 0.0197                |        |        |  |

| L        | 0.6         | 0.45 | 0.75 | 0.0236                | 0.0177 | 0.0295 |  |

| L1       | 1           |      |      | 0.0394                |        |        |  |

| k        | 3.5°        | 0.0° | 7.0° | 3.5°                  | 0.0°   | 7.0°   |  |

| CCC      |             | 0.08 |      |                       | 0.0031 | •      |  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

# Figure 39. Recommended footprint $^{(1)(2)}$

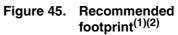

# Figure 44. LQFP48, 48-pin low-profile quad flat package outline<sup>(1)</sup>

1. Drawing is not to scale.

2. Dimensions are in millimeters.

| Table 55. | LQFP48, 48-pin low-profile quad flat package mechanical data |

|-----------|--------------------------------------------------------------|

|-----------|--------------------------------------------------------------|

| Symbol |       | millimeters |       | inches <sup>(1)</sup> |        |        |

|--------|-------|-------------|-------|-----------------------|--------|--------|

|        | Тур   | Min         | Max   | Тур                   | Min    | Мах    |

| A      |       |             | 1.600 |                       |        | 0.0630 |

| A1     |       | 0.050       | 0.150 |                       | 0.0020 | 0.0059 |

| A2     | 1.400 | 1.350       | 1.450 | 0.0551                | 0.0531 | 0.0571 |

| b      | 0.220 | 0.170       | 0.270 | 0.0087                | 0.0067 | 0.0106 |

| с      |       | 0.090       | 0.200 |                       | 0.0035 | 0.0079 |

| D      | 9.000 | 8.800       | 9.200 | 0.3543                | 0.3465 | 0.3622 |

| D1     | 7.000 | 6.800       | 7.200 | 0.2756                | 0.2677 | 0.2835 |

| D3     | 5.500 |             |       | 0.2165                |        |        |

| E      | 9.000 | 8.800       | 9.200 | 0.3543                | 0.3465 | 0.3622 |

| E1     | 7.000 | 6.800       | 7.200 | 0.2756                | 0.2677 | 0.2835 |

| E3     | 5.500 |             |       | 0.2165                |        |        |

| е      | 0.500 |             |       | 0.0197                |        |        |

| L      | 0.600 | 0.450       | 0.750 | 0.0236                | 0.0177 | 0.0295 |

| L1     | 1.000 |             |       | 0.0394                |        |        |

| k      | 3.5°  | 0°          | 7°    | 3.5°                  | 0°     | 7°     |

| ссс    |       | 0.080       |       | 0.0031                |        |        |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

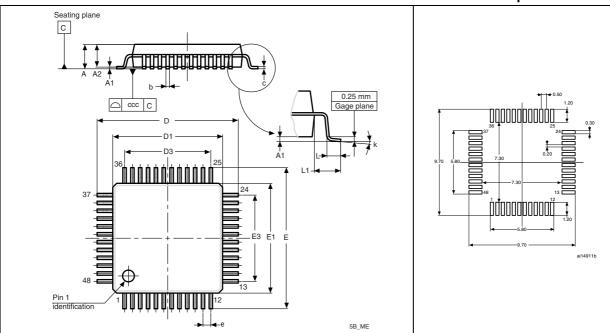

Using the values obtained in *Table 56*  $T_{Jmax}$  is calculated as follows:

- For LQFP100, 46 °C/W

- $T_{Jmax} = 115 \ ^{\circ}C + (46 \ ^{\circ}C/W \times 134 \ mW) = 115 \ ^{\circ}C + 6.2 \ ^{\circ}C = 121.2 \ ^{\circ}C$

This is within the range of the suffix 7 version parts (–40 <  $T_J$  < 125 °C).

In this case, parts must be ordered at least with the temperature range suffix 7 (see *Table 57: Ordering information scheme*).

Figure 46. LQFP100 P<sub>D</sub> max vs. T<sub>A</sub>