Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, Motor Control PWM, PDR, POR, PVD, PWM, Temp Sensor, WDT          |

| Number of I/O              | 51                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 20K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-TFBGA                                                              |

| Supplier Device Package    | 64-TFBGA (5x5)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f103r8h6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 8 | <b>Revision history</b> |  | 5 |

|---|-------------------------|--|---|

|---|-------------------------|--|---|

# List of figures

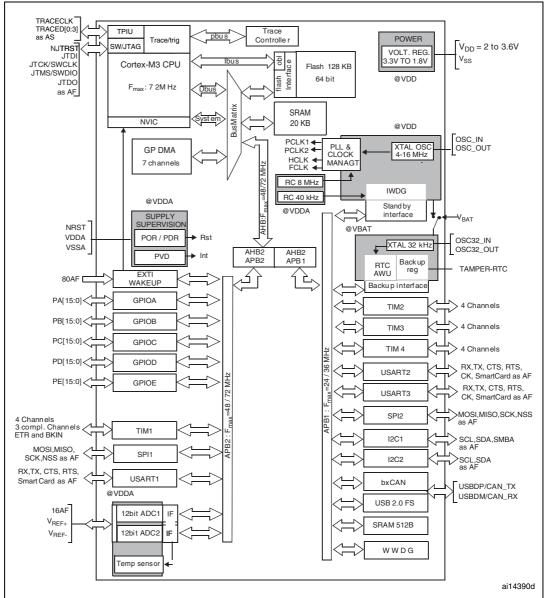

| Figure 1.  | STM32F103xx performance line block diagram                                                                                                                  | . 19 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2.  | Clock tree                                                                                                                                                  |      |

| Figure 3.  | STM32F103xx performance line LFBGA100 ballout                                                                                                               | . 21 |

| Figure 4.  | STM32F103xx performance line LQFP100 pinout                                                                                                                 | . 22 |

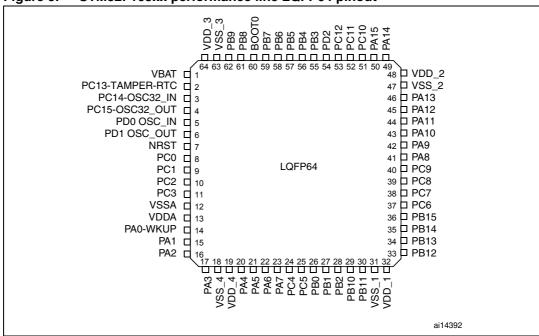

| Figure 5.  | STM32F103xx performance line LQFP64 pinout                                                                                                                  | . 23 |

| Figure 6.  | STM32F103xx performance line TFBGA64 ballout                                                                                                                |      |

| Figure 7.  | STM32F103xx performance line LQFP48 pinout                                                                                                                  |      |

| Figure 8.  | STM32F103xx Performance Line VFQFPN36 pinout.                                                                                                               |      |

| Figure 9.  |                                                                                                                                                             |      |

| Figure 10. | Pin loading conditions.                                                                                                                                     |      |

| Figure 11. | Pin input voltage                                                                                                                                           |      |

| Figure 12. | Power supply scheme.                                                                                                                                        |      |

| Figure 13. | Current consumption measurement scheme                                                                                                                      |      |

| Figure 14. | Typical current consumption in Run mode versus frequency (at 3.6 V) -                                                                                       |      |

|            | code with data processing running from RAM, peripherals enabled.                                                                                            | . 40 |

| Figure 15. | Typical current consumption in Run mode versus frequency (at 3.6 V) -                                                                                       |      |

| rigulo io. | code with data processing running from RAM, peripherals disabled                                                                                            | 40   |

| Figure 16. | Typical current consumption in Stop mode with regulator in Run mode versus                                                                                  |      |

| riguro ro. | temperature at $V_{DD}$ = 3.3 V and 3.6 V                                                                                                                   | 42   |

| Figure 17. | Typical current consumption in Stop mode with regulator in Low-power mode versus                                                                            |      |

| rigure i/. | temperature at $V_{DD}$ = 3.3 V and 3.6 V                                                                                                                   | 43   |

| Figure 18. | Typical current consumption in Standby mode versus temperature at                                                                                           | . 40 |

| riguie io. | $V_{DD} = 3.3 \text{ V} \text{ and } 3.6 \text{ V} \dots$                                                                                                   | 13   |

| Figure 19. | High-speed external clock source AC timing diagram                                                                                                          |      |

| Figure 20. | Low-speed external clock source AC timing diagram                                                                                                           |      |

| Figure 20. | Typical application with an 8 MHz crystal                                                                                                                   |      |

| Figure 21. | Typical application with a 32.768 kHz crystal                                                                                                               |      |

|            | I/O AC characteristics definition                                                                                                                           |      |

| Figure 23. |                                                                                                                                                             |      |

| Figure 24. | Recommended NRST pin protection                                                                                                                             |      |

| Figure 25. | I <sup>2</sup> C bus AC waveforms and measurement circuit                                                                                                   |      |

| Figure 26. | SPI timing diagram - slave mode and CPHA = 0                                                                                                                | . 04 |

| Figure 27. | SPI timing diagram - slave mode and CPHA = $1^{(1)}$                                                                                                        | . 64 |

| Figure 28. | SPI timing diagram - master mode <sup>(1)</sup>                                                                                                             |      |

| Figure 29. | USB timings: definition of data signal rise and fall time                                                                                                   |      |

| Figure 30. | ADC accuracy characteristics                                                                                                                                |      |

| Figure 31. | Typical connection diagram using the ADC                                                                                                                    |      |

| Figure 32. | Power supply and reference decoupling (V <sub>REF+</sub> not connected to V <sub>DDA</sub> )                                                                | . 70 |

| Figure 33. | Power supply and reference decoupling (V <sub>REF+</sub> connected to V <sub>DDA</sub> )<br>VFQFPN36 6 x 6 mm, 0.5 mm pitch, package outline <sup>(1)</sup> | . /1 |

| Figure 34. | VFQFPN36 6 x 6 mm, 0.5 mm pitch, package outline                                                                                                            | 73   |

| Figure 35. | Recommended footprint (dimensions in mm) <sup>(1)(2)(3)</sup>                                                                                               |      |

| Figure 36. | LFBGA100 - low profile fine pitch ball grid array package outline                                                                                           |      |

| Figure 37. | Recommended PCB design rules (0.80/0.75 mm pitch BGA)                                                                                                       |      |

| Figure 38. | LQFP100, 100-pin low-profile quad flat package outline                                                                                                      |      |

| Figure 39. | Recommended footprint <sup>(1)</sup>                                                                                                                        | . 76 |

| Figure 40. | LQFP64, 64-pin low-profile quad flat package outline                                                                                                        | . 77 |

| Figure 41. | Recommended footprint <sup>(1)</sup>                                                                                                                        | . 77 |

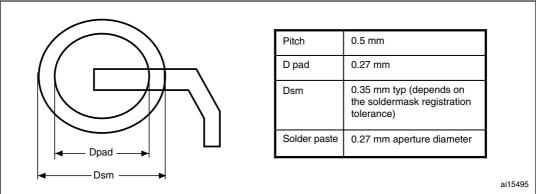

| Figure 42. | TFBGA64 - 8 x 8 active ball array, 5 x 5 mm, 0.5 mm pitch, package outline                                                                                  | . 78 |

| Figure 43. | Recommended PCB design rules for pads (0.5 mm pitch BGA)                                                                                                    | . 79 |

| Figure 44. | LQFP48, 48-pin low-profile quad flat package outline | 80 |

|------------|------------------------------------------------------|----|

| Figure 45. | Recommended footprint <sup>(1)</sup>                 | 80 |

| Figure 46. | LQFP100 P <sub>D</sub> max vs. T <sub>A</sub>        | 83 |

57

This hardware block provides flexible interrupt management features with minimal interrupt latency.

## 2.3.6 External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 19 edge detector lines used to generate interrupt/event requests. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 80 GPIOs can be connected to the 16 external interrupt lines.

## 2.3.7 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-16 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example on failure of an indirectly used external crystal, resonator or oscillator).

Several prescalers allow the configuration of the AHB frequency, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the AHB and the high-speed APB domains is 72 MHz. The maximum allowed frequency of the low-speed APB domain is 36 MHz. See *Figure 2* for details on the clock tree.

## 2.3.8 Boot modes

At startup, boot pins are used to select one of three boot options:

- Boot from User Flash

- Boot from System Memory

- Boot from embedded SRAM

The boot loader is located in System Memory. It is used to reprogram the Flash memory by using USART1. For further details please refer to AN2606.

## 2.3.9 Power supply schemes

- V<sub>DD</sub> = 2.0 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 2.0 to 3.6 V: external analog power supplies for ADC, reset blocks, RCs and PLL (minimum voltage to be applied to V<sub>DDA</sub> is 2.4 V when the ADC is used). V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

- V<sub>BAT</sub> = 1.8 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

For more details on how to connect power pins, refer to *Figure 12: Power supply scheme*.

## 2.3.10 Power supply supervisor

The device has an integrated power-on reset (POR)/power-down reset (PDR) circuitry. It is always active, and ensures proper operation starting from/down to 2 V. The device remains

in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$ , without the need for an external reset circuit.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

Refer to Table 11: Embedded reset and power control block characteristics for the values of  $V_{POR/PDR}$  and  $V_{PVD}$ .

## 2.3.11 Voltage regulator

The regulator has three operation modes: main (MR), low power (LPR) and power down.

- MR is used in the nominal regulation mode (Run)

- LPR is used in the Stop mode

- Power down is used in Standby mode: the regulator output is in high impedance: the kernel circuitry is powered down, inducing zero consumption (but the contents of the registers and SRAM are lost)

This regulator is always enabled after reset. It is disabled in Standby mode, providing high impedance output.

### 2.3.12 Low-power modes

The STM32F103xx performance line supports three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

• Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

• Stop mode

The Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low power mode.

The device can be woken up from Stop mode by any of the EXTI line. The EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm or the USB wakeup.

Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.8 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, SRAM and register contents are lost except for registers in the Backup domain and Standby circuitry.

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped by entering Stop or Standby mode.

can also be seen as a complete general-purpose timer. The 4 independent channels can be used for

- Input capture

- Output compare

- PWM generation (edge- or center-aligned modes)

- One-pulse mode output

If configured as a general-purpose 16-bit timer, it has the same features as the TIMx timer. If configured as the 16-bit PWM generator, it has full modulation capability (0-100%).

In debug mode, the advanced-control timer counter can be frozen and the PWM outputs disabled to turn off any power switch driven by these outputs.

Many features are shared with those of the general-purpose TIM timers which have the same architecture. The advanced-control timer can therefore work together with the TIM timers via the Timer Link feature for synchronization or event chaining.

### General-purpose timers (TIMx)

There are up to three synchronizable general-purpose timers embedded in the STM32F103xx performance line devices. These timers are based on a 16-bit auto-reload up/down counter, a 16-bit prescaler and feature 4 independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 12 input captures/output compares/PWMs on the largest packages.

The general-purpose timers can work together with the advanced-control timer via the Timer Link feature for synchronization or event chaining. Their counter can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs. They all have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

#### Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 40 kHz internal RC and as it operates independently of the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes. The counter can be frozen in debug mode.

#### Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

Figure 1. STM32F103xx performance line block diagram

1.  $T_A = -40$  °C to +105 °C (junction temperature up to 125 °C).

2. AF = alternate function on I/O port pin.

Figure 5. STM32F103xx performance line LQFP64 pinout

| igure | 1                         | 2                    | 3         | 4       | 5       | 6           | 7      | 8       |

|-------|---------------------------|----------------------|-----------|---------|---------|-------------|--------|---------|

| A     | •<br>/PC14-<br>O\\$C32_IN | , PC13-,<br>AMPER-RT | C ( PB9 ) | ( PB4 ) | ( PB3 ) | (PA15)      | (PA14) | (PA13)  |

| В     | ,Ρ́C15-`,<br>OŚC32_ΟUT    | VBAT                 | (PB8)     | BOOTO   | ( PD2 ) | (PC11)      | (PC10) | (PA12)  |

| С     | OSC_IN                    | Vss_4                | (PB7)     | (PB5)   | (PC12)  | (PA10)      | (PA9)  | (PA11)  |

| D     | OSC_OUT                   | VDD_4                | (PB6)     | VSS_3   | VSS_2   | ,<br>VSS_1, | (PA8)  | (PC9)   |

| E     | (NRST)                    | (PC1)                | (PC0)     | WDD_3'  | VDD_2'  | VDD_1       | (PC7)  | (PC8)   |

| F     | (VSSA)                    | (PC2)                | (PA2)     | ( PA5 ) | (PB0)   | (PC6)       | (PB15) | (PB14)  |

| G     | WREF+i                    | PĄO-WKŲP             | (PA3)     | PA6     | (PB1)   | (PB2)       | (PB10) | (PB13)  |

| н     | VDDA,                     | ( PA1 )              | (PA4)     | PA7     | (PC4)   | (PC5)       | (PB11) | (PB12)  |

|       |                           |                      |           |         |         |             |        | AI15494 |

Figure 6. STM32F103xx performance line TFBGA64 ballout

# 5 Electrical characteristics

# 5.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to  $V_{SS}$ .

## 5.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

# 5.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A$  = 25 °C,  $V_{DD}$  = 3.3 V (for the 2 V  $\leq$   $V_{DD}$   $\leq$  3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\Sigma$ ).

## 5.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

# 5.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 10*.

## 5.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 11*.

| Table 9.       | General operating conditions (continued)                            |                                      |     |      |      |  |  |

|----------------|---------------------------------------------------------------------|--------------------------------------|-----|------|------|--|--|

| Symbol         | Parameter                                                           | Conditions                           | Min | Max  | Unit |  |  |

|                |                                                                     | LFBGA100                             |     | 454  |      |  |  |

|                |                                                                     | LQFP100                              |     | 434  |      |  |  |

| Р              | Power dissipation at $T_A = 85 \degree C$                           | TFBGA64                              |     | 308  | m\\/ |  |  |

| P <sub>D</sub> | for suffix 6 or $T_A = 105 \ ^{\circ}C$ for suffix 7 <sup>(3)</sup> | LQFP64                               |     | 444  | mW   |  |  |

|                |                                                                     | LQFP48                               |     | 363  |      |  |  |

|                |                                                                     | VFQFPN36                             |     | 1110 |      |  |  |

|                | Ambient temperature for 6                                           | Maximum power dissipation            | -40 | 85   | °C   |  |  |

| Та             | suffix version                                                      | Low power dissipation <sup>(4)</sup> | -40 | 105  | C    |  |  |

| IA             | Ambient temperature for 7                                           | Maximum power dissipation            | -40 | 105  | °C   |  |  |

|                | suffix version                                                      | Low power dissipation <sup>(4)</sup> | -40 | 125  | C    |  |  |

| <b>.</b>       | lunction tomporature range                                          | 6 suffix version                     | -40 | 105  | °C   |  |  |

| TJ             | Junction temperature range                                          | 7 suffix version                     | -40 | 125  | U    |  |  |

Table 9. General operating conditions (continued)

1. When the ADC is used, refer to *Table 45: ADC characteristics*.

2. It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up and operation.

- If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>J</sub>max (see *Table 6.2: Thermal characteristics on page 81*).

- In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>J</sub>max (see Table 6.2: Thermal characteristics on page 81).

## 5.3.2 Operating conditions at power-up / power-down

Subject to general operating conditions for T<sub>A</sub>.

#### Table 10. Operating conditions at power-up / power-down

| Symbol           | Parameter                      | Conditions | Min | Max      | Unit  |

|------------------|--------------------------------|------------|-----|----------|-------|

| 1                | V <sub>DD</sub> rise time rate |            | 0   | $\infty$ | µs/V  |

| <sup>I</sup> VDD | V <sub>DD</sub> fall time rate |            | 20  | $\infty$ | μ5/ V |

## 5.3.3 Embedded reset and power control block characteristics

The parameters given in *Table 11* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

# 5.3.4 Embedded reference voltage

The parameters given in *Table 12* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

| Symbol                                | Parameter                                                     | Conditions                                                               | Min  | Тур  | Max                 | Unit |

|---------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------|------|------|---------------------|------|

| V                                     | Internal reference voltage                                    | $-40 \ ^{\circ}\text{C} < \text{T}_{\text{A}} < +105 \ ^{\circ}\text{C}$ | 1.16 | 1.20 | 1.26                | V    |

| V <sub>REFINT</sub>                   | Internal reference voltage                                    | −40 °C < T <sub>A</sub> < +85 °C                                         | 1.16 | 1.20 | 1.24                | V    |

| T <sub>S_vrefint</sub> <sup>(1)</sup> | ADC sampling time when reading the internal reference voltage |                                                                          |      | 5.1  | 17.1 <sup>(2)</sup> | μs   |

Table 12. Embedded internal reference voltage

1. Shortest sampling time can be determined in the application by multiple iterations.

2. Guaranteed by design, not tested in production.

## 5.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 13: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to Dhrystone 2.1 code.

#### Maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load)

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time is adjusted to the f<sub>HCLK</sub> frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 48 MHz and 2 wait states above)

- Prefetch in ON (reminder: this bit must be set before clock setting and bus prescaling)

- When the peripherals are enabled  $f_{PCLK1} = f_{HCLK}/2$ ,  $f_{PCLK2} = f_{HCLK}$

The parameters given in *Table 13*, *Table 14* and *Table 15* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

| Symbol            | Parameter           | Conditions                                                                         | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|-------------------|---------------------|------------------------------------------------------------------------------------|--------------------|-----|--------------------|------|

|                   |                     | Read mode $f_{HCLK} = 72 \text{ MHz}$ with 2 wait states, $V_{DD} = 3.3 \text{ V}$ |                    |     | 20                 | mA   |

| I <sub>DD</sub>   | Supply current      | Write / Erase modes<br>$f_{HCLK} = 72 \text{ MHz}, V_{DD} = 3.3 \text{ V}$         |                    |     | 5                  | mA   |

|                   |                     | Power-down mode / Halt, $V_{DD} = 3.0$ to 3.6 V                                    |                    |     | 50                 | μA   |

| V <sub>prog</sub> | Programming voltage |                                                                                    | 2                  |     | 3.6                | V    |

Table 28. Flash memory characteristics (continued)

1. Guaranteed by design, not tested in production.

#### Table 29. Flash memory endurance and data retention

| Symbol           | Parameter      | Conditions                                                                              | Value              |     |     | Unit    |

|------------------|----------------|-----------------------------------------------------------------------------------------|--------------------|-----|-----|---------|

| Symbol Parameter |                | Conditions                                                                              | Min <sup>(1)</sup> | Тур | Max | Unit    |

| N <sub>END</sub> | Endurance      | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                 |     |     | kcycles |

|                  |                | 1 kcycle <sup>(2)</sup> at $T_A = 85 \ ^{\circ}C$                                       | 30                 |     |     |         |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at $T_A = 105 \ ^\circ C$                                       | 10                 |     |     | Years   |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                 |     |     |         |

1. Based on characterization, not tested in production.

2. Cycling performed over the whole temperature range.

## 5.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 1000-4-2 standard.

- **FTB**: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 1000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 30*. They are based on the EMS levels and classes defined in application note AN1709.

# 5.3.12 I/O port characteristics

## General input/output characteristics

Unless otherwise specified, the parameters given in *Table 34* are derived from tests performed under the conditions summarized in *Table 9*. All I/Os are CMOS and TTL compliant.

| Symbol           | Parameter                                                     | Conditions                                      | Min                               | Тур | Max                  | Unit |

|------------------|---------------------------------------------------------------|-------------------------------------------------|-----------------------------------|-----|----------------------|------|

| $V_{IL}$         | Input low level voltage                                       |                                                 | -0.5                              |     | 0.8                  |      |

| V <sub>IH</sub>  | Standard IO input high level voltage                          | TTL ports                                       | 2                                 |     | V <sub>DD</sub> +0.5 | V    |

|                  | IO FT <sup>(1)</sup> input high level voltage                 |                                                 | 2                                 |     | 5.5V                 |      |

| V <sub>IL</sub>  | Input low level voltage                                       | CMOS porto                                      | -0.5                              |     | 0.35 V <sub>DD</sub> | V    |

| V <sub>IH</sub>  | Input high level voltage                                      | CMOS ports                                      | 0.65 V <sub>DD</sub>              |     | V <sub>DD</sub> +0.5 | v    |

| M                | Standard IO Schmitt trigger voltage hysteresis <sup>(2)</sup> |                                                 | 200                               |     |                      | mV   |

| V <sub>hys</sub> | IO FT Schmitt trigger voltage<br>hysteresis <sup>(2)</sup>    |                                                 | 5% V <sub>DD</sub> <sup>(3)</sup> |     |                      | mV   |

| 1                | Input leakage current <sup>(4)</sup>                          | $V_{SS} \le V_{IN} \le V_{DD}$<br>Standard I/Os |                                   |     | ±1                   |      |

| l <sub>lkg</sub> | input leakage current V                                       | V <sub>IN</sub> = 5 V<br>I/O FT                 |                                   |     | 3                    | μA   |

| R <sub>PU</sub>  | Weak pull-up equivalent resistor <sup>(5)</sup>               | $V_{IN} = V_{SS}$                               | 30                                | 40  | 50                   | kΩ   |

| R <sub>PD</sub>  | Weak pull-down equivalent resistor <sup>(5)</sup>             | $V_{IN} = V_{DD}$                               | 30                                | 40  | 50                   | kΩ   |

| C <sub>IO</sub>  | I/O pin capacitance                                           |                                                 |                                   | 5   |                      | pF   |

Table 34.I/O static characteristics

1. FT = Five-volt tolerant.

2. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization, not tested in production.

- 3. With a minimum of 100 mV.

- 4. Leakage could be higher than max. if negative current is injected on adjacent pins.

- 5. Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This MOS/NMOS contribution to the series resistance is minimum (~10% order).

All I/Os are CMOS and TTL compliant (no software configuration required), their characteristics consider the most strict CMOS-technology or TTL parameters:

- For V<sub>IH</sub>:

- if V<sub>DD</sub> is in the [2.00 V 3.08 V] range: CMOS characteristics but TTL included

- if V<sub>DD</sub> is in the [3.08 V 3.60 V] range: TTL characteristics but CMOS included

- For V<sub>IL</sub>:

- if V<sub>DD</sub> is in the [2.00 V 2.28 V] range: TTL characteristics but CMOS included

- if V<sub>DD</sub> is in the [2.28 V 3.60 V] range: CMOS characteristics but TTL included

### Equation 1: R<sub>AIN</sub> max formula:

$$R_{AIN} < \frac{I_{S}}{f_{ADC} \times C_{ADC} \times ln(2^{N+2})} - R_{ADC}$$

The formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. Here N = 12 (from 12-bit resolution).

### Table 46. $R_{AIN}$ max for $f_{ADC} = 14 \text{ MHz}^{(1)}$

| T <sub>s</sub> (cycles) | t <sub>S</sub> (μs) | R <sub>AIN</sub> max (kΩ) |

|-------------------------|---------------------|---------------------------|

| 1.5                     | 0.11                | 1.2                       |

| 7.5                     | 0.54                | 10                        |

| 13.5                    | 0.96                | 19                        |

| 28.5                    | 2.04                | 41                        |

| 41.5                    | 2.96                | 60                        |

| 55.5                    | 3.96                | 80                        |

| 71.5                    | 5.11                | 104                       |

| 239.5                   | 17.1                | 350                       |

1. Based on characterization, not tested in production.

# Table 47. ADC accuracy - limited test conditions<sup>(1) (2)</sup>

| Symbol | Parameter                    | Test conditions                                                   | Тур  | Max <sup>(3)</sup> | Unit |

|--------|------------------------------|-------------------------------------------------------------------|------|--------------------|------|

| ET     | Total unadjusted error       | f <sub>PCLK2</sub> = 56 MHz,                                      | ±1.3 | ±2                 |      |

| EO     | Offset error                 | $f_{ADC} = 14 \text{ MHz}, \text{ R}_{AIN} < 10 \text{ k}\Omega,$ | ±1   | ±1.5               |      |

| EG     | Gain error                   | V <sub>DDA</sub> = 3 V to 3.6 V<br>T₄ = 25 °C                     | ±0.5 | ±1.5               | LSB  |

| ED     | Differential linearity error | Measurements made after                                           | ±0.7 | ±1                 |      |

| EL     | Integral linearity error     | ADC calibration                                                   | ±0.8 | ±1.5               |      |

1. ADC DC accuracy values are measured after internal calibration.

ADC Accuracy vs. Negative Injection Current: Injecting negative current on any of the standard (non-robust) analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to standard analog pins which may potentially inject negative current. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in *Section 5.3.12* does not affect the ADC accuracy.

3. Based on characterization, not tested in production.

# 6 Package characteristics

# 6.1 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

1. Non solder mask defined (NSMD) pads are recommended

2. 4 to 6 mils solder paste screen printing process

## 6.2.2 Selecting the product temperature range

When ordering the microcontroller, the temperature range is specified in the ordering information scheme shown in *Table 57: Ordering information scheme*.

Each temperature range suffix corresponds to a specific guaranteed ambient temperature at maximum dissipation and, to a specific maximum junction temperature.

As applications do not commonly use the STM32F103xx at maximum dissipation, it is useful to calculate the exact power consumption and junction temperature to determine which temperature range will be best suited to the application.

The following examples show how to calculate the temperature range needed for a given application.

#### **Example 1: High-performance application**

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax} = 82$  °C (measured according to JESD51-2), I<sub>DDmax</sub> = 50 mA, V<sub>DD</sub> = 3.5 V, maximum 20 I/Os used at the same time in output at low level with I<sub>OL</sub> = 8 mA, V<sub>OL</sub>= 0.4 V and maximum 8 I/Os used at the same time in output at low level with I<sub>OL</sub> = 20 mA, V<sub>OL</sub>= 1.3 V

$P_{INTmax} = 50 \text{ mA} \times 3.5 \text{ V} = 175 \text{ mW}$

$P_{IOmax} = 20 \times 8 \text{ mA} \times 0.4 \text{ V} + 8 \times 20 \text{ mA} \times 1.3 \text{ V} = 272 \text{ mW}$

This gives:  $P_{INTmax} = 175 \text{ mW}$  and  $P_{IOmax} = 272 \text{ mW}$ :

$P_{Dmax} = 175 + 272 = 447 \text{ mW}$

Thus:  $P_{Dmax} = 447 \text{ mW}$

Using the values obtained in *Table 56* T<sub>Jmax</sub> is calculated as follows:

- For LQFP100, 46 °C/W

T<sub>Jmax</sub> = 82 °C + (46 °C/W × 447 mW) = 82 °C + 20.6 °C = 102.6 °C

This is within the range of the suffix 6 version parts ( $-40 < T_J < 105 \text{ °C}$ ).

In this case, parts must be ordered at least with the temperature range suffix 6 (see *Table 57: Ordering information scheme*).

#### **Example 2: High-temperature application**

Using the same rules, it is possible to address applications that run at high ambient temperatures with a low dissipation, as long as junction temperature  $T_J$  remains within the specified range.

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax} = 115 \text{ °C}$  (measured according to JESD51-2),  $I_{DDmax} = 20 \text{ mA}$ ,  $V_{DD} = 3.5 \text{ V}$ , maximum 20 I/Os used at the same time in output at low level with  $I_{OL} = 8 \text{ mA}$ ,  $V_{OL} = 0.4 \text{ V}$   $P_{INTmax} = 20 \text{ mA} \times 3.5 \text{ V} = 70 \text{ mW}$   $P_{IOmax} = 20 \times 8 \text{ mA} \times 0.4 \text{ V} = 64 \text{ mW}$ This gives:  $P_{INTmax} = 70 \text{ mW}$  and  $P_{IOmax} = 64 \text{ mW}$ :  $P_{Dmax} = 70 + 64 = 134 \text{ mW}$ Thus:  $P_{Dmax} = 134 \text{ mW}$

| Date        | Revision | n Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 22-Nov-2007 | 4        | Document status promoted from preliminary data to datasheet.<br>The STM32F103xx is USB certified. Small text changes.<br><i>Power supply schemes on page</i> 13 modified. Number of<br>communication peripherals corrected for STM32F103Xx and number of<br>GPIOs corrected for LQFP package in Table 2: STM32F103xx medium<br>density device features and peripheral counts.<br>Main function and default alternate function modified for PC14 and<br>PC15 in, <i>Note 5</i> added and Remap column added in Table 5: Medium-<br>density STM32F103xx pin definitions.<br>VpD-Vss ratings and Note 1 modified in Table 6: Voltage<br>characteristics, <i>Note</i> 1 modified in Table 7: Current characteristics.<br><i>Note</i> 1 and <i>Note</i> 2 added in Table 11: Embedded reset and power<br>control block characteristics.<br>I <sub>DD</sub> value at 72 MHz with peripherals enabled modified in Table 14:<br><i>Maximum current consumption in Run mode, code with data</i><br>processing running from RAM.<br>I <sub>DD</sub> value at 72 MHz with peripherals enabled modified in Table 15:<br><i>Maximum current consumption in Sleep mode, code running from</i><br><i>Flash or RAM on page</i> 41.<br>I <sub>DD</sub> vBAT typical value at 2.4 V modified and I <sub>DD</sub> vBAT maximum values<br>added in Table 16: Typical and maximum current consumptions in <i>Slop</i><br>and Standby modes. Note added in Table 17 on page 44 and Table 18<br>on page 45. ADC1 and ADC2 consumption.<br>Table 19: Peripheral current consumption.<br>SU(HSE) and I <sub>SU(LSE)</sub> conditions modified in Table 22 and Table 23,<br>respectively.<br>Maximum values removed from Table 26: Low-power mode wakeup<br>timings. t <sub>RET</sub> conditions modified in Table 22: Flash memory endurance<br>and data retention. Figure 12: Power supply scheme corrected.<br><i>Figure</i> 17: Typical current consumption in Slop mode with regulator in<br>Low-power mode versus temperature at V <sub>DD</sub> = 3.3 V and 3.6 V added.<br>Note removed below <i>Figure</i> 26: SPI timing diagram - slave mode and<br><i>CPHA</i> = 0. Note added below Figure 27: SPI timing diagram - slave<br>mode and <i>CPHA</i> = 1 <sup>(1)</sup> .<br>Details on unused pins removed from General input/output<br>characteristics on page 56. |  |

# Table 58. Document revision history (continued)

| Date        | Revision                                                                                                                                                                                                                                                                                                                                                                                                                      | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 21-Jul-2008 | 8                                                                                                                                                                                                                                                                                                                                                                                                                             | Power supply supervisor updated and $V_{DDA}$ added to Table 9: General<br>operating conditions.Capacitance modified in Figure 12: Power supply scheme on page 33.Table notes revised in Section 5: Electrical characteristics.Table 16: Typical and maximum current consumptions in Stop and<br>Standby modes modified.Data added to Table 16: Typical and maximum current consumptions in<br>Stop and Standby modes and Table 21: Typical current consumption in<br>Standby mode removed.fHSE_ext modified in Table 20: High-speed external user clock<br>characteristics on page 47. fPLL_IN modified in Table 27: PLL<br>characteristics on page 52.Minimum SDA and SCL fall time value for Fast mode removed from<br>Table 39: I <sup>2</sup> C characteristics on page 61, note 1 modified.th(NSS) modified in Table 41: SPI characteristics on page 63 and<br>Figure 26: SPI timing diagram - slave mode and CPHA = 0 on page 64.CADC modified in Table 45: ADC characteristics on page 67 and<br>Figure 31: Typical connection diagram using the ADC modified.Typical S_temp value removed from Table 49: TS characteristics on<br>page 71.LQFP48 package specifications updated (see Table 55 and Table 45),<br>Section 6: Package characteristics revised.Axx option removed from Table 57: Ordering information scheme on<br>page 84.Small text changes. |  |  |

| 22-Sep-2008 | STM32F103x6 part numbers removed (see Table 57: Ordering information scheme). Small text changes.         General-purpose timers (TIMx) and Advanced-control timer (TIM1) page 15 updated.         Notes updated in Table 5: Medium-density STM32F103xx pin definitions on page 26.         Note 2 modified below Table 6: Voltage characteristics on page 34, I∆V <sub>DDx</sub> I min and I∆V <sub>DDx</sub> I min removed. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

# Table 58. Document revision history (continued)