Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, Motor Control PWM, PDR, POR, PVD, PWM, Temp Sensor, WDT          |

| Number of I/O              | 51                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 20K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-TFBGA                                                              |

| Supplier Device Package    | 64-TFBGA (5x5)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f103rbh6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 5  | Elect | rical ch  | aracteristics                                          | 32   |

|----|-------|-----------|--------------------------------------------------------|------|

|    | 5.1   | Parame    | eter conditions                                        | 32   |

|    |       | 5.1.1     | Minimum and maximum values                             | 32   |

|    |       | 5.1.2     | Typical values                                         | 32   |

|    |       | 5.1.3     | Typical curves                                         | 32   |

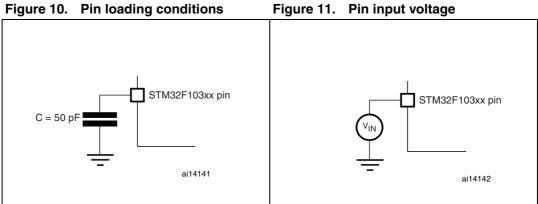

|    |       | 5.1.4     | Loading capacitor                                      | 32   |

|    |       | 5.1.5     | Pin input voltage                                      | 32   |

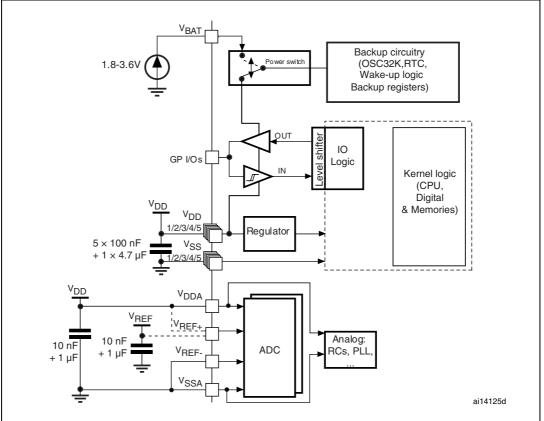

|    |       | 5.1.6     | Power supply scheme                                    | 33   |

|    |       | 5.1.7     | Current consumption measurement                        | 34   |

|    | 5.2   | Absolut   | e maximum ratings                                      | 34   |

|    | 5.3   | Operati   | ng conditions                                          | 35   |

|    |       | 5.3.1     | General operating conditions                           | 35   |

|    |       | 5.3.2     | Operating conditions at power-up / power-down          | 36   |

|    |       | 5.3.3     | Embedded reset and power control block characteristics | 36   |

|    |       | 5.3.4     | Embedded reference voltage                             | 38   |

|    |       | 5.3.5     | Supply current characteristics                         | 38   |

|    |       | 5.3.6     | External clock source characteristics                  | 47   |

|    |       | 5.3.7     | Internal clock source characteristics                  | 50   |

|    |       | 5.3.8     | PLL characteristics                                    | 52   |

|    |       | 5.3.9     | Memory characteristics                                 | 52   |

|    |       | 5.3.10    | EMC characteristics                                    | 53   |

|    |       | 5.3.11    | Absolute maximum ratings (electrical sensitivity)      | 55   |

|    |       | 5.3.12    | I/O port characteristics                               | 56   |

|    |       | 5.3.13    | NRST pin characteristics                               | 59   |

|    |       | 5.3.14    | TIM timer characteristics                              | 60   |

|    |       | 5.3.15    | Communications interfaces                              | 61   |

|    |       | 5.3.16    | CAN (controller area network) interface                | 66   |

|    |       | 5.3.17    | 12-bit ADC characteristics                             | 67   |

|    |       | 5.3.18    | Temperature sensor characteristics                     | 71   |

| 6  | Pack  | age cha   | racteristics                                           | 72   |

|    | 6.1   | Packag    | e mechanical data                                      | 72   |

|    | 6.2   | Therma    | Il characteristics                                     | 81   |

|    |       | 6.2.1     | Reference document                                     | 81   |

|    |       | 6.2.2     | Selecting the product temperature range                |      |

| 7  | Orde  | ring info | ormation scheme                                        | 84   |

| 57 |       |           | Doc ID 13587 Rev 10                                    | 3/91 |

| 8 | <b>Revision history</b> |  | 5 |

|---|-------------------------|--|---|

|---|-------------------------|--|---|

| Figure 44. | LQFP48, 48-pin low-profile quad flat package outline | 80 |

|------------|------------------------------------------------------|----|

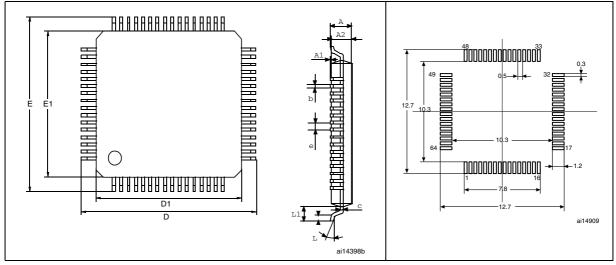

| Figure 45. | Recommended footprint <sup>(1)</sup>                 | 80 |

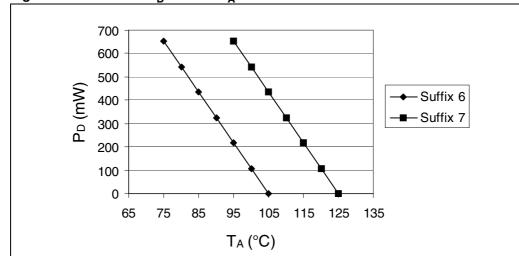

| Figure 46. | LQFP100 P <sub>D</sub> max vs. T <sub>A</sub>        | 83 |

57

# 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32F103x8 and STM32F103xB medium-density performance line microcontrollers. For more details on the whole STMicroelectronics STM32F103xx family, please refer to *Section 2.2: Full compatibility throughout the family*.

The medium-density STM32F103xx datasheet should be read in conjunction with the low-, medium- and high-density STM32F10xxx reference manual. The reference and Flash programming manuals are both available from the STMicroelectronics website www.st.com.

For information on the Cortex<sup>™</sup>-M3 core please refer to the Cortex<sup>™</sup>-M3 Technical Reference Manual, available from the www.arm.com website at the following address: http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.ddi0337e/.

# 2 Description

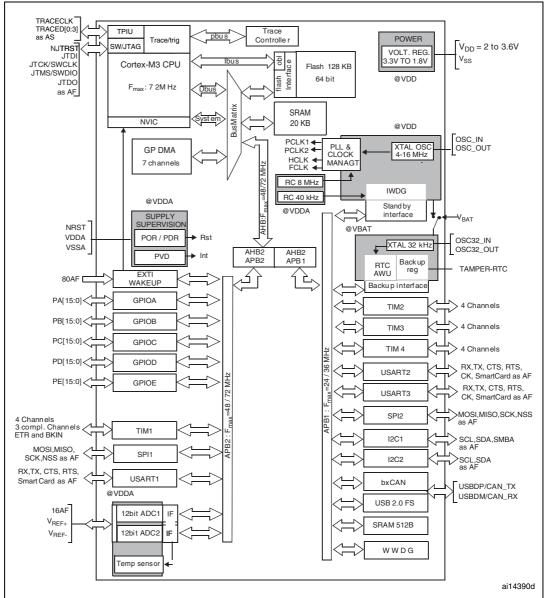

The STM32F103x8 and STM32F103xB performance line family incorporates the highperformance ARM Cortex<sup>™</sup>-M3 32-bit RISC core operating at a 72 MHz frequency, highspeed embedded memories (Flash memory up to 128 Kbytes and SRAM up to 20 Kbytes), and an extensive range of enhanced I/Os and peripherals connected to two APB buses. All devices offer two 12-bit ADCs, three general purpose 16-bit timers plus one PWM timer, as well as standard and advanced communication interfaces: up to two I<sup>2</sup>Cs and SPIs, three USARTs, an USB and a CAN.

The STM32F103xx medium-density performance line family operates from a 2.0 to 3.6 V power supply. It is available in both the -40 to +85 °C temperature range and the -40 to +105 °C extended temperature range. A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F103xx medium-density performance line family includes devices in six different package types: from 36 pins to 100 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

These features make the STM32F103xx medium-density performance line microcontroller family suitable for a wide range of applications:

- Motor drive and application control

- Medical and handheld equipment

- PC peripherals gaming and GPS platforms

- Industrial applications: PLC, inverters, printers, and scanners

- Alarm systems, Video intercom, and HVAC

*Figure 1* shows the general block diagram of the device family.

### 2.3.13 DMA

The flexible 7-channel general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The DMA controller supports circular buffer management avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with support for software trigger on each channel. Configuration is made by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: SPI, I<sup>2</sup>C, USART, general-purpose and advanced-control timers TIMx and ADC.

# 2.3.14 RTC (real-time clock) and backup registers

The RTC and the backup registers are supplied through a switch that takes power either on  $V_{DD}$  supply when present or through the  $V_{BAT}$  pin. The backup registers are ten 16-bit registers used to store 20 bytes of user application data when  $V_{DD}$  power is not present.

The real-time clock provides a set of continuously running counters which can be used with suitable software to provide a clock calendar function, and provides an alarm interrupt and a periodic interrupt. It is clocked by a 32.768 kHz external crystal, resonator or oscillator, the internal low-power RC oscillator or the high-speed external clock divided by 128. The internal low-power RC has a typical frequency of 40 kHz. The RTC can be calibrated using an external 512 Hz output to compensate for any natural crystal deviation. The RTC features a 32-bit programmable counter for long-term measurement using the Compare register to generate an alarm. A 20-bit prescaler is used for the time base clock and is by default configured to generate a time base of 1 second from a clock at 32.768 kHz.

# 2.3.15 Timers and watchdogs

The medium-density STM32F103xx performance line devices include an advanced-control timer, three general-purpose timers, two watchdog timers and a SysTick timer.

*Table 4* compares the features of the advanced-control and general-purpose timers.

| Timer                  | mer Counter counter type |                         |                                       |     | Capture/compare<br>channels | Complementary<br>outputs |  |

|------------------------|--------------------------|-------------------------|---------------------------------------|-----|-----------------------------|--------------------------|--|

| TIM1                   | 16-bit                   | Up,<br>down,<br>up/down | Any integer<br>between 1<br>and 65536 | Yes | 4                           | Yes                      |  |

| TIM2,<br>TIM3,<br>TIM4 | 16-bit                   | Up,<br>down,<br>up/down | Any integer<br>between 1<br>and 65536 | Yes | 4                           | No                       |  |

Table 4.Timer feature comparison

#### Advanced-control timer (TIM1)

The advanced-control timer (TIM1) can be seen as a three-phase PWM multiplexed on 6 channels. It has complementary PWM outputs with programmable inserted dead-times. It

can also be seen as a complete general-purpose timer. The 4 independent channels can be used for

- Input capture

- Output compare

- PWM generation (edge- or center-aligned modes)

- One-pulse mode output

If configured as a general-purpose 16-bit timer, it has the same features as the TIMx timer. If configured as the 16-bit PWM generator, it has full modulation capability (0-100%).

In debug mode, the advanced-control timer counter can be frozen and the PWM outputs disabled to turn off any power switch driven by these outputs.

Many features are shared with those of the general-purpose TIM timers which have the same architecture. The advanced-control timer can therefore work together with the TIM timers via the Timer Link feature for synchronization or event chaining.

### General-purpose timers (TIMx)

There are up to three synchronizable general-purpose timers embedded in the STM32F103xx performance line devices. These timers are based on a 16-bit auto-reload up/down counter, a 16-bit prescaler and feature 4 independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 12 input captures/output compares/PWMs on the largest packages.

The general-purpose timers can work together with the advanced-control timer via the Timer Link feature for synchronization or event chaining. Their counter can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs. They all have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

#### Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 40 kHz internal RC and as it operates independently of the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes. The counter can be frozen in debug mode.

#### Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

Figure 1. STM32F103xx performance line block diagram

1.  $T_A = -40$  °C to +105 °C (junction temperature up to 125 °C).

2. AF = alternate function on I/O port pin.

# Pinouts and pin description

|          |        | Pin               |        |         |          | y 51M32F103XX p                    |                     | (2)                        |                                                  | Alternate functions                                                               |       |  |

|----------|--------|-------------------|--------|---------|----------|------------------------------------|---------------------|----------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------|-------|--|

| LFBGA100 | LQFP48 | TFBGA64           | LQFP64 | LQFP100 | VFQFPN36 | Pin name                           | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                                           | Remap |  |

| A3       | -      |                   | -      | 1       | -        | PE2                                | I/O                 | FT                         | PE2                                              | TRACECK                                                                           |       |  |

| B3       | -      |                   | -      | 2       | -        | PE3                                | I/O                 | FT                         | PE3                                              | TRACED0                                                                           |       |  |

| C3       | -      |                   | -      | 3       | -        | PE4                                | I/O                 | FT                         | PE4                                              | TRACED1                                                                           |       |  |

| D3       | -      |                   | -      | 4       | -        | PE5                                | I/O                 | FT                         | PE5                                              | TRACED2                                                                           |       |  |

| E3       | -      |                   | -      | 5       | -        | PE6                                | I/O                 | FT                         | PE6                                              | TRACED3                                                                           |       |  |

| B2       | 1      | B2                | 1      | 6       | -        | V <sub>BAT</sub>                   | S                   |                            | V <sub>BAT</sub>                                 |                                                                                   |       |  |

| A2       | 2      | A2                | 2      | 7       | -        | PC13-TAMPER-<br>RTC <sup>(4)</sup> | I/O                 |                            | PC13 <sup>(5)</sup>                              | TAMPER-RTC                                                                        |       |  |

| A1       | 3      | A1                | 3      | 8       | -        | PC14-OSC32_IN <sup>(4)</sup>       | I/O                 |                            | PC14 <sup>(5)</sup>                              | OSC32_IN                                                                          |       |  |

| B1       | 4      | B1                | 4      | 9       | -        | PC15-<br>OSC32_OUT <sup>(4)</sup>  | I/O                 |                            | PC15 <sup>(5)</sup>                              | OSC32_OUT                                                                         |       |  |

| C2       | -      | -                 | -      | 10      | -        | V <sub>SS_5</sub>                  | S                   |                            | V <sub>SS_5</sub>                                |                                                                                   |       |  |

| D2       | -      | -                 | -      | 11      | -        | V <sub>DD_5</sub>                  | S                   |                            | $V_{DD_5}$                                       |                                                                                   |       |  |

| C1       | 5      | C1                | 5      | 12      | 2        | OSC_IN                             | I                   |                            | OSC_IN                                           |                                                                                   |       |  |

| D1       | 6      | D1                | 6      | 13      | 3        | OSC_OUT                            | 0                   |                            | OSC_OUT                                          |                                                                                   |       |  |

| E1       | 7      | E1                | 7      | 14      | 4        | NRST                               | I/O                 |                            | NRST                                             |                                                                                   |       |  |

| F1       | -      | E3                | 8      | 15      | -        | PC0                                | I/O                 |                            | PC0                                              | ADC12_IN10                                                                        |       |  |

| F2       | -      | E2                | 9      | 16      | -        | PC1                                | I/O                 |                            | PC1                                              | ADC12_IN11                                                                        |       |  |

| E2       | -      | F2                | 10     | 17      | -        | PC2                                | I/O                 |                            | PC2                                              | ADC12_IN12                                                                        |       |  |

| F3       | -      | _(6)              | 11     | 18      | -        | PC3                                | I/O                 |                            | PC3                                              | ADC12_IN13                                                                        |       |  |

| G1       | 8      | F1                | 12     | 19      | 5        | V <sub>SSA</sub>                   | S                   |                            | V <sub>SSA</sub>                                 |                                                                                   |       |  |

| H1       | -      | -                 | I      | 20      | -        | V <sub>REF-</sub>                  | S                   |                            | V <sub>REF-</sub>                                |                                                                                   |       |  |

| J1       | -      | G1 <sup>(6)</sup> | I      | 21      | -        | V <sub>REF+</sub>                  | S                   |                            | $V_{REF+}$                                       |                                                                                   |       |  |

| K1       | 9      | H1                | 13     | 22      | 6        | V <sub>DDA</sub>                   | S                   |                            | $V_{DDA}$                                        |                                                                                   |       |  |

| G2       | 10     | G2                | 14     | 23      | 7        | PA0-WKUP                           | I/O                 |                            | PA0                                              | WKUP/<br>USART2_CTS <sup>(7)</sup> /<br>ADC12_IN0/<br>TIM2_CH1_ETR <sup>(7)</sup> |       |  |

| H2       | 11     | H2                | 15     | 24      | 8        | PA1                                | I/O                 |                            | PA1                                              | USART2_RTS <sup>(7)</sup> /<br>ADC12_IN1/<br>TIM2_CH2 <sup>(7)</sup>              |       |  |

| J2       | 12     | F3                | 16     | 25      | 9        | PA2                                | I/O                 |                            | PA2                                              | USART2_TX <sup>(7)</sup> /<br>ADC12_IN2/<br>TIM2_CH3 <sup>(7)</sup>               |       |  |

# Table 5. Medium-density STM32F103xx pin definitions

|          |        | Pin     | IS     |         |          |                   |                     | (2)                        |                                                  | Alternate f                                                          | unctions  |

|----------|--------|---------|--------|---------|----------|-------------------|---------------------|----------------------------|--------------------------------------------------|----------------------------------------------------------------------|-----------|

| LFBGA100 | LQFP48 | TFBGA64 | LQFP64 | LQFP100 | VFQFPN36 | Pin name          | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                              | Remap     |

| K2       | 13     | G3      | 17     | 26      | 10       | PA3               | I/O                 |                            | PA3                                              | USART2_RX <sup>(7)</sup> /<br>ADC12_IN3/<br>TIM2_CH4 <sup>(7)</sup>  |           |

| E4       | -      | C2      | 18     | 27      | -        | V <sub>SS_4</sub> | S                   |                            | $V_{SS_4}$                                       |                                                                      |           |

| F4       | -      | D2      | 19     | 28      | -        | V <sub>DD_4</sub> | S                   |                            | V <sub>DD_4</sub>                                |                                                                      |           |

| G3       | 14     | НЗ      | 20     | 29      | 11       | PA4               | I/O                 |                            | PA4                                              | SPI1_NSS <sup>(7)</sup> /<br>USART2_CK <sup>(7)</sup> /<br>ADC12_IN4 |           |

| НЗ       | 15     | F4      | 21     | 30      | 12       | PA5               | I/O                 |                            | PA5                                              | SPI1_SCK <sup>(7)</sup> /<br>ADC12_IN5                               |           |

| JЗ       | 16     | G4      | 22     | 31      | 13       | PA6               | I/O                 |                            | PA6                                              | SPI1_MISO <sup>(7)</sup> /<br>ADC12_IN6/<br>TIM3_CH1 <sup>(7)</sup>  | TIM1_BKIN |

| КЗ       | 17     | H4      | 23     | 32      | 14       | PA7               | I/O                 |                            | PA7                                              | SPI1_MOSI <sup>(7)</sup> /<br>ADC12_IN7/<br>TIM3_CH2 <sup>(7)</sup>  | TIM1_CH1N |

| G4       | -      | H5      | 24     | 33      |          | PC4               | I/O                 |                            | PC4                                              | ADC12_IN14                                                           |           |

| H4       | -      | H6      | 25     | 34      |          | PC5               | I/O                 |                            | PC5                                              | ADC12_IN15                                                           |           |

| J4       | 18     | F5      | 26     | 35      | 15       | PB0               | I/O                 |                            | PB0                                              | ADC12_IN8/<br>TIM3_CH3 <sup>(7)</sup>                                | TIM1_CH2N |

| K4       | 19     | G5      | 27     | 36      | 16       | PB1               | I/O                 |                            | PB1                                              | ADC12_IN9/<br>TIM3_CH4 <sup>(7)</sup>                                | TIM1_CH3N |

| G5       | 20     | G6      | 28     | 37      | 17       | PB2               | I/O                 | FT                         | PB2/BOOT1                                        |                                                                      |           |

| H5       | -      | -       | -      | 38      | -        | PE7               | I/O                 | FT                         | PE7                                              |                                                                      | TIM1_ETR  |

| J5       | -      | -       | -      | 39      | -        | PE8               | I/O                 | FT                         | PE8                                              |                                                                      | TIM1_CH1N |

| K5       | -      | -       | -      | 40      | -        | PE9               | I/O                 | FT                         | PE9                                              |                                                                      | TIM1_CH1  |

| G6       | -      | -       | -      | 41      | -        | PE10              | I/O                 | FT                         | PE10                                             |                                                                      | TIM1_CH2N |

| H6       | -      | -       | -      | 42      | -        | PE11              | I/O                 | FT                         | PE11                                             |                                                                      | TIM1_CH2  |

| J6       | -      | -       | -      | 43      | -        | PE12              | I/O                 | FT                         | PE12                                             |                                                                      | TIM1_CH3N |

| K6       | -      | -       | -      | 44      | -        | PE13              | I/O                 | FT                         | PE13                                             |                                                                      | TIM1_CH3  |

| G7       | -      | •       | -      | 45      | -        | PE14              | I/O                 | FT                         | PE14                                             |                                                                      | TIM1_CH4  |

| H7       | -      | -       | -      | 46      | -        | PE15              | I/O                 | FT                         | PE15                                             |                                                                      | TIM1_BKIN |

| J7       | 21     | G7      | 29     | 47      | -        | PB10              | I/O                 | FT                         | PB10                                             | I2C2_SCL/<br>USART3_TX <sup>(7)</sup>                                | TIM2_CH3  |

| K7       | 22     | H7      | 30     | 48      | -        | PB11              | I/O                 | FT                         | PB11                                             | I2C2_SDA/<br>USART3_RX <sup>(7)</sup>                                | TIM2_CH4  |

| E7       | 23     | D6      | 31     | 49      | 18       | V <sub>SS_1</sub> | S                   |                            | $V_{SS_1}$                                       |                                                                      |           |

| Table 5. | Medium-density | y STM32F103xx | pin definitions | (continued) |  |

|----------|----------------|---------------|-----------------|-------------|--|

|----------|----------------|---------------|-----------------|-------------|--|

|          |        | Pin     |        |         |          | y 51M32F103XX p   |                     |                            | •                                                | Alternate functions                                                                |                          |  |

|----------|--------|---------|--------|---------|----------|-------------------|---------------------|----------------------------|--------------------------------------------------|------------------------------------------------------------------------------------|--------------------------|--|

| LFBGA100 | LQFP48 | TFBGA64 | LQFP64 | LQFP100 | VFQFPN36 | Pin name          | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                                            | Remap                    |  |

| F7       | 24     | E6      | 32     | 50      | 19       | V <sub>DD_1</sub> | S                   |                            | $V_{DD_1}$                                       |                                                                                    |                          |  |

| K8       | 25     | H8      | 33     | 51      | -        | PB12              | I/O                 | FT                         | PB12                                             | SPI2_NSS/<br>I2C2_SMBAI/<br>USART3_CK <sup>(7)</sup> /<br>TIM1_BKIN <sup>(7)</sup> |                          |  |

| J8       | 26     | G8      | 34     | 52      | -        | PB13              | I/O                 | FT                         | PB13                                             | SPI2_SCK/<br>USART3_CTS <sup>(7)</sup> /<br>TIM1_CH1N <sup>(7)</sup>               |                          |  |

| H8       | 27     | F8      | 35     | 53      | -        | PB14              | I/O                 | FT                         | PB14                                             | SPI2_MISO/<br>USART3_RTS <sup>(7)</sup><br>TIM1_CH2N <sup>(7)</sup>                |                          |  |

| G8       | 28     | F7      | 36     | 54      | -        | PB15              | I/O                 | FT                         | PB15                                             | SPI2_MOSI/<br>TIM1_CH3N <sup>(7)</sup>                                             |                          |  |

| K9       | -      | -       | -      | 55      | -        | PD8               | I/O                 | FT                         | PD8                                              |                                                                                    | USART3_TX                |  |

| J9       | -      | -       | -      | 56      | -        | PD9               | I/O                 | FT                         | PD9                                              |                                                                                    | USART3_RX                |  |

| H9       | -      | -       | -      | 57      | -        | PD10              | I/O                 | FT                         | PD10                                             |                                                                                    | USART3_CK                |  |

| G9       | -      | -       | -      | 58      | -        | PD11              | I/O                 | FT                         | PD11                                             |                                                                                    | USART3_CTS               |  |

| K10      | -      | -       | -      | 59      | -        | PD12              | I/O                 | FT                         | PD12                                             |                                                                                    | TIM4_CH1 /<br>USART3_RTS |  |

| J10      | -      | -       | -      | 60      | -        | PD13              | I/O                 | FT                         | PD13                                             |                                                                                    | TIM4_CH2                 |  |

| H10      | -      | -       | -      | 61      | -        | PD14              | I/O                 | FT                         | PD14                                             |                                                                                    | TIM4_CH3                 |  |

| G10      | -      | -       | -      | 62      | -        | PD15              | I/O                 | FT                         | PD15                                             |                                                                                    | TIM4_CH4                 |  |

| F10      | -      | F6      | 37     | 63      | -        | PC6               | I/O                 | FT                         | PC6                                              |                                                                                    | TIM3_CH1                 |  |

| E10      |        | E7      | 38     | 64      | -        | PC7               | I/O                 | FT                         | PC7                                              |                                                                                    | TIM3_CH2                 |  |

| F9       |        | E8      | 39     | 65      | -        | PC8               | I/O                 | FT                         | PC8                                              |                                                                                    | TIM3_CH3                 |  |

| E9       | -      | D8      | 40     | 66      | -        | PC9               | I/O                 | FT                         | PC9                                              |                                                                                    | TIM3_CH4                 |  |

| D9       | 29     | D7      | 41     | 67      | 20       | PA8               | I/O                 | FT                         | PA8                                              | USART1_CK/<br>TIM1_CH1 <sup>(7)</sup> /MCO                                         |                          |  |

| C9       | 30     | C7      | 42     | 68      | 21       | PA9               | I/O                 | FT                         | PA9                                              | USART1_TX <sup>(7)</sup> /<br>TIM1_CH2 <sup>(7)</sup>                              |                          |  |

| D10      | 31     | C6      | 43     | 69      | 22       | PA10              | I/O                 | FT                         | PA10                                             | USART1_RX <sup>(7)</sup> /<br>TIM1_CH3 <sup>(7)</sup>                              |                          |  |

| C10      | 32     | C8      | 44     | 70      | 23       | PA11              | I/O                 | FT                         | PA11                                             | USART1_CTS/<br>CANRX <sup>(7)</sup> / USBDM<br>TIM1_CH4 <sup>(7)</sup>             |                          |  |

| B10      | 33     | B8      | 45     | 71      | 24       | PA12              | I/O                 | FT                         | PA12                                             | USART1_RTS/<br>CANTX <sup>(7)</sup> //USBDP<br>TIM1_ETR <sup>(7)</sup>             |                          |  |

# Table 5. Medium-density STM32F103xx pin definitions (continued)

# Figure 10. Pin loading conditions

#### Power supply scheme 5.1.6

| Table 9.       | General operating conditio                                                               | ins (continued)                                |     |     |            |  |

|----------------|------------------------------------------------------------------------------------------|------------------------------------------------|-----|-----|------------|--|

| Symbol         | Parameter                                                                                | Conditions                                     | Min | Max | Unit       |  |

|                |                                                                                          | LFBGA100                                       |     | 454 |            |  |

|                |                                                                                          | LQFP100                                        |     | 434 |            |  |

| Р              | Power dissipation at $T_A = 85 \text{ °C}$<br>for suffix 6 or $T_A = 105 \text{ °C}$ for | TFBGA64                                        |     | 308 | mW         |  |

| P <sub>D</sub> | suffix $7^{(3)}$                                                                         | LQFP64                                         |     | 444 | 11177      |  |

|                |                                                                                          | 363                                            |     |     |            |  |

|                |                                                                                          | VFQFPN36                                       |     |     |            |  |

|                | Ambient temperature for 6                                                                | Maximum power dissipation                      | -40 | 85  | °C         |  |

| Та             | suffix version                                                                           | Low power dissipation <sup>(4)</sup>           | -40 | 105 | C          |  |

| IA             | Ambient temperature for 7                                                                | Maximum power dissipation                      | -40 | 105 | °C         |  |

|                | suffix version                                                                           | x version Low power dissipation <sup>(4)</sup> |     | 125 | C          |  |

| TJ             | lunction tomporature range                                                               | 6 suffix version                               | -40 | 105 | ° <b>0</b> |  |

| IJ             | Junction temperature range                                                               | 7 suffix version                               | -40 | 125 | °C         |  |

Table 9. General operating conditions (continued)

1. When the ADC is used, refer to *Table 45: ADC characteristics*.

2. It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up and operation.

- If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>J</sub>max (see *Table 6.2: Thermal characteristics on page 81*).

- In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>J</sub>max (see Table 6.2: Thermal characteristics on page 81).

# 5.3.2 Operating conditions at power-up / power-down

Subject to general operating conditions for T<sub>A</sub>.

#### Table 10. Operating conditions at power-up / power-down

| Symbol           | Parameter                      | Conditions | Min | Max      | Unit  |

|------------------|--------------------------------|------------|-----|----------|-------|

| 1                | V <sub>DD</sub> rise time rate |            | 0   | $\infty$ | µs/V  |

| <sup>I</sup> VDD | V <sub>DD</sub> fall time rate |            | 20  | $\infty$ | μ5/ ν |

# 5.3.3 Embedded reset and power control block characteristics

The parameters given in *Table 11* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

# 5.3.4 Embedded reference voltage

The parameters given in *Table 12* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

| Symbol                                | Parameter                                                     | Conditions                                                               | Min  | Тур  | Max                 | Unit |

|---------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------|------|------|---------------------|------|

| V <sub>REFINT</sub>                   | Internal reference voltage                                    | $-40 \ ^{\circ}\text{C} < \text{T}_{\text{A}} < +105 \ ^{\circ}\text{C}$ | 1.16 | 1.20 | 1.26                | V    |

|                                       |                                                               | −40 °C < T <sub>A</sub> < +85 °C                                         | 1.16 | 1.20 | 1.24                | V    |

| T <sub>S_vrefint</sub> <sup>(1)</sup> | ADC sampling time when reading the internal reference voltage |                                                                          |      | 5.1  | 17.1 <sup>(2)</sup> | μs   |

Table 12. Embedded internal reference voltage

1. Shortest sampling time can be determined in the application by multiple iterations.

2. Guaranteed by design, not tested in production.

# 5.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 13: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to Dhrystone 2.1 code.

#### Maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load)

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time is adjusted to the f<sub>HCLK</sub> frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 48 MHz and 2 wait states above)

- Prefetch in ON (reminder: this bit must be set before clock setting and bus prescaling)

- When the peripherals are enabled  $f_{PCLK1} = f_{HCLK}/2$ ,  $f_{PCLK2} = f_{HCLK}$

The parameters given in *Table 13*, *Table 14* and *Table 15* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

| Symbol | Parameter                       | Conditions                          | f      | Max                    | Unit                    |      |

|--------|---------------------------------|-------------------------------------|--------|------------------------|-------------------------|------|

| Symbol | Farailleter                     |                                     | fHCLK  | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Onit |

|        |                                 |                                     | 72 MHz | 30                     | 32                      |      |

|        |                                 |                                     | 48 MHz | 20                     | 20.5                    |      |

|        |                                 | External clock <sup>(2)</sup> , all | 36 MHz | 15.5                   | 16                      |      |

|        | Supply current in<br>Sleep mode | peripherals enabled                 | 24 MHz | 11.5                   | 12                      |      |

|        |                                 |                                     | 16 MHz | 8.5                    | 9                       |      |

|        |                                 |                                     | 8 MHz  | 5.5                    | 6                       | mA   |

| IDD    |                                 |                                     | 72 MHz | 7.5                    | 8                       | ША   |

|        |                                 |                                     | 48 MHz | 6                      | 6.5                     |      |

|        |                                 | External clock <sup>(2)</sup> , all | 36 MHz | 5                      | 5.5                     |      |

|        |                                 | peripherals disabled                | 24 MHz | 4.5                    | 5                       |      |

|        |                                 |                                     | 16 MHz | 4                      | 4.5                     |      |

|        |                                 |                                     | 8 MHz  | 3                      | 4                       |      |

# Table 15. Maximum current consumption in Sleep mode, code running from Flash or RAM

1. based on characterization, tested in production at  $V_{\text{DD}\ \text{max}},\,f_{\text{HCLK}}$  max with peripherals enabled.

2. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

|                 |                      |                                   |                   | Туј                                       | o <sup>(1)</sup>         |      |

|-----------------|----------------------|-----------------------------------|-------------------|-------------------------------------------|--------------------------|------|

| Symbol          | Parameter            | Conditions                        | f <sub>HCLK</sub> | All peripherals<br>enabled <sup>(2)</sup> | All peripherals disabled | Unit |

|                 |                      |                                   | 72 MHz            | 14.4                                      | 5.5                      |      |

|                 |                      |                                   | 48 MHz            | 9.9                                       | 3.9                      |      |

|                 |                      |                                   | 36 MHz            | 7.6                                       | 3.1                      |      |

|                 |                      |                                   | 24 MHz            | 5.3                                       | 2.3                      |      |

|                 |                      |                                   | 16 MHz            | 3.8                                       | 1.8                      |      |

|                 |                      | External clock <sup>(3)</sup>     | 8 MHz             | 2.1                                       | 1.2                      |      |

|                 | Supply<br>current in |                                   | 4 MHz             | 1.6                                       | 1.1                      |      |

|                 |                      |                                   | 2 MHz             | 1.3                                       | 1                        |      |

|                 |                      |                                   | 1 MHz             | 1.11                                      | 0.98                     |      |

|                 |                      |                                   | 500 kHz           | 1.04                                      | 0.96                     |      |

|                 |                      |                                   | 125 kHz           | 0.98                                      | 0.95                     | mA   |

| I <sub>DD</sub> | Sleep mode           |                                   | 64 MHz            | 12.3                                      | 4.4                      | ШA   |

|                 |                      |                                   | 48 MHz            | 9.3                                       | 3.3                      |      |

|                 |                      |                                   | 36 MHz            | 7                                         | 2.5                      |      |

|                 |                      |                                   | 24 MHz            | 4.8                                       | 1.8                      |      |

|                 |                      | Running on high speed internal RC | 16 MHz            | 3.2                                       | 1.2                      |      |

|                 |                      | (HSI), AHB prescaler              | 8 MHz             | 1.6                                       | 0.6                      |      |

|                 |                      | used to reduce the<br>frequency   | 4 MHz             | 1                                         | 0.5                      |      |

|                 |                      | 1 - 7                             | 2 MHz             | 0.72                                      | 0.47                     |      |

|                 |                      |                                   | 1 MHz             | 0.56                                      | 0.44                     |      |

|                 |                      |                                   | 500 kHz           | 0.49                                      | 0.42                     |      |

|                 |                      |                                   | 125 kHz           | 0.43                                      | 0.41                     |      |

Table 18.Typical current consumption in Sleep mode, code running from Flash or<br/>RAM

1. Typical values are measures at  $T_A$  = 25 °C,  $V_{DD}$  = 3.3 V.

2. Add an additional power consumption of 0.8 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

3. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

# 5.3.6 External clock source characteristics

# High-speed external user clock generated from an external source

The characteristics given in *Table 20* result from tests performed using an high-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 9*.

|                                            | nigh speed external doer block bhaldetensilos       |                                                                   |              |     |                    |      |  |  |

|--------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------|--------------|-----|--------------------|------|--|--|

| Symbol                                     | Parameter                                           | Conditions                                                        | Min          | Тур | Max                | Unit |  |  |

| f <sub>HSE_ext</sub>                       | User external clock source frequency <sup>(1)</sup> |                                                                   | 0            | 8   | 25                 | MHz  |  |  |

| V <sub>HSEH</sub>                          | OSC_IN input pin high level voltage                 |                                                                   | $0.7 V_{DD}$ |     | V <sub>DD</sub>    | v    |  |  |

| V <sub>HSEL</sub>                          | OSC_IN input pin low level voltage                  |                                                                   | $V_{SS}$     |     | $0.3V_{\text{DD}}$ | v    |  |  |

| t <sub>w(HSE)</sub><br>t <sub>w(HSE)</sub> | OSC_IN high or low time <sup>(1)</sup>              |                                                                   | 16           |     |                    | ns   |  |  |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub> | OSC_IN rise or fall time <sup>(1)</sup>             |                                                                   |              |     | 20                 |      |  |  |

| C <sub>in(HSE)</sub>                       | OSC_IN input capacitance <sup>(1)</sup>             |                                                                   |              | 5   |                    | pF   |  |  |

| DuCy <sub>(HSE)</sub>                      | Duty cycle                                          |                                                                   | 45           |     | 55                 | %    |  |  |

| ΙL                                         | OSC_IN Input leakage current                        | $\begin{array}{c} V_{SS} \leq V_{IN} \leq V_{D} \\ D \end{array}$ |              |     | ±1                 | μA   |  |  |

Table 20.

High-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

#### Low-speed external user clock generated from an external source

The characteristics given in *Table 21* result from tests performed using an low-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 9*.

| Table 21. | Low-speed external user clock characteristics |

|-----------|-----------------------------------------------|

|-----------|-----------------------------------------------|

| Symbol                                     | Parameter                                              | Conditions                  | Min                | Тур    | Max                | Unit |  |  |

|--------------------------------------------|--------------------------------------------------------|-----------------------------|--------------------|--------|--------------------|------|--|--|

| f <sub>LSE_ext</sub>                       | User External clock source<br>frequency <sup>(1)</sup> |                             |                    | 32.768 | 1000               | kHz  |  |  |

| $V_{LSEH}$                                 | OSC32_IN input pin high level voltage                  |                             | 0.7V <sub>DD</sub> |        | V <sub>DD</sub>    | V    |  |  |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage                   |                             | V <sub>SS</sub>    |        | 0.3V <sub>DD</sub> | v    |  |  |

| t <sub>w(LSE)</sub><br>t <sub>w(LSE)</sub> | OSC32_IN high or low time <sup>(1)</sup>               |                             | 450                |        |                    | nc   |  |  |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time <sup>(1)</sup>              |                             |                    |        | 50                 | ns   |  |  |

| C <sub>in(LSE)</sub>                       | OSC32_IN input capacitance <sup>(1)</sup>              |                             |                    | 5      |                    | pF   |  |  |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                                             |                             | 30                 |        | 70                 | %    |  |  |

| ΙL                                         | OSC32_IN Input leakage<br>current                      | $V_{SS} \le V_{IN} \le V_D$ |                    |        | ±1                 | μA   |  |  |

| Symbol            | Parameter           | Conditions                                                                         | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|-------------------|---------------------|------------------------------------------------------------------------------------|--------------------|-----|--------------------|------|

|                   | Supply current      | Read mode $f_{HCLK} = 72 \text{ MHz}$ with 2 wait states, $V_{DD} = 3.3 \text{ V}$ |                    |     | 20                 | mA   |

| I <sub>DD</sub>   |                     | Write / Erase modes<br>$f_{HCLK} = 72 \text{ MHz}, V_{DD} = 3.3 \text{ V}$         |                    |     | 5                  | mA   |

|                   |                     | Power-down mode / Halt, $V_{DD} = 3.0$ to 3.6 V                                    |                    |     | 50                 | μA   |

| V <sub>prog</sub> | Programming voltage |                                                                                    | 2                  |     | 3.6                | V    |

Table 28. Flash memory characteristics (continued)

1. Guaranteed by design, not tested in production.

#### Table 29. Flash memory endurance and data retention

| Symbol Parameter                |           | Conditions                                                                              |                    | Unit |     |         |

|---------------------------------|-----------|-----------------------------------------------------------------------------------------|--------------------|------|-----|---------|

| Symbol                          | Falameter |                                                                                         | Min <sup>(1)</sup> | Тур  | Max | Unit    |

| N <sub>END</sub>                | Endurance | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                 |      |     | kcycles |

| t <sub>RET</sub> Data retention |           | 1 kcycle <sup>(2)</sup> at $T_A = 85 \ ^{\circ}C$                                       | 30                 |      |     |         |

|                                 |           | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                 |      |     | Years   |

|                                 |           | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                 |      |     |         |

1. Based on characterization, not tested in production.

2. Cycling performed over the whole temperature range.

# 5.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 1000-4-2 standard.

- **FTB**: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 1000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 30*. They are based on the EMS levels and classes defined in application note AN1709.

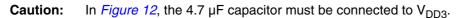

Figure 33. Power supply and reference decoupling ( $V_{REF+}$  connected to  $V_{DDA}$ )

1.  $V_{REF+}$  and  $V_{REF-}$  inputs are available only on 100-pin packages.

# 5.3.18 Temperature sensor characteristics

#### Table 49. TS characteristics

| Symbol                                | Parameter                                      | Min  | Тур  | Max  | Unit  |

|---------------------------------------|------------------------------------------------|------|------|------|-------|

| T <sub>L</sub> <sup>(1)</sup>         | V <sub>SENSE</sub> linearity with temperature  |      | ±1   | ±2   | °C    |

| Avg_Slope <sup>(1)</sup>              | Average slope                                  | 4.0  | 4.3  | 4.6  | mV/°C |

| V <sub>25</sub> <sup>(1)</sup>        | Voltage at 25 °C                               | 1.34 | 1.43 | 1.52 | V     |

| t <sub>START</sub> <sup>(2)</sup>     | Startup time                                   | 4    |      | 10   | μs    |

| T <sub>S_temp</sub> <sup>(3)(2)</sup> | ADC sampling time when reading the temperature |      |      | 17.1 | μs    |

1. Based on characterization, not tested in production.

2. Guaranteed by design, not tested in production.

3. Shortest sampling time can be determined in the application by multiple iterations.

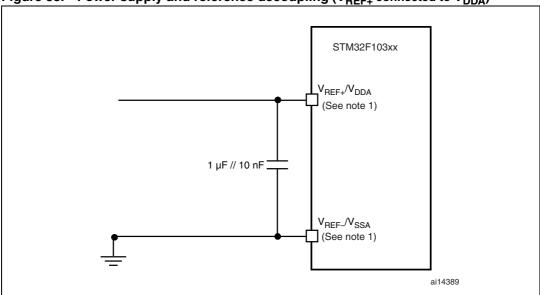

# Figure 40. LQFP64, 64-pin low-profile quad flat package Figure 40. Containe<sup>(1)</sup>

1. Drawing is not to scale.

2. Dimensions are in millimeters.

| Table 53. | LQFP64, 64-pin low-p | rofile quad flat package mechanical data |

|-----------|----------------------|------------------------------------------|

|           |                      |                                          |

| Dim  |                | mm    | mm inches <sup>(1)</sup> |        | inches <sup>(1)</sup> |        |  |

|------|----------------|-------|--------------------------|--------|-----------------------|--------|--|

| Dim. | Min            | Тур   | Max                      | Min    | Тур                   | Max    |  |

| А    |                |       | 1.60                     |        |                       | 0.0630 |  |

| A1   | 0.05           |       | 0.15                     | 0.0020 |                       | 0.0059 |  |

| A2   | 1.35           | 1.40  | 1.45                     | 0.0531 | 0.0551                | 0.0571 |  |

| b    | 0.17           | 0.22  | 0.27                     | 0.0067 | 0.0087                | 0.0106 |  |

| С    | 0.09           |       | 0.20                     | 0.0035 |                       | 0.0079 |  |

| D    |                | 12.00 |                          |        | 0.4724                |        |  |

| D1   |                | 10.00 |                          |        | 0.3937                |        |  |

| Е    |                | 12.00 |                          |        | 0.4724                |        |  |

| E1   |                | 10.00 |                          |        | 0.3937                |        |  |

| е    |                | 0.50  |                          |        | 0.0197                |        |  |

| θ    | 0°             | 3.5°  | <b>7</b> °               | 0°     | 3.5°                  | 7°     |  |

| L    | 0.45           | 0.60  | 0.75                     | 0.0177 | 0.0236                | 0.0295 |  |

| L1   |                | 1.00  |                          |        | 0.0394                |        |  |

| N    | Number of pins |       |                          |        |                       |        |  |

| IN   |                |       | (                        | 64     |                       |        |  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

Using the values obtained in *Table 56*  $T_{Jmax}$  is calculated as follows:

- For LQFP100, 46 °C/W

- $T_{Jmax} = 115 \ ^{\circ}C + (46 \ ^{\circ}C/W \times 134 \ mW) = 115 \ ^{\circ}C + 6.2 \ ^{\circ}C = 121.2 \ ^{\circ}C$

This is within the range of the suffix 7 version parts (–40 <  $T_J$  < 125 °C).

In this case, parts must be ordered at least with the temperature range suffix 7 (see *Table 57: Ordering information scheme*).

Figure 46. LQFP100 P<sub>D</sub> max vs. T<sub>A</sub>