Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, Motor Control PWM, PDR, POR, PVD, PWM, Temp Sensor, WDT          |

| Number of I/O              | 51                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 20K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f103rbt7 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of figures

| Figure 1.  | STM32F103xx performance line block diagram                                                                                                                  | . 19 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

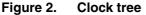

| Figure 2.  | Clock tree                                                                                                                                                  |      |

| Figure 3.  | STM32F103xx performance line LFBGA100 ballout                                                                                                               | . 21 |

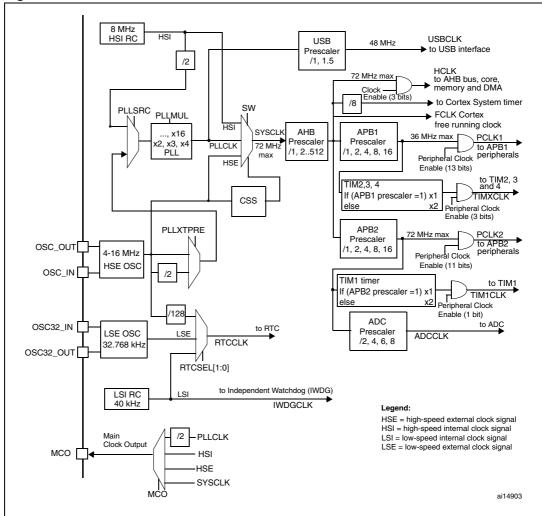

| Figure 4.  | STM32F103xx performance line LQFP100 pinout                                                                                                                 | . 22 |

| Figure 5.  | STM32F103xx performance line LQFP64 pinout                                                                                                                  | . 23 |

| Figure 6.  | STM32F103xx performance line TFBGA64 ballout                                                                                                                |      |

| Figure 7.  | STM32F103xx performance line LQFP48 pinout                                                                                                                  |      |

| Figure 8.  | STM32F103xx Performance Line VFQFPN36 pinout.                                                                                                               |      |

| Figure 9.  |                                                                                                                                                             |      |

| Figure 10. | Pin loading conditions.                                                                                                                                     |      |

| Figure 11. | Pin input voltage                                                                                                                                           |      |

| Figure 12. | Power supply scheme.                                                                                                                                        |      |

| Figure 13. | Current consumption measurement scheme                                                                                                                      |      |

| Figure 14. | Typical current consumption in Run mode versus frequency (at 3.6 V) -                                                                                       |      |

|            | code with data processing running from RAM, peripherals enabled.                                                                                            | . 40 |

| Figure 15. | Typical current consumption in Run mode versus frequency (at 3.6 V) -                                                                                       |      |

| rigulo io. | code with data processing running from RAM, peripherals disabled                                                                                            | 40   |

| Figure 16. | Typical current consumption in Stop mode with regulator in Run mode versus                                                                                  |      |

| riguro ro. | temperature at $V_{DD}$ = 3.3 V and 3.6 V                                                                                                                   | 42   |

| Figure 17. | Typical current consumption in Stop mode with regulator in Low-power mode versus                                                                            |      |

| rigure i/. | temperature at $V_{DD}$ = 3.3 V and 3.6 V                                                                                                                   | 43   |

| Figure 18. | Typical current consumption in Standby mode versus temperature at                                                                                           | . 40 |

| riguie io. | $V_{DD} = 3.3 \text{ V} \text{ and } 3.6 \text{ V} \dots$                                                                                                   | 13   |

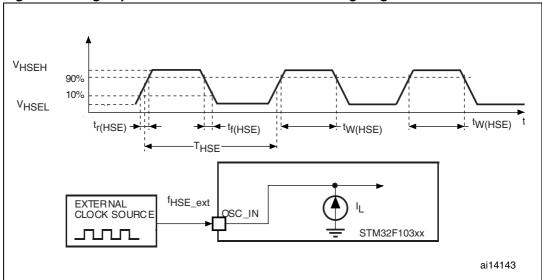

| Figure 19. | High-speed external clock source AC timing diagram                                                                                                          |      |

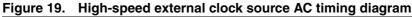

| Figure 20. | Low-speed external clock source AC timing diagram                                                                                                           |      |

| Figure 20. | Typical application with an 8 MHz crystal                                                                                                                   |      |

| Figure 21. | Typical application with a 32.768 kHz crystal                                                                                                               |      |

|            | I/O AC characteristics definition                                                                                                                           |      |

| Figure 23. |                                                                                                                                                             |      |

| Figure 24. | Recommended NRST pin protection                                                                                                                             |      |

| Figure 25. | I <sup>2</sup> C bus AC waveforms and measurement circuit                                                                                                   |      |

| Figure 26. | SPI timing diagram - slave mode and CPHA = 0                                                                                                                | . 04 |

| Figure 27. | SPI timing diagram - slave mode and CPHA = $1^{(1)}$                                                                                                        | . 64 |

| Figure 28. | SPI timing diagram - master mode <sup>(1)</sup>                                                                                                             |      |

| Figure 29. | USB timings: definition of data signal rise and fall time                                                                                                   |      |

| Figure 30. | ADC accuracy characteristics                                                                                                                                |      |

| Figure 31. | Typical connection diagram using the ADC                                                                                                                    |      |

| Figure 32. | Power supply and reference decoupling (V <sub>REF+</sub> not connected to V <sub>DDA</sub> )                                                                | . 70 |

| Figure 33. | Power supply and reference decoupling (V <sub>REF+</sub> connected to V <sub>DDA</sub> )<br>VFQFPN36 6 x 6 mm, 0.5 mm pitch, package outline <sup>(1)</sup> | . /1 |

| Figure 34. | VFQFPN36 6 x 6 mm, 0.5 mm pitch, package outline                                                                                                            | 73   |

| Figure 35. | Recommended footprint (dimensions in mm) <sup>(1)(2)(3)</sup>                                                                                               |      |

| Figure 36. | LFBGA100 - low profile fine pitch ball grid array package outline                                                                                           |      |

| Figure 37. | Recommended PCB design rules (0.80/0.75 mm pitch BGA)                                                                                                       |      |

| Figure 38. | LQFP100, 100-pin low-profile quad flat package outline                                                                                                      |      |

| Figure 39. | Recommended footprint <sup>(1)</sup>                                                                                                                        | . 76 |

| Figure 40. | LQFP64, 64-pin low-profile quad flat package outline                                                                                                        | . 77 |

| Figure 41. | Recommended footprint <sup>(1)</sup>                                                                                                                        | . 77 |

| Figure 42. | TFBGA64 - 8 x 8 active ball array, 5 x 5 mm, 0.5 mm pitch, package outline                                                                                  | . 78 |

| Figure 43. | Recommended PCB design rules for pads (0.5 mm pitch BGA)                                                                                                    | . 79 |

# 2.2 Full compatibility throughout the family

The STM32F103xx is a complete family whose members are fully pin-to-pin, software and feature compatible. In the reference manual, the STM32F103x4 and STM32F103x6 are identified as low-density devices, the STM32F103x8 and STM32F103xB are referred to as medium-density devices, and the STM32F103xC, STM32F103xD and STM32F103xE are referred to as high-density devices.

Low- and high-density devices are an extension of the STM32F103x8/B devices, they are specified in the STM32F103x4/6 and STM32F103xC/D/E datasheets, respectively. Low-density devices feature lower Flash memory and RAM capacities, less timers and peripherals. High-density devices have higher Flash memory and RAM capacities, and additional peripherals like SDIO, FSMC, I<sup>2</sup>S and DAC, while remaining fully compatible with the other members of the STM32F103xx family.

The STM32F103x4, STM32F103x6, STM32F103xC, STM32F103xD and STM32F103xE are a drop-in replacement for STM32F103x8/B medium-density devices, allowing the user to try different memory densities and providing a greater degree of freedom during the development cycle.

Moreover, the STM32F103xx performance line family is fully compatible with all existing STM32F101xx access line and STM32F102xx USB access line devices.

|        | Low-density devices                          |           | Medium-density devices                                 |                         | High-density devices                                                                     |                                                                  |                 |  |  |

|--------|----------------------------------------------|-----------|--------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------|-----------------|--|--|

| Pinout | 16 KB 32 KB<br>Flash Flash <sup>(1)</sup>    |           | 64 KB 128 KB<br>Flash Flash                            |                         |                                                                                          |                                                                  | 512 KB<br>Flash |  |  |

|        | 6 KB RAM                                     | 10 KB RAM | 20 KB RAM                                              | 20 KB RAM               | 48 KB RAM                                                                                | 64 KB RAM                                                        | 64 KB RAM       |  |  |

| 144    |                                              |           | 5 × USARTs                                             |                         |                                                                                          |                                                                  |                 |  |  |

| 100    |                                              |           | 3 × USARTs                                             |                         | $4 \times 16$ -bit timers, 2 × basic timers<br>3 × SPIs, 2 × I <sup>2</sup> Ss, 2 × I2Cs |                                                                  |                 |  |  |

| 64     | 2 × USART:<br>2 × 16-bit tir<br>1 × SPI, 1 × | mers      | $3 \times 16$ -bit tim<br>2 × SPIs, 2 ×<br>CAN, 1 × PW | l <sup>2</sup> Cs, USB, | USB, CAN, 2<br>3 × ADCs, 1                                                               | $2 \times PWM$ time<br>$\times DAC, 1 \times S$<br>and 144 pins) | ers<br>DIO      |  |  |

| 48     | CAN, 1 × P                                   |           | 2 × ADC                                                |                         |                                                                                          |                                                                  |                 |  |  |

| 36     | 2 × ADCs                                     |           |                                                        |                         |                                                                                          |                                                                  |                 |  |  |

Table 3.STM32F103xx family

For orderable part numbers that do not show the A internal code after the temperature range code (6 or 7), the reference datasheet for electrical characteristics is that of the STM32F103x8/B medium-density devices.

# 2.3 Overview

# 2.3.1 ARM<sup>®</sup> Cortex<sup>TM</sup>-M3 core with embedded Flash and SRAM

The ARM Cortex<sup>™</sup>-M3 processor is the latest generation of ARM processors for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM Cortex<sup>™</sup>-M3 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The STM32F103xx performance line family having an embedded ARM core, is therefore compatible with all ARM tools and software.

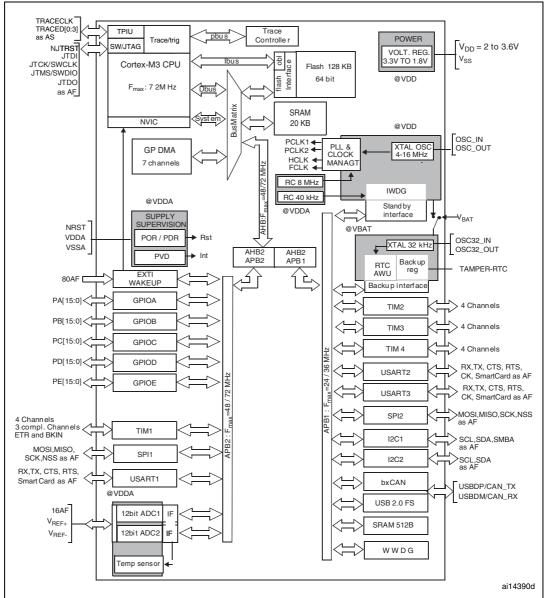

*Figure 1* shows the general block diagram of the device family.

### 2.3.2 Embedded Flash memory

64 or 128 Kbytes of embedded Flash is available for storing programs and data.

### 2.3.3 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

### 2.3.4 Embedded SRAM

Twenty Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states.

### 2.3.5 Nested vectored interrupt controller (NVIC)

The STM32F103xx performance line embeds a nested vectored interrupt controller able to handle up to 43 maskable interrupt channels (not including the 16 interrupt lines of Cortex<sup>™</sup>-M3) and 16 priority levels.

- Closely coupled NVIC gives low-latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of *late arriving* higher priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

### 2.3.13 DMA

The flexible 7-channel general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The DMA controller supports circular buffer management avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with support for software trigger on each channel. Configuration is made by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: SPI, I<sup>2</sup>C, USART, general-purpose and advanced-control timers TIMx and ADC.

### 2.3.14 RTC (real-time clock) and backup registers

The RTC and the backup registers are supplied through a switch that takes power either on  $V_{DD}$  supply when present or through the  $V_{BAT}$  pin. The backup registers are ten 16-bit registers used to store 20 bytes of user application data when  $V_{DD}$  power is not present.

The real-time clock provides a set of continuously running counters which can be used with suitable software to provide a clock calendar function, and provides an alarm interrupt and a periodic interrupt. It is clocked by a 32.768 kHz external crystal, resonator or oscillator, the internal low-power RC oscillator or the high-speed external clock divided by 128. The internal low-power RC has a typical frequency of 40 kHz. The RTC can be calibrated using an external 512 Hz output to compensate for any natural crystal deviation. The RTC features a 32-bit programmable counter for long-term measurement using the Compare register to generate an alarm. A 20-bit prescaler is used for the time base clock and is by default configured to generate a time base of 1 second from a clock at 32.768 kHz.

### 2.3.15 Timers and watchdogs

The medium-density STM32F103xx performance line devices include an advanced-control timer, three general-purpose timers, two watchdog timers and a SysTick timer.

*Table 4* compares the features of the advanced-control and general-purpose timers.

| Timer                  | Counter resolution | Counter<br>type         | Prescaler<br>factor                   | DMA request generation | Capture/compare<br>channels | Complementary<br>outputs |

|------------------------|--------------------|-------------------------|---------------------------------------|------------------------|-----------------------------|--------------------------|

| TIM1                   | 16-bit             | Up,<br>down,<br>up/down | Any integer<br>between 1<br>and 65536 | Yes                    | 4                           | Yes                      |

| TIM2,<br>TIM3,<br>TIM4 | 16-bit             | Up,<br>down,<br>up/down | Any integer<br>between 1<br>and 65536 | Yes                    | 4                           | No                       |

Table 4.Timer feature comparison

### Advanced-control timer (TIM1)

The advanced-control timer (TIM1) can be seen as a three-phase PWM multiplexed on 6 channels. It has complementary PWM outputs with programmable inserted dead-times. It

Figure 1. STM32F103xx performance line block diagram

1.  $T_A = -40$  °C to +105 °C (junction temperature up to 125 °C).

2. AF = alternate function on I/O port pin.

1. When the HSI is used as a PLL clock input, the maximum system clock frequency that can be achieved is 64 MHz.

- For the USB function to be available, both HSE and PLL must be enabled, with the CPU running at either 48 MHz or 72 MHz.

- 3. To have an ADC conversion time of 1  $\mu s,$  APB2 must be at 14 MHz, 28 MHz or 56 MHz.

Figure 4. STM32F103xx performance line LQFP100 pinout

# 5 Electrical characteristics

# 5.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to  $V_{SS}$ .

## 5.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

## 5.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A$  = 25 °C,  $V_{DD}$  = 3.3 V (for the 2 V  $\leq$   $V_{DD}$   $\leq$  3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\Sigma$ ).

## 5.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

## 5.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 10*.

## 5.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 11*.

| Symbol | Parameter         | Conditions                          |                   | Ма                     | Unit                    |        |      |      |  |

|--------|-------------------|-------------------------------------|-------------------|------------------------|-------------------------|--------|------|------|--|

| Symbol | Farameter         | Conditions                          | f <sub>HCLK</sub> | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit   |      |      |  |

|        |                   |                                     | 72 MHz            | 50                     | 50.3                    |        |      |      |  |

|        |                   |                                     | 48 MHz            | 36.1                   | 36.2                    |        |      |      |  |

|        |                   | External clock <sup>(2)</sup> , all | 36 MHz            | 28.6                   | 28.7                    |        |      |      |  |

|        |                   | peripherals enabled                 |                   | peripherals enabled    | peripherals enabled     | 24 MHz | 19.9 | 20.1 |  |

|        |                   |                                     |                   | 16 MHz                 | 14.7                    | 14.9   |      |      |  |

|        | Supply current in |                                     |                   | 8 MHz                  | 8.6                     | 8.9    | mA   |      |  |

| IDD    | Run mode          |                                     | 72 MHz            | 32.8                   | 32.9                    | mA     |      |      |  |

|        |                   |                                     | 48 MHz            | 24.4                   | 24.5                    |        |      |      |  |

|        |                   | External clock <sup>(2)</sup> , all | 36 MHz            | 19.8                   | 19.9                    |        |      |      |  |

|        |                   | peripherals disabled                | 24 MHz            | 13.9                   | 14.2                    |        |      |      |  |

|        |                   |                                     | 16 MHz            | 10.7                   | 11                      |        |      |      |  |

|        |                   |                                     | 8 MHz             | 6.8                    | 7.1                     |        |      |      |  |

# Table 13.Maximum current consumption in Run mode, code with data processing<br/>running from Flash

1. Based on characterization, not tested in production.

2. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

# Table 14.Maximum current consumption in Run mode, code with data processing<br/>running from RAM

| Symbol           | Parameter            | Conditions                          | 4                      | Ма                      | Unit |      |  |

|------------------|----------------------|-------------------------------------|------------------------|-------------------------|------|------|--|

| Symbol Parameter | Conditions           | <sup>f</sup> HCLK                   | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |      |  |

|                  |                      |                                     | 72 MHz                 | 48                      | 50   |      |  |

|                  |                      |                                     | 48 MHz                 | 31.5                    | 32   |      |  |

|                  |                      | External clock <sup>(2)</sup> , all | 36 MHz                 | 24                      | 25.5 |      |  |

|                  |                      | peripherals enabled                 | peripherals enabled    | 24 MHz                  | 17.5 | 18   |  |

|                  |                      |                                     |                        | 16 MHz                  | 12.5 | 13   |  |

|                  | Supply<br>current in |                                     | 8 MHz                  | 7.5                     | 8    | mA   |  |

| I <sub>DD</sub>  | Run mode             |                                     | 72 MHz                 | 29                      | 29.5 | IIIA |  |

|                  |                      |                                     | 48 MHz                 | 20.5                    | 21   |      |  |

|                  |                      | External clock <sup>(2)</sup> , all | 36 MHz                 | 16                      | 16.5 |      |  |

|                  |                      | peripherals disabled                | 24 MHz                 | 11.5                    | 12   |      |  |

|                  |                      |                                     | 16 MHz                 | 8.5                     | 9    |      |  |

|                  |                      | 8                                   | 8 MHz                  | 5.5                     | 6    |      |  |

1. Based on characterization, tested in production at  $V_{\text{DD}}$  max,  $f_{\text{HCLK}}$  max.

2. External clock is 8 MHz and PLL is on when  $f_{\text{HCLK}}$  > 8 MHz.

### **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in *Table 19*. The MCU is placed under the following conditions:

- all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- ambient operating temperature and V<sub>DD</sub> supply voltage conditions summarized in Table 6

|      | Peripheral                                                                                                                                 | Typical consumption at 25 °C | Unit |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------|

|      | TIM2                                                                                                                                       | 1.2                          |      |

| APB1 | TIM3                                                                                                                                       | 1.2                          |      |

|      | TIM4                                                                                                                                       | 0.9                          |      |

|      | SPI2                                                                                                                                       | 0.2                          |      |

|      | USART2                                                                                                                                     | 0.35                         | mA   |

|      | USART3                                                                                                                                     | 0.35                         | ША   |

|      | I2C1                                                                                                                                       | 0.39                         |      |

|      | I2C2                                                                                                                                       | 0.39                         |      |

|      | USB                                                                                                                                        | 0.65                         |      |

|      | CAN                                                                                                                                        | 0.72                         |      |

|      | GPIO A                                                                                                                                     | 0.47                         |      |

|      | TIM2<br>TIM3<br>TIM4<br>SPI2<br>USART2<br>USART3<br>I2C1<br>I2C2<br>USB<br>CAN<br>GPIO A<br>GPIO A<br>GPIO B<br>GPIO C<br>GPIO D<br>GPIO E | 0.47                         |      |

|      | GPIO C                                                                                                                                     | 0.47                         |      |

|      | GPIO D                                                                                                                                     | 0.47                         |      |

|      | GPIO E                                                                                                                                     | 0.47                         |      |

| APDZ | ADC1 <sup>(2)</sup>                                                                                                                        | 1.81                         | mA   |

|      | ADC2                                                                                                                                       | 1.78                         |      |

| APB2 | TIM1                                                                                                                                       | 1.6                          |      |

|      | SPI1                                                                                                                                       | 0.43                         |      |

| APB2 | USART1                                                                                                                                     | 0.85                         |      |

Table 19.

Peripheral current consumption<sup>(1)</sup>

1.  $f_{HCLK} = 72 \text{ MHz}, f_{APB1} = f_{HCLK}/2, f_{APB2} = f_{HCLK}$ , default prescaler value for each peripheral.

Specific conditions for ADC: f<sub>HCLK</sub> = 56 MHz, f<sub>APB1</sub> = f<sub>HCLK</sub>/2, f<sub>APB2</sub> = f<sub>HCLK</sub>, f<sub>ADCCLK</sub> = f<sub>APB2/4</sub>, ADON bit in the ADC\_CR2 register is set to 1.

## 5.3.6 External clock source characteristics

## High-speed external user clock generated from an external source

The characteristics given in *Table 20* result from tests performed using an high-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 9*.

|                                            | nigh speed external user block bhardblenshos        |                                                                            |             |     |                    |      |

|--------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------|-------------|-----|--------------------|------|

| Symbol                                     | Parameter                                           | Conditions                                                                 | Min         | Тур | Max                | Unit |

| f <sub>HSE_ext</sub>                       | User external clock source frequency <sup>(1)</sup> |                                                                            | 0           | 8   | 25                 | MHz  |

| V <sub>HSEH</sub>                          | OSC_IN input pin high level voltage                 |                                                                            | $0.7V_{DD}$ |     | V <sub>DD</sub>    | v    |

| V <sub>HSEL</sub>                          | OSC_IN input pin low level voltage                  |                                                                            | $V_{SS}$    |     | $0.3V_{\text{DD}}$ | v    |

| t <sub>w(HSE)</sub><br>t <sub>w(HSE)</sub> | OSC_IN high or low time <sup>(1)</sup>              |                                                                            | 16          |     |                    | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub> | OSC_IN rise or fall time <sup>(1)</sup>             |                                                                            |             |     | 20                 | 115  |

| C <sub>in(HSE)</sub>                       | OSC_IN input capacitance <sup>(1)</sup>             |                                                                            |             | 5   |                    | pF   |

| DuCy <sub>(HSE)</sub>                      | Duty cycle                                          |                                                                            | 45          |     | 55                 | %    |

| ΙL                                         | OSC_IN Input leakage current                        | $\begin{array}{c} V_{SS} \leq V_{IN} \leq V_{D} \\ & \text{D} \end{array}$ |             |     | ±1                 | μA   |

Table 20.

High-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

### Low-speed external user clock generated from an external source

The characteristics given in *Table 21* result from tests performed using an low-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 9*.

| Table 21. | Low-speed external user clock characteristics |

|-----------|-----------------------------------------------|

|-----------|-----------------------------------------------|

| Symbol                                     | Parameter                                              | Conditions                  | Min                | Тур    | Мах                | Unit |

|--------------------------------------------|--------------------------------------------------------|-----------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                       | User External clock source<br>frequency <sup>(1)</sup> |                             |                    | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage                  |                             | 0.7V <sub>DD</sub> |        | V <sub>DD</sub>    | V    |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage                   |                             | V <sub>SS</sub>    |        | 0.3V <sub>DD</sub> | v    |

| t <sub>w(LSE)</sub><br>t <sub>w(LSE)</sub> | OSC32_IN high or low time <sup>(1)</sup>               |                             | 450                |        |                    |      |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time <sup>(1)</sup>              |                             |                    |        | 50                 | ns   |

| C <sub>in(LSE)</sub>                       | OSC32_IN input capacitance <sup>(1)</sup>              |                             |                    | 5      |                    | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                                             |                             | 30                 |        | 70                 | %    |

| ١L                                         | OSC32_IN Input leakage<br>current                      | $V_{SS} \le V_{IN} \le V_D$ |                    |        | ±1                 | μA   |

1. Guaranteed by design, not tested in production.

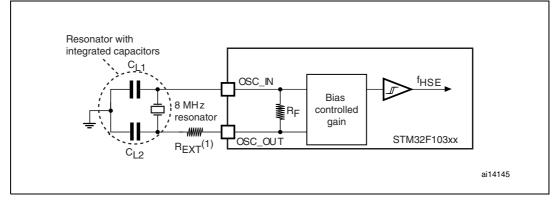

### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 16 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 22*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                             | Parameter                                                                                     | Conditions                                               | Min | Тур | Max | Unit |

|------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------|-----|-----|-----|------|

| f <sub>OSC_IN</sub>                | Oscillator frequency                                                                          |                                                          | 4   | 8   | 16  | MHz  |

| R <sub>F</sub>                     | Feedback resistor                                                                             |                                                          |     | 200 |     | kΩ   |

| $C_{L1} \\ C_{L2}^{(3)}$           | Recommended load capacitance versus equivalent serial resistance of the crystal $(R_S)^{(4)}$ | R <sub>S</sub> = 30 Ω                                    |     | 30  |     | pF   |

| i <sub>2</sub>                     | HSE driving current                                                                           | $V_{DD}$ = 3.3 V, $V_{IN}$ = $V_{SS}$<br>with 30 pF load |     |     | 1   | mA   |

| 9 <sub>m</sub>                     | Oscillator transconductance                                                                   | Startup                                                  | 25  |     |     | mA/V |

| t <sub>SU(HSE</sub> <sup>(5)</sup> | startup time                                                                                  | V <sub>DD</sub> is stabilized                            |     | 2   |     | ms   |

Table 22.

HSE 4-16 MHz oscillator characteristics<sup>(1) (2)</sup>

1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

2. Based on characterization, not tested in production.

- 3. For  $C_{L1}$  and  $C_{L2}$  it is recommended to use high-quality ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator.  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ .

- 4. The relatively low value of the RF resistor offers a good protection against issues resulting from use in a humid environment, due to the induced leakage and the bias condition change. However, it is recommended to take this point into account if the MCU is used in tough humidity conditions.

- t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

### Figure 21. Typical application with an 8 MHz crystal

1. R<sub>EXT</sub> value depends on the crystal characteristics. Typical value is in the range of 5 to 6R<sub>S</sub>.

### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 23*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

|                                     | Ten benet mene handab                                  |                                                                                    |     |      |

|-------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------|-----|------|

| Symbol                              | Parameter                                              | Conditions                                                                         | Тур | Unit |

| t <sub>WUSLEEP</sub> <sup>(1)</sup> | Wakeup from Sleep mode                                 | Wakeup on HSI RC clock                                                             | 1.8 | μs   |

| twustop <sup>(1)</sup>              | Wakeup from Stop mode<br>(regulator in run mode)       | HSI RC wakeup time = 2 µs                                                          | 3.6 | 110  |

|                                     | Wakeup from Stop mode<br>(regulator in low power mode) | HSI RC wakeup time = 2 $\mu$ s, Regulator<br>wakeup from LP mode time = 5 $\mu$ s  | 5.4 | μs   |

| t <sub>WUSTDBY</sub> <sup>(1)</sup> | Wakeup from Standby mode                               | HSI RC wakeup time = 2 $\mu$ s, Regulator wakeup from power down time = 38 $\mu$ s | 50  | μs   |

Table 26. Low-power mode wakeup timings

1. The wakeup times are measured from the wakeup event to the point in which the user application code reads the first instruction.

## 5.3.8 PLL characteristics

The parameters given in *Table 27* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

| Symbol               | Parameter                      | Test conditions |                    | Unit |                    |      |

|----------------------|--------------------------------|-----------------|--------------------|------|--------------------|------|

| Symbol               | Parameter                      | Test conditions | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

| f                    | PLL input clock <sup>(2)</sup> |                 | 1                  | 8.0  | 25                 | MHz  |

| f <sub>PLL_IN</sub>  | PLL input clock duty cycle     |                 | 40                 |      | 60                 | %    |

| f <sub>PLL_OUT</sub> | PLL multiplier output clock    |                 | 16                 |      | 72                 | MHz  |

| t <sub>LOCK</sub>    | PLL lock time                  |                 |                    |      | 200                | μs   |

Table 27. PLL characteristics

1. Based on characterization, not tested in production.

2. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{\mathsf{PLL}\_\mathsf{OUT}}$ .

### 5.3.9 Memory characteristics

### **Flash memory**

The characteristics are given at  $T_A = -40$  to 105 °C unless otherwise specified.

| Symbol             | Parameter Conditions    |                                 | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |  |

|--------------------|-------------------------|---------------------------------|--------------------|------|--------------------|------|--|

| t <sub>prog</sub>  | 16-bit programming time | $T_A = -40$ to +105 °C          | 40                 | 52.5 | 70                 | μs   |  |

| t <sub>ERASE</sub> | Page (1 KB) erase time  | T <sub>A</sub> = -40 to +105 °C | 20                 |      | 40                 | ms   |  |

| t <sub>ME</sub>    | Mass erase time         | T <sub>A</sub> = -40 to +105 °C | 20                 |      | 40                 | ms   |  |

Table 28.

Flash memory characteristics

| Symbol            | Parameter           | Conditions                                                                         | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|-------------------|---------------------|------------------------------------------------------------------------------------|--------------------|-----|--------------------|------|

|                   |                     | Read mode $f_{HCLK} = 72 \text{ MHz}$ with 2 wait states, $V_{DD} = 3.3 \text{ V}$ |                    |     | 20                 | mA   |

| I <sub>DD</sub>   | Supply current      | Write / Erase modes<br>$f_{HCLK} = 72 \text{ MHz}, V_{DD} = 3.3 \text{ V}$         |                    |     | 5                  | mA   |

|                   |                     | Power-down mode / Halt, $V_{DD} = 3.0$ to 3.6 V                                    |                    |     | 50                 | μA   |

| V <sub>prog</sub> | Programming voltage |                                                                                    | 2                  |     | 3.6                | V    |

Table 28. Flash memory characteristics (continued)

1. Guaranteed by design, not tested in production.

### Table 29. Flash memory endurance and data retention

| Symbol                      | Parameter Conditions | Conditions                                                                              | Value |     |      | Unit    |

|-----------------------------|----------------------|-----------------------------------------------------------------------------------------|-------|-----|------|---------|

|                             |                      | Min <sup>(1)</sup>                                                                      | Тур   | Max | Unit |         |

| N <sub>END</sub>            | Endurance            | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10    |     |      | kcycles |

|                             |                      | 1 kcycle <sup>(2)</sup> at $T_A = 85 \ ^{\circ}C$                                       | 30    |     |      |         |

| t <sub>RET</sub> Data reter | Data retention       | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10    |     |      | Years   |

|                             |                      | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20    |     |      |         |

1. Based on characterization, not tested in production.

2. Cycling performed over the whole temperature range.

## 5.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 1000-4-2 standard.

- **FTB**: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 1000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 30*. They are based on the EMS levels and classes defined in application note AN1709.

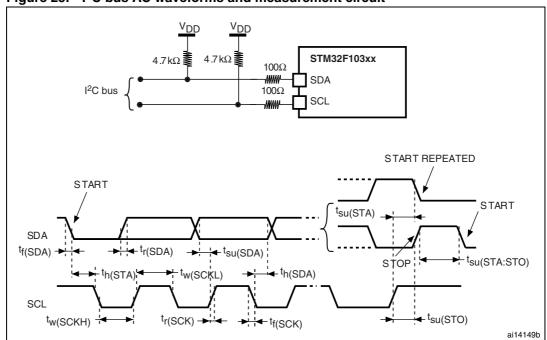

Figure 25. I<sup>2</sup>C bus AC waveforms and measurement circuit

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

# Table 40. SCL frequency $(f_{PCLK1} = 36 \text{ MHz.}, V_{DD} = 3.3 \text{ V})^{(1)(2)}$

| f ((tH=)               | I2C_CCR value                  |

|------------------------|--------------------------------|

| f <sub>SCL</sub> (kHz) | <b>R<sub>P</sub> = 4.7 k</b> Ω |

| 400                    | 0x801E                         |

| 300                    | 0x8028                         |

| 200                    | 0x803C                         |

| 100                    | 0x00B4                         |

| 50                     | 0x0168                         |

| 20                     | 0x0384                         |

1.  $R_P$  = External pull-up resistance,  $f_{SCL} = I^2C$  speed,

For speeds around 200 kHz, the tolerance on the achieved speed is of ±5%. For other speed ranges, the tolerance on the achieved speed ±2%. These variations depend on the accuracy of the external components used to design the application.

### 5.3.17 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 45* are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 9*.

Note: It is recommended to perform a calibration after each power-up.

| Table 45.                        | ADC characteristics                       |                           | -                                                                          |                    |                    | 1                  |

|----------------------------------|-------------------------------------------|---------------------------|----------------------------------------------------------------------------|--------------------|--------------------|--------------------|

| Symbol                           | Parameter                                 | Conditions                | Min                                                                        | Тур                | Max                | Unit               |

| V <sub>DDA</sub>                 | Power supply                              |                           | 2.4                                                                        |                    | 3.6                | V                  |

| V <sub>REF+</sub>                | Positive reference voltage                |                           | 2.4                                                                        |                    | V <sub>DDA</sub>   | V                  |

| I <sub>VREF</sub>                | Current on the V <sub>REF</sub> input pin |                           |                                                                            | 160 <sup>(1)</sup> | 220 <sup>(1)</sup> | μA                 |

| f <sub>ADC</sub>                 | ADC clock frequency                       |                           | 0.6                                                                        |                    | 14                 | MHz                |

| f <sub>S</sub> <sup>(2)</sup>    | Sampling rate                             |                           | 0.05                                                                       |                    | 1                  | MHz                |

| £ (2)                            | External trigger frequency                | f <sub>ADC</sub> = 14 MHz |                                                                            |                    | 823                | kHz                |

| f <sub>TRIG</sub> <sup>(2)</sup> |                                           |                           |                                                                            |                    | 17                 | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub> <sup>(3)</sup>  | Conversion voltage range                  |                           | 0 (V <sub>SSA</sub> or V <sub>REF-</sub><br>tied to ground)                |                    | V <sub>REF+</sub>  | V                  |

| R <sub>AIN</sub> <sup>(2)</sup>  | External input impedance                  |                           | See Equation 1 and Table 46                                                |                    |                    | kΩ                 |

| R <sub>ADC</sub> <sup>(2)</sup>  | Sampling switch resistance                |                           |                                                                            |                    | 1                  | kΩ                 |

| C <sub>ADC</sub> <sup>(2)</sup>  | Internal sample and hold capacitor        |                           |                                                                            |                    | 12                 | pF                 |

| + (2)                            | Calibration time                          | f <sub>ADC</sub> = 14 MHz | 5.9                                                                        |                    |                    | μs                 |

| t <sub>CAL</sub> <sup>(2)</sup>  |                                           |                           | 83                                                                         |                    |                    | 1/f <sub>ADC</sub> |

| t <sub>lat</sub> (2)             | Injection trigger conversion              | f <sub>ADC</sub> = 14 MHz |                                                                            |                    | 0.214              | μs                 |

| <sup>l</sup> lat` '              | latency                                   |                           |                                                                            |                    | 3 <sup>(4)</sup>   | 1/f <sub>ADC</sub> |

| t <sub>latr</sub> (2)            | Regular trigger conversion                | f <sub>ADC</sub> = 14 MHz |                                                                            |                    | 0.143              | μs                 |

| <sup>l</sup> latr` '             | latency                                   |                           |                                                                            |                    | 2 <sup>(4)</sup>   | 1/f <sub>ADC</sub> |

| t <sub>S</sub> <sup>(2)</sup>    | Sampling time                             | f <sub>ADC</sub> = 14 MHz | 0.107                                                                      |                    | 17.1               | μs                 |

|                                  |                                           |                           | 1.5                                                                        |                    | 239.5              | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(2)</sup> | Power-up time                             |                           | 0                                                                          | 0                  | 1                  | μs                 |

|                                  | Total conversion time                     | f <sub>ADC</sub> = 14 MHz | 1                                                                          |                    | 18                 | μs                 |

| t <sub>CONV</sub> <sup>(2)</sup> | (including sampling time)                 |                           | 14 to 252 (t <sub>S</sub> for sampling +12.5 for successive approximation) |                    |                    | 1/f <sub>ADC</sub> |

Table 45.

ADC characteristics

1. Based on characterization, not tested in production.

2. Guaranteed by design, not tested in production.

4. For external triggers, a delay of 1/f<sub>PCLK2</sub> must be added to the latency specified in *Table 45*.

In devices delivered in VFQFPN and LQFP packages, V<sub>REF+</sub> is internally connected to V<sub>DDA</sub> and V<sub>REF-</sub> is internally connected to V<sub>SSA</sub>. Devices that come in the TFBGA64 package have a V<sub>REF+</sub> pin but no V<sub>REF-</sub> pin (V<sub>REF-</sub> is internally connected to V<sub>SSA</sub>), see *Table 5* and *Figure 6*.

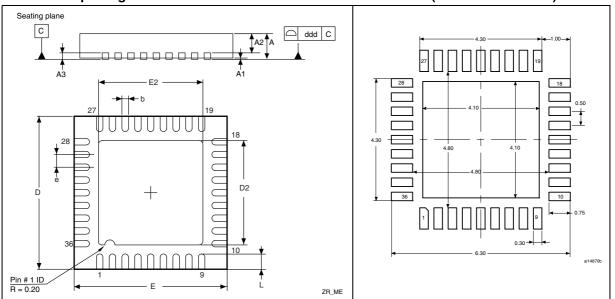

1. Drawing is not to scale.

2. The back-side pad is not internally connected to the  $V_{SS}$  or  $V_{DD}$  power pads.

3. There is an exposed die pad on the underside of the VFQFPN package. It should be soldered to the PCB. All leads should also be soldered to the PCB.

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур   | Max   | Min                   | Тур    | Max    |

| А      | 0.800       | 0.900 | 1.000 | 0.0315                | 0.0354 | 0.0394 |

| A1     |             | 0.020 | 0.050 |                       | 0.0008 | 0.0020 |

| A2     |             | 0.650 | 1.000 |                       | 0.0256 | 0.0394 |

| A3     |             | 0.250 |       |                       | 0.0098 |        |

| b      | 0.180       | 0.230 | 0.300 | 0.0071                | 0.0091 | 0.0118 |

| D      | 5.875       | 6.000 | 6.125 | 0.2313                | 0.2362 | 0.2411 |

| D2     | 1.750       | 3.700 | 4.250 | 0.0689                | 0.1457 | 0.1673 |

| E      | 5.875       | 6.000 | 6.125 | 0.2313                | 0.2362 | 0.2411 |

| E2     | 1.750       | 3.700 | 4.250 | 0.0689                | 0.1457 | 0.1673 |

| е      | 0.450       | 0.500 | 0.550 | 0.0177                | 0.0197 | 0.0217 |

| L      | 0.350       | 0.550 | 0.750 | 0.0138                | 0.0217 | 0.0295 |

| ddd    |             | 0.080 |       | 0.0031                |        |        |

#### Table 50. VFQFPN36 6 x 6 mm, 0.5 mm pitch, package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

# Figure 35. Recommended footprint (dimensions in mm)<sup>(1)(2)(3)</sup>

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21-Jul-2008 | 8        | Power supply supervisor updated and $V_{DDA}$ added to Table 9: General<br>operating conditions.Capacitance modified in Figure 12: Power supply scheme on page 33.Table notes revised in Section 5: Electrical characteristics.Table 16: Typical and maximum current consumptions in Stop and<br>Standby modes modified.Data added to Table 16: Typical and maximum current consumptions in<br>Stop and Standby modes and Table 21: Typical current consumption in<br>Standby mode removed.fHSE_ext modified in Table 20: High-speed external user clock<br>characteristics on page 47. fPLL_IN modified in Table 27: PLL<br>characteristics on page 52.Minimum SDA and SCL fall time value for Fast mode removed from<br>Table 39: I <sup>2</sup> C characteristics on page 61, note 1 modified.th(NSS) modified in Table 41: SPI characteristics on page 63 and<br>Figure 26: SPI timing diagram - slave mode and CPHA = 0 on page 64.CADC modified in Table 45: ADC characteristics on page 67 and<br>Figure 31: Typical connection diagram using the ADC modified.Typical S_temp value removed from Table 49: TS characteristics on<br>page 71.LQFP48 package specifications updated (see Table 55 and Table 45),<br>Section 6: Package characteristics revised.Axx option removed from Table 57: Ordering information scheme on<br>page 84.Small text changes. |

| 22-Sep-2008 | 9        | STM32F103x6 part numbers removed (see <i>Table 57: Ordering</i><br><i>information scheme</i> ). Small text changes.<br><i>General-purpose timers (TIMx)</i> and <i>Advanced-control timer (TIM1)</i> on<br><i>page 15</i> updated.<br>Notes updated in <i>Table 5: Medium-density STM32F103xx pin</i><br><i>definitions on page 26.</i><br><i>Note 2</i> modified below <i>Table 6: Voltage characteristics on page 34</i> ,<br>$ \Delta V_{DDx} $ min and $ \Delta V_{DDx} $ min removed.<br>Measurement conditions specified in <i>Section 5.3.5: Supply current</i><br><i>characteristics on page 38.</i><br>$I_{DD}$ in standby mode at 85 °C modified in <i>Table 16: Typical and</i><br><i>maximum current consumptions in Stop and Standby modes on</i><br><i>page 42.</i><br><i>General input/output characteristics on page 56</i> modified.<br>$f_{HCLK}$ conditions modified in <i>Table 30: EMS characteristics on page 54.</i><br>$\Theta_{JA}$ and pitch value modified for LFBGA100 package in <i>Table 56:</i><br><i>Package thermal characteristics.</i> Small text changes.                                                                                                                                                                                                                                                                       |

# Table 58. Document revision history (continued)

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | 10       | I/O information clarified <i>on page 1</i> .<br><i>Figure 3: STM32F103xx performance line LFBGA100 ballout</i> modified.<br><i>Figure 9: Memory map</i> modified. <i>Table 4: Timer feature comparison</i><br>added.<br>PB4, PB13, PB14, PB15, PB3/TRACESWO moved from Default<br>column to Remap column in <i>Table 5: Medium-density STM32F103xx</i><br><i>pin definitions</i> . |

| 23-Apr-2009 |          | P <sub>D</sub> for LFBGA100 corrected in <i>Table 9: General operating conditions</i> .<br>Note modified in <i>Table 13: Maximum current consumption in Run</i><br><i>mode, code with data processing running from Flash</i> and <i>Table 15:</i><br><i>Maximum current consumption in Sleep mode, code running from</i><br><i>Flash or RAM</i> .                                  |

|             |          | Table 20: High-speed external user clock characteristics and Table 21:Low-speed external user clock characteristics modified.                                                                                                                                                                                                                                                      |

|             |          | <i>Figure 17</i> shows a typical curve (title modified). ACC <sub>HSI</sub> max values modified in <i>Table 24: HSI oscillator characteristics</i> .                                                                                                                                                                                                                               |

|             |          | TFBGA64 package added (see <i>Table 54</i> and <i>Table 42</i> ). Small text changes.                                                                                                                                                                                                                                                                                              |

# Table 58. Document revision history (continued)