Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 72MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB            |

| Peripherals                | DMA, Motor Control PWM, PDR, POR, PVD, PWM, Temp Sensor, WDT            |

| Number of I/O              | 51                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 20K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 16x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | -                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f103rbt7tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of figures

| Figure 1.  | STM32F103xx performance line block diagram                                                                                                                  | . 19 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2.  | Clock tree                                                                                                                                                  |      |

| Figure 3.  | STM32F103xx performance line LFBGA100 ballout                                                                                                               | . 21 |

| Figure 4.  | STM32F103xx performance line LQFP100 pinout                                                                                                                 | . 22 |

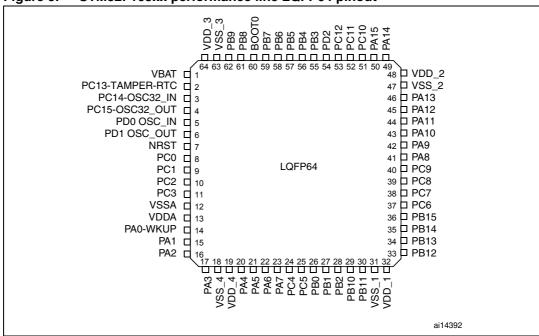

| Figure 5.  | STM32F103xx performance line LQFP64 pinout                                                                                                                  | . 23 |

| Figure 6.  | STM32F103xx performance line TFBGA64 ballout                                                                                                                |      |

| Figure 7.  | STM32F103xx performance line LQFP48 pinout                                                                                                                  |      |

| Figure 8.  | STM32F103xx Performance Line VFQFPN36 pinout.                                                                                                               |      |

| Figure 9.  |                                                                                                                                                             |      |

| Figure 10. | Pin loading conditions.                                                                                                                                     |      |

| Figure 11. | Pin input voltage                                                                                                                                           |      |

| Figure 12. | Power supply scheme.                                                                                                                                        |      |

| Figure 13. | Current consumption measurement scheme                                                                                                                      |      |

| Figure 14. | Typical current consumption in Run mode versus frequency (at 3.6 V) -                                                                                       |      |

|            | code with data processing running from RAM, peripherals enabled.                                                                                            | . 40 |

| Figure 15. | Typical current consumption in Run mode versus frequency (at 3.6 V) -                                                                                       |      |

| rigulo io. | code with data processing running from RAM, peripherals disabled                                                                                            | 40   |

| Figure 16. | Typical current consumption in Stop mode with regulator in Run mode versus                                                                                  |      |

| riguro ro. | temperature at $V_{DD}$ = 3.3 V and 3.6 V                                                                                                                   | 42   |

| Figure 17. | Typical current consumption in Stop mode with regulator in Low-power mode versus                                                                            |      |

| rigure i/. | temperature at $V_{DD}$ = 3.3 V and 3.6 V                                                                                                                   | 43   |

| Figure 18. | Typical current consumption in Standby mode versus temperature at                                                                                           | . 40 |

| rigure ro. | $V_{DD} = 3.3 \text{ V} \text{ and } 3.6 \text{ V} \dots$                                                                                                   | 13   |

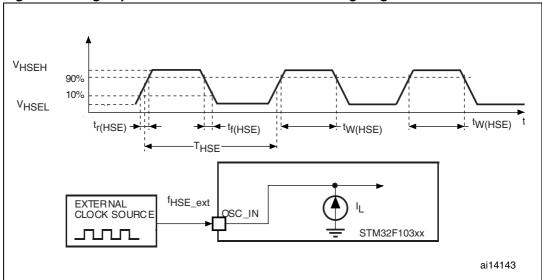

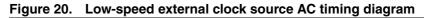

| Figure 19. | High-speed external clock source AC timing diagram                                                                                                          |      |

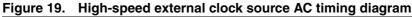

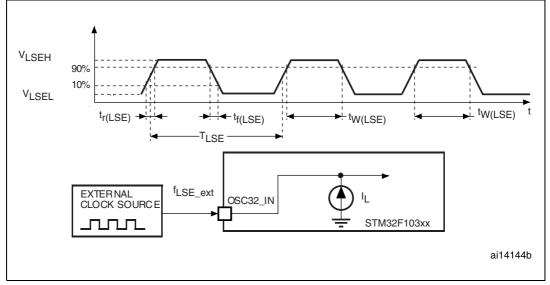

| Figure 20. | Low-speed external clock source AC timing diagram                                                                                                           |      |

| Figure 20. | Typical application with an 8 MHz crystal                                                                                                                   |      |

| Figure 21. | Typical application with a 32.768 kHz crystal                                                                                                               |      |

|            | I/O AC characteristics definition                                                                                                                           |      |

| Figure 23. |                                                                                                                                                             |      |

| Figure 24. | Recommended NRST pin protection                                                                                                                             |      |

| Figure 25. | I <sup>2</sup> C bus AC waveforms and measurement circuit                                                                                                   |      |

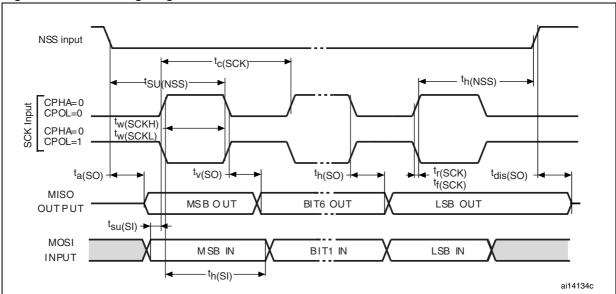

| Figure 26. | SPI timing diagram - slave mode and CPHA = 0                                                                                                                | . 04 |

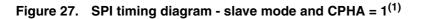

| Figure 27. | SPI timing diagram - slave mode and CPHA = $1^{(1)}$                                                                                                        | . 64 |

| Figure 28. | SPI timing diagram - master mode <sup>(1)</sup>                                                                                                             |      |

| Figure 29. | USB timings: definition of data signal rise and fall time                                                                                                   |      |

| Figure 30. | ADC accuracy characteristics                                                                                                                                |      |

| Figure 31. | Typical connection diagram using the ADC                                                                                                                    |      |

| Figure 32. | Power supply and reference decoupling (V <sub>REF+</sub> not connected to V <sub>DDA</sub> )                                                                | . 70 |

| Figure 33. | Power supply and reference decoupling (V <sub>REF+</sub> connected to V <sub>DDA</sub> )<br>VFQFPN36 6 x 6 mm, 0.5 mm pitch, package outline <sup>(1)</sup> | . /1 |

| Figure 34. | VFQFPN36 6 x 6 mm, 0.5 mm pitch, package outline                                                                                                            | 73   |

| Figure 35. | Recommended footprint (dimensions in mm) <sup>(1)(2)(3)</sup>                                                                                               |      |

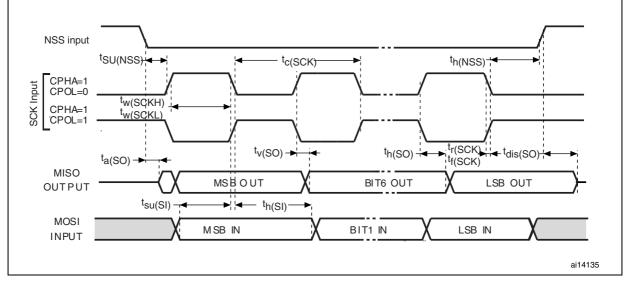

| Figure 36. | LFBGA100 - low profile fine pitch ball grid array package outline                                                                                           |      |

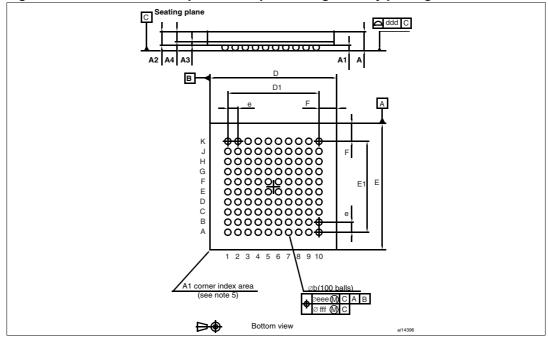

| Figure 37. | Recommended PCB design rules (0.80/0.75 mm pitch BGA)                                                                                                       |      |

| Figure 38. | LQFP100, 100-pin low-profile quad flat package outline                                                                                                      |      |

| Figure 39. | Recommended footprint <sup>(1)</sup>                                                                                                                        | . 76 |

| Figure 40. | LQFP64, 64-pin low-profile quad flat package outline                                                                                                        | . 77 |

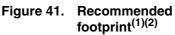

| Figure 41. | Recommended footprint <sup>(1)</sup>                                                                                                                        | . 77 |

| Figure 42. | TFBGA64 - 8 x 8 active ball array, 5 x 5 mm, 0.5 mm pitch, package outline                                                                                  | . 78 |

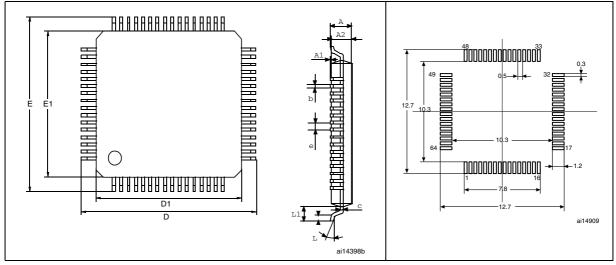

| Figure 43. | Recommended PCB design rules for pads (0.5 mm pitch BGA)                                                                                                    | . 79 |

# 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32F103x8 and STM32F103xB medium-density performance line microcontrollers. For more details on the whole STMicroelectronics STM32F103xx family, please refer to *Section 2.2: Full compatibility throughout the family*.

The medium-density STM32F103xx datasheet should be read in conjunction with the low-, medium- and high-density STM32F10xxx reference manual. The reference and Flash programming manuals are both available from the STMicroelectronics website www.st.com.

For information on the Cortex<sup>™</sup>-M3 core please refer to the Cortex<sup>™</sup>-M3 Technical Reference Manual, available from the www.arm.com website at the following address: http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.ddi0337e/.

# 2 Description

The STM32F103x8 and STM32F103xB performance line family incorporates the highperformance ARM Cortex<sup>™</sup>-M3 32-bit RISC core operating at a 72 MHz frequency, highspeed embedded memories (Flash memory up to 128 Kbytes and SRAM up to 20 Kbytes), and an extensive range of enhanced I/Os and peripherals connected to two APB buses. All devices offer two 12-bit ADCs, three general purpose 16-bit timers plus one PWM timer, as well as standard and advanced communication interfaces: up to two I<sup>2</sup>Cs and SPIs, three USARTs, an USB and a CAN.

The STM32F103xx medium-density performance line family operates from a 2.0 to 3.6 V power supply. It is available in both the -40 to +85 °C temperature range and the -40 to +105 °C extended temperature range. A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F103xx medium-density performance line family includes devices in six different package types: from 36 pins to 100 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

These features make the STM32F103xx medium-density performance line microcontroller family suitable for a wide range of applications:

- Motor drive and application control

- Medical and handheld equipment

- PC peripherals gaming and GPS platforms

- Industrial applications: PLC, inverters, printers, and scanners

- Alarm systems, Video intercom, and HVAC

*Figure 1* shows the general block diagram of the device family.

This hardware block provides flexible interrupt management features with minimal interrupt latency.

# 2.3.6 External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 19 edge detector lines used to generate interrupt/event requests. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 80 GPIOs can be connected to the 16 external interrupt lines.

# 2.3.7 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-16 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example on failure of an indirectly used external crystal, resonator or oscillator).

Several prescalers allow the configuration of the AHB frequency, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the AHB and the high-speed APB domains is 72 MHz. The maximum allowed frequency of the low-speed APB domain is 36 MHz. See *Figure 2* for details on the clock tree.

# 2.3.8 Boot modes

At startup, boot pins are used to select one of three boot options:

- Boot from User Flash

- Boot from System Memory

- Boot from embedded SRAM

The boot loader is located in System Memory. It is used to reprogram the Flash memory by using USART1. For further details please refer to AN2606.

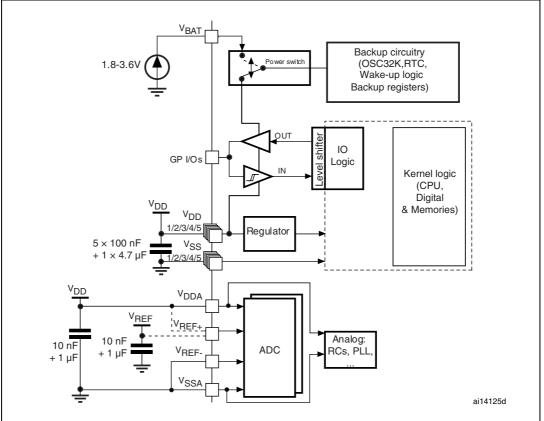

# 2.3.9 Power supply schemes

- V<sub>DD</sub> = 2.0 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 2.0 to 3.6 V: external analog power supplies for ADC, reset blocks, RCs and PLL (minimum voltage to be applied to V<sub>DDA</sub> is 2.4 V when the ADC is used). V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

- V<sub>BAT</sub> = 1.8 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

For more details on how to connect power pins, refer to *Figure 12: Power supply scheme*.

# 2.3.10 Power supply supervisor

The device has an integrated power-on reset (POR)/power-down reset (PDR) circuitry. It is always active, and ensures proper operation starting from/down to 2 V. The device remains

in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$ , without the need for an external reset circuit.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

Refer to Table 11: Embedded reset and power control block characteristics for the values of  $V_{POR/PDR}$  and  $V_{PVD}$ .

# 2.3.11 Voltage regulator

The regulator has three operation modes: main (MR), low power (LPR) and power down.

- MR is used in the nominal regulation mode (Run)

- LPR is used in the Stop mode

- Power down is used in Standby mode: the regulator output is in high impedance: the kernel circuitry is powered down, inducing zero consumption (but the contents of the registers and SRAM are lost)

This regulator is always enabled after reset. It is disabled in Standby mode, providing high impedance output.

# 2.3.12 Low-power modes

The STM32F103xx performance line supports three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

• Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

• Stop mode

The Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low power mode.

The device can be woken up from Stop mode by any of the EXTI line. The EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm or the USB wakeup.

Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.8 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, SRAM and register contents are lost except for registers in the Backup domain and Standby circuitry.

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped by entering Stop or Standby mode.

Figure 5. STM32F103xx performance line LQFP64 pinout

|          |        | Pin     | IS     |         |          |                   |                     | (2)                        |                                                  | Alternate f                                                          | unctions  |

|----------|--------|---------|--------|---------|----------|-------------------|---------------------|----------------------------|--------------------------------------------------|----------------------------------------------------------------------|-----------|

| LFBGA100 | LQFP48 | TFBGA64 | LQFP64 | LQFP100 | VFQFPN36 | Pin name          | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                              | Remap     |

| K2       | 13     | G3      | 17     | 26      | 10       | PA3               | I/O                 |                            | PA3                                              | USART2_RX <sup>(7)</sup> /<br>ADC12_IN3/<br>TIM2_CH4 <sup>(7)</sup>  |           |

| E4       | -      | C2      | 18     | 27      | -        | V <sub>SS_4</sub> | S                   |                            | $V_{SS_4}$                                       |                                                                      |           |

| F4       | -      | D2      | 19     | 28      | -        | V <sub>DD_4</sub> | S                   |                            | V <sub>DD_4</sub>                                |                                                                      |           |

| G3       | 14     | НЗ      | 20     | 29      | 11       | PA4               | I/O                 |                            | PA4                                              | SPI1_NSS <sup>(7)</sup> /<br>USART2_CK <sup>(7)</sup> /<br>ADC12_IN4 |           |

| НЗ       | 15     | F4      | 21     | 30      | 12       | PA5               | I/O                 |                            | PA5                                              | SPI1_SCK <sup>(7)</sup> /<br>ADC12_IN5                               |           |

| JЗ       | 16     | G4      | 22     | 31      | 13       | PA6               | I/O                 |                            | PA6                                              | SPI1_MISO <sup>(7)</sup> /<br>ADC12_IN6/<br>TIM3_CH1 <sup>(7)</sup>  | TIM1_BKIN |

| КЗ       | 17     | H4      | 23     | 32      | 14       | PA7               | I/O                 |                            | PA7                                              | SPI1_MOSI <sup>(7)</sup> /<br>ADC12_IN7/<br>TIM3_CH2 <sup>(7)</sup>  | TIM1_CH1N |

| G4       | -      | H5      | 24     | 33      |          | PC4               | I/O                 |                            | PC4                                              | ADC12_IN14                                                           |           |

| H4       | -      | H6      | 25     | 34      |          | PC5               | I/O                 |                            | PC5                                              | ADC12_IN15                                                           |           |

| J4       | 18     | F5      | 26     | 35      | 15       | PB0               | I/O                 |                            | PB0                                              | ADC12_IN8/<br>TIM3_CH3 <sup>(7)</sup>                                | TIM1_CH2N |

| K4       | 19     | G5      | 27     | 36      | 16       | PB1               | I/O                 |                            | PB1                                              | ADC12_IN9/<br>TIM3_CH4 <sup>(7)</sup>                                | TIM1_CH3N |

| G5       | 20     | G6      | 28     | 37      | 17       | PB2               | I/O                 | FT                         | PB2/BOOT1                                        |                                                                      |           |

| H5       | -      | -       | -      | 38      | -        | PE7               | I/O                 | FT                         | PE7                                              |                                                                      | TIM1_ETR  |

| J5       | -      | -       | -      | 39      | -        | PE8               | I/O                 | FT                         | PE8                                              |                                                                      | TIM1_CH1N |

| K5       | -      | -       | -      | 40      | -        | PE9               | I/O                 | FT                         | PE9                                              |                                                                      | TIM1_CH1  |

| G6       | -      | -       | -      | 41      | -        | PE10              | I/O                 | FT                         | PE10                                             |                                                                      | TIM1_CH2N |

| H6       | -      | -       | -      | 42      | -        | PE11              | I/O                 | FT                         | PE11                                             |                                                                      | TIM1_CH2  |

| J6       | -      | -       | -      | 43      | -        | PE12              | I/O                 | FT                         | PE12                                             |                                                                      | TIM1_CH3N |

| K6       | -      | -       | -      | 44      | -        | PE13              | I/O                 | FT                         | PE13                                             |                                                                      | TIM1_CH3  |

| G7       | -      | •       | -      | 45      | -        | PE14              | I/O                 | FT                         | PE14                                             |                                                                      | TIM1_CH4  |

| H7       | -      | -       | -      | 46      | -        | PE15              | I/O                 | FT                         | PE15                                             |                                                                      | TIM1_BKIN |

| J7       | 21     | G7      | 29     | 47      | -        | PB10              | I/O                 | FT                         | PB10                                             | I2C2_SCL/<br>USART3_TX <sup>(7)</sup>                                | TIM2_CH3  |

| K7       | 22     | H7      | 30     | 48      | -        | PB11              | I/O                 | FT                         | PB11                                             | I2C2_SDA/<br>USART3_RX <sup>(7)</sup>                                | TIM2_CH4  |

| E7       | 23     | D6      | 31     | 49      | 18       | V <sub>SS_1</sub> | S                   |                            | $V_{SS_1}$                                       |                                                                      |           |

| Table 5. | Medium-density | y STM32F103xx | pin definitions | (continued) |  |

|----------|----------------|---------------|-----------------|-------------|--|

|----------|----------------|---------------|-----------------|-------------|--|

|          |        | Pin     | IS     |         |          |                   |                                           | (2) |                         | Alternate f | unctions |

|----------|--------|---------|--------|---------|----------|-------------------|-------------------------------------------|-----|-------------------------|-------------|----------|

| LFBGA100 | LQFP48 | TFBGA64 | LQFP64 | LQFP100 | VFQFPN36 | Pin name          | L/D C C C C C C C C C C C C C C C C C C C |     | function <sup>(3)</sup> | Default     | Remap    |

| D4       | -      | -       | -      | 97      | -        | PE0               | I/O                                       | FT  | PE0                     | TIM4_ETR    |          |

| C4       | -      | -       | -      | 98      | -        | PE1               | I/O                                       | FT  | PE1                     |             |          |

| E5       | 47     | D4      | 63     | 99      | 36       | V <sub>SS_3</sub> | S                                         |     | $V_{SS_3}$              |             |          |

| F5       | 48     | E4      | 64     | 100     | 1        | V <sub>DD_3</sub> | S                                         |     | $V_{DD_3}$              |             |          |

Table 5.

Medium-density STM32F103xx pin definitions (continued)

1. I = input, O = output, S = supply, HiZ = high impedance.

2. FT = 5 V tolerant.

- 3. Function availability depends on the chosen device. For devices having reduced peripheral counts, it is always the lower number of peripheral that is included. For example, if a device has only one SPI and two USARTs, they will be called SPI1 and USART1 & USART2, respectively. Refer to *Table 2 on page 10*.

- 4. PC13, PC14 and PC15 are supplied through the power switch and since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 is restricted: only one I/O at a time can be used as an output, the speed has to be limited to 2 MHz with a maximum load of 30 pF and these I/Os must not be used as a current source (e.g. to drive an LED).

- 5. Main function after the first backup domain power-up. Later on, it depends on the contents of the Backup registers even after reset (because these registers are not reset by the main reset). For details on how to manage these IOs, refer to the Battery backup domain and BKP register description sections in the STM32F10xxx reference manual, available from the STMicroelectronics website: www.st.com.

- 6. Unlike in the LQFP64 package, there is no PC3 in the TFBGA64 package. The V<sub>REF+</sub> functionality is provided instead.

- This alternate function can be remapped by software to some other port pins (if available on the used package). For more

details, refer to the Alternate function I/O and debug configuration section in the STM32F10xxx reference manual, available

from the STMicroelectronics website: www.st.com.

- 8. The pins number 2 and 3 in the VFQFPN36 package, 5 and 6 in the LQFP48 and LQFP64 packages, and C1 and C2 in the TFBGA64 package are configured as OSC\_IN/OSC\_OUT after reset, however the functionality of PD0 and PD1 can be remapped by software on these pins. For the LQFP100 package, PD0 and PD1 are available by default, so there is no need for remapping. For more details, refer to the Alternate function I/O and debug configuration section in the STM32F10xxx reference manual.

The use of PD0 and PD1 in output mode is limited as they can only be used at 50 MHz in output mode.

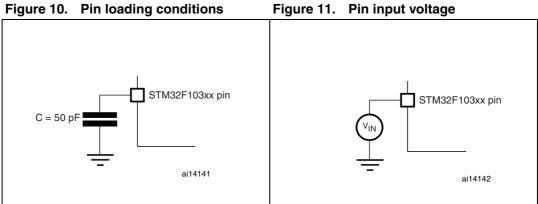

# Figure 10. Pin loading conditions

#### Power supply scheme 5.1.6

# Typical current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load).

- All peripherals are disabled except if it is explicitly mentioned.

- The Flash access time is adjusted to f<sub>HCLK</sub> frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 48 MHz and 2 wait states above).

- Ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in *Table 9*.

- Prefetch is ON (Reminder: this bit must be set before clock setting and bus prescaling)

- When the peripherals are enabled  $f_{PCLK1} = f_{HCLK}/4$ ,  $f_{PCLK2} = f_{HCLK}/2$ ,  $f_{ADCCLK} = f_{PCLK2}/4$

Table 17.Typical current consumption in Run mode, code with data processing<br/>running from Flash

|                 |                      |                                 |                   | Ту                                        | p <sup>(1)</sup>         |      |  |

|-----------------|----------------------|---------------------------------|-------------------|-------------------------------------------|--------------------------|------|--|

| Symbol          | Parameter            | Conditions                      | f <sub>HCLK</sub> | All peripherals<br>enabled <sup>(2)</sup> | All peripherals disabled | Unit |  |

|                 |                      |                                 | 72 MHz            | 36                                        | 27                       |      |  |

|                 |                      |                                 | 48 MHz            | 24.2                                      | 18.6                     |      |  |

|                 |                      |                                 | 36 MHz            | 19                                        | 14.8                     |      |  |

|                 |                      |                                 | 24 MHz            | 12.9                                      | 10.1                     |      |  |

|                 |                      |                                 | 16 MHz            | 9.3                                       | 7.4                      |      |  |

|                 |                      | External clock <sup>(3)</sup>   | 8 MHz             | 5.5                                       | 4.6                      | mA   |  |

|                 |                      |                                 | 4 MHz             | 3.3                                       | 2.8                      |      |  |

|                 |                      |                                 | 2 MHz             | 2.2                                       | 1.9                      |      |  |

|                 |                      |                                 | 1 MHz             | 1.6                                       | 1.45                     |      |  |

|                 |                      |                                 | 500 kHz           | 1.3                                       | 1.25                     |      |  |

| 1               | Supply<br>current in |                                 | 125 kHz           | 1.08                                      | 1.06                     |      |  |

| I <sub>DD</sub> | Run mode             |                                 |                   | 64 MHz                                    | 31.4                     | 23.9 |  |

|                 |                      |                                 | 48 MHz            | 23.5                                      | 17.9                     |      |  |

|                 |                      |                                 | 36 MHz            | 18.3                                      | 14.1                     |      |  |

|                 |                      | Running on high                 | 24 MHz            | 12.2                                      | 9.5                      |      |  |

|                 |                      | speed internal RC               | 16 MHz            | 8.5                                       | 6.8                      |      |  |

|                 |                      | (HSI), AHB<br>prescaler used to | 8 MHz             | 4.9                                       | 4                        | mA   |  |

|                 |                      | reduce the                      | 4 MHz             | 2.7                                       | 2.2                      |      |  |

|                 |                      | frequency                       | 2 MHz             | 1.6                                       | 1.4                      |      |  |

|                 |                      |                                 | 1 MHz             | 1.02                                      | 0.9                      |      |  |

|                 |                      |                                 | 500 kHz           | 0.73                                      | 0.67                     |      |  |

|                 |                      |                                 | 125 kHz           | 0.5                                       | 0.48                     |      |  |

1. Typical values are measures at  $T_A$  = 25 °C,  $V_{DD}$  = 3.3 V.

2. Add an additional power consumption of 0.8 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

3. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

1. Guaranteed by design, not tested in production.

#### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 16 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 22*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

# High-speed internal (HSI) RC oscillator

| Symbol               | Parameter                           | Conditions             | Min  | Тур | Max | Unit |

|----------------------|-------------------------------------|------------------------|------|-----|-----|------|

| f <sub>HSI</sub>     | Frequency                           |                        |      | 8   |     | MHz  |

|                      |                                     | $T_A = -40$ to 105 °C  | -2   | ±1  | 2.5 | %    |

| ACC .                | Accuracy of HSI oscillator          | $T_A = -10$ to 85 °C   | -1.5 | ±1  | 2.2 | %    |

| ACC <sub>HSI</sub>   |                                     | $T_A = 0$ to 70 °C     | -1.3 | ±1  | 2   | %    |

|                      |                                     | T <sub>A</sub> = 25 °C | -1.1 | ±1  | 1.8 | %    |

| t <sub>su(HSI)</sub> | HSI oscillator startup time         |                        | 1    |     | 2   | μs   |

| I <sub>DD(HSI)</sub> | HSI oscillator power<br>consumption |                        |      | 80  | 100 | μA   |

# Table 24. HSI oscillator characteristics<sup>(1) (2)</sup>

1. Guaranteed by design, not tested in production.

2.  $V_{DD} = 3.3$  V,  $T_A = -40$  to 105 °C unless otherwise specified.

# Low-speed internal (LSI) RC oscillator

# Table 25. LSI oscillator characteristics <sup>(1)</sup>

| Symbol                              | Parameter                        | Min | Тур  | Max | Unit |

|-------------------------------------|----------------------------------|-----|------|-----|------|

| f <sub>LSI</sub> <sup>(2)</sup>     | Frequency                        | 30  | 40   | 60  | kHz  |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time      |     |      | 85  | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption |     | 0.65 | 1.2 | μA   |

1.  $V_{DD}$  = 3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

2. Based on characterization, not tested in production.

3. Guaranteed by design, not tested in production.

#### Wakeup time from low-power mode

The wakeup times given in *Table 26* is measured on a wakeup phase with a 8-MHz HSI RC oscillator. The clock source used to wake up the device depends from the current operating mode:

- Stop or Standby mode: the clock source is the RC oscillator

- Sleep mode: the clock source is the clock that was set before entering Sleep mode.

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

# 5.3.11 Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

# Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

Table 32. ESD absolute maximum ratings

| Symbol                | Ratings                                               | Conditions                                              | Class | Maximum value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|---------------------------------------------------------|-------|------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | $T_A = +25 \ ^{\circ}C$<br>conforming to<br>JESD22-A114 | 2     | 2000                         | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | $T_A = +25 \text{ °C}$<br>conforming to<br>JESD22-C101  | 11    | 500                          | v    |

1. Based on characterization results, not tested in production.

# Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

#### Table 33.Electrical sensitivities

| Symbol | Parameter             | Conditions                            | Class      |

|--------|-----------------------|---------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +105$ °C conforming to JESD78A | II level A |

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to +/-8 mA, and sink +20 mA (with a relaxed  $V_{OL}$ ).

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 5.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating I<sub>VDD</sub> (see *Table 7*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating I<sub>VSS</sub> (see *Table 7*).

#### **Output voltage levels**

Unless otherwise specified, the parameters given in *Table 35* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*. All I/Os are CMOS and TTL compliant.

| Symbol                            | Parameter                                                                     | Conditions                                                 | Min                  | Max | Unit |

|-----------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------|----------------------|-----|------|

| V <sub>OL</sub> <sup>(1)</sup>    | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | TTL port                                                   |                      | 0.4 | V    |

| V <sub>OH</sub> <sup>(2)</sup>    | Output high level voltage for an I/O pin when 8 pins are sourced at same time | I <sub>IO</sub> = +8 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V | V <sub>DD</sub> -0.4 |     | v    |

| V <sub>OL</sub> <sup>(1)</sup>    | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | CMOS port                                                  |                      | 0.4 | V    |

| V <sub>OH</sub> <sup>(2)</sup>    | Output high level voltage for an I/O pin when 8 pins are sourced at same time | I <sub>IO</sub> =+ 8mA<br>2.7 V < V <sub>DD</sub> < 3.6 V  | 2.4                  |     | v    |

| V <sub>OL</sub> <sup>(1)(3)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | l <sub>IO</sub> = +20 mA                                   |                      | 1.3 | V    |

| V <sub>OH</sub> <sup>(2)(3)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at same time | 2.7 V < V <sub>DD</sub> < 3.6 V                            | V <sub>DD</sub> -1.3 |     | v    |

| V <sub>OL</sub> <sup>(1)(3)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | I <sub>IO</sub> = +6 mA                                    |                      | 0.4 | V    |

| V <sub>OH</sub> <sup>(2)(3)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at same time | 2 V < V <sub>DD</sub> < 2.7 V                              | V <sub>DD</sub> -0.4 |     | v    |

Table 35. Output voltage characteristics

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 7* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 7 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

3. Based on characterization data, not tested in production.

# Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 23* and *Table 36*, respectively.

Unless otherwise specified, the parameters given in *Table 36* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

| MODEx[1:0]<br>bit value <sup>(1)</sup>                                                                                                                                                                                                     | Symbol                                                            | Parameter                                                                                                                                | Conditions                                                        | Min | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|                                                                                                                                                                                                                                            | f <sub>max(IO)out</sub>                                           | Maximum frequency <sup>(2)</sup>                                                                                                         | $C_{L} = 50 \text{ pF}, V_{DD} = 2 \text{ V to } 3.6 \text{ V}$   |     | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MHz  |

| 10                                                                                                                                                                                                                                         | t <sub>f(IO)out</sub>                                             | Output high to low<br>level fall time                                                                                                    | С <sub>1</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V            |     | 125 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ns   |

|                                                                                                                                                                                                                                            | t <sub>r(IO)out</sub>                                             | Output low to high<br>level rise time                                                                                                    | $V_{\rm DD} = 2$ v to 3.0 v                                       |     | $\begin{array}{c c} & 2 \\ & 125^{(3)} \\ & 125^{(3)} \\ & 10 \\ & 25^{(3)} \\ & 25^{(3)} \\ & 25^{(3)} \\ & 50 \\ & 30 \\ & 20 \\ & 50 \\ & 30 \\ & 12^{(3)} \\ & 8^{(3)} \\ & 12^{(3)} \\ & 8^{(3)} \\ & 12^{(3)} \\ & 8^{(3)} \\ & 12^{(3)} \\ & & 12^{(3)} \\ & & \\ \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 115  |

|                                                                                                                                                                                                                                            | f <sub>max(IO)out</sub>                                           | Maximum frequency <sup>(2)</sup>                                                                                                         | $C_{L} = 50 \text{ pF}, V_{DD} = 2 \text{ V to } 3.6 \text{ V}$   |     | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | MHz  |

| 01                                                                                                                                                                                                                                         | Output I                                                          | Output high to low<br>level fall time                                                                                                    | C = 50  pE V = 2 V  to  2  eV                                     |     | 25 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

|                                                                                                                                                                                                                                            | t <sub>r(IO)out</sub>                                             | $\begin{array}{c} C_{L} = 50 \text{ pF}, \text{ V}_{DD} = 2 \text{ V to } 3.6 \text{ V} \\ \hline \\ \text{level rise time} \end{array}$ |                                                                   |     | 25 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ns   |

|                                                                                                                                                                                                                                            |                                                                   |                                                                                                                                          | $C_{L} = 30 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$ |     | MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

|                                                                                                                                                                                                                                            | F <sub>max(IO)out</sub>                                           | Maximum frequency <sup>(2)</sup>                                                                                                         | $C_{L} = 50 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$ |     | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | MHz  |

|                                                                                                                                                                                                                                            |                                                                   |                                                                                                                                          | $C_{L} = 50 \text{ pF}, V_{DD} = 2 \text{ V to } 2.7 \text{ V}$   |     | 2<br>125 <sup>(3)</sup><br>125 <sup>(3)</sup><br>10<br>25 <sup>(3)</sup><br>25 <sup>(3)</sup><br>30<br>20<br>5 <sup>(3)</sup><br>8 <sup>(3)</sup><br>12 <sup>(3)</sup><br>8 <sup>(3)</sup><br>12 <sup>(3)</sup><br>8 <sup>(3)</sup><br>12 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | MHz  |