Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, Motor Control PWM, PDR, POR, PVD, PWM, Temp Sensor, WDT          |

| Number of I/O              | 26                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 20K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 10x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 36-VFQFN Exposed Pad                                                  |

| Supplier Device Package    | 36-VFQFPN (6x6)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f103tbu6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 | Introd | luction   |                                                                        |

|---|--------|-----------|------------------------------------------------------------------------|

| 2 | Descr  | ription . | 9                                                                      |

|   | 2.1    | Device of | overview                                                               |

|   | 2.2    | Full com  | npatibility throughout the family                                      |

|   | 2.3    | Overvie   | w 12                                                                   |

|   |        | 2.3.1     | ARM® CortexTM-M3 core with embedded Flash and SRAM12                   |

|   |        | 2.3.2     | Embedded Flash memory12                                                |

|   |        | 2.3.3     | CRC (cyclic redundancy check) calculation unit                         |

|   |        | 2.3.4     | Embedded SRAM                                                          |

|   |        | 2.3.5     | Nested vectored interrupt controller (NVIC)                            |

|   |        | 2.3.6     | External interrupt/event controller (EXTI)                             |

|   |        | 2.3.7     | Clocks and startup                                                     |

|   |        | 2.3.8     | Boot modes                                                             |

|   |        | 2.3.9     | Power supply schemes                                                   |

|   |        | 2.3.10    | Power supply supervisor                                                |

|   |        | 2.3.11    | Voltage regulator                                                      |

|   |        | 2.3.12    | Low-power modes                                                        |

|   |        | 2.3.13    | DMA                                                                    |

|   |        | 2.3.14    | RTC (real-time clock) and backup registers                             |

|   |        | 2.3.15    | Timers and watchdogs                                                   |

|   |        | 2.3.16    | $I^2C$ bus $\ldots \ldots \ldots 17$                                   |

|   |        | 2.3.17    | Universal synchronous/asynchronous receiver transmitter (USART) $\$ 17 |

|   |        | 2.3.18    | Serial peripheral interface (SPI)17                                    |

|   |        | 2.3.19    | Controller area network (CAN)17                                        |

|   |        | 2.3.20    | Universal serial bus (USB) 17                                          |

|   |        | 2.3.21    | GPIOs (general-purpose inputs/outputs)                                 |

|   |        | 2.3.22    | ADC (analog-to-digital converter)                                      |

|   |        | 2.3.23    | Temperature sensor                                                     |

|   |        | 2.3.24    | Serial wire JTAG debug port (SWJ-DP) 18                                |

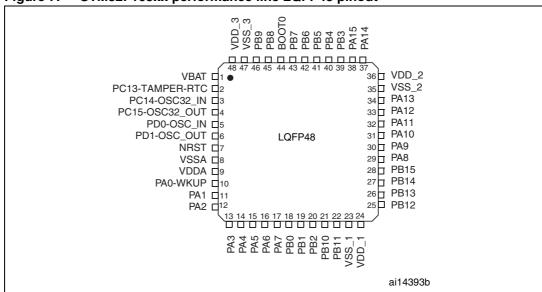

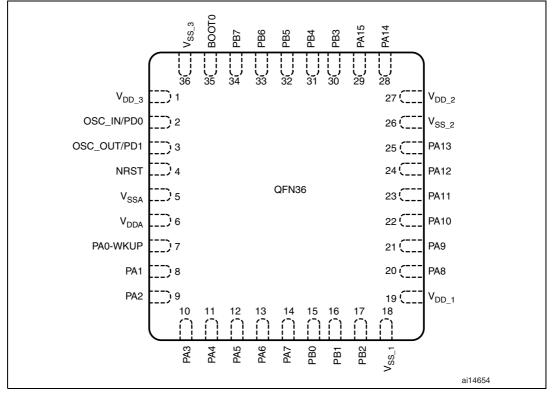

| 3 | Pinou  | its and j | pin description 21                                                     |

| 4 | Memo   | ory map   | ping                                                                   |

# 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32F103x8 and STM32F103xB medium-density performance line microcontrollers. For more details on the whole STMicroelectronics STM32F103xx family, please refer to *Section 2.2: Full compatibility throughout the family*.

The medium-density STM32F103xx datasheet should be read in conjunction with the low-, medium- and high-density STM32F10xxx reference manual. The reference and Flash programming manuals are both available from the STMicroelectronics website www.st.com.

For information on the Cortex<sup>™</sup>-M3 core please refer to the Cortex<sup>™</sup>-M3 Technical Reference Manual, available from the www.arm.com website at the following address: http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.ddi0337e/.

# 2 Description

The STM32F103x8 and STM32F103xB performance line family incorporates the highperformance ARM Cortex<sup>™</sup>-M3 32-bit RISC core operating at a 72 MHz frequency, highspeed embedded memories (Flash memory up to 128 Kbytes and SRAM up to 20 Kbytes), and an extensive range of enhanced I/Os and peripherals connected to two APB buses. All devices offer two 12-bit ADCs, three general purpose 16-bit timers plus one PWM timer, as well as standard and advanced communication interfaces: up to two I<sup>2</sup>Cs and SPIs, three USARTs, an USB and a CAN.

The STM32F103xx medium-density performance line family operates from a 2.0 to 3.6 V power supply. It is available in both the -40 to +85 °C temperature range and the -40 to +105 °C extended temperature range. A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F103xx medium-density performance line family includes devices in six different package types: from 36 pins to 100 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

These features make the STM32F103xx medium-density performance line microcontroller family suitable for a wide range of applications:

- Motor drive and application control

- Medical and handheld equipment

- PC peripherals gaming and GPS platforms

- Industrial applications: PLC, inverters, printers, and scanners

- Alarm systems, Video intercom, and HVAC

*Figure 1* shows the general block diagram of the device family.

# 2.1 Device overview

|               | Peripheral         | STM32F103Tx                         | STM32  | F103Cx | STM32F103Rx        |        | STM32F103Vx          |        |  |

|---------------|--------------------|-------------------------------------|--------|--------|--------------------|--------|----------------------|--------|--|

| Flash         | n - Kbytes         | 64                                  | 64     | 128    | 64 128             |        | 64                   | 128    |  |

| SRAI          | M - Kbytes         | 20                                  | 20     | 20     | 2                  | 0      | 2                    | 20     |  |

| ers           | General-purpose    | 3                                   | 3      | 3      | :                  | 3      | :                    | 3      |  |

| Timers        | Advanced-control   | 1                                   | -      | 1      |                    | 1      | -                    | 1      |  |

| L             | SPI                | 1                                   | 2      | 2      | 2                  | 2      |                      | 2      |  |

| Communication | l <sup>2</sup> C   | 1                                   | 2      | 2      | 2                  | 2      | 2                    | 2      |  |

| unic          | USART              | 2                                   | 3      | 3      | 3 3                |        | 3                    |        |  |

| omn           | USB                | 1                                   | 1      | 1      | 1                  |        | -                    | 1      |  |

| S             | CAN                | 1                                   | 1      | 1      | 1                  |        | 1                    |        |  |

| GPIC          | )s                 | 26                                  | 3      | 7      | 5                  | 1      | 8                    | 0      |  |

| 12-bi         | t synchronized ADC | 2                                   | 2      | 2 2    |                    | 2      | 2                    |        |  |

| Num           | ber of channels    | 10 channels                         | 10 cha | annels | 16 cha             | annels | 16 cha               | annels |  |

| CPU           | frequency          |                                     |        | 72     | MHz                |        |                      |        |  |

| Oper          | ating voltage      |                                     |        | 2.0 to | 9.6 V              |        |                      |        |  |

| Oper          | ating temperatures | Ambient tempera<br>Junction tempera |        |        |                    |        | (see <i>Tab</i>      | ole 9) |  |

| Pack          | ages               | VFQFPN36                            | LQF    | P48    | LQFP64,<br>TFBGA64 |        | LQFP100,<br>LFBGA100 |        |  |

#### Table 2. STM32F103xx medium-density device features and peripheral counts

## 2.2 Full compatibility throughout the family

The STM32F103xx is a complete family whose members are fully pin-to-pin, software and feature compatible. In the reference manual, the STM32F103x4 and STM32F103x6 are identified as low-density devices, the STM32F103x8 and STM32F103xB are referred to as medium-density devices, and the STM32F103xC, STM32F103xD and STM32F103xE are referred to as high-density devices.

Low- and high-density devices are an extension of the STM32F103x8/B devices, they are specified in the STM32F103x4/6 and STM32F103xC/D/E datasheets, respectively. Low-density devices feature lower Flash memory and RAM capacities, less timers and peripherals. High-density devices have higher Flash memory and RAM capacities, and additional peripherals like SDIO, FSMC, I<sup>2</sup>S and DAC, while remaining fully compatible with the other members of the STM32F103xx family.

The STM32F103x4, STM32F103x6, STM32F103xC, STM32F103xD and STM32F103xE are a drop-in replacement for STM32F103x8/B medium-density devices, allowing the user to try different memory densities and providing a greater degree of freedom during the development cycle.

Moreover, the STM32F103xx performance line family is fully compatible with all existing STM32F101xx access line and STM32F102xx USB access line devices.

|        | Low-dens                                     | ity devices | Medium-den                                             | sity devices            | High-density devices                                                                                                                                                        |                 |                 |  |  |

|--------|----------------------------------------------|-------------|--------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|--|--|

| Pinout | 16 KB 32 KB<br>Flash Flash <sup>(1)</sup>    |             | 64 KB<br>Flash                                         | 128 KB<br>Flash         | 256 KB<br>Flash                                                                                                                                                             | 384 KB<br>Flash | 512 KB<br>Flash |  |  |

|        | 6 KB RAM                                     | 10 KB RAM   | 20 KB RAM                                              | 20 KB RAM               | 48 KB RAM                                                                                                                                                                   | 64 KB RAM       | 64 KB RAM       |  |  |

| 144    |                                              |             |                                                        |                         | 5 × USARTs<br>4 × 16-bit timers, 2 × basic timers<br>3 × SPIs, 2 × $I^2$ Ss, 2 × I2Cs<br>USB, CAN, 2 × PWM timers<br>3 × ADCs, 1 × DAC, 1 × SDIO<br>FSMC (100 and 144 pins) |                 |                 |  |  |

| 100    |                                              |             | 3 × USARTs                                             |                         |                                                                                                                                                                             |                 |                 |  |  |

| 64     | 2 × USART:<br>2 × 16-bit tir<br>1 × SPI, 1 × | mers        | $3 \times 16$ -bit tim<br>2 × SPIs, 2 ×<br>CAN, 1 × PW | l <sup>2</sup> Cs, USB, |                                                                                                                                                                             |                 |                 |  |  |

| 48     | CAN, 1 × P                                   |             | 2 × ADC                                                |                         |                                                                                                                                                                             |                 |                 |  |  |

| 36     | 2 × ADCs                                     |             |                                                        |                         |                                                                                                                                                                             |                 |                 |  |  |

Table 3.STM32F103xx family

For orderable part numbers that do not show the A internal code after the temperature range code (6 or 7), the reference datasheet for electrical characteristics is that of the STM32F103x8/B medium-density devices.

in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$ , without the need for an external reset circuit.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

Refer to Table 11: Embedded reset and power control block characteristics for the values of  $V_{POR/PDR}$  and  $V_{PVD}$ .

#### 2.3.11 Voltage regulator

The regulator has three operation modes: main (MR), low power (LPR) and power down.

- MR is used in the nominal regulation mode (Run)

- LPR is used in the Stop mode

- Power down is used in Standby mode: the regulator output is in high impedance: the kernel circuitry is powered down, inducing zero consumption (but the contents of the registers and SRAM are lost)

This regulator is always enabled after reset. It is disabled in Standby mode, providing high impedance output.

#### 2.3.12 Low-power modes

The STM32F103xx performance line supports three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

• Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

• Stop mode

The Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low power mode.

The device can be woken up from Stop mode by any of the EXTI line. The EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm or the USB wakeup.

Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.8 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, SRAM and register contents are lost except for registers in the Backup domain and Standby circuitry.

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped by entering Stop or Standby mode.

| igure | 1                         | 2                    | 3         | 4       | 5       | 6           | 7      | 8       |

|-------|---------------------------|----------------------|-----------|---------|---------|-------------|--------|---------|

| A     | •<br>/PC14-<br>O\\$C32_IN | , PC13-,<br>AMPER-RT | C ( PB9 ) | ( PB4 ) | ( PB3 ) | (PA15)      | (PA14) | (PA13)  |

| В     | ,Ρ́C15-`,<br>OŚC32_ΟUT    | VBAT                 | (PB8)     | BOOTO   | ( PD2 ) | (PC11)      | (PC10) | (PA12)  |

| С     | OSC_IN                    | Vss_4                | (PB7)     | (PB5)   | (PC12)  | (PA10)      | (PA9)  | (PA11)  |

| D     | OSC_OUT                   | VDD_4                | (PB6)     | VSS_3   | VSS_2   | ,<br>VSS_1, | (PA8)  | (PC9)   |

| E     | (NRST)                    | (PC1)                | (PC0)     | WDD_3'  | VDD_2'  | VDD_1       | (PC7)  | (PC8)   |

| F     | (VSSA)                    | (PC2)                | (PA2)     | ( PA5 ) | (PB0)   | (PC6)       | (PB15) | (PB14)  |

| G     | WREF+i                    | PĄO-WKŲP             | (PA3)     | PA6     | (PB1)   | (PB2)       | (PB10) | (PB13)  |

| н     | VDDA,                     | ( PA1 )              | (PA4)     | PA7     | (PC4)   | (PC5)       | (PB11) | (PB12)  |

|       |                           |                      |           |         |         |             |        | AI15494 |

Figure 6. STM32F103xx performance line TFBGA64 ballout

5

|          |        | Pin     | IS     |         |          |                   |                     | (2)                        |                                                  | Alternate f                                                          | unctions  |

|----------|--------|---------|--------|---------|----------|-------------------|---------------------|----------------------------|--------------------------------------------------|----------------------------------------------------------------------|-----------|

| LFBGA100 | LQFP48 | TFBGA64 | LQFP64 | LQFP100 | VFQFPN36 | Pin name          | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                              | Remap     |

| K2       | 13     | G3      | 17     | 26      | 10       | PA3               | I/O                 |                            | PA3                                              | USART2_RX <sup>(7)</sup> /<br>ADC12_IN3/<br>TIM2_CH4 <sup>(7)</sup>  |           |

| E4       | -      | C2      | 18     | 27      | -        | V <sub>SS_4</sub> | S                   |                            | $V_{SS_4}$                                       |                                                                      |           |

| F4       | -      | D2      | 19     | 28      | -        | V <sub>DD_4</sub> | S                   |                            | V <sub>DD_4</sub>                                |                                                                      |           |

| G3       | 14     | НЗ      | 20     | 29      | 11       | PA4               | I/O                 |                            | PA4                                              | SPI1_NSS <sup>(7)</sup> /<br>USART2_CK <sup>(7)</sup> /<br>ADC12_IN4 |           |

| НЗ       | 15     | F4      | 21     | 30      | 12       | PA5               | I/O                 |                            | PA5                                              | SPI1_SCK <sup>(7)</sup> /<br>ADC12_IN5                               |           |

| JЗ       | 16     | G4      | 22     | 31      | 13       | PA6               | I/O                 |                            | PA6                                              | SPI1_MISO <sup>(7)</sup> /<br>ADC12_IN6/<br>TIM3_CH1 <sup>(7)</sup>  | TIM1_BKIN |

| КЗ       | 17     | H4      | 23     | 32      | 14       | PA7               | I/O                 |                            | PA7                                              | SPI1_MOSI <sup>(7)</sup> /<br>ADC12_IN7/<br>TIM3_CH2 <sup>(7)</sup>  | TIM1_CH1N |

| G4       | -      | H5      | 24     | 33      |          | PC4               | I/O                 |                            | PC4                                              | ADC12_IN14                                                           |           |

| H4       | -      | H6      | 25     | 34      |          | PC5               | I/O                 |                            | PC5                                              | ADC12_IN15                                                           |           |

| J4       | 18     | F5      | 26     | 35      | 15       | PB0               | I/O                 |                            | PB0                                              | ADC12_IN8/<br>TIM3_CH3 <sup>(7)</sup>                                | TIM1_CH2N |

| K4       | 19     | G5      | 27     | 36      | 16       | PB1               | I/O                 |                            | PB1                                              | ADC12_IN9/<br>TIM3_CH4 <sup>(7)</sup>                                | TIM1_CH3N |

| G5       | 20     | G6      | 28     | 37      | 17       | PB2               | I/O                 | FT                         | PB2/BOOT1                                        |                                                                      |           |

| H5       | -      | -       | -      | 38      | -        | PE7               | I/O                 | FT                         | PE7                                              |                                                                      | TIM1_ETR  |

| J5       | -      | -       | -      | 39      | -        | PE8               | I/O                 | FT                         | PE8                                              |                                                                      | TIM1_CH1N |

| K5       | -      | -       | -      | 40      | -        | PE9               | I/O                 | FT                         | PE9                                              |                                                                      | TIM1_CH1  |

| G6       | -      | -       | -      | 41      | -        | PE10              | I/O                 | FT                         | PE10                                             |                                                                      | TIM1_CH2N |

| H6       | -      | -       | -      | 42      | -        | PE11              | I/O                 | FT                         | PE11                                             |                                                                      | TIM1_CH2  |

| J6       | -      | -       | -      | 43      | -        | PE12              | I/O                 | FT                         | PE12                                             |                                                                      | TIM1_CH3N |

| K6       | -      | -       | -      | 44      | -        | PE13              | I/O                 | FT                         | PE13                                             |                                                                      | TIM1_CH3  |

| G7       | -      | •       | -      | 45      | -        | PE14              | I/O                 | FT                         | PE14                                             |                                                                      | TIM1_CH4  |

| H7       | -      | -       | -      | 46      | -        | PE15              | I/O                 | FT                         | PE15                                             |                                                                      | TIM1_BKIN |

| J7       | 21     | G7      | 29     | 47      | -        | PB10              | I/O                 | FT                         | PB10                                             | I2C2_SCL/<br>USART3_TX <sup>(7)</sup>                                | TIM2_CH3  |

| K7       | 22     | H7      | 30     | 48      | -        | PB11              | I/O                 | FT                         | PB11                                             | I2C2_SDA/<br>USART3_RX <sup>(7)</sup>                                | TIM2_CH4  |

| E7       | 23     | D6      | 31     | 49      | 18       | V <sub>SS_1</sub> | S                   |                            | $V_{SS_1}$                                       |                                                                      |           |

| Table 5. | Medium-density | y STM32F103xx | pin definitions | (continued) |  |

|----------|----------------|---------------|-----------------|-------------|--|

|----------|----------------|---------------|-----------------|-------------|--|

## STM32F103x8, STM32F103xB

57

|          |        | Pir     | IS     |         |          |                   |                     | (2)                        |                                                  | Alternate                                            | functions                            |

|----------|--------|---------|--------|---------|----------|-------------------|---------------------|----------------------------|--------------------------------------------------|------------------------------------------------------|--------------------------------------|

| LFBGA100 | LQFP48 | TFBGA64 | LQFP64 | LQFP100 | VFQFPN36 | Pin name          | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                              | Remap                                |

| A10      | 34     | A8      | 46     | 72      | 25       | PA13              | I/O                 | FT                         | JTMS/SWDIO                                       |                                                      | PA13                                 |

| F8       | -      | -       | -      | 73      | -        |                   |                     | Not                        | connected                                        |                                                      |                                      |

| E6       | 35     | D5      | 47     | 74      | 26       | V <sub>SS_2</sub> | S                   |                            | V <sub>SS_2</sub>                                |                                                      |                                      |

| F6       | 36     | E5      | 48     | 75      | 27       | V <sub>DD_2</sub> | S                   |                            | V <sub>DD_2</sub>                                |                                                      |                                      |

| A9       | 37     | A7      | 49     | 76      | 28       | PA14              | I/O                 | FT                         | JTCK/SWCLK                                       |                                                      | PA14                                 |

| A8       | 38     | A6      | 50     | 77      | 29       | PA15              | I/O                 | FT                         | JTDI                                             |                                                      | TIM2_CH1_ETR/<br>PA15 /SPI1_NSS      |

| B9       | -      | B7      | 51     | 78      |          | PC10              | I/O                 | FT                         | PC10                                             |                                                      | USART3_TX                            |

| B8       | -      | B6      | 52     | 79      |          | PC11              | I/O                 | FT                         | PC11                                             |                                                      | USART3_RX                            |

| C8       | -      | C5      | 53     | 80      |          | PC12              | I/O                 | FT                         | PC12                                             |                                                      | USART3_CK                            |

| D8       | 5      | C1      | 5      | 81      | 2        | PD0               | I/O                 | FT                         | OSC_IN <sup>(8)</sup>                            |                                                      | CANRX                                |

| E8       | 6      | D1      | 6      | 82      | 3        | PD1               | I/O                 | FT                         | OSC_OUT <sup>(8)</sup>                           |                                                      | CANTX                                |

| B7       |        | B5      | 54     | 83      | -        | PD2               | I/O                 | FT                         | PD2                                              | TIM3_ETR                                             |                                      |

| C7       | -      | -       | -      | 84      | -        | PD3               | I/O                 | FT                         | PD3                                              |                                                      | USART2_CTS                           |

| D7       | -      | -       | -      | 85      | -        | PD4               | I/O                 | FT                         | PD4                                              |                                                      | USART2_RTS                           |

| B6       | -      | -       | -      | 86      | -        | PD5               | I/O                 | FT                         | PD5                                              |                                                      | USART2_TX                            |

| C6       | -      | -       | -      | 87      | -        | PD6               | I/O                 | FT                         | PD6                                              |                                                      | USART2_RX                            |

| D6       | -      | -       | -      | 88      | -        | PD7               | I/O                 | FT                         | PD7                                              |                                                      | USART2_CK                            |

| A7       | 39     | A5      | 55     | 89      | 30       | PB3               | I/O                 | FT                         | JTDO                                             |                                                      | TIM2_CH2/PB3<br>TRACESWO<br>SPI1_SCK |

| A6       | 40     | A4      | 56     | 90      | 31       | PB4               | I/O                 | FT                         | JNTRST                                           |                                                      | TIM3_CH1/PB4/<br>SPI1_MISO           |

|          |        |         |        |         |          |                   |                     |                            |                                                  |                                                      |                                      |

| C5       | 41     | C4      | 57     | 91      | 32       | PB5               | I/O                 |                            | PB5                                              | I2C1_SMBAI                                           | TIM3_CH2 /<br>SPI1_MOSI              |

| B5       | 42     | D3      | 58     | 92      | 33       | PB6               | I/O                 | FT                         | PB6                                              | l2C1_SCL <sup>(7)</sup> /<br>TIM4_CH1 <sup>(7)</sup> | USART1_TX                            |

| A5       | 43     | C3      | 59     | 93      | 34       | PB7               | I/O                 | FT                         | PB7                                              | I2C1_SDA <sup>(7)</sup> /<br>TIM4_CH2 <sup>(7)</sup> | USART1_RX                            |

| D5       | 44     | B4      | 60     | 94      | 35       | BOOT0             | Ι                   |                            | BOOT0                                            |                                                      |                                      |

| B4       | 45     | B3      | 61     | 95      | -        | PB8               | I/O                 | FT                         | PB8                                              | TIM4_CH3 <sup>(7)</sup>                              | I2C1_SCL /<br>CANRX                  |

| A4       | 46     | A3      | 62     | 96      | -        | PB9               | I/O                 | FT                         | PB9                                              | TIM4_CH4 <sup>(7)</sup>                              | I2C1_SDA/<br>CANTX                   |

## Table 5. Medium-density STM32F103xx pin definitions (continued)

# 5 Electrical characteristics

## 5.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to  $V_{SS}$ .

### 5.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

## 5.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A$  = 25 °C,  $V_{DD}$  = 3.3 V (for the 2 V  $\leq$   $V_{DD}$   $\leq$  3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\Sigma$ ).

### 5.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

## 5.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 10*.

### 5.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 11*.

| Symbol                                  | Ratings                                                                                  | Max. | Unit |

|-----------------------------------------|------------------------------------------------------------------------------------------|------|------|

| I <sub>VDD</sub>                        | Total current into V <sub>DD</sub> /V <sub>DDA</sub> power lines (source) <sup>(1)</sup> | 150  |      |

| I <sub>VSS</sub>                        | Total current out of $V_{SS}$ ground lines (sink) <sup>(1)</sup>                         | 150  |      |

| 1                                       | Output current sunk by any I/O and control pin                                           | 25   |      |

| IIO                                     | Output current source by any I/Os and control pin                                        | - 25 | mA   |

|                                         | Injected current on NRST pin                                                             | ± 5  | ШA   |

| I <sub>INJ(PIN)</sub> <sup>(2)(3)</sup> | Injected current on HSE OSC_IN and LSE OSC_IN pins                                       | ± 5  |      |

|                                         | Injected current on any other pin <sup>(4)</sup>                                         | ± 5  |      |

| $\Sigma I_{INJ(PIN)}^{(2)}$             | Total injected current (sum of all I/O and control pins) <sup>(4)</sup>                  | ± 25 |      |

Table 7.Current characteristics

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub> > V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>.

3. Negative injection disturbs the analog performance of the device. See note in *Section 5.3.17: 12-bit ADC characteristics*.

4. When several inputs are submitted to a current injection, the maximum Σl<sub>INJ(PIN)</sub> is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterization with Σl<sub>INJ(PIN)</sub> maximum current injection on four I/O port pins of the device.

Table 8.Thermal characteristics

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | °C   |

# 5.3 Operating conditions

### 5.3.1 General operating conditions

#### Table 9.General operating conditions

| Symbol                          | Parameter                                  | Conditions                        | Min | Max | Unit |

|---------------------------------|--------------------------------------------|-----------------------------------|-----|-----|------|

| f <sub>HCLK</sub>               | Internal AHB clock frequency               |                                   | 0   | 72  |      |

| f <sub>PCLK1</sub>              | Internal APB1 clock frequency              |                                   | 0   | 36  | MHz  |

| f <sub>PCLK2</sub>              | Internal APB2 clock frequency              |                                   | 0   | 72  |      |

| V <sub>DD</sub>                 | Standard operating voltage                 |                                   | 2   | 3.6 | V    |

| V <sub>DDA</sub> <sup>(1)</sup> | Analog operating voltage<br>(ADC not used) | Must be the same potential        | 2   | 3.6 | V    |

| V DDA`´                         | Analog operating voltage<br>(ADC used)     | as V <sub>DD</sub> <sup>(2)</sup> | 2.4 | 3.6 | v    |

| V <sub>BAT</sub>                | Backup operating voltage                   |                                   | 1.8 | 3.6 | V    |

| Symbol | Parameter         | Conditions                          |                   | Ма                     | ax <sup>(1)</sup>       | Unit |  |

|--------|-------------------|-------------------------------------|-------------------|------------------------|-------------------------|------|--|

| Symbol | Falameter         | Conditions                          | <sup>f</sup> HCLK | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Onic |  |

|        |                   |                                     | 72 MHz            | 50                     | 50.3                    |      |  |

|        |                   |                                     | 48 MHz            | 36.1                   | 36.2                    |      |  |

|        |                   | External clock <sup>(2)</sup> , all | 36 MHz            | 28.6                   | 28.7                    |      |  |

|        | Supply current in | peripherals enabled                 | 24 MHz            | 19.9                   | 20.1                    | - mA |  |

|        |                   |                                     | 16 MHz            | 14.7                   | 14.9                    |      |  |

|        |                   |                                     | 8 MHz             | 8.6                    | 8.9                     |      |  |

| IDD    | Run mode          |                                     | 72 MHz            | 32.8                   | 32.9                    |      |  |

|        |                   |                                     | 48 MHz            | 24.4                   | 24.5                    |      |  |

|        |                   | External clock <sup>(2)</sup> , all | 36 MHz            | 19.8                   | 19.9                    |      |  |

|        |                   | peripherals disabled                | 24 MHz            | 13.9                   | 14.2                    |      |  |

|        |                   |                                     | 16 MHz            | 10.7                   | 11                      |      |  |

|        |                   |                                     | 8 MHz             | 6.8                    | 7.1                     |      |  |

# Table 13.Maximum current consumption in Run mode, code with data processing<br/>running from Flash

1. Based on characterization, not tested in production.

2. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

# Table 14.Maximum current consumption in Run mode, code with data processing<br/>running from RAM

| Symbol | Parameter                        | Conditions                                                                                                                                                                            | fhclk  | Ма                     | Unit                    |      |

|--------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------|-------------------------|------|

|        | Falametei                        |                                                                                                                                                                                       |        | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Onit |

|        | Supply<br>current in<br>Run mode | Supply<br>current in<br>Run mode<br>External clock <sup>(2)</sup> , all<br>1<br>8<br>7<br>4<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>7<br>4<br>7<br>4<br>7<br>4<br>7<br>4<br>7 | 72 MHz | 48                     | 50                      |      |

|        |                                  |                                                                                                                                                                                       | 48 MHz | 31.5                   | 32                      |      |

|        |                                  |                                                                                                                                                                                       | 36 MHz | 24                     | 25.5                    |      |

|        |                                  |                                                                                                                                                                                       | 24 MHz | 17.5                   | 18                      |      |

|        |                                  |                                                                                                                                                                                       | 16 MHz | 12.5                   | 13                      |      |

| 1      |                                  |                                                                                                                                                                                       | 8 MHz  | 7.5                    | 8                       | mA   |

| IDD    |                                  |                                                                                                                                                                                       | 72 MHz | 29                     | 29.5                    |      |

|        |                                  |                                                                                                                                                                                       | 48 MHz | 20.5                   | 21                      |      |

|        |                                  |                                                                                                                                                                                       | 36 MHz | 16                     | 16.5                    |      |

|        |                                  |                                                                                                                                                                                       | 24 MHz | 11.5                   | 12                      |      |

|        |                                  |                                                                                                                                                                                       | 16 MHz | 8.5                    | 9                       |      |

|        |                                  |                                                                                                                                                                                       | 8 MHz  | 5.5                    | 6                       |      |

1. Based on characterization, tested in production at  $V_{\text{DD}}$  max,  $f_{\text{HCLK}}$  max.

2. External clock is 8 MHz and PLL is on when  $f_{\text{HCLK}}$  > 8 MHz.

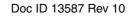

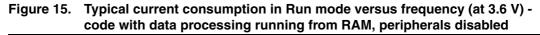

Figure 14. Typical current consumption in Run mode versus frequency (at 3.6 V) - code with data processing running from RAM, peripherals enabled

|                 | Parameter                          | Conditions                                                                                      | fhclk   | Туј                                       |                          |      |

|-----------------|------------------------------------|-------------------------------------------------------------------------------------------------|---------|-------------------------------------------|--------------------------|------|

| Symbol          |                                    |                                                                                                 |         | All peripherals<br>enabled <sup>(2)</sup> | All peripherals disabled | Unit |

|                 |                                    |                                                                                                 | 72 MHz  | 14.4                                      | 5.5                      |      |

|                 |                                    |                                                                                                 | 48 MHz  | 9.9                                       | 3.9                      |      |

|                 |                                    |                                                                                                 | 36 MHz  | 7.6                                       | 3.1                      |      |

|                 |                                    |                                                                                                 | 24 MHz  | 5.3                                       | 2.3                      |      |

|                 |                                    |                                                                                                 | 16 MHz  | 3.8                                       | 1.8                      |      |

|                 |                                    | External clock <sup>(3)</sup>                                                                   | 8 MHz   | 2.1                                       | 1.2                      |      |

|                 | Supply<br>current in<br>Sleep mode |                                                                                                 | 4 MHz   | 1.6                                       | 1.1                      |      |

|                 |                                    |                                                                                                 | 2 MHz   | 1.3                                       | 1                        | - mA |

|                 |                                    |                                                                                                 | 1 MHz   | 1.11                                      | 0.98                     |      |

|                 |                                    |                                                                                                 | 500 kHz | 1.04                                      | 0.96                     |      |

|                 |                                    |                                                                                                 | 125 kHz | 0.98                                      | 0.95                     |      |

| I <sub>DD</sub> |                                    | Running on high<br>speed internal RC<br>(HSI), AHB prescaler<br>used to reduce the<br>frequency | 64 MHz  | 12.3                                      | 4.4                      |      |

|                 |                                    |                                                                                                 | 48 MHz  | 9.3                                       | 3.3                      |      |

|                 |                                    |                                                                                                 | 36 MHz  | 7                                         | 2.5                      |      |

|                 |                                    |                                                                                                 | 24 MHz  | 4.8                                       | 1.8                      |      |

|                 |                                    |                                                                                                 | 16 MHz  | 3.2                                       | 1.2                      |      |

|                 |                                    |                                                                                                 | 8 MHz   | 1.6                                       | 0.6                      |      |

|                 |                                    |                                                                                                 | 4 MHz   | 1                                         | 0.5                      |      |

|                 |                                    |                                                                                                 | 2 MHz   | 0.72                                      | 0.47                     |      |

|                 |                                    |                                                                                                 | 1 MHz   | 0.56                                      | 0.44                     |      |

|                 |                                    |                                                                                                 | 500 kHz | 0.49                                      | 0.42                     |      |

|                 |                                    |                                                                                                 | 125 kHz | 0.43                                      | 0.41                     |      |

Table 18.Typical current consumption in Sleep mode, code running from Flash or<br/>RAM

1. Typical values are measures at  $T_A$  = 25 °C,  $V_{DD}$  = 3.3 V.

2. Add an additional power consumption of 0.8 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

3. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

1. Guaranteed by design, not tested in production.

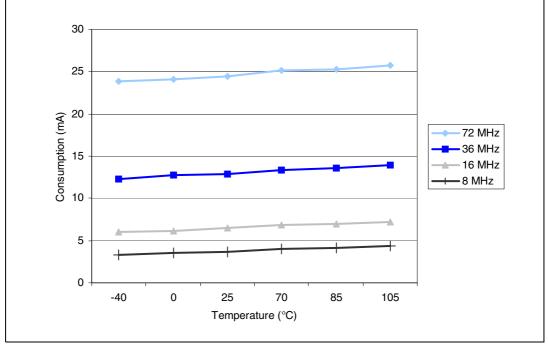

#### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 16 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 22*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

#### 5.3.15 Communications interfaces

#### I<sup>2</sup>C interface characteristics

Unless otherwise specified, the parameters given in *Table 39* are derived from tests performed under the ambient temperature,  $f_{PCLK1}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

The STM32F103xx performance line  $I^2C$  interface meets the requirements of the standard  $I^2C$  communication protocol with the following restrictions: the I/O pins SDA and SCL are mapped to are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and V<sub>DD</sub> is disabled, but is still present.

The I<sup>2</sup>C characteristics are described in *Table 39*. Refer also to *Section 5.3.12: I/O port characteristics* for more details on the input/output alternate function characteristics (SDA and SCL).

| Symbol                                     | Parameter                               | Standard mode I <sup>2</sup> C <sup>(1)</sup> |      | Fast mode I <sup>2</sup> C <sup>(1)(2)</sup> |                    | Unit |

|--------------------------------------------|-----------------------------------------|-----------------------------------------------|------|----------------------------------------------|--------------------|------|

| Symbol                                     | Falameter                               | Min                                           | Max  | Min                                          | Max                | Unit |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                      | 4.7                                           |      | 1.3                                          |                    |      |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                     | 4.0                                           |      | 0.6                                          |                    | μs   |

| t <sub>su(SDA)</sub>                       | SDA setup time                          | 250                                           |      | 100                                          |                    |      |

| t <sub>h(SDA)</sub>                        | SDA data hold time                      | 0 <sup>(3)</sup>                              |      | 0 <sup>(4)</sup>                             | 900 <sup>(3)</sup> |      |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                   |                                               | 1000 | 20 + 0.1C <sub>b</sub>                       | 300                | ns   |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                   |                                               | 300  |                                              | 300                |      |

| t <sub>h(STA)</sub>                        | Start condition hold time               | 4.0                                           |      | 0.6                                          |                    |      |

| t <sub>su(STA)</sub>                       | Repeated Start condition setup time     | 4.7                                           |      | 0.6                                          |                    | μs   |

| t <sub>su(STO)</sub>                       | Stop condition setup time               | 4.0                                           |      | 0.6                                          |                    | μS   |

| t <sub>w(STO:STA)</sub>                    | Stop to Start condition time (bus free) | 4.7                                           |      | 1.3                                          |                    | μS   |

| C <sub>b</sub>                             | Capacitive load for each bus line       |                                               | 400  |                                              | 400                | pF   |

| Table 39. I <sup>2</sup> | C characteristi | cs |

|--------------------------|-----------------|----|

|--------------------------|-----------------|----|

1. Guaranteed by design, not tested in production.

2.  $f_{PCLK1}$  must be higher than 2 MHz to achieve the maximum standard mode I<sup>2</sup>C frequency. It must be higher than 4 MHz to achieve the maximum fast mode I<sup>2</sup>C frequency.

3. The maximum hold time of the Start condition has only to be met if the interface does not stretch the low period of SCL signal.

4. The device must internally provide a hold time of at least 300ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL.

#### Equation 1: R<sub>AIN</sub> max formula:

$$R_{AIN} < \frac{I_{S}}{f_{ADC} \times C_{ADC} \times ln(2^{N+2})} - R_{ADC}$$

The formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. Here N = 12 (from 12-bit resolution).

#### Table 46. $R_{AIN}$ max for $f_{ADC} = 14 \text{ MHz}^{(1)}$

| T <sub>s</sub> (cycles) | t <sub>S</sub> (μs) | R <sub>AIN</sub> max (kΩ) |

|-------------------------|---------------------|---------------------------|

| 1.5                     | 0.11                | 1.2                       |

| 7.5                     | 0.54                | 10                        |

| 13.5                    | 0.96                | 19                        |

| 28.5                    | 2.04                | 41                        |

| 41.5                    | 2.96                | 60                        |

| 55.5                    | 3.96                | 80                        |

| 71.5                    | 5.11                | 104                       |

| 239.5                   | 17.1                | 350                       |

1. Based on characterization, not tested in production.

## Table 47. ADC accuracy - limited test conditions<sup>(1) (2)</sup>

| Symbol | Parameter                    | Test conditions                                                   | Тур  | Max <sup>(3)</sup> | Unit |

|--------|------------------------------|-------------------------------------------------------------------|------|--------------------|------|

| ET     | Total unadjusted error       | f <sub>PCLK2</sub> = 56 MHz,                                      | ±1.3 | ±2                 |      |

| EO     | Offset error                 | $f_{ADC} = 14 \text{ MHz}, \text{ R}_{AIN} < 10 \text{ k}\Omega,$ | ±1   | ±1.5               |      |

| EG     | Gain error                   | V <sub>DDA</sub> = 3 V to 3.6 V<br>T₄ = 25 °C                     |      | ±1.5               | LSB  |

| ED     | Differential linearity error | Measurements made after                                           | ±0.7 | ±1                 |      |

| EL     | Integral linearity error     | ADC calibration                                                   | ±0.8 | ±1.5               |      |

1. ADC DC accuracy values are measured after internal calibration.

ADC Accuracy vs. Negative Injection Current: Injecting negative current on any of the standard (non-robust) analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to standard analog pins which may potentially inject negative current. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in *Section 5.3.12* does not affect the ADC accuracy.

3. Based on characterization, not tested in production.

# 6 Package characteristics

# 6.1 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

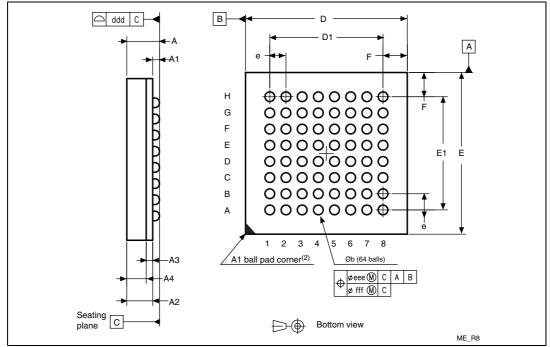

Figure 42. TFBGA64 - 8 x 8 active ball array, 5 x 5 mm, 0.5 mm pitch, package outline

1. Drawing is not to scale.

Table 54.TFBGA64 - 8 x 8 active ball array, 5 x 5 mm, 0.5 mm pitch, package<br/>mechanical data

| Quanta d | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|----------|-------------|-------|-------|-----------------------|--------|--------|--|

| Symbol   | Тур         | Min   | Max   | Тур                   | Min    | Max    |  |

| A        |             |       | 1.200 |                       |        | 0.0472 |  |

| A1       |             | 0.150 |       |                       | 0.0059 |        |  |

| A2       | 0.785       |       |       | 0.0309                |        |        |  |

| A3       | 0.200       |       |       | 0.0079                |        |        |  |

| A4       |             |       | 0.600 |                       |        | 0.0236 |  |

| b        | 0.300       | 0.250 | 0.350 | 0.0118                | 0.0098 | 0.0138 |  |

| D        | 5.000       | 4.850 | 5.150 | 0.1969                | 0.1909 | 0.2028 |  |

| D1       | 3.500       |       |       | 0.1378                |        |        |  |

| E        | 5.000       | 4.850 | 5.150 | 0.1969                | 0.1909 | 0.2028 |  |

| E1       | 3.500       |       |       | 0.1378                |        |        |  |

| е        | 0.500       |       |       | 0.0197                |        |        |  |

| F        | 0.750       |       |       | 0.0295                |        |        |  |

| ddd      |             | 0.080 |       |                       | 0.0031 |        |  |

| eee      | 0.150       |       |       | 0.0059                |        |        |  |

| fff      |             | 0.050 |       |                       | 0.0020 |        |  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

## 6.2 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 9: General operating conditions on page 35*.

The maximum chip-junction temperature,  $T_{\rm J}$  max, in degrees Celsius, may be calculated using the following equation:

$$T_J max = T_A max + (P_D max \times \Theta_{JA})$$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in °C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

$P_{I/O}$  max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I}/\mathsf{O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V<sub>OL</sub> / I<sub>OL</sub> and V<sub>OH</sub> / I<sub>OH</sub> of the I/Os at low and high level in the application.

Table 56. Package thermal characteristics

| Symbol          | Parameter                                                                         | Value | Unit |

|-----------------|-----------------------------------------------------------------------------------|-------|------|

|                 | Thermal resistance junction-ambient<br>LFBGA100 - 10 × 10 mm / 0.8 mm pitch       | 44    |      |

|                 | <b>Thermal resistance junction-ambient</b><br>LQFP100 - 14 × 14 mm / 0.5 mm pitch | 46    |      |

|                 | Thermal resistance junction-ambient<br>LQFP64 - 10 × 10 mm / 0.5 mm pitch         | 45    | °C/W |

| Θ <sub>JA</sub> | <b>Thermal resistance junction-ambient</b><br>TFBGA64 - 5 × 5 mm / 0.5 mm pitch   | 65    | C/vv |

|                 | Thermal resistance junction-ambient<br>LQFP48 - 7 x 7 mm / 0.5 mm pitch           | 55    |      |

|                 | <b>Thermal resistance junction-ambient</b><br>VFQFPN 36 - 6 × 6 mm / 0.5 mm pitch | 18    |      |

#### 6.2.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.