Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, Motor Control PWM, PDR, POR, PVD, PWM, Temp Sensor, WDT          |

| Number of I/O              | 80                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 20K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-LFBGA                                                             |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f103v8h6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### SysTick timer

This timer is dedicated for OS, but could also be used as a standard downcounter. It features:

- A 24-bit downcounter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0

- Programmable clock source

#### 2.3.16 I<sup>2</sup>C bus

Up to two I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support standard and fast modes.

They support dual slave addressing (7-bit only) and both 7/10-bit addressing in master mode. A hardware CRC generation/verification is embedded.

They can be served by DMA and they support SM Bus 2.0/PM Bus.

#### 2.3.17 Universal synchronous/asynchronous receiver transmitter (USART)

One of the USART interfaces is able to communicate at speeds of up to 4.5 Mbit/s. The other available interfaces communicate at up to 2.25 Mbit/s. They provide hardware management of the CTS and RTS signals, IrDA SIR ENDEC support, are ISO 7816 compliant and have LIN Master/Slave capability.

All USART interfaces can be served by the DMA controller.

#### 2.3.18 Serial peripheral interface (SPI)

Up to two SPIs are able to communicate up to 18 Mbits/s in slave and master modes in fullduplex and simplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

Both SPIs can be served by the DMA controller.

#### 2.3.19 Controller area network (CAN)

The CAN is compliant with specifications 2.0A and B (active) with a bit rate up to 1 Mbit/s. It can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. It has three transmit mailboxes, two receive FIFOs with 3 stages and 14 scalable filter banks.

#### 2.3.20 Universal serial bus (USB)

The STM32F103xx performance line embeds a USB device peripheral compatible with the USB full-speed 12 Mbs. The USB interface implements a full-speed (12 Mbit/s) function interface. It has software-configurable endpoint setting and suspend/resume support. The dedicated 48 MHz clock is generated from the internal main PLL (the clock source must use a HSE crystal oscillator).

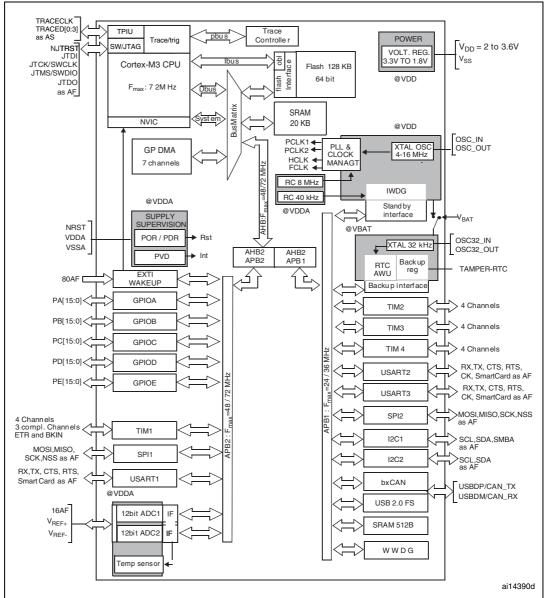

Figure 1. STM32F103xx performance line block diagram

1.  $T_A = -40$  °C to +105 °C (junction temperature up to 125 °C).

2. AF = alternate function on I/O port pin.

## Pinouts and pin description

|          |        | Pin               |        |         |          | y 51M32F103XX p                    |                     | (2)                        |                                                  | Alternate fu                                                                      | unctions |

|----------|--------|-------------------|--------|---------|----------|------------------------------------|---------------------|----------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------|----------|

| LFBGA100 | LQFP48 | TFBGA64           | LQFP64 | LQFP100 | VFQFPN36 | Pin name                           | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                                           | Remap    |

| A3       | -      |                   | -      | 1       | -        | PE2                                | I/O                 | FT                         | PE2                                              | TRACECK                                                                           |          |

| B3       | -      |                   | -      | 2       | -        | PE3                                | I/O                 | FT                         | PE3                                              | TRACED0                                                                           |          |

| C3       | -      |                   | -      | 3       | -        | PE4                                | I/O                 | FT                         | PE4                                              | TRACED1                                                                           |          |

| D3       | -      |                   | -      | 4       | -        | PE5                                | I/O                 | FT                         | PE5                                              | TRACED2                                                                           |          |

| E3       | -      |                   | -      | 5       | -        | PE6                                | I/O                 | FT                         | PE6                                              | TRACED3                                                                           |          |

| B2       | 1      | B2                | 1      | 6       | -        | V <sub>BAT</sub>                   | S                   |                            | V <sub>BAT</sub>                                 |                                                                                   |          |

| A2       | 2      | A2                | 2      | 7       | -        | PC13-TAMPER-<br>RTC <sup>(4)</sup> | I/O                 |                            | PC13 <sup>(5)</sup>                              | TAMPER-RTC                                                                        |          |

| A1       | 3      | A1                | 3      | 8       | -        | PC14-OSC32_IN <sup>(4)</sup>       | I/O                 |                            | PC14 <sup>(5)</sup>                              | OSC32_IN                                                                          |          |

| B1       | 4      | B1                | 4      | 9       | -        | PC15-<br>OSC32_OUT <sup>(4)</sup>  | I/O                 |                            | PC15 <sup>(5)</sup>                              | OSC32_OUT                                                                         |          |

| C2       | -      | -                 | -      | 10      | -        | V <sub>SS_5</sub>                  | S                   |                            | V <sub>SS_5</sub>                                |                                                                                   |          |

| D2       | -      | -                 | -      | 11      | -        | V <sub>DD_5</sub>                  | S                   |                            | $V_{DD_5}$                                       |                                                                                   |          |

| C1       | 5      | C1                | 5      | 12      | 2        | OSC_IN                             | I                   |                            | OSC_IN                                           |                                                                                   |          |

| D1       | 6      | D1                | 6      | 13      | 3        | OSC_OUT                            | 0                   |                            | OSC_OUT                                          |                                                                                   |          |

| E1       | 7      | E1                | 7      | 14      | 4        | NRST                               | I/O                 |                            | NRST                                             |                                                                                   |          |

| F1       | -      | E3                | 8      | 15      | -        | PC0                                | I/O                 |                            | PC0                                              | ADC12_IN10                                                                        |          |

| F2       | -      | E2                | 9      | 16      | -        | PC1                                | I/O                 |                            | PC1                                              | ADC12_IN11                                                                        |          |

| E2       | -      | F2                | 10     | 17      | -        | PC2                                | I/O                 |                            | PC2                                              | ADC12_IN12                                                                        |          |

| F3       | -      | _(6)              | 11     | 18      | -        | PC3                                | I/O                 |                            | PC3                                              | ADC12_IN13                                                                        |          |

| G1       | 8      | F1                | 12     | 19      | 5        | V <sub>SSA</sub>                   | S                   |                            | V <sub>SSA</sub>                                 |                                                                                   |          |

| H1       | -      | -                 | I      | 20      | -        | V <sub>REF-</sub>                  | S                   |                            | V <sub>REF-</sub>                                |                                                                                   |          |

| J1       | -      | G1 <sup>(6)</sup> | I      | 21      | -        | V <sub>REF+</sub>                  | S                   |                            | $V_{REF+}$                                       |                                                                                   |          |

| K1       | 9      | H1                | 13     | 22      | 6        | V <sub>DDA</sub>                   | S                   |                            | $V_{DDA}$                                        |                                                                                   |          |

| G2       | 10     | G2                | 14     | 23      | 7        | PA0-WKUP                           | I/O                 |                            | PA0                                              | WKUP/<br>USART2_CTS <sup>(7)</sup> /<br>ADC12_IN0/<br>TIM2_CH1_ETR <sup>(7)</sup> |          |

| H2       | 11     | H2                | 15     | 24      | 8        | PA1                                | I/O                 |                            | PA1                                              | USART2_RTS <sup>(7)</sup> /<br>ADC12_IN1/<br>TIM2_CH2 <sup>(7)</sup>              |          |

| J2       | 12     | F3                | 16     | 25      | 9        | PA2                                | I/O                 |                            | PA2                                              | USART2_TX <sup>(7)</sup> /<br>ADC12_IN2/<br>TIM2_CH3 <sup>(7)</sup>               |          |

#### Table 5. Medium-density STM32F103xx pin definitions

|          |        | Pin     | IS     |         |          |                   |                     | (2)                        |                                                  | Alternate f                                                          | unctions  |

|----------|--------|---------|--------|---------|----------|-------------------|---------------------|----------------------------|--------------------------------------------------|----------------------------------------------------------------------|-----------|

| LFBGA100 | LQFP48 | TFBGA64 | LQFP64 | LQFP100 | VFQFPN36 | Pin name          | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                              | Remap     |

| K2       | 13     | G3      | 17     | 26      | 10       | PA3               | I/O                 |                            | PA3                                              | USART2_RX <sup>(7)</sup> /<br>ADC12_IN3/<br>TIM2_CH4 <sup>(7)</sup>  |           |

| E4       | -      | C2      | 18     | 27      | -        | V <sub>SS_4</sub> | S                   |                            | $V_{SS_4}$                                       |                                                                      |           |

| F4       | -      | D2      | 19     | 28      | -        | V <sub>DD_4</sub> | S                   |                            | V <sub>DD_4</sub>                                |                                                                      |           |

| G3       | 14     | НЗ      | 20     | 29      | 11       | PA4               | I/O                 |                            | PA4                                              | SPI1_NSS <sup>(7)</sup> /<br>USART2_CK <sup>(7)</sup> /<br>ADC12_IN4 |           |

| НЗ       | 15     | F4      | 21     | 30      | 12       | PA5               | I/O                 |                            | PA5                                              | SPI1_SCK <sup>(7)</sup> /<br>ADC12_IN5                               |           |

| JЗ       | 16     | G4      | 22     | 31      | 13       | PA6               | I/O                 |                            | PA6                                              | SPI1_MISO <sup>(7)</sup> /<br>ADC12_IN6/<br>TIM3_CH1 <sup>(7)</sup>  | TIM1_BKIN |

| КЗ       | 17     | H4      | 23     | 32      | 14       | PA7               | I/O                 |                            | PA7                                              | SPI1_MOSI <sup>(7)</sup> /<br>ADC12_IN7/<br>TIM3_CH2 <sup>(7)</sup>  | TIM1_CH1N |

| G4       | -      | H5      | 24     | 33      |          | PC4               | I/O                 |                            | PC4                                              | ADC12_IN14                                                           |           |

| H4       | -      | H6      | 25     | 34      |          | PC5               | I/O                 |                            | PC5                                              | ADC12_IN15                                                           |           |

| J4       | 18     | F5      | 26     | 35      | 15       | PB0               | I/O                 |                            | PB0                                              | ADC12_IN8/<br>TIM3_CH3 <sup>(7)</sup>                                | TIM1_CH2N |

| K4       | 19     | G5      | 27     | 36      | 16       | PB1               | I/O                 |                            | PB1                                              | ADC12_IN9/<br>TIM3_CH4 <sup>(7)</sup>                                | TIM1_CH3N |

| G5       | 20     | G6      | 28     | 37      | 17       | PB2               | I/O                 | FT                         | PB2/BOOT1                                        |                                                                      |           |

| H5       | -      | -       | -      | 38      | -        | PE7               | I/O                 | FT                         | PE7                                              |                                                                      | TIM1_ETR  |

| J5       | -      | -       | -      | 39      | -        | PE8               | I/O                 | FT                         | PE8                                              |                                                                      | TIM1_CH1N |

| K5       | -      | -       | -      | 40      | -        | PE9               | I/O                 | FT                         | PE9                                              |                                                                      | TIM1_CH1  |

| G6       | -      | -       | -      | 41      | -        | PE10              | I/O                 | FT                         | PE10                                             |                                                                      | TIM1_CH2N |

| H6       | -      | -       | -      | 42      | -        | PE11              | I/O                 | FT                         | PE11                                             |                                                                      | TIM1_CH2  |

| J6       | -      | -       | -      | 43      | -        | PE12              | I/O                 | FT                         | PE12                                             |                                                                      | TIM1_CH3N |

| K6       | -      | -       | -      | 44      | -        | PE13              | I/O                 | FT                         | PE13                                             |                                                                      | TIM1_CH3  |

| G7       | -      | •       | -      | 45      | -        | PE14              | I/O                 | FT                         | PE14                                             |                                                                      | TIM1_CH4  |

| H7       | -      | -       | -      | 46      | -        | PE15              | I/O                 | FT                         | PE15                                             |                                                                      | TIM1_BKIN |

| J7       | 21     | G7      | 29     | 47      | -        | PB10              | I/O                 | FT                         | PB10                                             | I2C2_SCL/<br>USART3_TX <sup>(7)</sup>                                | TIM2_CH3  |

| K7       | 22     | H7      | 30     | 48      | -        | PB11              | I/O                 | FT                         | PB11                                             | I2C2_SDA/<br>USART3_RX <sup>(7)</sup>                                | TIM2_CH4  |

| E7       | 23     | D6      | 31     | 49      | 18       | V <sub>SS_1</sub> | S                   |                            | $V_{SS_1}$                                       |                                                                      |           |

| Table 5. | Medium-density | y STM32F103xx | pin definitions | (continued) |  |

|----------|----------------|---------------|-----------------|-------------|--|

|----------|----------------|---------------|-----------------|-------------|--|

# 5 Electrical characteristics

## 5.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to  $V_{SS}$ .

#### 5.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

## 5.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A$  = 25 °C,  $V_{DD}$  = 3.3 V (for the 2 V  $\leq$   $V_{DD}$   $\leq$  3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\Sigma$ ).

#### 5.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

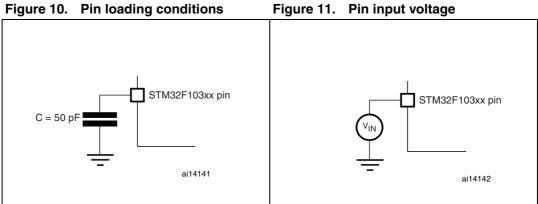

## 5.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 10*.

#### 5.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 11*.

#### Figure 10. Pin loading conditions

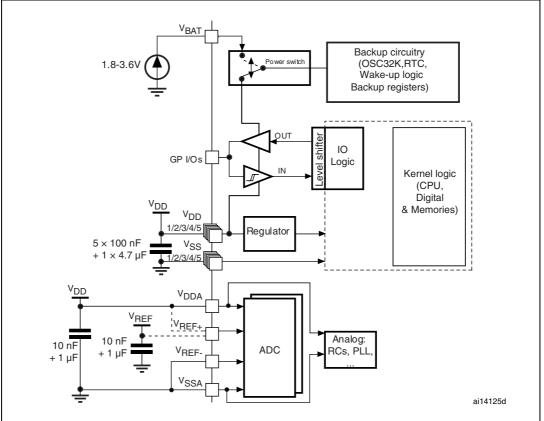

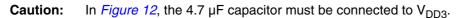

#### Power supply scheme 5.1.6

#### 5.1.7 Current consumption measurement

#### Figure 13. Current consumption measurement scheme

## 5.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 6: Voltage characteristics*, *Table 7: Current characteristics*, and *Table 8: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                           | Ratings                                                               | Min                                                                         | Мах                  | Unit |  |

|----------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------|------|--|

| V <sub>DD</sub> -V <sub>SS</sub> | External main supply voltage (including $V_{DDA}$ and $V_{DD})^{(1)}$ | -0.3                                                                        | 4.0                  |      |  |

| V <sub>IN</sub>                  | Input voltage on five volt tolerant pin <sup>(2)</sup>                | $V_{SS} - 0.3$                                                              | +5.5                 | V    |  |

|                                  | Input voltage on any other pin <sup>(2)</sup>                         | $V_{SS}-0.3$                                                                | V <sub>DD</sub> +0.3 |      |  |

| $ \Delta V_{DDx} $               | Variations between different V <sub>DD</sub> power pins               |                                                                             | 50                   | mV   |  |

| $ V_{SSX} - V_{SS} $             | Variations between all the different ground pins                      |                                                                             | 50                   | IIIV |  |

| V <sub>ESD(HBM)</sub>            | Electrostatic discharge voltage (human body model)                    | see Section 5.3.11:<br>Absolute maximum ratings<br>(electrical sensitivity) |                      |      |  |

Table 6.

Voltage characteristics

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2.  $I_{INJ(PIN)}$  must never be exceeded (see *Table 7: Current characteristics*). This is implicitly insured if  $V_{IN}$  maximum is respected. If  $V_{IN}$  maximum cannot be respected, the injection current must be limited externally to the  $I_{INJ(PIN)}$  value. A positive injection is induced by  $V_{IN}$  >  $V_{IN}$  max while a negative injection is induced by  $V_{IN}$  <  $V_{SS}$ .

## 5.3.6 External clock source characteristics

## High-speed external user clock generated from an external source

The characteristics given in *Table 20* result from tests performed using an high-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 9*.

|                                            | nigh speed external user block bhardblenstibis      |                                                                            |             |     |                    |      |

|--------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------|-------------|-----|--------------------|------|

| Symbol                                     | Parameter                                           | Conditions                                                                 | Min         | Тур | Max                | Unit |

| f <sub>HSE_ext</sub>                       | User external clock source frequency <sup>(1)</sup> |                                                                            | 0           | 8   | 25                 | MHz  |

| V <sub>HSEH</sub>                          | OSC_IN input pin high level voltage                 |                                                                            | $0.7V_{DD}$ |     | V <sub>DD</sub>    | v    |

| V <sub>HSEL</sub>                          | OSC_IN input pin low level voltage                  |                                                                            | $V_{SS}$    |     | $0.3V_{\text{DD}}$ | v    |

| t <sub>w(HSE)</sub><br>t <sub>w(HSE)</sub> | OSC_IN high or low time <sup>(1)</sup>              |                                                                            | 16          |     |                    | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub> | OSC_IN rise or fall time <sup>(1)</sup>             |                                                                            |             |     | 20                 | 115  |

| C <sub>in(HSE)</sub>                       | OSC_IN input capacitance <sup>(1)</sup>             |                                                                            |             | 5   |                    | pF   |

| DuCy <sub>(HSE)</sub>                      | Duty cycle                                          |                                                                            | 45          |     | 55                 | %    |

| ΙL                                         | OSC_IN Input leakage current                        | $\begin{array}{c} V_{SS} \leq V_{IN} \leq V_{D} \\ & \text{D} \end{array}$ |             |     | ±1                 | μA   |

Table 20.

High-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

#### Low-speed external user clock generated from an external source

The characteristics given in *Table 21* result from tests performed using an low-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 9*.

| Table 21. | Low-speed external user clock characteristics |

|-----------|-----------------------------------------------|

|-----------|-----------------------------------------------|

| Symbol                                     | Parameter                                              | Conditions                  | Min                | Тур    | Мах                | Unit |

|--------------------------------------------|--------------------------------------------------------|-----------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                       | User External clock source<br>frequency <sup>(1)</sup> |                             |                    | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage                  |                             | 0.7V <sub>DD</sub> |        | V <sub>DD</sub>    | V    |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage                   |                             | V <sub>SS</sub>    |        | 0.3V <sub>DD</sub> | v    |

| t <sub>w(LSE)</sub><br>t <sub>w(LSE)</sub> | OSC32_IN high or low time <sup>(1)</sup>               |                             | 450                |        |                    |      |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time <sup>(1)</sup>              |                             |                    |        | 50                 | ns   |

| C <sub>in(LSE)</sub>                       | OSC32_IN input capacitance <sup>(1)</sup>              |                             |                    | 5      |                    | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                                             |                             | 30                 |        | 70                 | %    |

| ١L                                         | OSC32_IN Input leakage<br>current                      | $V_{SS} \le V_{IN} \le V_D$ |                    |        | ±1                 | μA   |

|                                     | Lon ponor mode nanoup                                                      | lininge                                                                            |     |      |

|-------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----|------|

| Symbol                              | Parameter                                                                  | Conditions                                                                         | Тур | Unit |

| t <sub>WUSLEEP</sub> <sup>(1)</sup> | Wakeup from Sleep mode                                                     | Wakeup on HSI RC clock                                                             | 1.8 | μs   |

| . (1)                               | Wakeup from Stop mode<br>(regulator in run mode) HSI RC wakeup time = 2 µs |                                                                                    | 3.6 | 110  |

| t <sub>WUSTOP</sub> <sup>(1)</sup>  | Wakeup from Stop mode<br>(regulator in low power mode)                     | HSI RC wakeup time = 2 $\mu$ s, Regulator<br>wakeup from LP mode time = 5 $\mu$ s  | 5.4 | μs   |

| t <sub>WUSTDBY</sub> <sup>(1)</sup> | Wakeup from Standby mode                                                   | HSI RC wakeup time = 2 $\mu$ s, Regulator wakeup from power down time = 38 $\mu$ s | 50  | μs   |

Table 26. Low-power mode wakeup timings

1. The wakeup times are measured from the wakeup event to the point in which the user application code reads the first instruction.

#### 5.3.8 PLL characteristics

The parameters given in *Table 27* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

| Symbol               | Parameter                      | Test conditions |                    | Unit |                    |      |

|----------------------|--------------------------------|-----------------|--------------------|------|--------------------|------|

| Symbol               | Parameter                      | Test conditions | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

| 4                    | PLL input clock <sup>(2)</sup> |                 | 1                  | 8.0  | 25                 | MHz  |

| f <sub>PLL_IN</sub>  | PLL input clock duty cycle     |                 | 40                 |      | 60                 | %    |

| f <sub>PLL_OUT</sub> | PLL multiplier output clock    |                 | 16                 |      | 72                 | MHz  |

| t <sub>LOCK</sub>    | PLL lock time                  |                 |                    |      | 200                | μs   |

Table 27. PLL characteristics

1. Based on characterization, not tested in production.

2. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{\mathsf{PLL}\_\mathsf{OUT}}$ .

#### 5.3.9 Memory characteristics

#### **Flash memory**

The characteristics are given at  $T_A = -40$  to 105 °C unless otherwise specified.

| Symbol             | Parameter               | Conditions                      | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

|--------------------|-------------------------|---------------------------------|--------------------|------|--------------------|------|

| t <sub>prog</sub>  | 16-bit programming time | $T_A = -40$ to +105 °C          | 40                 | 52.5 | 70                 | μs   |

| t <sub>ERASE</sub> | Page (1 KB) erase time  | T <sub>A</sub> = -40 to +105 °C | 20                 |      | 40                 | ms   |

| t <sub>ME</sub>    | Mass erase time         | T <sub>A</sub> = -40 to +105 °C | 20                 |      | 40                 | ms   |

Table 28.

Flash memory characteristics

#### 5.3.11 Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

Table 32. ESD absolute maximum ratings

| Symbol                | Ratings                                               | Conditions                                              | Class | Maximum value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|---------------------------------------------------------|-------|------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | $T_A = +25 \ ^{\circ}C$<br>conforming to<br>JESD22-A114 | 2     | 2000                         | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | $T_A = +25 \text{ °C}$<br>conforming to<br>JESD22-C101  | 11    | 500                          | v    |

1. Based on characterization results, not tested in production.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

#### Table 33.Electrical sensitivities

| Symbol | Parameter             | Conditions                            | Class      |

|--------|-----------------------|---------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +105$ °C conforming to JESD78A | II level A |

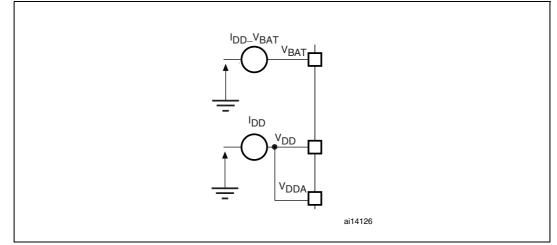

Figure 25. I<sup>2</sup>C bus AC waveforms and measurement circuit

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

# Table 40. SCL frequency $(f_{PCLK1} = 36 \text{ MHz.}, V_{DD} = 3.3 \text{ V})^{(1)(2)}$

| f ((tH=)               | I2C_CCR value                  |

|------------------------|--------------------------------|

| f <sub>SCL</sub> (kHz) | <b>R<sub>P</sub> = 4.7 k</b> Ω |

| 400                    | 0x801E                         |

| 300                    | 0x8028                         |

| 200                    | 0x803C                         |

| 100                    | 0x00B4                         |

| 50                     | 0x0168                         |

| 20                     | 0x0384                         |

1.  $R_P$  = External pull-up resistance,  $f_{SCL} = I^2C$  speed,

For speeds around 200 kHz, the tolerance on the achieved speed is of ±5%. For other speed ranges, the tolerance on the achieved speed ±2%. These variations depend on the accuracy of the external components used to design the application.

#### Equation 1: R<sub>AIN</sub> max formula:

$$R_{AIN} < \frac{I_{S}}{f_{ADC} \times C_{ADC} \times ln(2^{N+2})} - R_{ADC}$$

The formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. Here N = 12 (from 12-bit resolution).

#### Table 46. $R_{AIN}$ max for $f_{ADC} = 14 \text{ MHz}^{(1)}$

| T <sub>s</sub> (cycles) | t <sub>S</sub> (μs) | R <sub>AIN</sub> max (kΩ) |

|-------------------------|---------------------|---------------------------|

| 1.5                     | 0.11                | 1.2                       |

| 7.5                     | 0.54                | 10                        |

| 13.5                    | 0.96                | 19                        |

| 28.5                    | 2.04                | 41                        |

| 41.5                    | 2.96                | 60                        |

| 55.5                    | 3.96                | 80                        |

| 71.5                    | 5.11                | 104                       |

| 239.5                   | 17.1                | 350                       |

1. Based on characterization, not tested in production.

## Table 47. ADC accuracy - limited test conditions<sup>(1) (2)</sup>

| Symbol | Parameter                    | Test conditions                                                   | Тур  | Max <sup>(3)</sup> | Unit |

|--------|------------------------------|-------------------------------------------------------------------|------|--------------------|------|

| ET     | Total unadjusted error       | f <sub>PCLK2</sub> = 56 MHz,                                      | ±1.3 | ±2                 |      |

| EO     | Offset error                 | $f_{ADC} = 14 \text{ MHz}, \text{ R}_{AIN} < 10 \text{ k}\Omega,$ | ±1   | ±1.5               |      |

| EG     | Gain error                   | V <sub>DDA</sub> = 3 V to 3.6 V<br>T₄ = 25 °C                     | ±0.5 | ±1.5               | LSB  |

| ED     | Differential linearity error | Measurements made after                                           | ±0.7 | ±1                 |      |

| EL     | Integral linearity error     | ADC calibration                                                   | ±0.8 | ±1.5               |      |

1. ADC DC accuracy values are measured after internal calibration.

ADC Accuracy vs. Negative Injection Current: Injecting negative current on any of the standard (non-robust) analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to standard analog pins which may potentially inject negative current. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in *Section 5.3.12* does not affect the ADC accuracy.

3. Based on characterization, not tested in production.

# 6 Package characteristics

# 6.1 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

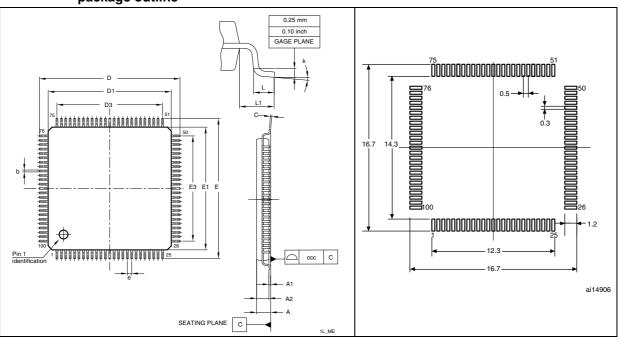

# Figure 38. LQFP100, 100-pin low-profile quad flat package outline<sup>(1)</sup>

1. Drawing is not to scale.

2. Dimensions are in millimeters.

#### Table 52. LQPF100, 100-pin low-profile quad flat package mechanical data

| O h l    | millimeters |      |      | inches <sup>(1)</sup> |        |        |  |

|----------|-------------|------|------|-----------------------|--------|--------|--|

| Symbol - | Тур         | Min  | Мах  | Тур                   | Min    | Мах    |  |

| А        |             |      | 1.6  |                       |        | 0.063  |  |

| A1       |             | 0.05 | 0.15 |                       | 0.002  | 0.0059 |  |

| A2       | 1.4         | 1.35 | 1.45 | 0.0551                | 0.0531 | 0.0571 |  |

| b        | 0.22        | 0.17 | 0.27 | 0.0087                | 0.0067 | 0.0106 |  |

| С        |             | 0.09 | 0.2  |                       | 0.0035 | 0.0079 |  |

| D        | 16          | 15.8 | 16.2 | 0.6299                | 0.622  | 0.6378 |  |

| D1       | 14          | 13.8 | 14.2 | 0.5512                | 0.5433 | 0.5591 |  |

| D3       | 12          |      |      | 0.4724                |        |        |  |

| Е        | 16          | 15.8 | 16.2 | 0.6299                | 0.622  | 0.6378 |  |

| E1       | 14          | 13.8 | 14.2 | 0.5512                | 0.5433 | 0.5591 |  |

| E3       | 12          |      |      | 0.4724                |        |        |  |

| е        | 0.5         |      |      | 0.0197                |        |        |  |

| L        | 0.6         | 0.45 | 0.75 | 0.0236                | 0.0177 | 0.0295 |  |

| L1       | 1           |      |      | 0.0394                |        |        |  |

| k        | 3.5°        | 0.0° | 7.0° | 3.5°                  | 0.0°   | 7.0°   |  |

| CCC      |             | 0.08 |      |                       | 0.0031 | •      |  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

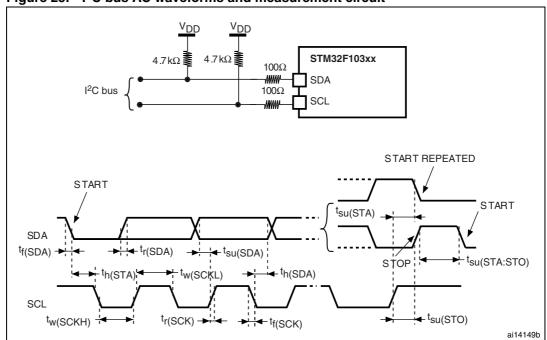

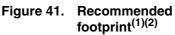

# Figure 39. Recommended footprint $^{(1)(2)}$

# Figure 40. LQFP64, 64-pin low-profile quad flat package Figure 40. Containe<sup>(1)</sup>

1. Drawing is not to scale.

2. Dimensions are in millimeters.

| Table 53. | LQFP64, 64-pin low-p | rofile quad flat package mechanical data |

|-----------|----------------------|------------------------------------------|

|           |                      |                                          |

| Dim  | mm             |       |            | inches <sup>(1)</sup> |        |        |

|------|----------------|-------|------------|-----------------------|--------|--------|

| Dim. | Min            | Тур   | Max        | Min                   | Тур    | Max    |

| А    |                |       | 1.60       |                       |        | 0.0630 |

| A1   | 0.05           |       | 0.15       | 0.0020                |        | 0.0059 |

| A2   | 1.35           | 1.40  | 1.45       | 0.0531                | 0.0551 | 0.0571 |

| b    | 0.17           | 0.22  | 0.27       | 0.0067                | 0.0087 | 0.0106 |

| С    | 0.09           |       | 0.20       | 0.0035                |        | 0.0079 |

| D    |                | 12.00 |            |                       | 0.4724 |        |

| D1   |                | 10.00 |            |                       | 0.3937 |        |

| Е    |                | 12.00 |            |                       | 0.4724 |        |

| E1   |                | 10.00 |            |                       | 0.3937 |        |

| е    |                | 0.50  |            |                       | 0.0197 |        |

| θ    | 0°             | 3.5°  | <b>7</b> ° | 0°                    | 3.5°   | 7°     |

| L    | 0.45           | 0.60  | 0.75       | 0.0177                | 0.0236 | 0.0295 |

| L1   |                | 1.00  |            |                       | 0.0394 |        |

| N    | Number of pins |       |            |                       |        |        |

| IN   |                |       | (          | 64                    |        |        |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

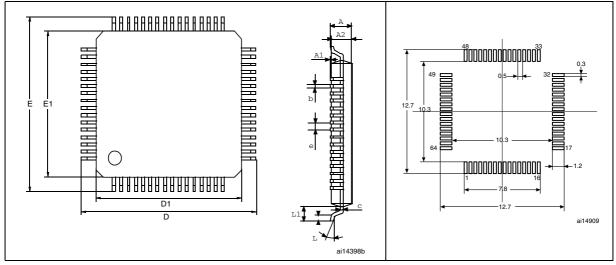

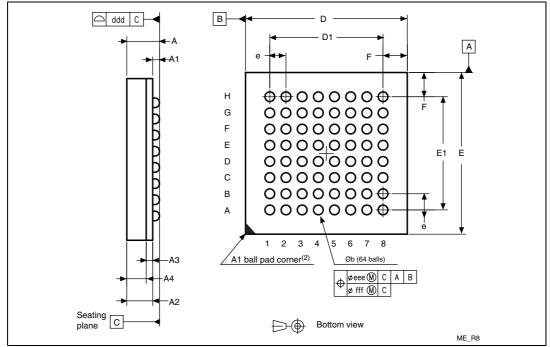

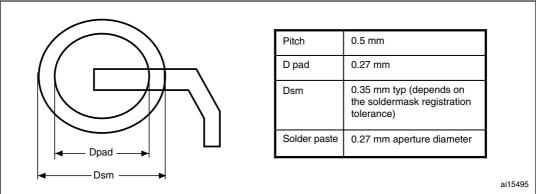

Figure 42. TFBGA64 - 8 x 8 active ball array, 5 x 5 mm, 0.5 mm pitch, package outline

1. Drawing is not to scale.

Table 54.TFBGA64 - 8 x 8 active ball array, 5 x 5 mm, 0.5 mm pitch, package<br/>mechanical data

| Gumbal | millimeters |       |        | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|-------|--------|-----------------------|--------|--------|--|

| Symbol | Тур         | Min   | Max    | Тур                   | Min    | Max    |  |

| A      |             |       | 1.200  |                       |        | 0.0472 |  |

| A1     |             | 0.150 |        |                       | 0.0059 |        |  |

| A2     | 0.785       |       |        | 0.0309                |        |        |  |

| A3     | 0.200       |       |        | 0.0079                |        |        |  |

| A4     |             |       | 0.600  |                       |        | 0.0236 |  |

| b      | 0.300       | 0.250 | 0.350  | 0.0118                | 0.0098 | 0.0138 |  |

| D      | 5.000       | 4.850 | 5.150  | 0.1969                | 0.1909 | 0.2028 |  |

| D1     | 3.500       |       |        | 0.1378                |        |        |  |

| E      | 5.000       | 4.850 | 5.150  | 0.1969                | 0.1909 | 0.2028 |  |

| E1     | 3.500       |       |        | 0.1378                |        |        |  |

| е      | 0.500       |       |        | 0.0197                |        |        |  |

| F      | 0.750       |       |        | 0.0295                |        |        |  |

| ddd    |             | 0.080 |        |                       | 0.0031 |        |  |

| eee    | 0.150       |       | 0.0059 |                       |        |        |  |

| fff    |             | 0.050 |        |                       | 0.0020 |        |  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Non solder mask defined (NSMD) pads are recommended

2. 4 to 6 mils solder paste screen printing process

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |          | I/O information clarified <i>on page 1</i> .<br><i>Figure 3: STM32F103xx performance line LFBGA100 ballout</i> modified.<br><i>Figure 9: Memory map</i> modified. <i>Table 4: Timer feature comparison</i><br>added.<br>PB4, PB13, PB14, PB15, PB3/TRACESWO moved from Default<br>column to Remap column in <i>Table 5: Medium-density STM32F103xx</i><br><i>pin definitions</i> . |

| 23-Apr-2009 | 10       | P <sub>D</sub> for LFBGA100 corrected in <i>Table 9: General operating conditions</i> .<br>Note modified in <i>Table 13: Maximum current consumption in Run</i><br><i>mode, code with data processing running from Flash</i> and <i>Table 15:</i><br><i>Maximum current consumption in Sleep mode, code running from</i><br><i>Flash or RAM</i> .                                  |

|             |          | Table 20: High-speed external user clock characteristics and Table 21:Low-speed external user clock characteristics modified.                                                                                                                                                                                                                                                      |

|             |          | <i>Figure 17</i> shows a typical curve (title modified). ACC <sub>HSI</sub> max values modified in <i>Table 24: HSI oscillator characteristics</i> .                                                                                                                                                                                                                               |

|             |          | TFBGA64 package added (see <i>Table 54</i> and <i>Table 42</i> ). Small text changes.                                                                                                                                                                                                                                                                                              |

## Table 58. Document revision history (continued)

#### **Please Read Carefully:**

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2009 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

Doc ID 13587 Rev 10