Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, Motor Control PWM, PDR, POR, PVD, PWM, Temp Sensor, WDT          |

| Number of I/O              | 80                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 20K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-LFBGA                                                             |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f103vbh6 |

# List of tables

| Table 1.  | Device summary                                                            | . 1 |

|-----------|---------------------------------------------------------------------------|-----|

| Table 2.  | STM32F103xx medium-density device features and peripheral counts          |     |

| Table 3.  | STM32F103xx family                                                        |     |

| Table 4.  | Timer feature comparison                                                  |     |

| Table 5.  | Medium-density STM32F103xx pin definitions                                |     |

| Table 6.  | Voltage characteristics                                                   |     |

| Table 7.  | Current characteristics                                                   |     |

| Table 8.  | Thermal characteristics                                                   |     |

| Table 9.  | General operating conditions                                              |     |

| Table 10. | Operating conditions at power-up / power-down                             |     |

| Table 11. | Embedded reset and power control block characteristics                    |     |

| Table 12. | Embedded internal reference voltage                                       |     |

| Table 12. | Maximum current consumption in Run mode, code with data processing        | 50  |

| Table 15. | running from Flash                                                        | 39  |

| Table 14. | Maximum current consumption in Run mode, code with data processing        | 00  |

| 145.5     | running from RAM                                                          | 39  |

| Table 15. | Maximum current consumption in Sleep mode, code running from Flash or RAM |     |

| Table 16. | Typical and maximum current consumptions in Stop and Standby modes        |     |

| Table 17. | Typical current consumption in Run mode, code with data processing        |     |

|           | running from Flash                                                        | 44  |

| Table 18. | Typical current consumption in Sleep mode, code running from Flash or     |     |

|           | RAM                                                                       |     |

| Table 19. | Peripheral current consumption                                            |     |

| Table 20. | High-speed external user clock characteristics                            |     |

| Table 21. | Low-speed external user clock characteristics                             |     |

| Table 22. | HSE 4-16 MHz oscillator characteristics                                   |     |

| Table 23. | LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz)            |     |

| Table 24. | HSI oscillator characteristics                                            |     |

| Table 25. | LSI oscillator characteristics                                            |     |

| Table 26. | Low-power mode wakeup timings                                             |     |

| Table 27. | PLL characteristics                                                       |     |

| Table 28. | Flash memory characteristics                                              |     |

| Table 29. | Flash memory endurance and data retention                                 | 53  |

| Table 30. | EMS characteristics                                                       | 54  |

| Table 31. | EMI characteristics                                                       | 54  |

| Table 32. | ESD absolute maximum ratings                                              | 55  |

| Table 33. | Electrical sensitivities                                                  |     |

| Table 34. | I/O static characteristics                                                |     |

| Table 35. | Output voltage characteristics                                            | 57  |

| Table 36. | I/O AC characteristics                                                    | 58  |

| Table 37. | NRST pin characteristics                                                  | 59  |

| Table 38. | TIMx characteristics                                                      |     |

| Table 39. | I <sup>2</sup> C characteristics                                          | 61  |

| Table 40. | SCL frequency (f <sub>PCLK1</sub> = 36 MHz.,V <sub>DD</sub> = 3.3 V)      |     |

| Table 41. | SPI characteristics                                                       |     |

| Table 42. | USB startup time                                                          | 65  |

| Table 43. | USB DC electrical characteristics                                         | 66  |

| Table 44. | USB: Full-speed electrical characteristics                                | 66  |

## STM32F103x8, STM32F103xB

## List of tables

| Table 45. | ADC characteristics                                                                | . 67 |

|-----------|------------------------------------------------------------------------------------|------|

| Table 46. | $R_{AIN}$ max for $f_{ADC} = 14$ MHz                                               | . 68 |

| Table 47. | ADC accuracy - limited test conditions                                             |      |

| Table 48. | ADC accuracy                                                                       | . 69 |

| Table 49. | TS characteristics                                                                 | . 71 |

| Table 50. | VFQFPN36 6 x 6 mm, 0.5 mm pitch, package mechanical data                           | . 73 |

| Table 51. | LFBGA100 - low profile fine pitch ball grid array package mechanical data          | . 74 |

| Table 52. | LQPF100, 100-pin low-profile quad flat package mechanical data                     | . 76 |

| Table 53. | LQFP64, 64-pin low-profile quad flat package mechanical data                       | . 77 |

| Table 54. | TFBGA64 - 8 x 8 active ball array, 5 x 5 mm, 0.5 mm pitch, package mechanical data | . 78 |

| Table 55. | LQFP48, 48-pin low-profile quad flat package mechanical data                       | . 80 |

| Table 56. | Package thermal characteristics                                                    | . 81 |

| Table 57  | Ordering information scheme                                                        | 84   |

#### 2.3.13 DMA

The flexible 7-channel general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The DMA controller supports circular buffer management avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with support for software trigger on each channel. Configuration is made by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: SPI, I<sup>2</sup>C, USART, general-purpose and advanced-control timers TIMx and ADC.

### 2.3.14 RTC (real-time clock) and backup registers

The RTC and the backup registers are supplied through a switch that takes power either on  $V_{DD}$  supply when present or through the  $V_{BAT}$  pin. The backup registers are ten 16-bit registers used to store 20 bytes of user application data when  $V_{DD}$  power is not present.

The real-time clock provides a set of continuously running counters which can be used with suitable software to provide a clock calendar function, and provides an alarm interrupt and a periodic interrupt. It is clocked by a 32.768 kHz external crystal, resonator or oscillator, the internal low-power RC oscillator or the high-speed external clock divided by 128. The internal low-power RC has a typical frequency of 40 kHz. The RTC can be calibrated using an external 512 Hz output to compensate for any natural crystal deviation. The RTC features a 32-bit programmable counter for long-term measurement using the Compare register to generate an alarm. A 20-bit prescaler is used for the time base clock and is by default configured to generate a time base of 1 second from a clock at 32.768 kHz.

# 2.3.15 Timers and watchdogs

The medium-density STM32F103xx performance line devices include an advanced-control timer, three general-purpose timers, two watchdog timers and a SysTick timer.

*Table 4* compares the features of the advanced-control and general-purpose timers.

Table 4. Timer feature comparison

| Timer                  | Counter resolution | Counter<br>type         | Prescaler factor                      | DMA request generation | Capture/compare channels | Complementary outputs |

|------------------------|--------------------|-------------------------|---------------------------------------|------------------------|--------------------------|-----------------------|

| TIM1                   | 16-bit             | Up,<br>down,<br>up/down | Any integer<br>between 1<br>and 65536 | Yes                    | 4                        | Yes                   |

| TIM2,<br>TIM3,<br>TIM4 | 16-bit             | Up,<br>down,<br>up/down | Any integer<br>between 1<br>and 65536 | Yes                    | 4                        | No                    |

#### Advanced-control timer (TIM1)

The advanced-control timer (TIM1) can be seen as a three-phase PWM multiplexed on 6 channels. It has complementary PWM outputs with programmable inserted dead-times. It

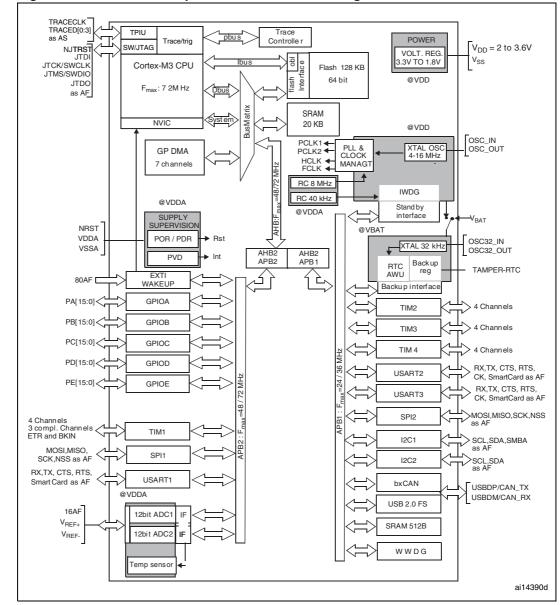

Figure 1. STM32F103xx performance line block diagram

- 1.  $T_A = -40$  °C to +105 °C (junction temperature up to 125 °C).

- 2. AF = alternate function on I/O port pin.

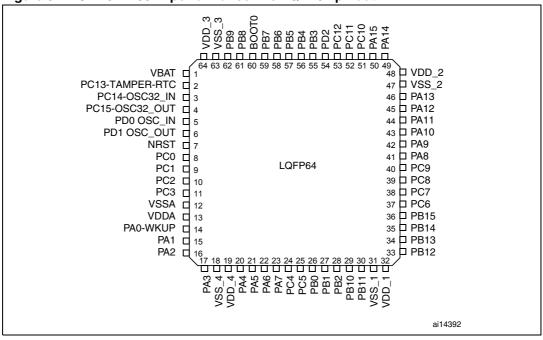

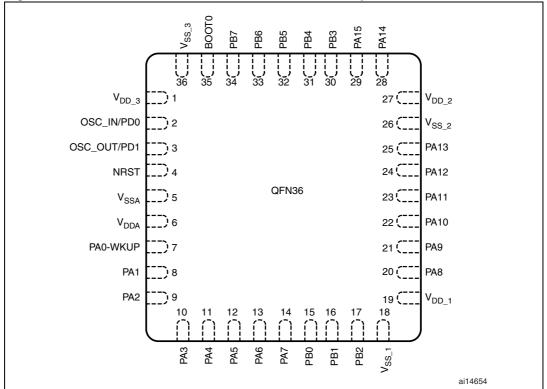

Figure 5. STM32F103xx performance line LQFP64 pinout

57

VDD\_3 VSS\_3 PB9 PB8 BOOT0 PB7 PB6 PB5 PB4 PB3 PA15 ′36 🗖 VDD\_2 VBAT 🗆 35 VSS\_2 PC13-TAMPER-RTC 2 34 PA13 PC14-OSC32\_IN 🖂 33 PA12 PC15-OSC32\_OUT d 32 PA11 PD0-OSC\_IN 🗖 5 31 PA10 PD1-OSC\_OUT d6 LQFP48 NRST [7 VSSA [8 VDDA [9 PA0-WKUP [10] 30 PA9 29 PA8 28 PB15 27 PB14 26 PB13 25 PB12 PA1 🗖 11 PA2 12 PA3 C PA4 C PA5 C PA6 C PA7 C PB1 PB1 PB2 PB10 PB10 PB11 VSS\_1 VSS\_1 VSS\_1 VSS\_1 VSS\_1 VSS\_1 PD1 PB11 VSS\_1 ai14393b

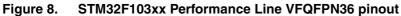

Figure 7. STM32F103xx performance line LQFP48 pinout

Figure 10. Pin loading conditions

Figure 11. Pin input voltage

STM32F103xx pin

C = 50 pF

ai14141

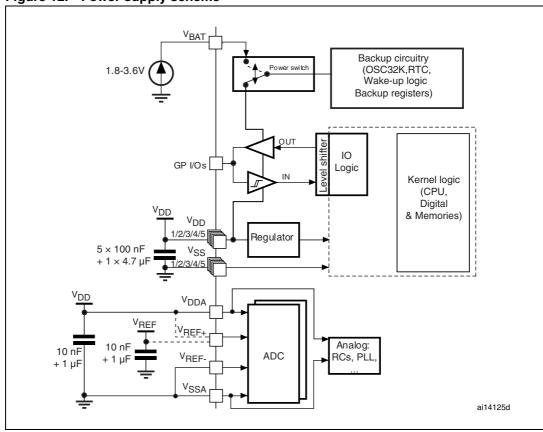

# 5.1.6 Power supply scheme

Figure 12. Power supply scheme

Caution: In Figure 12, the 4.7  $\mu$ F capacitor must be connected to  $V_{DD3}$ .

Ratings **Symbol** Unit Max. Total current into V<sub>DD</sub>/V<sub>DDA</sub> power lines (source)<sup>(1)</sup> 150  $I_{VDD}$ Total current out of V<sub>SS</sub> ground lines (sink)<sup>(1)</sup> 150  $I_{VSS}$ Output current sunk by any I/O and control pin 25  $I_{10}$ Output current source by any I/Os and control pin **- 25** mΑ Injected current on NRST pin ± 5 I<sub>INJ(PIN)</sub> (2)(3) Injected current on HSE OSC\_IN and LSE OSC\_IN pins ± 5 Injected current on any other pin<sup>(4)</sup> ± 5  $\Sigma I_{\text{INJ(PIN)}}^{(2)}$ Total injected current (sum of all I/O and control pins) (4) ± 25

Table 7. Current characteristics

- All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

- 2.  $I_{INJ(PIN)}$  must never be exceeded. This is implicitly insured if  $V_{IN}$  maximum is respected. If  $V_{IN}$  maximum cannot be respected, the injection current must be limited externally to the  $I_{INJ(PIN)}$  value. A positive injection is induced by  $V_{IN} > V_{DD}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ .

- 3. Negative injection disturbs the analog performance of the device. See note in Section 5.3.17: 12-bit ADC characteristics.

- 4. When several inputs are submitted to a current injection, the maximum ΣI<sub>INJ(PIN)</sub> is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterization with ΣI<sub>INJ(PIN)</sub> maximum current injection on four I/O port pins of the device.

Table 8. Thermal characteristics

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to +150 | °C   |

| T <sub>J</sub>   | Maximum junction temperature | 150         | °C   |

# 5.3 Operating conditions

## 5.3.1 General operating conditions

Table 9. General operating conditions

| Symbol                          | Parameter                               | Conditions                        | Min | Max | Unit |

|---------------------------------|-----------------------------------------|-----------------------------------|-----|-----|------|

| f <sub>HCLK</sub>               | Internal AHB clock frequency            |                                   | 0   | 72  |      |

| f <sub>PCLK1</sub>              | Internal APB1 clock frequency           | 0                                 | 36  | MHz |      |

| f <sub>PCLK2</sub>              | Internal APB2 clock frequency           |                                   | 0   | 72  |      |

| $V_{DD}$                        | Standard operating voltage              |                                   | 2   | 3.6 | V    |

| V (1)                           | Analog operating voltage (ADC not used) | Must be the same potential        | 2   | 3.6 | V    |

| V <sub>DDA</sub> <sup>(1)</sup> | Analog operating voltage (ADC used)     | as V <sub>DD</sub> <sup>(2)</sup> | 2.4 | 3.6 | v    |

| V <sub>BAT</sub>                | Backup operating voltage                |                                   | 1.8 | 3.6 | V    |

-40

125

| Symbol         | Parameter                                           | Conditions                           | Min | Max  | Unit |  |

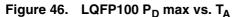

|----------------|-----------------------------------------------------|--------------------------------------|-----|------|------|--|

|                |                                                     | LFBGA100                             |     | 454  |      |  |

|                |                                                     | LQFP100                              |     | 434  |      |  |

| В              | Power dissipation at T <sub>A</sub> = 85 °C         | TFBGA64                              |     | 308  | m\\\ |  |

| P <sub>D</sub> | for suffix 6 or $T_A = 105$ °C for suffix $7^{(3)}$ | LQFP64                               |     | 444  | mW   |  |

|                |                                                     | LQFP48                               |     | 363  |      |  |

|                |                                                     | VFQFPN36                             |     | 1110 |      |  |

|                | Ambient temperature for 6 suffix version            | Maximum power dissipation            | -40 | 85   | °C   |  |

| Т,             |                                                     | Low power dissipation <sup>(4)</sup> | -40 | 105  |      |  |

| TA             | Ambient temperature for 7                           | Maximum power dissipation            | -40 | 105  | 00   |  |

|                | suffix version                                      | Low power dissipation <sup>(4)</sup> | -40 | 125  | °C   |  |

| т.             | lunation tomporature range                          | 6 suffix version                     | -40 | 105  | °C   |  |

| TJ             | Junction temperature range                          | 7 ouffix version                     | 40  | 105  | C    |  |

Table 9. General operating conditions (continued)

7 suffix version

## 5.3.2 Operating conditions at power-up / power-down

Subject to general operating conditions for T<sub>A</sub>.

Table 10. Operating conditions at power-up / power-down

| Symbol | Parameter                      | Conditions | Min | Max      | Unit  |

|--------|--------------------------------|------------|-----|----------|-------|

|        | V <sub>DD</sub> rise time rate |            | 0   | $\infty$ | us/V  |

| t∨DD   | V <sub>DD</sub> fall time rate |            | 20  | 8        | μ5/ ν |

#### 5.3.3 Embedded reset and power control block characteristics

The parameters given in *Table 11* are derived from tests performed under ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in *Table 9*.

<sup>1.</sup> When the ADC is used, refer to Table 45: ADC characteristics.

<sup>2.</sup> It is recommended to power  $V_{DD}$  and  $V_{DDA}$  from the same source. A maximum difference of 300 mV between  $V_{DD}$  and  $V_{DDA}$  can be tolerated during power-up and operation.

<sup>3.</sup> If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>J</sub>max (see *Table 6.2: Thermal characteristics on page 81*).

In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>J</sub>max (see Table 6.2: Thermal characteristics on page 81).

Table 13. Maximum current consumption in Run mode, code with data processing running from Flash

| Cumhal          | D                             | O a maliki a ma                     |                   | Ma                     | l lasit                 |      |

|-----------------|-------------------------------|-------------------------------------|-------------------|------------------------|-------------------------|------|

| Symbol          | Parameter                     | Conditions                          | f <sub>HCLK</sub> | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |

|                 |                               |                                     | 72 MHz            | 50                     | 50.3                    |      |

|                 |                               |                                     | 48 MHz            | 36.1                   | 36.2                    |      |

|                 |                               | External clock <sup>(2)</sup> , all | 36 MHz            | 28.6                   | 28.7                    |      |

|                 | Supply current in<br>Run mode | peripherals enabled                 | 24 MHz            | 19.9                   | 20.1                    | - mA |

|                 |                               |                                     | 16 MHz            | 14.7                   | 14.9                    |      |

|                 |                               |                                     | 8 MHz             | 8.6                    | 8.9                     |      |

| I <sub>DD</sub> |                               |                                     | 72 MHz            | 32.8                   | 32.9                    |      |

|                 |                               |                                     | 48 MHz            | 24.4                   | 24.5                    |      |

|                 |                               | External clock <sup>(2)</sup> , all | 36 MHz            | 19.8                   | 19.9                    |      |

|                 |                               | peripherals disabled                | 24 MHz            | 13.9                   | 14.2                    |      |

|                 |                               |                                     | 16 MHz            | 10.7                   | 11                      |      |

|                 |                               |                                     | 8 MHz             | 6.8                    | 7.1                     |      |

<sup>1.</sup> Based on characterization, not tested in production.

Table 14. Maximum current consumption in Run mode, code with data processing running from RAM

| Symbol          | Parameter                  | Conditions                          | f                   | Ma                     | Unit                    |       |  |

|-----------------|----------------------------|-------------------------------------|---------------------|------------------------|-------------------------|-------|--|

| Symbol          | Farameter                  | Conditions                          | fHCLK               | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Oilit |  |

|                 |                            |                                     | 72 MHz              | 48                     | 50                      |       |  |

|                 |                            |                                     | 48 MHz              | 31.5                   | 32                      |       |  |

|                 |                            | External clock <sup>(2)</sup> , all | 36 MHz              | 24                     | 25.5                    |       |  |

|                 | Supply current in Run mode | peripherals enabled                 | peripherals enabled | 24 MHz                 | 17.5                    | 18    |  |

|                 |                            |                                     | 16 MHz              | 12.5                   | 13                      |       |  |

|                 |                            |                                     | 8 MHz               | 7.5                    | 8                       | mA    |  |

| I <sub>DD</sub> |                            |                                     | 72 MHz              | 29                     | 29.5                    | IIIA  |  |

|                 |                            |                                     | 48 MHz              | 20.5                   | 21                      |       |  |

|                 |                            | External clock <sup>(2)</sup> , all | 36 MHz              | 16                     | 16.5                    |       |  |

|                 |                            | peripherals disabled                | 24 MHz              | 11.5                   | 12                      |       |  |

|                 |                            |                                     | 16 MHz              | 8.5                    | 9                       |       |  |

|                 |                            |                                     | 8 MHz               | 5.5                    | 6                       |       |  |

<sup>1.</sup> Based on characterization, tested in production at  $V_{DD}\,\text{max}$ ,  $f_{HCLK}\,\text{max}$ .

<sup>2.</sup> External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

<sup>2.</sup> External clock is 8 MHz and PLL is on when  $f_{HCLK} > 8$  MHz.

#### **Typical current consumption**

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load).

- All peripherals are disabled except if it is explicitly mentioned.

- The Flash access time is adjusted to f<sub>HCLK</sub> frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 48 MHz and 2 wait states above).

- Ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in Table 9.

- Prefetch is ON (Reminder: this bit must be set before clock setting and bus prescaling)

- When the peripherals are enabled  $f_{PCLK1} = f_{HCLK}/4$ ,  $f_{PCLK2} = f_{HCLK}/2$ ,  $f_{ADCCLK} = f_{PCLK2}/4$

Table 17. Typical current consumption in Run mode, code with data processing running from Flash

|                 |                                  |                               |                   | Ту                                     |                          |      |

|-----------------|----------------------------------|-------------------------------|-------------------|----------------------------------------|--------------------------|------|

| Symbol Pa       | Parameter                        | Conditions                    | f <sub>HCLK</sub> | All peripherals enabled <sup>(2)</sup> | All peripherals disabled | Unit |

|                 |                                  |                               | 72 MHz            | 36                                     | 27                       |      |

|                 |                                  |                               | 48 MHz            | 24.2                                   | 18.6                     |      |

|                 |                                  |                               | 36 MHz            | 19                                     | 14.8                     |      |

|                 |                                  |                               | 24 MHz            | 12.9                                   | 10.1                     |      |

|                 |                                  |                               | 16 MHz            | 9.3                                    | 7.4                      |      |

|                 |                                  | External clock <sup>(3)</sup> | 8 MHz             | 5.5                                    | 4.6                      | mA   |

|                 | Supply<br>current in<br>Run mode |                               | 4 MHz             | 3.3                                    | 2.8                      |      |

|                 |                                  |                               | 2 MHz             | 2.2                                    | 1.9                      |      |

|                 |                                  |                               | 1 MHz             | 1.6                                    | 1.45                     |      |

|                 |                                  |                               | 500 kHz           | 1.3                                    | 1.25                     |      |

|                 |                                  |                               | 125 kHz           | 1.08                                   | 1.06                     |      |

| I <sub>DD</sub> |                                  | Running on high               | 64 MHz            | 31.4                                   | 23.9                     |      |

|                 |                                  |                               | 48 MHz            | 23.5                                   | 17.9                     |      |

|                 |                                  |                               | 36 MHz            | 18.3                                   | 14.1                     |      |

|                 |                                  |                               | 24 MHz            | 12.2                                   | 9.5                      |      |

|                 |                                  | speed internal RC             | 16 MHz            | 8.5                                    | 6.8                      |      |

|                 |                                  | (HSI), AHB prescaler used to  | 8 MHz             | 4.9                                    | 4                        | mA   |

|                 |                                  | reduce the                    | 4 MHz             | 2.7                                    | 2.2                      |      |

|                 |                                  | frequency                     | 2 MHz             | 1.6                                    | 1.4                      |      |

|                 |                                  |                               | 1 MHz             | 1.02                                   | 0.9                      |      |

|                 |                                  |                               | 500 kHz           | 0.73                                   | 0.67                     |      |

|                 |                                  |                               | 125 kHz           | 0.5                                    | 0.48                     |      |

<sup>1.</sup> Typical values are measures at  $T_A$  = 25 °C,  $V_{DD}$  = 3.3 V.

<sup>2.</sup> Add an additional power consumption of 0.8 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

<sup>3.</sup> External clock is 8 MHz and PLL is on when  $f_{HCLK} > 8$  MHz.

| Symbol            | Parameter           | Conditions                                                                             | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|-------------------|---------------------|----------------------------------------------------------------------------------------|--------------------|-----|--------------------|------|

| I <sub>DD</sub>   |                     | Read mode<br>f <sub>HCLK</sub> = 72 MHz with 2 wait<br>states, V <sub>DD</sub> = 3.3 V |                    |     | 20                 | mA   |

|                   | Supply current      | Write / Erase modes<br>f <sub>HCLK</sub> = 72 MHz, V <sub>DD</sub> = 3.3 V             |                    |     | 5                  | mA   |

|                   |                     | Power-down mode / Halt,<br>V <sub>DD</sub> = 3.0 to 3.6 V                              |                    |     | 50                 | μΑ   |

| V <sub>prog</sub> | Programming voltage |                                                                                        | 2                  |     | 3.6                | V    |

Table 28. Flash memory characteristics (continued)

Table 29. Flash memory endurance and data retention

| Symbol             | Parameter      | Conditions                                                                              | Value              |     |     | Unit    |

|--------------------|----------------|-----------------------------------------------------------------------------------------|--------------------|-----|-----|---------|

|                    |                | Conditions                                                                              | Min <sup>(1)</sup> | Тур | Max |         |

| N <sub>END</sub>   | Endurance      | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                 |     |     | kcycles |

|                    |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30                 |     |     |         |

| t <sub>RET</sub> [ | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                 |     |     | Years   |

|                    |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                 |     |     |         |

<sup>1.</sup> Based on characterization, not tested in production.

#### 5.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- **Electrostatic discharge (ESD)** (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 1000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 1000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 30*. They are based on the EMS levels and classes defined in application note AN1709.

<sup>1.</sup> Guaranteed by design, not tested in production.

<sup>2.</sup> Cycling performed over the whole temperature range.

#### 5.3.12 I/O port characteristics

# General input/output characteristics

Unless otherwise specified, the parameters given in *Table 34* are derived from tests performed under the conditions summarized in *Table 9*. All I/Os are CMOS and TTL compliant.

Table 34. I/O static characteristics

| Symbol           | Parameter                                                     | Conditions                                      | Min                               | Тур | Max                  | Unit |  |

|------------------|---------------------------------------------------------------|-------------------------------------------------|-----------------------------------|-----|----------------------|------|--|

| $V_{IL}$         | Input low level voltage                                       |                                                 | -0.5                              |     | 0.8                  |      |  |

| V <sub>IH</sub>  | Standard IO input high level voltage                          | TTL ports                                       | 2                                 |     | V <sub>DD</sub> +0.5 | V    |  |

|                  | IO FT <sup>(1)</sup> input high level voltage                 |                                                 | 2                                 |     | 5.5V                 |      |  |

| V <sub>IL</sub>  | Input low level voltage                                       | CMOS norts                                      | -0.5                              |     | 0.35 V <sub>DD</sub> | V    |  |

| V <sub>IH</sub>  | Input high level voltage                                      | CMOS ports                                      | 0.65 V <sub>DD</sub>              |     | V <sub>DD</sub> +0.5 | v    |  |

| V                | Standard IO Schmitt trigger voltage hysteresis <sup>(2)</sup> |                                                 | 200                               |     |                      | mV   |  |

| V <sub>hys</sub> | IO FT Schmitt trigger voltage hysteresis <sup>(2)</sup>       |                                                 | 5% V <sub>DD</sub> <sup>(3)</sup> |     |                      | mV   |  |

| ı                | Input leakage current <sup>(4)</sup>                          | $V_{SS} \le V_{IN} \le V_{DD}$<br>Standard I/Os |                                   |     | ±1                   |      |  |

| I <sub>lkg</sub> | Imput leakage current V                                       | V <sub>IN</sub> = 5 V<br>I/O FT                 |                                   |     | 3                    | μΑ   |  |

| R <sub>PU</sub>  | Weak pull-up equivalent resistor <sup>(5)</sup>               | $V_{IN} = V_{SS}$                               | 30                                | 40  | 50                   | kΩ   |  |

| R <sub>PD</sub>  | Weak pull-down equivalent resistor <sup>(5)</sup>             | $V_{IN} = V_{DD}$                               | 30                                | 40  | 50                   | kΩ   |  |

| C <sub>IO</sub>  | I/O pin capacitance                                           |                                                 |                                   | 5   |                      | pF   |  |

<sup>1.</sup> FT = Five-volt tolerant.

- 4. Leakage could be higher than max. if negative current is injected on adjacent pins.

- Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This MOS/NMOS contribution to the series resistance is minimum (~10% order).

All I/Os are CMOS and TTL compliant (no software configuration required), their characteristics consider the most strict CMOS-technology or TTL parameters:

#### For V<sub>IH</sub>:

- if V<sub>DD</sub> is in the [2.00 V 3.08 V] range: CMOS characteristics but TTL included

- if V<sub>DD</sub> is in the [3.08 V 3.60 V] range: TTL characteristics but CMOS included

#### For V<sub>II</sub>:

- if V<sub>DD</sub> is in the [2.00 V 2.28 V] range: TTL characteristics but CMOS included

- if V<sub>DD</sub> is in the [2.28 V 3.60 V] range: CMOS characteristics but TTL included

<sup>2.</sup> Hysteresis voltage between Schmitt trigger switching levels. Based on characterization, not tested in production.

<sup>3.</sup> With a minimum of 100 mV.

#### 5.3.15 Communications interfaces

#### I<sup>2</sup>C interface characteristics

Unless otherwise specified, the parameters given in *Table 39* are derived from tests performed under the ambient temperature,  $f_{PCLK1}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

The STM32F103xx performance line  $I^2C$  interface meets the requirements of the standard  $I^2C$  communication protocol with the following restrictions: the I/O pins SDA and SCL are mapped to are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and  $V_{DD}$  is disabled, but is still present.

The I<sup>2</sup>C characteristics are described in *Table 39*. Refer also to *Section 5.3.12: I/O port characteristics* for more details on the input/output alternate function characteristics (SDA and SCL).

Table 39. I<sup>2</sup>C characteristics

| Symbol                                                 | Parameter                               | Standard mode I <sup>2</sup> C <sup>(1)</sup> |      | Fast mode I <sup>2</sup> C <sup>(1)(2)</sup> |                    | Unit  |

|--------------------------------------------------------|-----------------------------------------|-----------------------------------------------|------|----------------------------------------------|--------------------|-------|

| Symbol                                                 | Farameter                               | Min                                           | Max  | Min                                          | Max                | Oilit |

| t <sub>w(SCLL)</sub>                                   | SCL clock low time                      | 4.7                                           |      | 1.3                                          |                    | ше    |

| t <sub>w(SCLH)</sub>                                   | SCL clock high time                     | 4.0                                           |      | 0.6                                          |                    | μs    |

| t <sub>su(SDA)</sub>                                   | SDA setup time                          | 250                                           |      | 100                                          |                    |       |

| t <sub>h(SDA)</sub>                                    | SDA data hold time                      | 0(3)                                          |      | 0 <sup>(4)</sup>                             | 900 <sup>(3)</sup> |       |

| t <sub>r(SDA)</sub>                                    | SDA and SCL rise time                   |                                               | 1000 | 20 + 0.1C <sub>b</sub>                       | 300                | ns    |

| $\begin{matrix} t_{f(SDA)} \\ t_{f(SCL)} \end{matrix}$ | SDA and SCL fall time                   |                                               | 300  |                                              | 300                |       |

| t <sub>h(STA)</sub>                                    | Start condition hold time               | 4.0                                           |      | 0.6                                          |                    |       |

| t <sub>su(STA)</sub>                                   | Repeated Start condition setup time     | 4.7                                           |      | 0.6                                          |                    | μs    |

| t <sub>su(STO)</sub>                                   | Stop condition setup time               | 4.0                                           |      | 0.6                                          |                    | μS    |

| t <sub>w(STO:STA)</sub>                                | Stop to Start condition time (bus free) | 4.7                                           |      | 1.3                                          |                    | μS    |

| C <sub>b</sub>                                         | Capacitive load for each bus line       |                                               | 400  |                                              | 400                | pF    |

<sup>1.</sup> Guaranteed by design, not tested in production.

f<sub>PCLK1</sub> must be higher than 2 MHz to achieve the maximum standard mode I<sup>2</sup>C frequency. It must be higher than 4 MHz to achieve the maximum fast mode I<sup>2</sup>C frequency.

<sup>3.</sup> The maximum hold time of the Start condition has only to be met if the interface does not stretch the low period of SCL signal.

<sup>4.</sup> The device must internally provide a hold time of at least 300ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL.

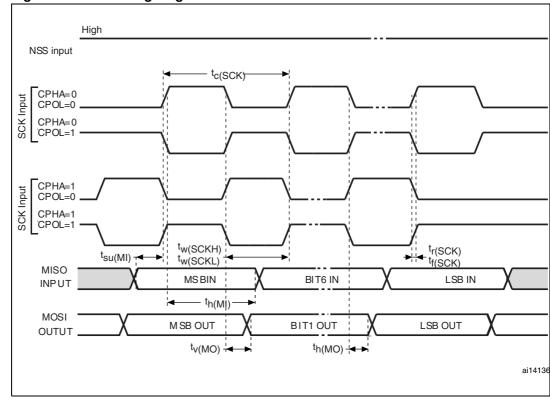

Figure 28. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

# **USB** characteristics

The USB interface is USB-IF certified (Full Speed).

Table 42. USB startup time

| Symbol                              | Parameter                    | Max | Unit |

|-------------------------------------|------------------------------|-----|------|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB transceiver startup time | 1   | μs   |

1. Guaranteed by design, not tested in production.

# 6 Package characteristics

# 6.1 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK® is an ST trademark.

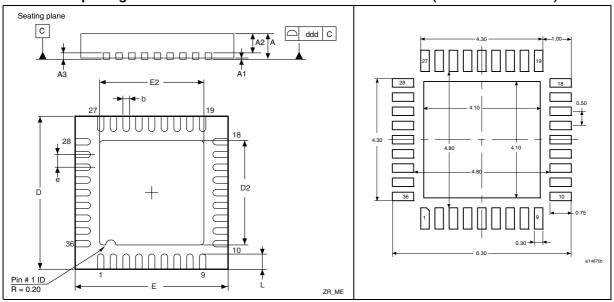

Figure 34. VFQFPN36 6 x 6 mm, 0.5 mm pitch, package outline<sup>(1)</sup>

Figure 35. Recommended footprint (dimensions in mm)<sup>(1)(2)(3)</sup>

- 1. Drawing is not to scale.

- 2. The back-side pad is not internally connected to the  $\rm V_{SS}$  or  $\rm V_{DD}$  power pads.

- 3. There is an exposed die pad on the underside of the VFQFPN package. It should be soldered to the PCB. All leads should also be soldered to the PCB.

Table 50. VFQFPN36 6 x 6 mm, 0.5 mm pitch, package mechanical data

| Complete |       | millimeters | illimeters inc |        |        | ches <sup>(1)</sup> |  |

|----------|-------|-------------|----------------|--------|--------|---------------------|--|

| Symbol   | Min   | Тур         | Max            | Min    | Тур    | Max                 |  |

| Α        | 0.800 | 0.900       | 1.000          | 0.0315 | 0.0354 | 0.0394              |  |

| A1       |       | 0.020       | 0.050          |        | 0.0008 | 0.0020              |  |

| A2       |       | 0.650       | 1.000          |        | 0.0256 | 0.0394              |  |

| A3       |       | 0.250       |                |        | 0.0098 |                     |  |

| b        | 0.180 | 0.230       | 0.300          | 0.0071 | 0.0091 | 0.0118              |  |

| D        | 5.875 | 6.000       | 6.125          | 0.2313 | 0.2362 | 0.2411              |  |

| D2       | 1.750 | 3.700       | 4.250          | 0.0689 | 0.1457 | 0.1673              |  |

| E        | 5.875 | 6.000       | 6.125          | 0.2313 | 0.2362 | 0.2411              |  |

| E2       | 1.750 | 3.700       | 4.250          | 0.0689 | 0.1457 | 0.1673              |  |

| е        | 0.450 | 0.500       | 0.550          | 0.0177 | 0.0197 | 0.0217              |  |

| L        | 0.350 | 0.550       | 0.750          | 0.0138 | 0.0217 | 0.0295              |  |

| ddd      | 0.080 |             |                |        | 0.0031 | 1                   |  |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

Using the values obtained in  $Table 56 T_{Jmax}$  is calculated as follows:

For LQFP100, 46 °C/W

$$T_{Jmax} = 115 \, ^{\circ}C + (46 \, ^{\circ}C/W \times 134 \, mW) = 115 \, ^{\circ}C + 6.2 \, ^{\circ}C = 121.2 \, ^{\circ}C$$

This is within the range of the suffix 7 version parts ( $-40 < T_J < 125$  °C).

In this case, parts must be ordered at least with the temperature range suffix 7 (see *Table 57: Ordering information scheme*).

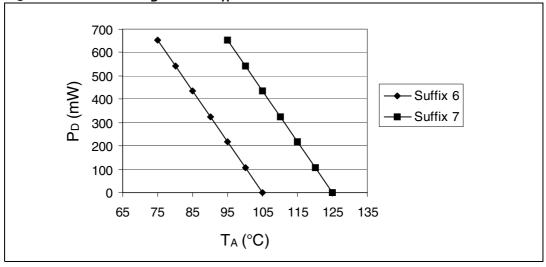

# 7 Ordering information scheme

Table 57. Ordering information scheme

xxx = programmed parts

TR = tape and real

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.

**577**

Although STM32F103x6 devices are not described in this datasheet, orderable part numbers that do not show the A internal code after temperature range code 6 or 7 should be referred to this datasheet for the electrical characteristics. The low-density datasheet only covers STM32F103x6 devices that feature the A code.

Table 58. Document revision history (continued)

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23-Apr-2009 | 10       | I/O information clarified <i>on page 1</i> .  Figure 3: STM32F103xx performance line LFBGA100 ballout modified.  Figure 9: Memory map modified. Table 4: Timer feature comparison added.  PB4, PB13, PB14, PB15, PB3/TRACESWO moved from Default column to Remap column in Table 5: Medium-density STM32F103xx pin definitions.  PD for LFBGA100 corrected in Table 9: General operating conditions.  Note modified in Table 13: Maximum current consumption in Run mode, code with data processing running from Flash and Table 15: Maximum current consumption in Sleep mode, code running from Flash or RAM.  Table 20: High-speed external user clock characteristics and Table 21: Low-speed external user clock characteristics modified.  Figure 17 shows a typical curve (title modified). ACCHSI max values modified in Table 24: HSI oscillator characteristics.  TFBGA64 package added (see Table 54 and Table 42). Small text changes. |