Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore ProcessorARM@ Cortex@-M3Core Size32-Bit Single-CoreSpeed24MHzConnectivityPC, IrDA, LINbus, SPI, UART/USARTPeripheralsDMA, PDR, POR, PVD, PWM, Temp Sensor, WDTNumber of I/O37Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size4K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 10x12b; D/A 2x12bOscillator TypeInternalQperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFP (7x7) |                            |                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------|

| Core Size32-Bit Single-CoreSpeed24MHzConnectivityI*C, IrDA, LINbus, SPI, UART/USARTPeripheralsDMA, PDR, POR, PVD, PWM, Temp Sensor, WDTNumber of I/O37Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size4K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 10x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package48-LQFP (7x7)                   | Product Status             | Active                                                                   |

| Speed24MHzConnectivityIPC, IrDA, LINbus, SPI, UART/USARTPeripheralsDMA, PDR, POR, PVD, PWM, Temp Sensor, WDTNumber of I/O37Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size4K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 10x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFP (7x7)                                                                            | Core Processor             | ARM® Cortex®-M3                                                          |

| ConnectivityPC, IrDA, LINbus, SPI, UART/USARTPeripheralsDMA, PDR, POR, PVD, PWM, Temp Sensor, WDTNumber of I/O37Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size4K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 10x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFP (7x7)                                                                                       | Core Size                  | 32-Bit Single-Core                                                       |

| PeripheralsDMA, PDR, POR, PVD, PWM, Temp Sensor, WDTNumber of I/O37Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size4K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 10x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFP (7x7)                                                                                                                                    | Speed                      | 24MHz                                                                    |

| Number of I/O37Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size4K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 10x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package48-LQFP (7x7)                                                                                                                                                          | Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size4K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 10x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFP (7x7)                                                                                                                                                                                                       | Peripherals                | DMA, PDR, POR, PVD, PWM, Temp Sensor, WDT                                |

| Program Memory TypeFLASHEEPROM Size-RAM Size4K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 10x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package48-LQFP (7x7)                                                                                                                                                                                                          | Number of I/O              | 37                                                                       |

| EEPROM Size-RAM Size4K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 10x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package48-LQFP (7x7)                                                                                                                                                                                                                                  | Program Memory Size        | 16KB (16K x 8)                                                           |

| RAM Size4K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 10x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package48-LQFP (7x7)                                                                                                                                                                                                                                              | Program Memory Type        | FLASH                                                                    |

| Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 10x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package48-LQFP (7x7)                                                                                                                                                                                                                                                            | EEPROM Size                | -                                                                        |

| Data ConvertersA/D 10x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package48-LQFP (7x7)                                                                                                                                                                                                                                                                                               | RAM Size                   | 4K x 8                                                                   |

| Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package48-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                   | Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                |

| Operating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package48-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                          | Data Converters            | A/D 10x12b; D/A 2x12b                                                    |

| Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package48-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                                                | Oscillator Type            | Internal                                                                 |

| Package / Case48-LQFPSupplier Device Package48-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                                                                          | Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Supplier Device Package     48-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                                                                                          | Mounting Type              | Surface Mount                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Package / Case             | 48-LQFP                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Supplier Device Package    | 48-LQFP (7x7)                                                            |

| Purchase URL https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f100c4t6btr                                                                                                                                                                                                                                                                                                                                                                                              | Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f100c4t6btr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1    | Intro | duction  |                                                                                |  |  |  |  |

|------|-------|----------|--------------------------------------------------------------------------------|--|--|--|--|

| 2    | Desc  | cription |                                                                                |  |  |  |  |

|      | 2.1   | Device   | Device overview                                                                |  |  |  |  |

|      | 2.2   | Overvie  | ew                                                                             |  |  |  |  |

|      |       | 2.2.1    | ARM <sup>®</sup> Cortex <sup>®</sup> -M3 core with embedded Flash and SRAM     |  |  |  |  |

|      |       | 2.2.2    | Embedded Flash memory14                                                        |  |  |  |  |

|      |       | 2.2.3    | CRC (cyclic redundancy check) calculation unit                                 |  |  |  |  |

|      |       | 2.2.4    | Embedded SRAM                                                                  |  |  |  |  |

|      |       | 2.2.5    | Nested vectored interrupt controller (NVIC)                                    |  |  |  |  |

|      |       | 2.2.6    | External interrupt/event controller (EXTI)                                     |  |  |  |  |

|      |       | 2.2.7    | Clocks and startup                                                             |  |  |  |  |

|      |       | 2.2.8    | Boot modes                                                                     |  |  |  |  |

|      |       | 2.2.9    | Power supply schemes                                                           |  |  |  |  |

|      |       | 2.2.10   | Power supply supervisor15                                                      |  |  |  |  |

|      |       | 2.2.11   | Voltage regulator                                                              |  |  |  |  |

|      |       | 2.2.12   | Low-power modes                                                                |  |  |  |  |

|      |       | 2.2.13   | DMA                                                                            |  |  |  |  |

|      |       | 2.2.14   | RTC (real-time clock) and backup registers                                     |  |  |  |  |

|      |       | 2.2.15   | Timers and watchdogs 17                                                        |  |  |  |  |

|      |       | 2.2.16   | l <sup>2</sup> C bus                                                           |  |  |  |  |

|      |       | 2.2.17   | Universal synchronous/asynchronous receiver transmitter (USART) 19             |  |  |  |  |

|      |       | 2.2.18   | Serial peripheral interface (SPI) 20                                           |  |  |  |  |

|      |       | 2.2.19   | HDMI (high-definition multimedia interface) consumer electronics control (CEC) |  |  |  |  |

|      |       | 2.2.20   | GPIOs (general-purpose inputs/outputs)                                         |  |  |  |  |

|      |       | 2.2.21   | Remap capability                                                               |  |  |  |  |

|      |       | 2.2.22   | ADC (analog-to-digital converter)                                              |  |  |  |  |

|      |       | 2.2.23   | DAC (digital-to-analog converter)21                                            |  |  |  |  |

|      |       | 2.2.24   | Temperature sensor                                                             |  |  |  |  |

|      |       | 2.2.25   | Serial wire JTAG debug port (SWJ-DP)                                           |  |  |  |  |

| 3    | Pino  | uts and  | pin description 22                                                             |  |  |  |  |

| 4    | Mem   | ory map  | oping                                                                          |  |  |  |  |

| 2/96 |       |          | DocID16455 Rev 9                                                               |  |  |  |  |

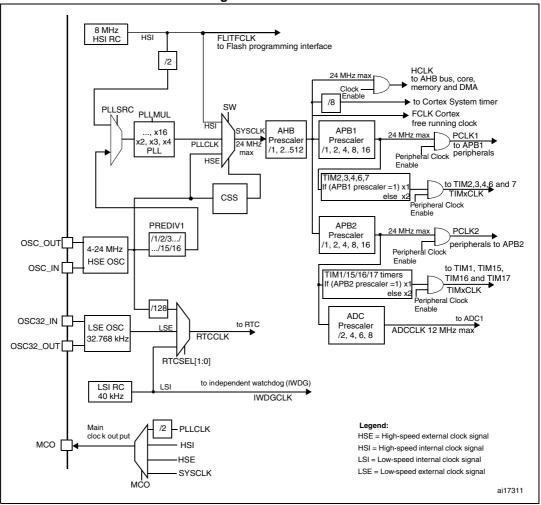

Figure 2. Clock tree

1. To have an ADC conversion time of 1.2  $\mu s,$  APB2 must be at 24 MHz.

#### 2.2.6 External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 18 edge detector lines used to generate interrupt/event requests. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 80 GPIOs can be connected to the 16 external interrupt lines.

#### 2.2.7 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-24 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example on failure of an indirectly used external crystal, resonator or oscillator).

Several prescalers allow the configuration of the AHB frequency, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the AHB and the APB domains is 24 MHz.

#### 2.2.8 Boot modes

At startup, boot pins are used to select one of three boot options:

- Boot from user Flash

- Boot from system memory

- Boot from embedded SRAM

The boot loader is located in System Memory. It is used to reprogram the Flash memory by using USART1. For further details please refer to AN2606.

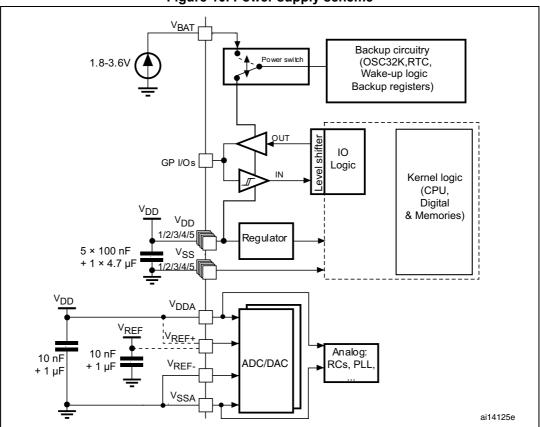

#### 2.2.9 **Power supply schemes**

- $V_{DD}$  = 2.0 to 3.6 V: External power supply for I/Os and the internal regulator. Provided externally through  $V_{DD}$  pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 2.0 to 3.6 V: External analog power supplies for ADC, DAC, Reset blocks, RCs and PLL (minimum voltage to be applied to V<sub>DDA</sub> is 2.4 V when the ADC or DAC is used).

$V_{DDA}$  and  $V_{SSA}$  must be connected to  $V_{DD}$  and  $V_{SS},$  respectively.

• V<sub>BAT</sub> = 1.8 to 3.6 V: Power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

#### 2.2.10 Power supply supervisor

The device has an integrated power on reset (POR)/power down reset (PDR) circuitry. It is always active, and ensures proper operation starting from/down to 2 V. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$ , without the need for an external reset circuit.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is

Each channel is connected to dedicated hardware DMA requests, with support for software trigger on each channel. Configuration is made by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: SPI, DAC, I<sup>2</sup>C, USART, all timers and ADC.

#### 2.2.14 RTC (real-time clock) and backup registers

The RTC and the backup registers are supplied through a switch that takes power either on  $V_{DD}$  supply when present or through the  $V_{BAT}$  pin. The backup registers are ten 16-bit registers used to store 20 bytes of user application data when  $V_{DD}$  power is not present.

The real-time clock provides a set of continuously running counters which can be used with suitable software to provide a clock calendar function, and provides an alarm interrupt and a periodic interrupt. It is clocked by a 32.768 kHz external crystal, resonator or oscillator, the internal low power RC oscillator or the high-speed external clock divided by 128. The internal low power RC has a typical frequency of 40 kHz. The RTC can be calibrated using an external 512 Hz output to compensate for any natural crystal deviation. The RTC features a 32-bit programmable counter for long term measurement using the Compare register to generate an alarm. A 20-bit prescaler is used for the time base clock and is by default configured to generate a time base of 1 second from a clock at 32.768 kHz.

#### 2.2.15 Timers and watchdogs

The STM32F100xx devices include an advanced-control timer, six general-purpose timers, two basic timers and two watchdog timers.

Table 3 compares the features of the advanced-control, general-purpose and basic timers.

| Timer                  | Counter resolution | Counter<br>type         | Prescaler<br>factor                   | DMA request generation | Capture/compare<br>channels | Complementary outputs |

|------------------------|--------------------|-------------------------|---------------------------------------|------------------------|-----------------------------|-----------------------|

| TIM1                   | 16-bit             | Up,<br>down,<br>up/down | Any integer<br>between 1<br>and 65536 | Yes                    | 4                           | Yes                   |

| TIM2,<br>TIM3,<br>TIM4 | 16-bit             | Up,<br>down,<br>up/down | Any integer<br>between 1<br>and 65536 | Yes                    | 4                           | No                    |

| TIM15                  | 16-bit             | Up                      | Any integer<br>between 1<br>and 65536 | Yes                    | 2                           | Yes                   |

| TIM16,<br>TIM17        | 16-bit             | Up                      | Any integer<br>between 1<br>and 65536 | Yes                    | 1                           | Yes                   |

| TIM6,<br>TIM7          | 16-bit             | Up                      | Any integer<br>between 1<br>and 65536 | Yes                    | 0                           | No                    |

Table 3. Timer feature comparison

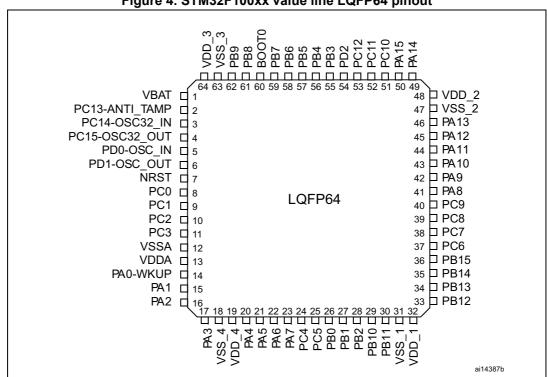

Figure 4. STM32F100xx value line LQFP64 pinout

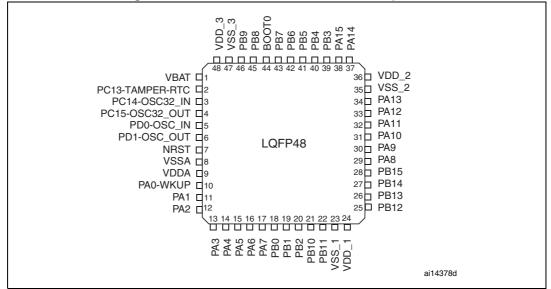

#### Figure 5. STM32F100xx value line LQFP48 pinout

DocID16455 Rev 9

|         | Pi     | ns      |        |                               |                     | y 31<br>ล                  |                                                  | Alternate functions <sup>(3)(4)</sup>                                                             |                          |

|---------|--------|---------|--------|-------------------------------|---------------------|----------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------|

| LQFP100 | LQFP64 | TFBGA64 | LQFP48 | Pin name                      | Type <sup>(1)</sup> | I / O level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                                                           | Remap                    |

| 9       | 4      | B1      | 4      | PC15-OSC32_OUT <sup>(5)</sup> | I/O                 | -                          | PC15 <sup>(6)</sup>                              | OSC32_OUT                                                                                         | -                        |

| 10      | -      | -       | -      | V <sub>SS_5</sub>             | S                   | -                          | V <sub>SS_5</sub>                                | -                                                                                                 | -                        |

| 11      | -      | -       | -      | V <sub>DD_5</sub>             | S                   | -                          | $V_{DD_5}$                                       | -                                                                                                 | -                        |

| 12      | 5      | C1      | 5      | OSC_IN                        | Ι                   | -                          | OSC_IN                                           | -                                                                                                 | PD0 <sup>(7)</sup>       |

| 13      | 6      | D1      | 6      | OSC_OUT                       | 0                   | -                          | OSC_OUT                                          | -                                                                                                 | PD1 <sup>(7)</sup>       |

| 14      | 7      | E1      | 7      | NRST                          | I/O                 | -                          | NRST                                             | -                                                                                                 | -                        |

| 15      | 8      | E3      | -      | PC0                           | I/O                 | -                          | PC0                                              | ADC1_IN10                                                                                         | -                        |

| 16      | 9      | E2      | -      | PC1                           | I/O                 | -                          | PC1                                              | ADC1_IN11                                                                                         | -                        |

| 17      | 10     | F2      | -      | PC2                           | I/O                 | -                          | PC2                                              | ADC1_IN12                                                                                         | -                        |

| 18      | 11     | _(8)    | -      | PC3                           | I/O                 | -                          | PC3                                              | ADC1_IN13                                                                                         | -                        |

| 19      | 12     | F1      | 8      | V <sub>SSA</sub>              | S                   | -                          | V <sub>SSA</sub>                                 | -                                                                                                 | -                        |

| 20      | -      | -       | -      | V <sub>REF-</sub>             | S                   | -                          | V <sub>REF-</sub>                                | -                                                                                                 | -                        |

| 21      | -      | G1      | -      | V <sub>REF+</sub>             | S                   | -                          | V <sub>REF+</sub>                                | -                                                                                                 | -                        |

| 22      | 13     | H1      | 9      | V <sub>DDA</sub>              | S                   | -                          | V <sub>DDA</sub>                                 | -                                                                                                 | -                        |

| 23      | 14     | G2      | 10     | PA0-WKUP                      | I/O                 | -                          | PA0                                              | WKUP / USART2_CTS <sup>(12)</sup> /<br>ADC1_IN0 /<br>TIM2_CH1_ETR <sup>(12)</sup>                 | -                        |

| 24      | 15     | H2      | 11     | PA1                           | I/O                 | -                          | PA1                                              | USART2_RTS <sup>(12)</sup> /<br>ADC1_IN1 / TIM2_CH2 <sup>(12)</sup>                               | -                        |

| 25      | 16     | F3      | 12     | PA2                           | I/O                 | -                          | PA2                                              | USART2_TX <sup>(12)</sup> /<br>ADC1_IN2 / TIM2_CH3 <sup>(12)</sup> /<br>TIM15_CH1 <sup>(12)</sup> | -                        |

| 26      | 17     | G3      | 13     | PA3                           | I/O                 | -                          | PA3                                              | USART2_RX <sup>(12)</sup> /<br>ADC1_IN3 / TIM2_CH4 <sup>(12)</sup><br>/ TIM15_CH2 <sup>(12)</sup> | -                        |

| 27      | 18     | C2      | -      | V <sub>SS_4</sub>             | S                   | -                          | V <sub>SS_4</sub>                                | -                                                                                                 | -                        |

| 28      | 19     | D2      | -      | V <sub>DD_4</sub>             | S                   | -                          | V <sub>DD_4</sub>                                | -                                                                                                 | -                        |

| 29      | 20     | H3      | 14     | PA4                           | I/O                 | -                          | PA4                                              | SPI1_NSS <sup>(12)</sup> /ADC1_IN4<br>USART2_CK <sup>(12)</sup> /<br>DAC1_OUT                     | -                        |

| 30      | 21     | F4      | 15     | PA5                           | I/O                 | -                          | PA5                                              | SPI1_SCK <sup>(12)</sup> /ADC1_IN5 /<br>DAC2_OUT                                                  | -                        |

| 31      | 22     | G4      | 16     | PA6                           | I/O                 | -                          | PA6                                              | SPI1_MISO <sup>(12)</sup> /ADC1_IN6/<br>TIM3_CH1 <sup>(12)</sup>                                  | TIM1_BKIN /<br>TIM16_CH1 |

| 32      | 23     | H4      | 17     | PA7                           | I/O                 | -                          | PA7                                              | SPI1_MOSI <sup>(12)</sup> /ADC1_IN7/<br>TIM3_CH2 <sup>(12)</sup>                                  | TIM1_CH1N<br>/ TIM17_CH1 |

Table 4. Low & medium-density STM32F100xx pin definitions (continued)

DocID16455 Rev 9

25/96

#### 5.1.6 Power supply scheme

**Caution:** In *Figure 10*, the 4.7  $\mu$ F capacitor must be connected to V<sub>DD3</sub>.

| Table 10. Embedded reset and power control block characteristics |                          |                             |                    |      |      |      |

|------------------------------------------------------------------|--------------------------|-----------------------------|--------------------|------|------|------|

| Symbol                                                           | Parameter                | Conditions                  | Min                | Тур  | Мах  | Unit |

|                                                                  |                          | PLS[2:0]=000 (rising edge)  | 2.1                | 2.18 | 2.26 | V    |

|                                                                  |                          | PLS[2:0]=000 (falling edge) | 2                  | 2.08 | 2.16 | V    |

|                                                                  |                          | PLS[2:0]=001 (rising edge)  | 2.19               | 2.28 | 2.37 | V    |

|                                                                  |                          | PLS[2:0]=001 (falling edge) | 2.09               | 2.18 | 2.27 | V    |

|                                                                  |                          | PLS[2:0]=010 (rising edge)  | 2.28               | 2.38 | 2.48 | V    |

|                                                                  |                          | PLS[2:0]=010 (falling edge) | 2.18               | 2.28 | 2.38 | V    |

|                                                                  |                          | PLS[2:0]=011 (rising edge)  | 2.38               | 2.48 | 2.58 | V    |

| V                                                                | Programmable voltage     | PLS[2:0]=011 (falling edge) | 2.28               | 2.38 | 2.48 | V    |

| V <sub>PVD</sub>                                                 | detector level selection | PLS[2:0]=100 (rising edge)  | 2.47               | 2.58 | 2.69 | V    |

|                                                                  |                          | PLS[2:0]=100 (falling edge) | 2.37               | 2.48 | 2.59 | V    |

|                                                                  |                          | PLS[2:0]=101 (rising edge)  | 2.57               | 2.68 | 2.79 | V    |

|                                                                  |                          | PLS[2:0]=101 (falling edge) | 2.47               | 2.58 | 2.69 | V    |

|                                                                  |                          | PLS[2:0]=110 (rising edge)  | 2.66               | 2.78 | 2.9  | V    |

|                                                                  |                          | PLS[2:0]=110 (falling edge) | 2.56               | 2.68 | 2.8  | V    |

|                                                                  |                          | PLS[2:0]=111 (rising edge)  | 2.76               | 2.88 | 3    | V    |

|                                                                  |                          | PLS[2:0]=111 (falling edge) | 2.66               | 2.78 | 2.9  | V    |

| V <sub>PVDhyst</sub> <sup>(2)</sup>                              | PVD hysteresis           | -                           | -                  | 100  | -    | mV   |

|                                                                  | Power on/power down      | Falling edge                | 1.8 <sup>(1)</sup> | 1.88 | 1.96 | V    |

| V <sub>POR/PDR</sub>                                             | reset threshold          | Rising edge                 | 1.84               | 1.92 | 2.0  | V    |

| V <sub>PDRhyst</sub> <sup>(2)</sup>                              | PDR hysteresis           | -                           | -                  | 40   | -    | mV   |

| t <sub>RSTTEMPO</sub> <sup>(2)</sup>                             | Reset temporization      | -                           | 1.5                | 2.5  | 4.5  | ms   |

Table 10. Embedded reset and power control block characteristics

1. The product behavior is guaranteed by design down to the minimum  $V_{\mbox{POR/PDR}}$  value.

2. Guaranteed by design.

#### 5.3.4 Embedded reference voltage

The parameters given in *Table 11* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

|                                       |                                                                     | I                                 |      |      |                     |        |

|---------------------------------------|---------------------------------------------------------------------|-----------------------------------|------|------|---------------------|--------|

| Symbol                                | Parameter                                                           | Conditions                        | Min  | Тур  | Мах                 | Unit   |

| V                                     | Internal reference voltage                                          | –40 °C < T <sub>A</sub> < +105 °C | 1.16 | 1.20 | 1.26                | V      |

| V <sub>REFINT</sub>                   | Internal reference voltage                                          | –40 °C < T <sub>A</sub> < +85 °C  | 1.16 | 1.20 | 1.24                | V      |

| T <sub>S_vrefint</sub> <sup>(1)</sup> | ADC sampling time when<br>reading the internal<br>reference voltage | -                                 | -    | 5.1  | 17.1 <sup>(2)</sup> | μs     |

| V <sub>RERINT</sub> <sup>(2)</sup>    | Internal reference voltage spread over the temperature range        | V <sub>DD</sub> = 3 V ±10 mV      | -    | -    | 10                  | mV     |

| T <sub>Coeff</sub> <sup>(2)</sup>     | Temperature coefficient                                             | -                                 | -    | -    | 100                 | ppm/°C |

Table 11. Embedded internal reference voltage

1. Shortest sampling time can be determined in the application by multiple iterations.

2. Guaranteed by design.

#### 5.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 11: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to Dhrystone 2.1 code.

#### Maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load)

- All peripherals are disabled except if it is explicitly mentioned

- Prefetch in on (reminder: this bit must be set before clock setting and bus prescaling)

- When the peripherals are enabled f<sub>PCLK1</sub> = f<sub>HCLK</sub>/2, f<sub>PCLK2</sub> = f<sub>HCLK</sub>

The parameters given in *Table 12* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

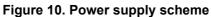

Figure 17. Typical current consumption in Standby mode versus temperature at  $V_{DD}$  = 3.3 V and 3.6 V

#### Typical current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load)

- All peripherals are disabled except if it is explicitly mentioned

- When the peripherals are enabled  $f_{PCLK1} = f_{HCLK}/4$ ,  $f_{PCLK2} = f_{HCLK}/2$ ,  $f_{ADCCLK} = f_{PCLK2}/4$

The parameters given in *Table 16* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

#### Output voltage levels

Unless otherwise specified, the parameters given in *Table 35* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*. All I/Os are CMOS and TTL compliant.

| Symbol                         | Parameter                                                                                                                                   | Conditions                                           | Min                  | Max | Unit |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------|-----|------|

| V <sub>OL</sub> <sup>(1)</sup> | Output Low level voltage for an I/O pin when 8 pins are sunk at the same time                                                               | CMOS port <sup>(2)</sup><br>I <sub>IO</sub> = +8 mA, | -                    | 0.4 | V    |

| V <sub>OH</sub> <sup>(3)</sup> | Output High level voltage for an I/O pin when 8 pins are sourced at the same time                                                           | $1_{O} - 40$ mA,<br>2.7 V < V <sub>DD</sub> < 3.6 V  | V <sub>DD</sub> -0.4 | -   | v    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at the same time                                                               | TTL port <sup>(2)</sup><br>I <sub>IO</sub> = +8 mA   | -                    | 0.4 | V    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin<br>when 8 pins are sourced at the same time $2.7 \text{ V} < \text{V}_{\text{DD}} < 300 \text{ m}$ |                                                      | 2.4                  | -   | v    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at the same time                                                               | l <sub>IO</sub> = +20 mA <sup>(4)</sup>              | -                    | 1.3 | V    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at the same time                                                           | 2.7 V < V <sub>DD</sub> < 3.6 V                      | V <sub>DD</sub> -1.3 | -   | v    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at the same time                                                               | I <sub>IO</sub> = +6 mA <sup>(4)</sup>               | -                    | 0.4 | V    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at the same time                                                           | 2 V < V <sub>DD</sub> < 2.7 V                        | V <sub>DD</sub> -0.4 | -   | V    |

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 6* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 6 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

4. Based on characterization data, not tested in production.

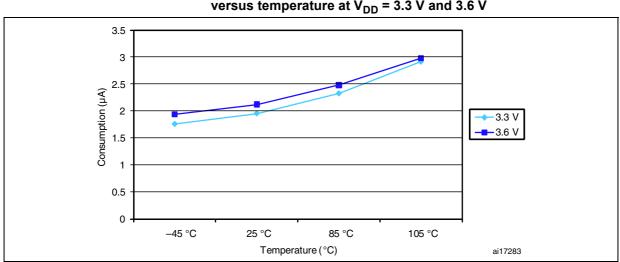

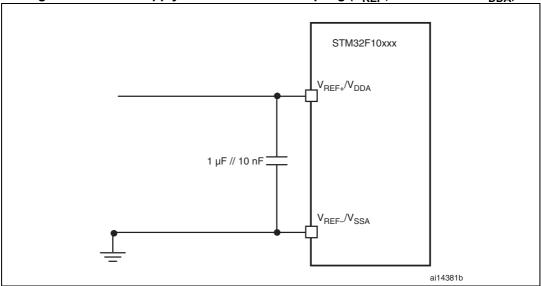

Figure 34. Power supply and reference decoupling ( $V_{REF+}$  not connected to  $V_{DDA}$ )

1.  $V_{\text{REF+}}$  is available on 100-pin packages and on TFBGA64 packages.  $V_{\text{REF-}}$  is available on 100-pin packages only.

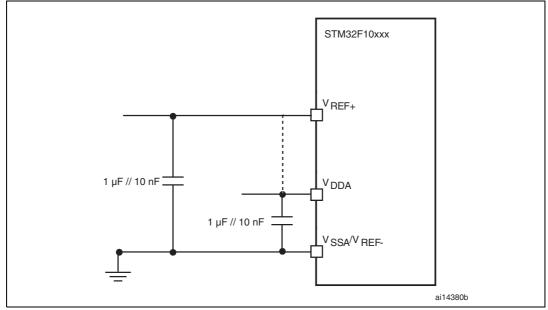

Figure 35. Power supply and reference decoupling ( $V_{REF+}$  connected to  $V_{DDA}$ )

1.  $V_{REF+}$  and  $V_{REF-}$  inputs are available only on 100-pin packages.

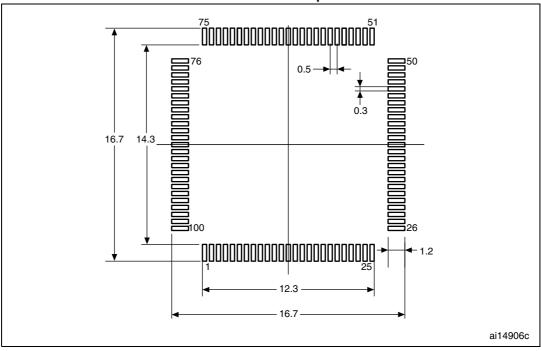

Figure 38. LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat recommended footprint

1. Dimensions are in millimeters.

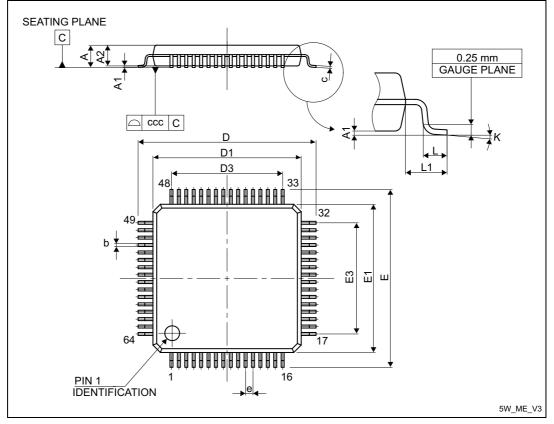

## 6.2 LQFP64 package information

Figure 40.LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package outline

1. Drawing is not in scale.

| Table 49. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package |

|---------------------------------------------------------------------|

| mechanical data                                                     |

| Current e l |       | millimeters |       | inches <sup>(1)</sup> |        |        |  |

|-------------|-------|-------------|-------|-----------------------|--------|--------|--|

| Symbol      | Min   | Тур         | Мах   | Min                   | Тур    | Мах    |  |

| А           | -     | -           | 1.600 | -                     | -      | 0.0630 |  |

| A1          | 0.050 | -           | 0.150 | 0.0020                | -      | 0.0059 |  |

| A2          | 1.350 | 1.400       | 1.450 | 0.0531                | 0.0551 | 0.0571 |  |

| b           | 0.170 | 0.220       | 0.270 | 0.0067                | 0.0087 | 0.0106 |  |

| С           | 0.090 | -           | 0.200 | 0.0035                | -      | 0.0079 |  |

| D           | -     | 12.000      | -     | -                     | 0.4724 | -      |  |

| D1          | -     | 10.000      | -     | -                     | 0.3937 | -      |  |

| D3          | -     | 7.500       | -     | -                     | 0.2953 | -      |  |

| E           | -     | 12.000      | -     | -                     | 0.4724 | -      |  |

| E1          | -     | 10.000      | -     | -                     | 0.3937 | -      |  |

| E3          | -     | 7.500       | -     | -                     | 0.2953 | -      |  |

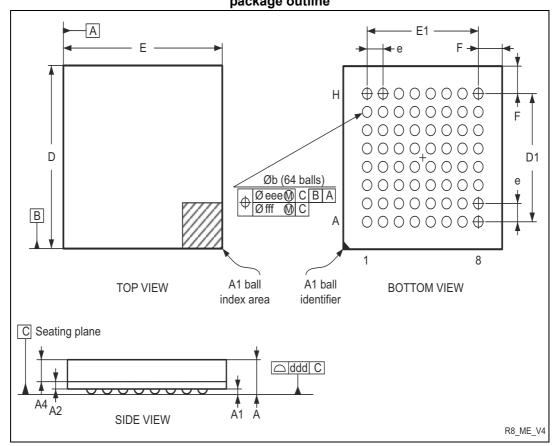

#### **Device marking for LQFP64**

The following figure gives an example of topside marking and pin 1 position identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 42. LQFP64 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

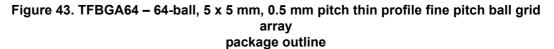

## 6.3 **TFBGA64** package information

<sup>1.</sup> Drawing is not to scale.

# Table 50. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ballgrid array package mechanical data

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol | Min   | Тур         | Max   | Min    | Тур                   | Max    |

| A      | -     | -           | 1.200 | -      | -                     | 0.0472 |

| A1     | 0.150 | -           | -     | 0.0059 | -                     | -      |

| A2     | -     | 0.200       | -     | -      | 0.0079                | -      |

| A4     | -     | -           | 0.600 | -      | -                     | 0.0236 |

| b      | 0.250 | 0.300       | 0.350 | 0.0098 | 0.0118                | 0.0138 |

| D      | 4.850 | 5.000       | 5.150 | 0.1909 | 0.1969                | 0.2028 |

| D1     | -     | 3.500       | -     | -      | 0.1378                | -      |

| E      | 4.850 | 5.000       | 5.150 | 0.1909 | 0.1969                | 0.2028 |

## 6.4 LQFP48 package information

SEATING PLANE A2 F 0.25 mm GAUGE PLANE ĸ D A1 D1 L1 D3 24 37 Œ b **CHE** <u>ш</u> ш Ē ----------£ 48 13 PIN 1 IDENTIFICATION 1 12 e 5B\_ME\_V2

Figure 46. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline

1. Drawing is not to scale.

| Table 52. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package |

|-------------------------------------------------------------------|

| mechanical data                                                   |

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|

|        | Min         | Тур   | Мах   | Min                   | Тур    | Max    |  |

| А      | -           | -     | 1.600 | -                     | -      | 0.0630 |  |

| A1     | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350       | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.170       | 0.220 | 0.270 | 0.0067                | 0.0087 | 0.0106 |  |

| С      | 0.090       | -     | 0.200 | 0.0035                | -      | 0.0079 |  |

| D      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |

| D1     | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |  |

| D3     | -           | 5.500 | -     | -                     | 0.2165 | -      |  |

| Е      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |

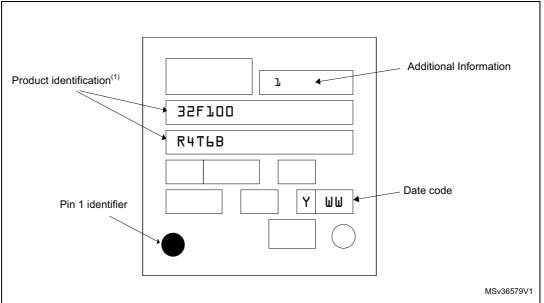

#### **Device marking for LQFP48**

The following figure gives an example of topside marking and pin 1 position identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 48. LQFP48 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

### 6.5 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 8: General operating conditions on page 34*.

The maximum chip-junction temperature,  $T_{\rm J}$  max, in degrees Celsius, may be calculated using the following equation:

$$T_J max = T_A max + (P_D max x \Theta_{JA})$$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

$\mathsf{P}_{\mathsf{I}/\mathsf{O}}$  max represents the maximum power dissipation on output pins where:

$$\mathsf{P}_{\mathsf{I}/\mathsf{O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol | Parameter                                                                   | Value | Unit |  |

|--------|-----------------------------------------------------------------------------|-------|------|--|

| QjA    | Thermal resistance junction-ambient<br>LQFP 100 - 14 × 14 mm / 0.5 mm pitch | 46    |      |  |

|        | Thermal resistance junction-ambient<br>LQFP 64 - 10 × 10 mm / 0.5 mm pitch  | 45    | °C/W |  |

|        | Thermal resistance junction-ambient<br>TFBGA64 - 5 × 5 mm / 0.5 mm pitch    | 65    |      |  |

|        | Thermal resistance junction-ambient<br>LQFP 48 - 7 × 7 mm / 0.5 mm pitch    | 55    |      |  |

#### Table 53. Package thermal characteristics

#### 6.5.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.

## 7 Ordering information scheme

#### Table 54. Ordering information scheme

| Example:                                                    | STM32 F 100 C 6 | Т | 6 | В | ххх |

|-------------------------------------------------------------|-----------------|---|---|---|-----|

| Device femily                                               |                 |   |   |   |     |

| Device family                                               |                 |   |   |   |     |

| STM32 = ARM-based 32-bit microcontroller                    |                 |   |   |   |     |

| Product type                                                |                 |   |   |   |     |

| F = General-purpose                                         |                 |   |   |   |     |

| Device subfamily                                            |                 |   |   |   |     |

| 100 = value line                                            |                 |   |   |   |     |

| Pin count                                                   |                 |   |   |   |     |

| C = 48 pins                                                 |                 |   |   |   |     |

| R = 64 pins                                                 |                 |   |   |   |     |

| V = 100 pins                                                |                 |   |   |   |     |

| Flash memory size                                           |                 |   |   |   |     |

| 4 = 16 Kbytes of Flash memory                               |                 |   |   |   |     |

| 6 = 32 Kbytes of Flash memory                               |                 |   |   |   |     |

| 8 = 64 Kbytes of Flash memory                               |                 |   |   |   |     |

| B = 128 Kbytes of Flash memory                              |                 |   |   |   |     |

| Package                                                     |                 |   |   |   |     |

| T = LQFP                                                    |                 |   |   |   |     |

| H = BGA                                                     |                 |   |   |   |     |

| Temperature range                                           |                 |   |   |   |     |

| 6 = Industrial temperature range, -40 to 85 °C              |                 |   |   |   |     |

| 7 = Industrial temperature range, $-40$ to $105 \text{ °C}$ |                 |   |   |   |     |

| Internal code                                               |                 |   |   |   |     |

| В                                                           |                 |   |   |   |     |

| Options                                                     |                 |   |   |   |     |

| •                                                           |                 |   |   |   | 1   |

xxx = programmed parts

TR = tape and real

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.