Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 24MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | DMA, PDR, POR, PVD, PWM, Temp Sensor, WDT                                |

| Number of I/O              | 37                                                                       |

| Program Memory Size        | 32KB (32K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 4K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                    |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 48-LQFP                                                                  |

| Supplier Device Package    | 48-LQFP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f100c6t6btr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 46.<br>Table 47. | DAC characteristics                                                     |

|------------------------|-------------------------------------------------------------------------|

| Table 48.              | LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat package             |

|                        | mechanical data                                                         |

| Table 49.              | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package               |

|                        | mechanical data                                                         |

| Table 50.              | TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball |

|                        | grid array package mechanical data                                      |

| Table 51.              | TFBGA64 recommended PCB design rules (0.5 mm pitch BGA)                 |

| Table 52.              | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package                 |

|                        | mechanical data                                                         |

| Table 53.              | Package thermal characteristics                                         |

| Table 54.              | Ordering information scheme                                             |

| Table 55.              | Document revision history                                               |

Their counters can be frozen in debug mode.

#### Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger generation. They can also be used as a generic 16-bit time base.

#### Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

#### Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

#### SysTick timer

This timer is dedicated for OS, but could also be used as a standard down counter. It features:

- A 24-bit down counter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0.

- Programmable clock source

## 2.2.16 I<sup>2</sup>C bus

The I<sup>2</sup>C bus interface can operate in multimaster and slave modes. It can support standard and fast modes.

It supports dual slave addressing (7-bit only) and both 7/10-bit addressing in master mode. A hardware CRC generation/verification is embedded. The interface can be served by DMA and it supports SM Bus 2.0/PM Bus.

## 2.2.17 Universal synchronous/asynchronous receiver transmitter (USART)

The STM32F100xx value line embeds three universal synchronous/asynchronous receiver transmitters (USART1, USART2 and USART3).

The available USART interfaces communicate at up to 3 Mbit/s. They provide hardware management of the CTS and RTS signals, they support IrDA SIR ENDEC, the multiprocessor communication mode, the single-wire half-duplex communication mode and have LIN Master/Slave capability.

The USART interfaces can be served by the DMA controller.

# 3 Pinouts and pin description

|   | 1                          | 2                    | 3       | 4       | 5       | 6 IFBGA                  | 7       | 8      |

|---|----------------------------|----------------------|---------|---------|---------|--------------------------|---------|--------|

| A | •<br>/PC14-,<br>0\&C32_lNT | , PC13-,<br>AMPER-RT | ( PB9 ) | ( PB4 ) | (PB3)   | (PA15)                   | (PA14)  | (PA13) |

| в | , PC15-,<br>OSC32_OUT      | VBAT)                | ( PB8 ) | воото   | (PD2)   | (PC11)                   | (PC10)  | (PA12) |

| C | OSC_IN                     | VSS_4                | ( PB7 ) | (PB5)   | (PC12)  | (PA10)                   | ( PA9 ) | (PA11) |

| D | OSC_OUT                    | VDD_4                | (PB6)   | ,VSS_3  | Vss_2   | ,VSS_1;                  | (PA8)   | (PC9)  |

| E | (NRST)                     | (PC1)                | (PC0)   | 'VDD_3' | VDD_2'  | ,<br>V <sub>DD_1</sub> , | (PC7)   | (PC8)  |

| F | (VSSA)                     | (PC2)                | (PA2 )  | (PA5)   | (PB0)   | (PC6)                    | (PB15)  | (PB14) |

| G | WREF+                      | PĄO-WKŲP             | ( PA3 ) | (PA6)   | (PB1)   | (PB2)                    | (PB10)  | (PB13) |

| н | V <sub>DDA</sub> ,         | ( PA1 )              | (PA4)   | PA7     | ( PC4 ) | (PC5)                    | (PB11)  | (PB12) |

|   |                            |                      |         |         |         |                          |         | Al1549 |

Figure 6. STM32F100xx value line TFBGA64 ballout

Table 4. Low & medium-density STM32F100xx pin definitions

|         | Pi     | ns      |        |                                |                     | 2)                                                                                                                                 |                     | Alternate functions <sup>(3)(4)</sup> |       |

|---------|--------|---------|--------|--------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------------------|-------|

| LQFP100 | LQFP64 | TFBGA64 | LQFP48 | Pin name                       | Type <sup>(1)</sup> | TAbe<br>(1)<br>end<br>(1)<br>end<br>(1)<br>end<br>(1)<br>end<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1) |                     | Default                               | Remap |

| 1       | -      | -       | -      | PE2                            | I/O                 | FT                                                                                                                                 | PE2                 | TRACECLK                              | -     |

| 2       | -      | -       | -      | PE3                            | I/O                 | FT                                                                                                                                 | PE3                 | TRACED0                               | -     |

| 3       | -      | -       | -      | PE4                            | I/O                 | FT                                                                                                                                 | PE4                 | TRACED1                               | -     |

| 4       | -      | -       | -      | PE5                            | I/O                 | FT                                                                                                                                 | PE5                 | TRACED2                               | -     |

| 5       | -      | -       | -      | PE6                            | I/O                 | FT                                                                                                                                 | PE6                 | TRACED3                               | -     |

| 6       | 1      | B2      | 1      | V <sub>BAT</sub>               | S                   | -                                                                                                                                  | V <sub>BAT</sub>    | -                                     | -     |

| 7       | 2      | A2      | 2      | PC13-TAMPER-RTC <sup>(5)</sup> | I/O                 | -                                                                                                                                  | PC13 <sup>(6)</sup> | TAMPER-RTC                            | -     |

| 8       | 3      | A1      | 3      | PC14-OSC32_IN <sup>(5)</sup>   | I/O                 | -                                                                                                                                  | PC14 <sup>(6)</sup> | OSC32_IN                              | -     |

1. I = input, O = output, S = supply, HiZ= high impedance.

- Function availability depends on the chosen device. For devices having reduced peripheral counts, it is always the lower number of peripherals that is included. For example, if a device has only one SPI, two USARTs and two timers, they will be called SPI1, USART1 & USART2 and TIM2 & TIM 3, respectively. Refer to Table 2 on page 11.

- 4. If several peripherals share the same I/O pin, to avoid conflict between these alternate functions only one peripheral should be enabled at a time through the peripheral clock enable bit (in the corresponding RCC peripheral clock enable register).

- PC13, PC14 and PC15 are supplied through the power switch and since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 in output mode is restricted: the speed should not exceed 2 MHz with a maximum load of 30 pF and these IOs must *not* be used as a current source (e.g. to drive an LED).

- 6. Main function after the first backup domain power-up. Later on, it depends on the contents of the Backup registers even after reset (because these registers are not reset by the main reset). For details on how to manage these IOs, refer to the Battery backup domain and BKP register description sections in the STM32F10xxx reference manual, available from the STMicroelectronics website: www.st.com.

- 7. The pins number 2 and 3 in the VFQFPN36 package, 5 and 6 in the LQFP48 and LQFP64 packages and C1 and C2 in the TFBGA64 package are configured as OSC\_IN/OSC\_OUT after reset, however the functionality of PD0 and PD1 can be remapped by software on these pins. For more details, refer to the Alternate function I/O and debug configuration section in the STM32F10xxx reference manual.

- 8. Unlike in the LQFP64 package, there is no PC3 in the TFBGA64 package. The V<sub>REF+</sub> functionality is provided instead.

- 9. I2C2 is not present on low-density value line devices.

- 10. SPI2 is not present on low-density value line devices.

- 11. TIM4 is not present on low-density value line devices.

- 12. This alternate function can be remapped by software to some other port pins (if available on the used package). For more details, refer to the Alternate function I/O and debug configuration section in the STM32F10xxx reference manual, available from the STMicroelectronics website: www.st.com.

<sup>2.</sup> FT= 5 V tolerant.

| Symbol         | Parameter                                                  | Parameter Conditions                 |     | Max | Unit |  |

|----------------|------------------------------------------------------------|--------------------------------------|-----|-----|------|--|

|                |                                                            | LQFP100                              | -   | 434 |      |  |

| р              | Power dissipation at $T_A =$ 85 °C for suffix 6 or $T_A =$ | LQFP64                               | -   | 444 | m\\/ |  |

| P <sub>D</sub> | 105 °C for suffix $7^{(2)}$                                | TFBGA64                              | -   | 308 | mW   |  |

|                |                                                            | LQFP48                               | -   | 363 |      |  |

|                | Ambient temperature for 6                                  | Maximum power dissipation            | -40 | 85  | °C   |  |

| Та             | suffix version                                             | Low power dissipation <sup>(3)</sup> | -40 | 105 | C    |  |

| IA             | Ambient temperature for 7 suffix version                   | Maximum power dissipation            | -40 | 105 | °C   |  |

|                |                                                            | Low power dissipation <sup>(3)</sup> | -40 | 125 | C    |  |

| TJ             | Junction temperature range                                 | 6 suffix version                     | -40 | 105 | С.   |  |

|                | Sunction temperature range                                 | 7 suffix version                     | -40 | 125 | 0    |  |

Table 8. General operating conditions (continued)

1. When the ADC is used, refer to *Table 42: ADC characteristics*.

2. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_J$ max (see *Table 6.5: Thermal characteristics on page 89*).

In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>J</sub>max (see Table 6.5: Thermal characteristics on page 89).

### 5.3.2 Operating conditions at power-up / power-down

Subject to general operating conditions for T<sub>A</sub>.

| Table 9. Operating | conditions at power-up | / power-down |

|--------------------|------------------------|--------------|

|--------------------|------------------------|--------------|

| Symbol           | Parameter                      | Min | Max | Unit  |

|------------------|--------------------------------|-----|-----|-------|

| t <sub>VDD</sub> | V <sub>DD</sub> rise time rate | 0   | ~   | us/V  |

|                  | V <sub>DD</sub> fall time rate | 20  | 8   | μ5/ V |

#### 5.3.3 Embedded reset and power control block characteristics

The parameters given in *Table 10* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

Note: It is recommended to power  $V_{DD}$  and  $V_{DDA}$  from the same source. A maximum difference of 300 mV between  $V_{DD}$  and  $V_{DDA}$  can be tolerated during power-up and operation.

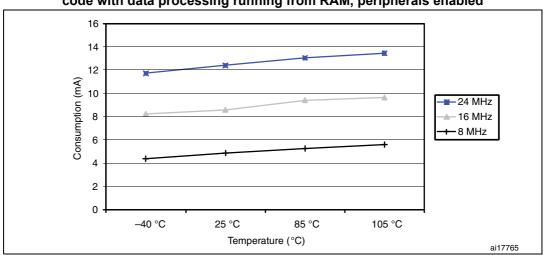

Figure 12. Maximum current consumption in Run mode versus frequency (at 3.6 V) - code with data processing running from RAM, peripherals enabled

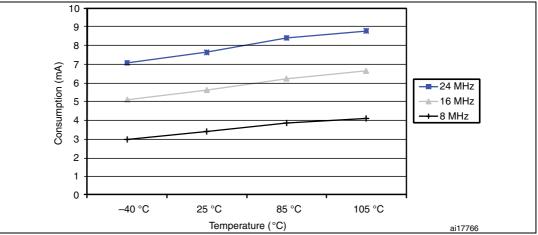

Figure 13. Maximum current consumption in Run mode versus frequency (at 3.6 V) - code with data processing running from RAM, peripherals disabled

Table 14. Maximum current consumption in Sleep mode, code running from Flash or RAM

| Symbol | Deremeter                       | Conditions                                            | £                 | Ма                     | Unit                    |      |

|--------|---------------------------------|-------------------------------------------------------|-------------------|------------------------|-------------------------|------|

| Symbol | Parameter                       |                                                       | f <sub>HCLK</sub> | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |

|        | Supply current<br>in Sleep mode | External clock <sup>(2)</sup> all peripherals enabled | 24 MHz            | 9.6                    | 10                      |      |

|        |                                 |                                                       | 16 MHz            | 7.1                    | 7.5                     | ]    |

|        |                                 |                                                       | 8 MHz             | 4.5                    | 4.8                     | m 4  |

| IDD    |                                 |                                                       | 24 MHz            | 3.8                    | 4                       | mA   |

|        |                                 |                                                       | 16 MHz            | 3.3                    | 3.5                     |      |

|        |                                 |                                                       | 8 MHz             | 2.7                    | 3                       |      |

1. Guaranteed by characterization, tested in production at  $V_{DD}$  max and  $f_{HCLK}$  max with peripherals enabled.

2. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

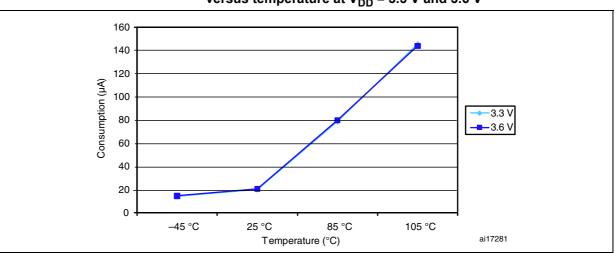

Figure 15. Typical current consumption in Stop mode with regulator in Run mode versus temperature at  $V_{DD}$  = 3.3 V and 3.6 V

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 22*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

Note: For  $C_{L1}$  and  $C_{L2}$  it is recommended to use high-quality ceramic capacitors in the 5 pF to 15 pF range selected to match the requirements of the crystal or resonator.  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ .

Load capacitance  $C_L$  has the following formula:  $C_L = C_{L1} \times C_{L2} / (C_{L1} + C_{L2}) + C_{stray}$  where  $C_{stray}$  is the pin capacitance and board or trace PCB-related capacitance. Typically, it is between 2 pF and 7 pF.

For further details, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

**Caution:** To avoid exceeding the maximum value of  $C_{L1}$  and  $C_{L2}$  (15 pF) it is strongly recommended to use a resonator with a load capacitance  $C_L \le 7$  pF. Never use a resonator with a load capacitance of 12.5 pF.

**Example:** if you choose a resonator with a load capacitance of  $C_L$  = 6 pF, and  $C_{stray}$  = 2 pF, then  $C_{L1}$  =  $C_{L2}$  = 8 pF.

| Symbol                              | Parameter                                                                                     | Conditions             |                                        | Min | Тур | Мах | Unit |

|-------------------------------------|-----------------------------------------------------------------------------------------------|------------------------|----------------------------------------|-----|-----|-----|------|

| R <sub>F</sub>                      | Feedback resistor                                                                             |                        | -                                      | -   | 5   | -   | MΩ   |

| $C_{L1} C_{L2}^{(2)}$               | Recommended load capacitance versus equivalent serial resistance of the crystal $(R_S)^{(3)}$ | R <sub>S</sub> = 30 KΩ |                                        | -   | -   | 15  | pF   |

| l <sub>2</sub>                      | LSE driving current                                                                           | V <sub>DD</sub> = 3    | .3 V V <sub>IN</sub> = V <sub>SS</sub> | -   | -   | 1.4 | μA   |

| 9 <sub>m</sub>                      | Oscillator transconductance                                                                   | -                      |                                        | 5   | -   | -   | µA/V |

|                                     |                                                                                               |                        | T <sub>A</sub> = 50 °C                 | -   | 1.5 | -   |      |

|                                     |                                                                                               |                        | T <sub>A</sub> = 25 °C                 | -   | 2.5 | -   |      |

|                                     |                                                                                               |                        | T <sub>A</sub> = 10 °C                 | -   | 4   | -   |      |

| t (4)                               |                                                                                               | V <sub>DD</sub> is     | T <sub>A</sub> = 0 °C                  | -   | 6   | -   |      |

| t <sub>SU(LSE)</sub> <sup>(4)</sup> | Startup time                                                                                  | stabilized             | T <sub>A</sub> = -10 °C                | -   | 10  | -   | S    |

|                                     |                                                                                               |                        | T <sub>A</sub> = -20 °C                | -   | 17  | -   |      |

|                                     |                                                                                               |                        | T <sub>A</sub> = -30 °C                | -   | 32  | -   |      |

|                                     |                                                                                               |                        | T <sub>A</sub> = -40 °C                | -   | 60  | -   |      |

Table 22. LSE oscillator characteristics  $(f_{LSE} = 32.768 \text{ kHz})^{(1)}$

1. Guaranteed by characterization results.

2. Refer to the note and caution paragraphs above the table.

- The oscillator selection can be optimized in terms of supply current using an high quality resonator with small R<sub>S</sub> value for example MSIV-TIN32.768 kHz. Refer to crystal manufacturer for more details

- 4. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

#### Low-speed internal (LSI) RC oscillator

| Table 24. LSI oso | illator characteristics <sup>(1)</sup> | ) |

|-------------------|----------------------------------------|---|

|-------------------|----------------------------------------|---|

| Symbol                              | Parameter                                          | Min | Тур  | Мах | Unit |

|-------------------------------------|----------------------------------------------------|-----|------|-----|------|

| f <sub>LSI</sub>                    | Frequency                                          | 30  | 40   | 60  | kHz  |

| $\Delta f_{LSI(T)}$                 | Temperature-related frequency drift <sup>(2)</sup> | -9  | -    | 9   | %    |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time                        | -   | -    | 85  | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption                   | -   | 0.65 | 1.2 | μA   |

1.  $V_{DD}$  = 3 V,  $T_A$  = -40 to 105 °C °C unless otherwise specified.

2. Guaranteed by characterization results.

3. Guaranteed by design.

#### Wakeup time from low-power mode

The wakeup times given in *Table 25* are measured on a wakeup phase with an 8-MHz HSI RC oscillator. The clock source used to wake up the device depends from the current operating mode:

- Stop or Standby mode: the clock source is the RC oscillator

- Sleep mode: the clock source is the clock that was set before entering Sleep mode.

All timings are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

| Symbol                              | Parameter                                           | Тур | Unit |

|-------------------------------------|-----------------------------------------------------|-----|------|

| t <sub>WUSLEEP</sub> <sup>(1)</sup> | Wakeup from Sleep mode                              | 1.8 | μs   |

| t <sub>WUSTOP</sub> <sup>(1)</sup>  | Wakeup from Stop mode (regulator in run mode)       | 3.6 |      |

| <sup>I</sup> WUSTOP <sup>(1)</sup>  | Wakeup from Stop mode (regulator in low-power mode) | 5.4 | μs   |

| t <sub>WUSTDBY</sub> <sup>(1)</sup> | Wakeup from Standby mode                            | 50  | μs   |

Table 25. Low-power mode wakeup timings

1. The wakeup times are measured from the wakeup event to the point at which the user application code reads the first instruction.

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device is monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol | Parameter                   | Conditions                                                                                                                  | Monitored<br>frequency band | Max vs. [f <sub>HSE</sub> /f <sub>HCLK</sub> ]<br>8/24 MHz | Unit |

|--------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------------------------------------------|------|

|        |                             | eak level $V_{DD} = 3.6 \text{ V}, \text{ T}_{A} = 25^{\circ}\text{C},$<br>LQFP100 package<br>compliant with SAE<br>J1752/3 | 0.1 MHz to 30 MHz           | 9                                                          |      |

| c c    | Dook lovel                  |                                                                                                                             | 30 MHz to 130 MHz           | 16                                                         | dBµV |

| SEMI   | S <sub>EMI</sub> Peak level |                                                                                                                             | 130 MHz to 1GHz             | 19                                                         |      |

|        |                             |                                                                                                                             | SAE EMI Level               | 4                                                          | -    |

## 5.3.11 Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

| Table 31. | ESD | absolute | maximum | ratings |

|-----------|-----|----------|---------|---------|

|           |     |          |         |         |

| Symbol                | Ratings                                               | Conditions                                           | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | $T_A = +25 \ ^{\circ}C$<br>conforming to JESD22-A114 | 2     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | $T_A = +25 \text{ °C}$<br>conforming to JESD22-C101  | Ш     | 500                             | v    |

1. Based on characterization results, not tested in production.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD78 IC latch-up standard.

| Symbol Parameter |                       | Conditions                           | Class      |  |

|------------------|-----------------------|--------------------------------------|------------|--|

| LU               | Static latch-up class | $T_A = +105$ °C conforming to JESD78 | II level A |  |

#### Table 32. Electrical sensitivities

## 5.3.13 I/O port characteristics

#### General input/output characteristics

Unless otherwise specified, the parameters given in *Table 34* are derived from tests performed under the conditions summarized in *Table 8*. All I/Os are CMOS and TTL compliant.

| Symbol                                | Parameter                                                | Conditions                                                         | Min                                | Тур | Мах                                | Unit |

|---------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------|------------------------------------|-----|------------------------------------|------|

| M                                     | Standard I/O input low level voltage                     |                                                                    | -0.3                               | -   | 0.28*(V <sub>DD</sub> -2 V)+0.8 V  |      |

| V <sub>IL</sub>                       | I/O FT <sup>(1)</sup> input low level voltage            | -                                                                  | -0.3                               | -   | 0.32*(V <sub>DD</sub> -2 V)+0.75 V |      |

|                                       | Standard I/O input<br>high level voltage                 |                                                                    | 0.41*(V <sub>DD</sub> -2 V) +1.3 V | -   | V <sub>DD</sub> +0.3               | V    |

| V <sub>IH</sub>                       | I/O FT <sup>(1)</sup> input high                         | $V_{DD} > 2 V$                                                     | 0.42*(\/2\+1.\/                    |     | 5.5                                | _    |

|                                       | level voltage                                            | V <sub>DD</sub> ≤2 V                                               | 0.42*(V <sub>DD</sub> –2)+1 V      | -   | 5.2                                |      |

| V <sub>hys</sub> Standard I/O Schmitt |                                                          | -                                                                  | 200                                | -   | -                                  | mV   |

| Tiy5                                  | I/O FT Schmitt trigger voltage hysteresis <sup>(2)</sup> |                                                                    | 5% V <sub>DD</sub> <sup>(3)</sup>  | -   | -                                  | mV   |

| 1                                     | Input leakage                                            | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>Standard I/Os | -                                  | -   | ±1                                 |      |

| l <sub>lkg</sub>                      | urrent <sup>(4)</sup>                                    | V <sub>IN</sub> = 5 V<br>I/O FT                                    |                                    | 3   | - μΑ                               |      |

| R <sub>PU</sub>                       | Weak pull-up<br>equivalent resistor <sup>(5)</sup>       | $V_{IN} = V_{SS}$                                                  | 30                                 | 40  | 50                                 | kΩ   |

| R <sub>PD</sub>                       | Weak pull-down<br>equivalent resistor <sup>(5)</sup>     | $V_{IN} = V_{DD}$                                                  | 30                                 | 40  | 50                                 | kΩ   |

| CIO                                   | I/O pin capacitance                                      | -                                                                  | -                                  | 5   | -                                  | pF   |

1. FT = 5V tolerant. To sustain a voltage higher than V<sub>DD</sub>+0.3 the internal pull-up/pull-down resistors must be disabled.

2. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by design.

- 3. With a minimum of 100 mV.

- 4. Leakage could be higher than max. if negative current is injected on adjacent pins.

- 5. Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimum (~10% order).

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 22* and *Figure 23* for standard I/Os, and in *Figure 24* and *Figure 25* for 5 V tolerant I/Os.

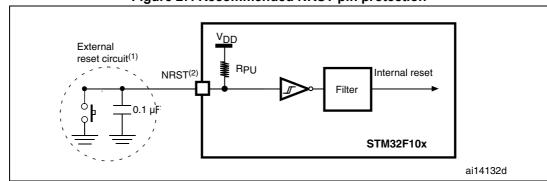

Figure 27. Recommended NRST pin protection

1. The reset network protects the device against parasitic resets.

The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 37. Otherwise the reset will not be taken into account by the device.

#### 5.3.15 TIMx characteristics

The parameters given in Table 38 are guaranteed by design.

Refer to Section 5.3.12: I/O current injection characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                           | Conditions <sup>(1)</sup>     | Min  | Max                     | Unit                 |  |  |

|------------------------|-------------------------------------|-------------------------------|------|-------------------------|----------------------|--|--|

| t mu                   | Timer resolution time               | -                             | 1    | -                       | t <sub>TIMxCLK</sub> |  |  |

| t <sub>res(TIM)</sub>  |                                     | f <sub>TIMxCLK</sub> = 24 MHz | 41.7 | -                       | ns                   |  |  |

| f                      | Timer external clock                |                               | 0    | f <sub>TIMxCLK</sub> /2 | MHz                  |  |  |

| f <sub>EXT</sub>       | frequency on CHx <sup>(2)</sup>     | f <sub>TIMxCLK</sub> = 24 MHz | 0    | 12                      | MHz                  |  |  |

| Res <sub>TIM</sub>     | Timer resolution                    | -                             | -    | 16                      | bit                  |  |  |

|                        | 16-bit counter clock period         | -                             | 1    | 65536                   | t <sub>TIMxCLK</sub> |  |  |

| <sup>t</sup> COUNTER   | when the internal clock is selected | f <sub>TIMxCLK</sub> = 24 MHz | -    | 2730                    | μs                   |  |  |

| t <sub>MAX_COUNT</sub> | Maximum possible count              | -                             | -    | 65536 × 65536           | t <sub>TIMxCLK</sub> |  |  |

|                        |                                     | f <sub>TIMxCLK</sub> = 24 MHz | -    | 178                     | s                    |  |  |

Table 38. TIMx characteristics

1. TIMx is used as a general term to refer to the TIM1, TIM2, TIM3, TIM4, TIM15, TIM16 and TIM17 timers.

2. CHx is used as a general term to refer to CH1 to CH4 for TIM1, TIM2, TIM3 and TIM4, to the CH1 to CH2 for TIM15, and to CH1 for TIM16 and TIM17.

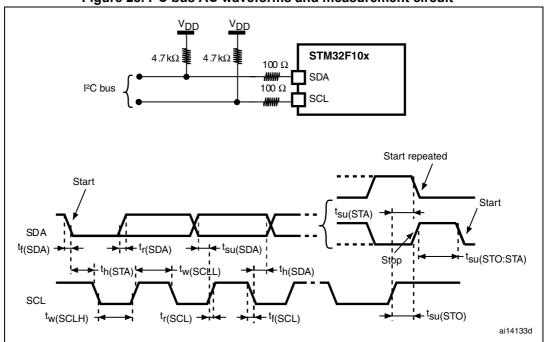

Figure 28. I<sup>2</sup>C bus AC waveforms and measurement circuit<sup>(1)</sup>

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}.}$

| £ ((-11->(3)                          | I2C_CCR value           |

|---------------------------------------|-------------------------|

| f <sub>SCL</sub> (kHz) <sup>(3)</sup> | R <sub>P</sub> = 4.7 kΩ |

| 400                                   | 0x8011                  |

| 300                                   | 0x8016                  |

| 200                                   | 0x8021                  |

| 100                                   | 0x0064                  |

| 50                                    | 0x00C8                  |

| 20                                    | 0x01F4                  |

## Table 40. SCL frequency $(f_{PCLK1} = 24 \text{ MHz}, V_{DD} = 3.3 \text{ V})^{(1)(2)}$

1.  $R_P$  = External pull-up resistance,  $f_{SCL}$  = I<sup>2</sup>C speed,

For speeds around 400 kHz, the tolerance on the achieved speed is of ±2%. For other speed ranges, the tolerance on the achieved speed ±1%. These variations depend on the accuracy of the external components used to design the application.

3. Guaranteed by design.

## 5.3.19 Temperature sensor characteristics

| Symbol                                | Parameter                                      |      | Тур  | Max       | Unit  |

|---------------------------------------|------------------------------------------------|------|------|-----------|-------|

| T <sub>L</sub> <sup>(1)</sup>         | V <sub>SENSE</sub> linearity with temperature  | -    | ±1   | <u>+2</u> | °C    |

| Avg_Slope <sup>(1)</sup>              | Average slope                                  | 4.0  | 4.3  | 4.6       | mV/°C |

| V <sub>25</sub> <sup>(1)</sup>        | Voltage at 25°C                                | 1.32 | 1.41 | 1.50      | V     |

| t <sub>START</sub> <sup>(2)</sup>     | Startup time                                   | 4    | -    | 10        | μs    |

| T <sub>S_temp</sub> <sup>(3)(2)</sup> | ADC sampling time when reading the temperature | -    | -    | 17.1      | μs    |

#### Table 47. TS characteristics

1. Guaranteed by characterization results.

2. Guaranteed by design.

3. Shortest sampling time can be determined in the application by multiple iterations.

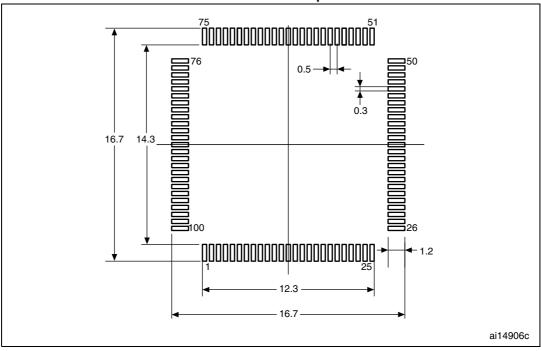

Figure 38. LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat recommended footprint

1. Dimensions are in millimeters.

| Ok.a.l | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур   | Мах   | Min                   | Тур    | Max    |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| К      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |

| CCC    | -           | -     | 0.080 | -                     | -      | 0.0031 |

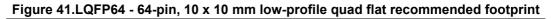

# Table 49. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat packagemechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are in millimeters.

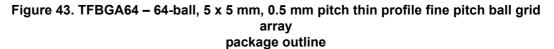

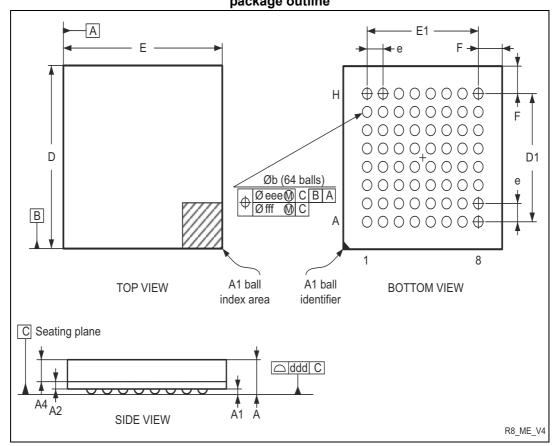

## 6.3 **TFBGA64** package information

<sup>1.</sup> Drawing is not to scale.

# Table 50. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ballgrid array package mechanical data

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|

| Symbol | Min         | Тур   | Max   | Min                   | Тур    | Max    |  |

| A      | -           | -     | 1.200 | -                     | -      | 0.0472 |  |

| A1     | 0.150       | -     | -     | 0.0059                | -      | -      |  |

| A2     | -           | 0.200 | -     | -                     | 0.0079 | -      |  |

| A4     | -           | -     | 0.600 | -                     | -      | 0.0236 |  |

| b      | 0.250       | 0.300 | 0.350 | 0.0098                | 0.0118 | 0.0138 |  |

| D      | 4.850       | 5.000 | 5.150 | 0.1909                | 0.1969 | 0.2028 |  |

| D1     | -           | 3.500 | -     | -                     | 0.1378 | -      |  |

| E      | 4.850       | 5.000 | 5.150 | 0.1909                | 0.1969 | 0.2028 |  |

# 6.4 LQFP48 package information

SEATING PLANE A2 F 0.25 mm GAUGE PLANE ĸ D A1 D1 L1 D3 24 37 Œ b **CHE** <u>ш</u> ш Ē ----------£ 48 13 PIN 1 IDENTIFICATION 1 12 e 5B\_ME\_V2

Figure 46. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline

1. Drawing is not to scale.

| Table 52. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package |  |  |  |  |  |  |

|-------------------------------------------------------------------|--|--|--|--|--|--|

| mechanical data                                                   |  |  |  |  |  |  |

|        | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур   | Мах   | Min                   | Тур    | Max    |

| А      | -           | -     | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220 | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090       | -     | 0.200 | 0.0035                | -      | 0.0079 |

| D      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |

| D1     | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |

| D3     | -           | 5.500 | -     | -                     | 0.2165 | -      |

| Е      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |

## 6.5 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 8: General operating conditions on page 34*.

The maximum chip-junction temperature,  $T_{\rm J}$  max, in degrees Celsius, may be calculated using the following equation:

$$T_J max = T_A max + (P_D max x \Theta_{JA})$$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

$\mathsf{P}_{\mathsf{I}/\mathsf{O}}$  max represents the maximum power dissipation on output pins where:

$$\mathsf{P}_{\mathsf{I}/\mathsf{O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol          | Parameter                                                                   | Value | Unit |  |

|-----------------|-----------------------------------------------------------------------------|-------|------|--|

| Q <sub>JA</sub> | Thermal resistance junction-ambient<br>LQFP 100 - 14 × 14 mm / 0.5 mm pitch | 46    |      |  |

|                 | Thermal resistance junction-ambient<br>LQFP 64 - 10 × 10 mm / 0.5 mm pitch  | 45    | °C/W |  |

|                 | Thermal resistance junction-ambient<br>TFBGA64 - 5 × 5 mm / 0.5 mm pitch    | 65    |      |  |

|                 | Thermal resistance junction-ambient<br>LQFP 48 - 7 × 7 mm / 0.5 mm pitch    | 55    |      |  |

#### Table 53. Package thermal characteristics

#### 6.5.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.