Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | ARM® Cortex®-M3                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 24MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | DMA, PDR, POR, PVD, PWM, Temp Sensor, WDT                                |

| Number of I/O              | 37                                                                       |

| Program Memory Size        | 64KB (64K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                    |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

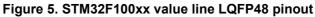

| Package / Case             | 48-LQFP                                                                  |

| Supplier Device Package    | 48-LQFP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f100c8t7btr |

| STM32F100x4. STM32F100x6. STM32F100x | O CTMAAACAAAA |

|--------------------------------------|---------------|

| 3 IVI3/F100X4                        | X SINS/FIDUXE |

| <b>^</b> - | 4   | 4   |

|------------|-----|-----|

| CO         | nte | nts |

|   | 6.5  | Therma    | al characteristics                      | . 89 |

|---|------|-----------|-----------------------------------------|------|

|   |      | 6.5.1     | Reference document                      | . 89 |

|   |      | 6.5.2     | Selecting the product temperature range | . 90 |

| 7 | Orde | ering inf | formation scheme                        | . 92 |

| 8 | Rovi | sion his  | etory                                   | 93   |

**5**//

# List of tables

| Table 1.  | Device summary                                                            | 1    |

|-----------|---------------------------------------------------------------------------|------|

| Table 2.  | STM32F100xx features and peripheral counts                                |      |

| Table 3.  | Timer feature comparison                                                  |      |

| Table 4.  | Low & medium-density STM32F100xx pin definitions                          |      |

| Table 5.  | Voltage characteristics                                                   | . 33 |

| Table 6.  | Current characteristics                                                   |      |

| Table 7.  | Thermal characteristics                                                   | . 34 |

| Table 8.  | General operating conditions                                              | . 34 |

| Table 9.  | Operating conditions at power-up / power-down                             |      |

| Table 10. | Embedded reset and power control block characteristics                    |      |

| Table 11. | Embedded internal reference voltage                                       |      |

| Table 12. | Maximum current consumption in Run mode, code with data processing        |      |

|           | running from Flash                                                        | . 38 |

| Table 13. | Maximum current consumption in Run mode, code with data processing        |      |

|           | running from RAM                                                          | . 38 |

| Table 14. | Maximum current consumption in Sleep mode, code running from Flash or RAM | . 39 |

| Table 15. | Typical and maximum current consumptions in Stop and Standby modes        |      |

| Table 16. | Typical current consumption in Run mode, code with data processing        |      |

|           | running from Flash                                                        | . 43 |

| Table 17. | Typical current consumption in Sleep mode, code running from Flash or RAM |      |

| Table 18. | Peripheral current consumption                                            |      |

| Table 19. | High-speed external user clock characteristics                            |      |

| Table 20. | Low-speed external user clock characteristics                             |      |

| Table 21. | HSE 4-24 MHz oscillator characteristics                                   |      |

| Table 22. | LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz)            | . 49 |

| Table 23. | HSI oscillator characteristics                                            |      |

| Table 24. | LSI oscillator characteristics                                            |      |

| Table 25. | Low-power mode wakeup timings                                             | . 51 |

| Table 26. | PLL characteristics                                                       |      |

| Table 27. | Flash memory characteristics                                              | . 53 |

| Table 28. | Flash memory endurance and data retention                                 |      |

| Table 29. | EMS characteristics                                                       |      |

| Table 30. | EMI characteristics                                                       | . 55 |

| Table 31. | ESD absolute maximum ratings                                              | . 55 |

| Table 32. | Electrical sensitivities                                                  |      |

| Table 33. | I/O current injection susceptibility                                      | . 56 |

| Table 34. | I/O static characteristics                                                |      |

| Table 35. | Output voltage characteristics                                            | . 60 |

| Table 36. | I/O AC characteristics                                                    | . 61 |

| Table 37. | NRST pin characteristics                                                  | . 62 |

| Table 38. | TIMx characteristics                                                      | . 63 |

| Table 39. | I <sup>2</sup> C characteristics                                          | . 64 |

| Table 40. | SCL frequency (f <sub>PCLK1</sub> = 24 MHz, V <sub>DD</sub> = 3.3 V)      | . 65 |

| Table 41. | SPI characteristics                                                       |      |

| Table 42. | ADC characteristics                                                       |      |

| Table 43. | R <sub>AIN</sub> max for f <sub>ADC</sub> = 12 MHz                        | . 70 |

| Table 44. | ADC accuracy - limited test conditions                                    | . 70 |

| Table 45. | ADC accuracy                                                              |      |

# List of tables

| Table 46. | DAC characteristics                                                     | 73 |

|-----------|-------------------------------------------------------------------------|----|

| Table 47. | TS characteristics                                                      | 75 |

| Table 48. | LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat package             |    |

|           | mechanical data                                                         | 77 |

| Table 49. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package               |    |

|           | mechanical data                                                         | 80 |

| Table 50. | TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball |    |

|           | grid array package mechanical data                                      | 83 |

| Table 51. | TFBGA64 recommended PCB design rules (0.5 mm pitch BGA)                 | 84 |

| Table 52. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package                 |    |

|           | mechanical data                                                         | 86 |

| Table 53. | Package thermal characteristics                                         |    |

| Table 54. | Ordering information scheme                                             | 92 |

| Table 55. | Document revision history                                               |    |

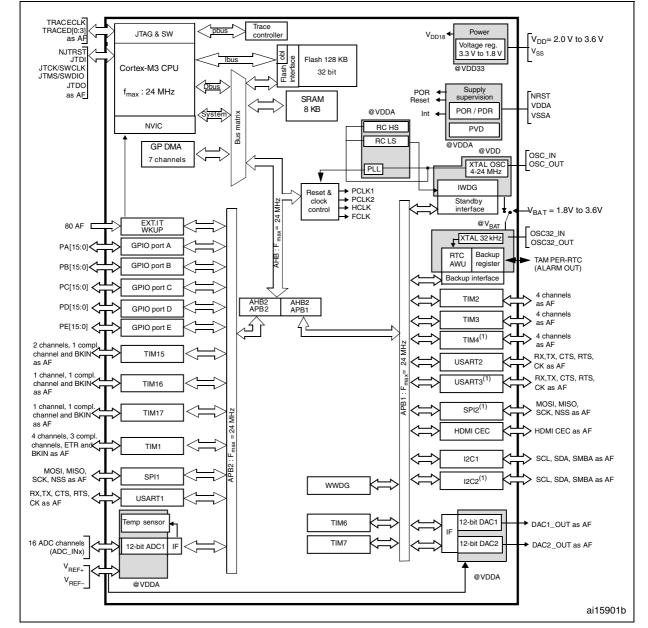

Figure 1. STM32F100xx value line block diagram

- 1. Peripherals not present in low-density value line devices.

- 2. AF = alternate function on I/O port pin.

- 3.  $T_A = -40$  °C to +85 °C (junction temperature up to 105 °C) or  $T_A = -40$  °C to +105 °C (junction temperature up to 125 °C).

57/

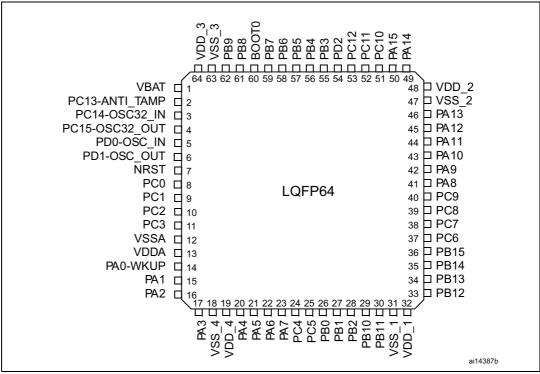

Figure 4. STM32F100xx value line LQFP64 pinout

1 8 PC14-(PC13-) OSC32\_INTAMPER RTC PB9 PB3 PA13 PB4 PA15 PA14 PC15-PB8 ВООТО PD2 (PC11) (PC10) В PA12 VBAT, OSC32\_OUT (PC12) PB7 ; PB5 (PA10) PA9 С PA11 OSC\_OUT PB6 PA8 PC9 D V<sub>SS\_3</sub> VSS\_2 VSS\_1, V<sub>DD\_4</sub> NRST Ε PC1 PC0 V<sub>DD\_1</sub>, PC7 PC8  $^{V}_{DD_3}$  $V_{DD_2}$ (PB15) PC6; PA5 PC2 PA2 ' PB0 ; 'PB14; F ( PB1 ) PB2 VREF+ PÁ0-WKŲP РАЗ PA6 G PB10 (PB13) Н PC4 PC5 PB11 (PB12) VDDA. Al15494

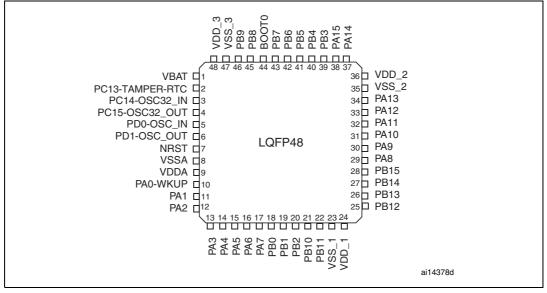

Figure 6. STM32F100xx value line TFBGA64 ballout

Table 4. Low & medium-density STM32F100xx pin definitions

|         | Pi     | ns      |        |                                |                     | 2)                                       |                     | Alternate function | s <sup>(3)(4)</sup> |

|---------|--------|---------|--------|--------------------------------|---------------------|------------------------------------------|---------------------|--------------------|---------------------|

| LQFP100 | LQFP64 | TFBGA64 | LQFP48 | Pin name                       | Type <sup>(1)</sup> | Type (1) Main function (3) (after reset) |                     | Default            | Remap               |

| 1       | -      | -       | -      | PE2                            | I/O                 | FT                                       | PE2                 | TRACECLK           | -                   |

| 2       | -      | -       | -      | PE3                            | I/O                 | FT                                       | PE3                 | TRACED0            | -                   |

| 3       | -      | -       | 1      | PE4                            | I/O                 | FT                                       | PE4                 | TRACED1            | -                   |

| 4       | -      | -       | 1      | PE5                            | I/O                 | FT                                       | PE5                 | TRACED2            | -                   |

| 5       | -      | -       | -      | PE6                            | I/O                 | FT                                       | PE6                 | TRACED3            | -                   |

| 6       | 1      | B2      | 1      | V <sub>BAT</sub>               | S                   | -                                        | $V_{BAT}$           | -                  | -                   |

| 7       | 2      | A2      | 2      | PC13-TAMPER-RTC <sup>(5)</sup> | I/O                 | -                                        | PC13 <sup>(6)</sup> | TAMPER-RTC         | -                   |

| 8       | 3      | A1      | 3      | PC14-OSC32_IN <sup>(5)</sup>   | I/O                 | -                                        | PC14 <sup>(6)</sup> | OSC32_IN           | -                   |

- 1. I = input, O = output, S = supply, HiZ= high impedance.

- 2. FT= 5 V tolerant.

- Function availability depends on the chosen device. For devices having reduced peripheral counts, it is always the lower number of peripherals that is included. For example, if a device has only one SPI, two USARTs and two timers, they will be called SPI1, USART1 & USART2 and TIM2 & TIM 3, respectively. Refer to Table 2 on page 11.

- 4. If several peripherals share the same I/O pin, to avoid conflict between these alternate functions only one peripheral should be enabled at a time through the peripheral clock enable bit (in the corresponding RCC peripheral clock enable register).

- 5. PC13, PC14 and PC15 are supplied through the power switch and since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 in output mode is restricted: the speed should not exceed 2 MHz with a maximum load of 30 pF and these IOs must *not* be used as a current source (e.g. to drive an LED).

- 6. Main function after the first backup domain power-up. Later on, it depends on the contents of the Backup registers even after reset (because these registers are not reset by the main reset). For details on how to manage these IOs, refer to the Battery backup domain and BKP register description sections in the STM32F10xxx reference manual, available from the STMicroelectronics website: www.st.com.

- 7. The pins number 2 and 3 in the VFQFPN36 package, 5 and 6 in the LQFP48 and LQFP64 packages and C1 and C2 in the TFBGA64 package are configured as OSC\_IN/OSC\_OUT after reset, however the functionality of PD0 and PD1 can be remapped by software on these pins. For more details, refer to the Alternate function I/O and debug configuration section in the STM32F10xxx reference manual.

- 8. Unlike in the LQFP64 package, there is no PC3 in the TFBGA64 package. The  $V_{REF+}$  functionality is provided instead.

- 9. I2C2 is not present on low-density value line devices.

- 10. SPI2 is not present on low-density value line devices.

- 11. TIM4 is not present on low-density value line devices.

- 12. This alternate function can be remapped by software to some other port pins (if available on the used package). For more details, refer to the Alternate function I/O and debug configuration section in the STM32F10xxx reference manual, available from the STMicroelectronics website: www.st.com.

#### 5.1.6 **Power supply scheme**

$V_{BAT}$ Backup circuitry (OSC32K,RTC, Power switch 1.8-3.6V Wake-up logic Backup registers) Ю GP I/Os Logic Kernel logic (CPU, Digital & Memories)  $V_{\text{DD}}$ 1/2/3/4/5 Regulator 5 × 100 nF  $V_{SS}$ + 1  $\times$  4.7  $\mu$ F 1/2/3/4/5  $V_{DDA}$ Analog: 10 nF ADC/DAC V<sub>REF</sub> RCs, PLL + 1 µF V<sub>SSA</sub> ai14125e

Figure 10. Power supply scheme

Caution: In Figure 10, the 4.7  $\mu F$  capacitor must be connected to  $V_{DD3}$ .

**Symbol Parameter Conditions** Min Max Unit LQFP100 434 Power dissipation at T<sub>A</sub> = LQFP64 444  $\mathsf{P}_{\mathsf{D}}$ 85 °C for suffix 6 or T<sub>A</sub> = mW TFBGA64 308 105 °C for suffix 7<sup>(2)</sup> LQFP48 \_ 363 Maximum power dissipation -4085 Ambient temperature for 6 °C suffix version Low power dissipation<sup>(3)</sup> -40 105 TA Maximum power dissipation -40 105 Ambient temperature for 7 °C suffix version Low power dissipation<sup>(3)</sup> <del>-4</del>0 125 6 suffix version -40 105 °C TJ Junction temperature range -40 125 7 suffix version

Table 8. General operating conditions (continued)

Note:

It is recommended to power  $V_{DD}$  and  $V_{DDA}$  from the same source. A maximum difference of 300 mV between  $V_{DD}$  and  $V_{DDA}$  can be tolerated during power-up and operation.

# 5.3.2 Operating conditions at power-up / power-down

Subject to general operating conditions for T<sub>A</sub>.

Table 9. Operating conditions at power-up / power-down

| Symbol    | Parameter                      | Min | Max | Unit  |  |

|-----------|--------------------------------|-----|-----|-------|--|

|           | V <sub>DD</sub> rise time rate | 0   | 8   | µs/V  |  |

| $t_{VDD}$ | V <sub>DD</sub> fall time rate | 20  | 8   | μ5/ ν |  |

# 5.3.3 Embedded reset and power control block characteristics

The parameters given in *Table 10* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

<sup>1.</sup> When the ADC is used, refer to Table 42: ADC characteristics.

<sup>2.</sup> If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>J</sub>max (see *Table 6.5: Thermal characteristics on page 89*).

In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>J</sub>max (see Table 6.5: Thermal characteristics on page 89).

Table 12. Maximum current consumption in Run mode, code with data processing running from Flash

| Symbol | Doromotor                        | Conditions                                              |                   | Ма                     | Unit                    |       |

|--------|----------------------------------|---------------------------------------------------------|-------------------|------------------------|-------------------------|-------|

|        | Parameter                        |                                                         | f <sub>HCLK</sub> | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Joint |

|        |                                  | External clock <sup>(2)</sup> , all peripherals enabled | 24 MHz            | 15.4                   | 15.7                    |       |

|        | Supply<br>current in<br>Run mode |                                                         | 16 MHz            | 11                     | 11.5                    |       |

|        |                                  |                                                         | 8 MHz             | 6.7                    | 6.9                     | mA    |

| IDD    |                                  |                                                         | 24 MHz            | 10.3                   | 10.5                    | ША    |

|        |                                  |                                                         | 16 MHz            | 7.8                    | 8.1                     |       |

|        |                                  |                                                         | 8 MHz             | 5.1                    | 5.3                     |       |

- 1. Guaranteed by characterization results.

- 2. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

Table 13. Maximum current consumption in Run mode, code with data processing running from RAM

| Symbol | Parameter                  | Conditions                                              | •                 | Ma                     | Unit                    |      |

|--------|----------------------------|---------------------------------------------------------|-------------------|------------------------|-------------------------|------|

|        | Parameter                  |                                                         | f <sub>HCLK</sub> | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C |      |

|        |                            | External clock <sup>(2)</sup> , all peripherals enabled | 24 MHz            | 14.5                   | 15                      |      |

|        | Supply current in Run mode |                                                         | 16 MHz            | 10                     | 10.5                    | mA   |

|        |                            |                                                         | 8 MHz             | 6                      | 6.3                     |      |

| IDD    |                            | External clock <sup>(2)</sup> all peripherals disabled  | 24MHz             | 9.3                    | 9.7                     | IIIA |

|        |                            |                                                         | 16 MHz            | 6.8                    | 7.2                     |      |

|        |                            |                                                         | 8 MHz             | 4.4                    | 4.7                     |      |

- 1. Guaranteed by characterization, tested in production at  $V_{\mbox{\scriptsize DD}}\,\mbox{\scriptsize max},\,f_{\mbox{\scriptsize HCLK}}\,\mbox{\scriptsize max}.$

- 2. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

Table 15. Typical and maximum current consumptions in Stop and Standby modes

|                      |                                         |                                                                                                                                                   |                                                  |                                                  | M                                                |                           |                         |      |

|----------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|---------------------------|-------------------------|------|

| Symbol               | Parameter                               | Conditions                                                                                                                                        | V <sub>DD</sub> /<br>V <sub>BAT</sub><br>= 2.0 V | V <sub>DD</sub> /<br>V <sub>BAT</sub> =<br>2.4 V | V <sub>DD</sub> /<br>V <sub>BAT</sub><br>= 3.3 V | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> = 105 °C | Unit |

|                      | Supply<br>current in<br>Stop mode       | Regulator in Run mode,<br>Low-speed and high-speed<br>internal RC oscillators and<br>high-speed oscillator OFF (no<br>independent watchdog)       | -                                                | 23.5                                             | 24                                               | 190                       | 350                     |      |

|                      |                                         | Regulator in Low-Power mode,<br>Low-speed and high-speed<br>internal RC oscillators and<br>high-speed oscillator OFF (no<br>independent watchdog) | -                                                | 13.5                                             | 14                                               | 170                       | 330                     |      |

| I <sub>DD</sub>      | Supply<br>current in<br>Standby<br>mode | Low-speed internal RC oscillator and independent watchdog ON                                                                                      | -                                                | 2.6                                              | 3.4                                              | -                         | -                       | μА   |

|                      |                                         | Low-speed internal RC oscillator ON, independent watchdog OFF                                                                                     | -                                                | 2.4                                              | 3.2                                              | -                         | -                       |      |

|                      |                                         | Low-speed internal RC oscillator and independent watchdog OFF, low-speed oscillator and RTC OFF                                                   | -                                                | 1.7                                              | 2                                                | 4                         | 5                       |      |

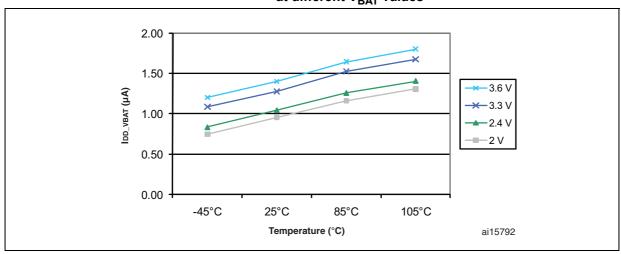

| I <sub>DD_VBAT</sub> | Backup<br>domain<br>supply current      | Low-speed oscillator and RTC<br>ON                                                                                                                | 0.9                                              | 1.1                                              | 1.4                                              | 1.9                       | 2.2                     |      |

<sup>1.</sup> Typical values are measured at  $T_A$  = 25 °C.

Figure 14. Typical current consumption on  $\rm V_{BAT}$  with RTC on vs. temperature at different  $\rm V_{BAT}$  values

Table 16. Typical current consumption in Run mode, code with data processing running from Flash

|                 |                   |                                              |                   | Typical                                   |                          |      |

|-----------------|-------------------|----------------------------------------------|-------------------|-------------------------------------------|--------------------------|------|

| Symbol          | Parameter         | Conditions                                   | f <sub>HCLK</sub> | All peripherals<br>enabled <sup>(2)</sup> | All peripherals disabled | Unit |

|                 |                   |                                              | 24 MHz            | 12.8                                      | 9.3                      |      |

|                 |                   |                                              | 16 MHz            | 9.3                                       | 6.6                      |      |

|                 |                   |                                              | 8 MHz             | 5.1                                       | 3.9                      |      |

|                 |                   | Running on high-speed external clock with an | 4 MHz             | 3.2                                       | 2.5                      |      |

|                 |                   | 8 MHz crystal <sup>(3)</sup>                 | 2 MHz             | 2.1                                       | 1.75                     |      |

|                 | Supply current in |                                              | 1 MHz             | 1.55                                      | 1.4                      |      |

|                 |                   |                                              | 500 kHz           | 1.3                                       | 1.2                      |      |

|                 |                   |                                              | 125 kHz           | 1.1                                       | 1.05                     | - mA |

| I <sub>DD</sub> | Run mode          |                                              | 24 MHz            | 12.2                                      | 8.6                      |      |

|                 |                   |                                              | 16 MHz            | 8.5                                       | 6                        |      |

|                 |                   |                                              | 8 MHz             | 4.6                                       | 3.3                      |      |

|                 |                   | Running on high-speed                        | 4 MHz             | 2.6                                       | 1.9                      |      |

|                 |                   | internal RC (HSI)                            | 2 MHz             | 1.5                                       | 1.15                     |      |

|                 |                   |                                              | 1 MHz             | 0.9                                       | 0.8                      |      |

|                 |                   |                                              | 500 kHz           | 0.65                                      | 0.6                      |      |

|                 |                   |                                              | 125 kHz           | 0.45                                      | 0.43                     |      |

<sup>1.</sup> Typical values are measures at  $T_A$  = 25 °C,  $V_{DD}$  = 3.3 V.

<sup>2.</sup> Add an additional power consumption of 0.8 mA for the ADC and of 0.5 mA for the DAC analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

<sup>3.</sup> An 8 MHz crystal is used as the external clock source. The AHB prescaler is used to reduce the frequency when  $f_{HCLK}$  < 8 MHz, the PLL is used when  $f_{HCLK}$  > 8 MHz.

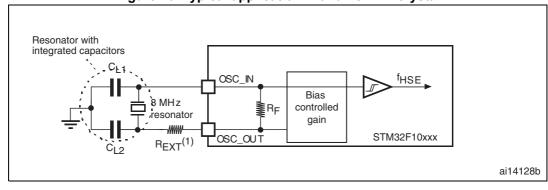

| Symbol                                            | Parameter                                                                                                        | Conditions                                           | Min | Тур | Max | Unit |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----|-----|-----|------|

| f <sub>OSC_IN</sub>                               | Oscillator frequency                                                                                             | -                                                    | 4   | 8   | 24  | MHz  |

| R <sub>F</sub>                                    | Feedback resistor                                                                                                | -                                                    | -   | 200 | -   | kΩ   |

| C <sub>L1</sub><br>C <sub>L2</sub> <sup>(3)</sup> | Recommended load capacitance versus equivalent serial resistance of the crystal (R <sub>S</sub> ) <sup>(4)</sup> | R <sub>S</sub> = 30 Ω                                | -   | 30  | -   | pF   |

| i <sub>2</sub>                                    | HSE driving current                                                                                              | $V_{DD}$ = 3.3 V $V_{IN}$ = $V_{SS}$ with 30 pF load | ı   | -   | 1   | mA   |

| 9 <sub>m</sub>                                    | Oscillator transconductance                                                                                      | Startup                                              | 25  | -   | ı   | mA/V |

| t <sub>SU(HSE)</sub>                              | Startup time                                                                                                     | V <sub>DD</sub> is stabilized                        | -   | 2   | -   | ms   |

Table 21. HSE 4-24 MHz oscillator characteristics<sup>(1)(2)</sup>

- 1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

- 2. Guaranteed by characterization results.

- 3. It is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator. C<sub>L1</sub> and C<sub>L2</sub> are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of C<sub>L1</sub> and C<sub>L2</sub>. PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing C<sub>L1</sub> and C<sub>L2</sub>.

- 4. The relatively low value of the RF resistor offers a good protection against issues resulting from use in a humid environment, due to the induced leakage and the bias condition change. However, it is recommended to take this point into account if the MCU is used in tough humidity conditions.

- t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

Figure 20. Typical application with an 8 MHz crystal

1.  $R_{\text{EXT}}$  value depends on the crystal characteristics.

#### 5.3.16 Communications interfaces

## I<sup>2</sup>C interface characteristics

Unless otherwise specified, the parameters given in *Table 39* are derived from tests performed under the ambient temperature,  $f_{PCLK1}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

The STM32F100xx value line  $I^2C$  interface meets the requirements of the standard  $I^2C$  communication protocol with the following restrictions: the I/O pins SDA and SCL are mapped to are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and  $V_{DD}$  is disabled, but is still present.

The I<sup>2</sup>C characteristics are described in *Table 39*. Refer also to *Section 5.3.12: I/O current injection characteristics* for more details on the input/output alternate function characteristics (SDA and SCL).

| Table 35. I C Characteristics |                                         |            |                                      |           |                    |      |  |

|-------------------------------|-----------------------------------------|------------|--------------------------------------|-----------|--------------------|------|--|

| Symbol                        | Parameter                               | Standard r | node I <sup>2</sup> C <sup>(1)</sup> | Fast mode | Unit               |      |  |

| Symbol                        | ratattietei                             | Min        | Max                                  | Min       | Max                | Unit |  |

| t <sub>w(SCLL)</sub>          | SCL clock low time                      | 4.7        | -                                    | 1.3       | -                  | 110  |  |

| t <sub>w(SCLH)</sub>          | SCL clock high time                     | 4.0        | -                                    | 0.6       | -                  | μs   |  |

| t <sub>su(SDA)</sub>          | SDA setup time                          | 250        | -                                    | 100       | -                  |      |  |

| t <sub>h(SDA)</sub>           | SDA data hold time                      | 0          | -                                    | 0         | 900 <sup>(3)</sup> |      |  |

| $t_{r(SDA)} \ t_{r(SCL)}$     |                                         |            | -                                    | 300       | ns                 |      |  |

| t <sub>f(SDA)</sub>           | SDA and SCL fall time                   | -          | 300                                  | -         | 300                | 300  |  |

| t <sub>h(STA)</sub>           | Start condition hold time               | 4.0        | -                                    | 0.6       | -                  |      |  |

| t <sub>su(STA)</sub>          | Repeated Start condition setup time     | 4.7        | -                                    | 0.6       | -                  | μs   |  |

| t <sub>su(STO)</sub>          | Stop condition setup time               | 4.0        | -                                    | 0.6       | -                  | μs   |  |

| t <sub>w(STO:STA)</sub>       | Stop to Start condition time (bus free) | 4.7        | -                                    | 1.3       | -                  | μs   |  |

| C <sub>b</sub>                | Capacitive load for each bus line       | -          | 400                                  | -         | 400                | pF   |  |

Table 39, I<sup>2</sup>C characteristics

<sup>1.</sup> Guaranteed by design.

f<sub>PCLK1</sub> must be at least 2 MHz to achieve standard mode I<sup>2</sup>C frequencies. It must be at least 4 MHz to achieve fast mode I<sup>2</sup>C frequencies. It must be a multiple of 10 MHz to reach the 400 kHz maximum I2C fast mode clock.

The maximum Data hold time has only to be met if the interface does not stretch the low period of SCL signal.

**Table 42. ADC characteristics**

| Symbol                           | Parameter                                       | Conditions                                                                 | Min                                 | Тур                | Max                | Unit               |

|----------------------------------|-------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------|--------------------|--------------------|--------------------|

| $V_{DDA}$                        | Power supply                                    | -                                                                          | 2.4                                 | -                  | 3.6                | V                  |

| V <sub>REF+</sub>                | Positive reference voltage                      | -                                                                          | 2.4                                 | -                  | $V_{DDA}$          | V                  |

| I <sub>VREF</sub>                | Current on the V <sub>REF</sub> input pin       | -                                                                          | -                                   | 160 <sup>(1)</sup> | 220 <sup>(1)</sup> | μΑ                 |

| f <sub>ADC</sub>                 | ADC clock frequency                             | -                                                                          | 0.6                                 | -                  | 12                 | MHz                |

| f <sub>S</sub> <sup>(2)</sup>    | Sampling rate                                   | -                                                                          | 0.05                                | -                  | 1                  | MHz                |

| £ (2)                            | E 1                                             | f <sub>ADC</sub> = 12 MHz                                                  | -                                   | -                  | 705                | kHz                |

| f <sub>TRIG</sub> <sup>(2)</sup> | External trigger frequency                      | -                                                                          | -                                   | -                  | 17                 | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub> <sup>(3)</sup>  | Conversion voltage range                        | -                                                                          | 0 (V <sub>SSA</sub> tied to ground) | -                  | V <sub>REF+</sub>  | V                  |

| R <sub>AIN</sub> <sup>(2)</sup>  | External input impedance                        | See Equation 1 and Table 43 for details                                    | -                                   | -                  | 50                 | κΩ                 |

| R <sub>ADC</sub> <sup>(2)</sup>  | Sampling switch resistance                      | -                                                                          | -                                   | -                  | 1                  | κΩ                 |

| C <sub>ADC</sub> <sup>(2)</sup>  | Internal sample and hold capacitor              | -                                                                          | -                                   | -                  | 8                  | pF                 |

| t <sub>CAL</sub> <sup>(2)</sup>  | Calibration time                                | f <sub>ADC</sub> = 12 MHz                                                  | 6.9                                 |                    | μs                 |                    |

| rCAL, ,                          | Calibration time                                | -                                                                          | 83                                  |                    | 1/f <sub>ADC</sub> |                    |

| . (2)                            | Injection trigger conversion                    | f <sub>ADC</sub> = 12 MHz                                                  | -                                   | -                  | 0.25               | μs                 |

| t <sub>lat</sub> <sup>(2)</sup>  | latency                                         | -                                                                          | -                                   | -                  | 3 <sup>(4)</sup>   | 1/f <sub>ADC</sub> |

| t <sub>latr</sub> <sup>(2)</sup> | Regular trigger conversion                      | f <sub>ADC</sub> = 12 MHz                                                  | -                                   | -                  | 0.166              | μs                 |

| latr'                            | latency                                         | -                                                                          | -                                   | -                  | 2 <sup>(4)</sup>   | 1/f <sub>ADC</sub> |

| t <sub>S</sub> <sup>(2)</sup>    | Compaling times                                 | f _ 40 MH=                                                                 | 0.125                               | -                  | 20.0               | μs                 |

|                                  | Sampling time                                   | $f_{ADC}$ = 12 MHz                                                         | 1.5                                 | -                  | 239.5              | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(2)</sup> | Power-up time                                   | -                                                                          | 0                                   | 0                  | 1                  | μs                 |

|                                  | Tatal aggregation times                         | f <sub>ADC</sub> = 12 MHz                                                  | 1.17                                | -                  | 21                 | μs                 |

| t <sub>CONV</sub> <sup>(2)</sup> | Total conversion time (including sampling time) | 14 to 252 (t <sub>S</sub> for sampling +12.5 for successive approximation) |                                     |                    | 1/f <sub>ADC</sub> |                    |

- 1. Based on characterization results, not tested in production.

- Guaranteed by design.

- $V_{REF+}$  can be internally connected to  $V_{DDA}$  and  $V_{REF-}$  can be internally connected to  $V_{SSA}$ , depending on the package. Refer to *Table 4: Low & medium-density STM32F100xx pin definitions* and *Figure 6* for further details.

- 4. For external triggers, a delay of  $1/f_{PCLK2}$  must be added to the latency specified in *Table 42*.

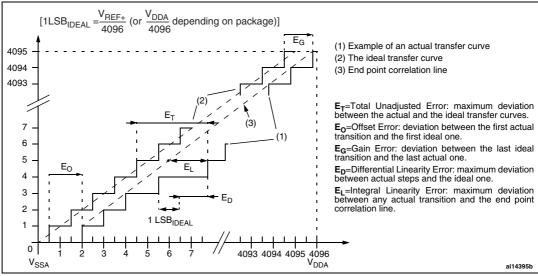

Equation 1:

$$R_{AIN}$$

max formula:  $T_S$

$$R_{AIN} < \frac{T_S}{f_{ADC} \times C_{ADC} \times ln(2^{N+2})} - R_{ADC}$$

The above formula (Equation 1) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. Here N = 12 (from 12-bit resolution).

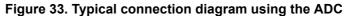

Figure 32. ADC accuracy characteristics

- 1. Refer to *Table 42* for the values of R<sub>AIN</sub>, R<sub>ADC</sub> and C<sub>ADC</sub>.

- C<sub>parasitic</sub> represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high C<sub>parasitic</sub> value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced.

### General PCB design guidelines

Power supply decoupling should be performed as shown in *Figure 34* or *Figure 35*, depending on whether  $V_{REF+}$  is connected to  $V_{DDA}$  or not. The 10 nF capacitors should be ceramic (good quality). They should be placed them as close as possible to the chip.

| Symbol                               | Parameter                                                                                                                                           | Min | Тур         | Max <sup>(1)</sup> | Unit | Comments                                                                                               |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|--------------------|------|--------------------------------------------------------------------------------------------------------|

|                                      | Offset error<br>(difference between measured<br>value at Code (0x800) and the<br>ideal value = V <sub>REF+</sub> /2)                                | -   | -           | ±10                | mV   | Given for the DAC in 12-bit configuration                                                              |

| Offset <sup>(1)</sup>                |                                                                                                                                                     | -   | -           | ±3                 | LSB  | Given for the DAC in 10-bit at V <sub>REF+</sub> = 3.6 V                                               |

|                                      |                                                                                                                                                     | -   | -           | ±12                | LSB  | Given for the DAC in 12-bit at V <sub>REF+</sub> = 3.6 V                                               |

| Gain<br>error <sup>(1)</sup>         | Gain error                                                                                                                                          | -   | -           | ±0.5               | %    | Given for the DAC in 12bit configuration                                                               |

| t <sub>SETTLING</sub> <sup>(1)</sup> | Settling time (full scale: for a 10-bit input code transition between the lowest and the highest input codes when DAC_OUT reaches final value ±1LSB | -   | 3           | 4                  | μs   | $C_{LOAD} \le 50 \text{ pF, } R_{LOAD} \ge 5 \text{ k}\Omega$                                          |

| Update rate <sup>(1)</sup>           | Max frequency for a correct DAC_OUT change when small variation in the input code (from code i to i+1LSB)                                           | ı   | ı           | 1                  | MS/s | $C_{LOAD} \le 50 \text{ pF, } R_{LOAD} \ge 5 \text{ k}\Omega$                                          |

| t <sub>WAKEUP</sub> (1)              | Wakeup time from off state<br>(Setting the ENx bit in the DAC<br>Control register)                                                                  | -   | 6.5         | 10                 | μs   | $C_{LOAD} \le 50$ pF, $R_{LOAD} \ge 5$ k $\Omega$ input code between lowest and highest possible ones. |

| PSRR+ (1)                            | Power supply rejection ratio (to $V_{DDA}$ ) (static DC measurement                                                                                 | -   | <b>–</b> 67 | -40                | dB   | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF                                                       |

Table 46. DAC characteristics (continued)

- Guaranteed by characterization results.

- 2. Guaranteed by design.

Buffer(1)

Figure 36. 12-bit buffered /non-buffered DAC

Buffered/Non-buffered DAC  $\mathsf{R}_\mathsf{L}$ 12-bit digital to analog DAC\_OUTx converter  $\mathsf{C}_\mathsf{L}$ ai17157V2

The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

Table 48. LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat package mechanical data

| Compleal | millimeters |        |        | inches <sup>(1)</sup> |        |        |  |

|----------|-------------|--------|--------|-----------------------|--------|--------|--|

| Symbol   | Min         | Тур    | Max    | Min                   | Тур    | Max    |  |

| А        | -           | -      | 1.600  | -                     | -      | 0.0630 |  |

| A1       | 0.050       | -      | 0.150  | 0.0020                | -      | 0.0059 |  |

| A2       | 1.350       | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |  |

| b        | 0.170       | 0.220  | 0.270  | 0.0067                | 0.0087 | 0.0106 |  |

| С        | 0.090       | -      | 0.200  | 0.0035                | -      | 0.0079 |  |

| D        | 15.800      | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |

| D1       | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |

| D3       | -           | 12.000 | -      | -                     | 0.4724 | -      |  |

| E        | 15.800      | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |

| E1       | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |

| E3       | -           | 12.000 | -      | -                     | 0.4724 | -      |  |

| е        | -           | 0.500  | -      | -                     | 0.0197 | -      |  |

| L        | 0.450       | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |  |

| L1       | -           | 1.000  | -      | -                     | 0.0394 | -      |  |

| k        | 0.0°        | 3.5°   | 7.0°   | 0.0°                  | 3.5°   | 7.0°   |  |

| ccc      | -           | -      | 0.080  | -                     | -      | 0.0031 |  |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

Table 55. Document revision history (continued)

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 08-Jun-2012 | 7        | Updated Table 6: Current characteristics on page 34 Updated Table 39: I2C characteristics on page 64 Corrected note "non-robust" in Section 5.3.17: 12-bit ADC characteristics on page 68 Updated Section 5.3.13: I/O port characteristics on page 57 Updated Section 2.2.20: GPIOs (general-purpose inputs/outputs) on page 20 Updated Table 4: Low & medium-density STM32F100xx pin definitions on page 24 Updated Section 5.3.1: General operating conditions on page 34 Updated Table 14: Maximum current consumption in Sleep mode, code running from Flash or RAM on page 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 08-Jun-2015 | 8        | Updated Table 18: Peripheral current consumption, Table 31: ESD absolute maximum ratings, Table 48: LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat package mechanical data, Table 49: LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package mechanical data, Table 50: TFBGA64 - 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball grid array package mechanical data, Table 51: TFBGA64 recommended PCB design rules (0.5 mm pitch BGA) and Table 52: LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package mechanical data.  Updated Figure 37: LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat package outline, Figure 38: LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat recommended footprint, Figure 40: LQFP64 - 10 x 10 mm 64 pin low-profile quad flat package outline, Figure 41: LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat recommended footprint, Figure 43: TFBGA64 - 64-ball, 5 x 5 mm, 0.5 mm pitch thin profile fine pitch ball grid array package outline, Figure 44: TFBGA64 - 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball grid array, recommended footprint, Figure 46: LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline and Figure 47: LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package recommended footprint.  Added Figure 39: LQFP100 marking example (package top view) Figure 45: TFBGA64 marking example (package top view) and Figure 48: LQFP48 marking example (package top view). |

| 21-Nov-2016 | 9        | Updated:  - Figure 7: Memory map  - Figure 18: High-speed external clock source AC timing diagram  - Figure 19: Low-speed external clock source AC timing diagram  - Table 19: High-speed external user clock characteristics  - Table 20: Low-speed external user clock characteristics  - Table 42: ADC characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

# IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved