Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 24MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | DMA, PDR, POR, PVD, PWM, Temp Sensor, WDT                                |

| Number of I/O              | 37                                                                       |

| Program Memory Size        | 128KB (128K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                    |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 48-LQFP                                                                  |

| Supplier Device Package    | 48-LQFP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f100cbt6btr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1    | Intro | duction  |                                                                                |

|------|-------|----------|--------------------------------------------------------------------------------|

| 2    | Desc  | cription |                                                                                |

|      | 2.1   | Device   | overview                                                                       |

|      | 2.2   | Overvie  | ew                                                                             |

|      |       | 2.2.1    | ARM <sup>®</sup> Cortex <sup>®</sup> -M3 core with embedded Flash and SRAM     |

|      |       | 2.2.2    | Embedded Flash memory14                                                        |

|      |       | 2.2.3    | CRC (cyclic redundancy check) calculation unit                                 |

|      |       | 2.2.4    | Embedded SRAM                                                                  |

|      |       | 2.2.5    | Nested vectored interrupt controller (NVIC)                                    |

|      |       | 2.2.6    | External interrupt/event controller (EXTI)                                     |

|      |       | 2.2.7    | Clocks and startup                                                             |

|      |       | 2.2.8    | Boot modes                                                                     |

|      |       | 2.2.9    | Power supply schemes                                                           |

|      |       | 2.2.10   | Power supply supervisor15                                                      |

|      |       | 2.2.11   | Voltage regulator                                                              |

|      |       | 2.2.12   | Low-power modes                                                                |

|      |       | 2.2.13   | DMA                                                                            |

|      |       | 2.2.14   | RTC (real-time clock) and backup registers                                     |

|      |       | 2.2.15   | Timers and watchdogs 17                                                        |

|      |       | 2.2.16   | l <sup>2</sup> C bus                                                           |

|      |       | 2.2.17   | Universal synchronous/asynchronous receiver transmitter (USART) 19             |

|      |       | 2.2.18   | Serial peripheral interface (SPI) 20                                           |

|      |       | 2.2.19   | HDMI (high-definition multimedia interface) consumer electronics control (CEC) |

|      |       | 2.2.20   | GPIOs (general-purpose inputs/outputs)                                         |

|      |       | 2.2.21   | Remap capability                                                               |

|      |       | 2.2.22   | ADC (analog-to-digital converter)                                              |

|      |       | 2.2.23   | DAC (digital-to-analog converter)21                                            |

|      |       | 2.2.24   | Temperature sensor                                                             |

|      |       | 2.2.25   | Serial wire JTAG debug port (SWJ-DP)                                           |

| 3    | Pino  | uts and  | pin description 22                                                             |

| 4    | Mem   | ory map  | oping                                                                          |

| 2/96 |       |          | DocID16455 Rev 9                                                               |

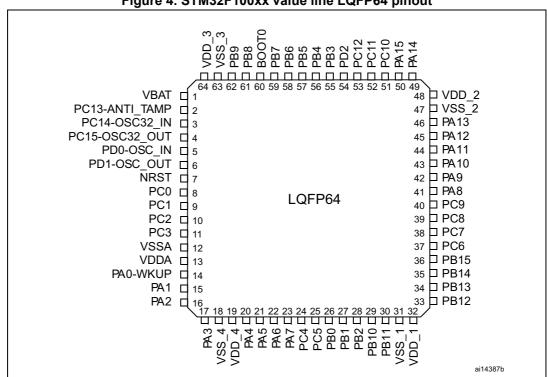

Figure 4. STM32F100xx value line LQFP64 pinout

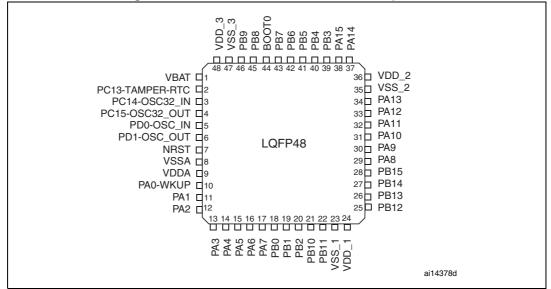

#### Figure 5. STM32F100xx value line LQFP48 pinout

DocID16455 Rev 9

|         | Pi     | ns      |        |                   |                     |                            | <b>-</b>                                         | Alternate function                                                                                                   | ,                      |

|---------|--------|---------|--------|-------------------|---------------------|----------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------|

| LQFP100 | LQFP64 | TFBGA64 | LQFP48 | Pin name          | Type <sup>(1)</sup> | I / O level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                                                                              | Remap                  |

| 33      | 24     | H5      | -      | PC4               | I/O                 | -                          | PC4                                              | ADC1_IN14                                                                                                            | -                      |

| 34      | 25     | H6      | -      | PC5               | I/O                 | -                          | PC5                                              | ADC1_IN15                                                                                                            | -                      |

| 35      | 26     | F5      | 18     | PB0               | I/O                 | -                          | PB0                                              | ADC1_IN8/TIM3_CH3 <sup>(12)</sup>                                                                                    | TIM1_CH2N              |

| 36      | 27     | G5      | 19     | PB1               | I/O                 | -                          | PB1                                              | ADC1_IN9/TIM3_CH4 <sup>(12)</sup>                                                                                    | TIM1_CH3N              |

| 37      | 28     | G6      | 20     | PB2               | I/O                 | FT                         | PB2/BOOT1                                        | -                                                                                                                    | -                      |

| 38      | -      | -       | -      | PE7               | I/O                 | FT                         | PE7                                              | -                                                                                                                    | TIM1_ETR               |

| 39      | -      | -       | -      | PE8               | I/O                 | FT                         | PE8                                              | -                                                                                                                    | TIM1_CH1N              |

| 40      | -      | -       | -      | PE9               | I/O                 | FT                         | PE9                                              | -                                                                                                                    | TIM1_CH1               |

| 41      | -      | -       | -      | PE10              | I/O                 | FT                         | PE10                                             | -                                                                                                                    | TIM1_CH2N              |

| 42      | -      | -       | -      | PE11              | I/O                 | FT                         | PE11                                             | -                                                                                                                    | TIM1_CH2               |

| 43      | -      | -       | -      | PE12              | I/O                 | FT                         | PE12                                             | -                                                                                                                    | TIM1_CH3N              |

| 44      | -      | -       | -      | PE13              | I/O                 | FT                         | PE13                                             | -                                                                                                                    | TIM1_CH3               |

| 45      | -      | -       | -      | PE14              | I/O                 | FT                         | PE14                                             | -                                                                                                                    | TIM1_CH4               |

| 46      | -      | -       | -      | PE15              | I/O                 | FT                         | PE15                                             | -                                                                                                                    | TIM1_BKIN              |

| 47      | 29     | G7      | 21     | PB10              | I/O                 | FT                         | PB10                                             | I2C2_SCL <sup>(9)</sup> /USART3_TX<br>(12)                                                                           | TIM2_CH3 /<br>HDMI_CEC |

| 48      | 30     | H7      | 22     | PB11              | I/O                 | FT                         | PB11                                             | I2C2_SDA <sup>(9)</sup> /USART3_RX <sup>(</sup><br>12)                                                               | TIM2_CH4               |

| 49      | 31     | D6      | 23     | V <sub>SS_1</sub> | S                   | -                          | V <sub>SS_1</sub>                                | -                                                                                                                    | -                      |

| 50      | 32     | E6      | 24     | V <sub>DD_1</sub> | S                   | -                          | V <sub>DD_1</sub>                                | -                                                                                                                    | -                      |

| 51      | 33     | H8      | 25     | PB12              | I/O                 | FT                         | PB12                                             | SPI2_NSS <sup>(10)</sup> /<br>I2C2_SMBA <sup>(9)</sup> /<br>TIM1_BKIN <sup>(12)</sup> /USART3_C<br>K <sup>(12)</sup> | -                      |

| 52      | 34     | G8      | 26     | PB13              | I/O                 | FT                         | PB13                                             | SPI2_SCK <sup>(10)</sup><br>/TIM1_CH1N <sup>(12)</sup><br>USART3_CTS <sup>(12)</sup>                                 | -                      |

| 53      | 35     | F8      | 27     | PB14              | I/O                 | FT                         | PB14                                             | SPI2_MISO <sup>(10)</sup> /<br>TIM1_CH2N <sup>(12)</sup> /<br>USART3_RTS <sup>(12)</sup>                             | TIM15_CH1              |

| 54      | 36     | F7      | 28     | PB15              | I/O                 | FT                         | PB15                                             | SPI2_MOSI <sup>(10)</sup> /<br>TIM1_CH3N /<br>TIM15_CH1N <sup>(12)</sup>                                             | TIM15_CH2              |

| 55      | -      | -       | -      | PD8               | I/O                 | FT                         | PD8                                              | -                                                                                                                    | USART3_TX              |

| 56      | -      | -       | -      | PD9               | I/O                 | FT                         | PD9                                              | -                                                                                                                    | USART3_RX              |

| Table 4. Low & medium-density \$ | STM32F100xx pin | definitions (continued) |

|----------------------------------|-----------------|-------------------------|

|                                  |                 |                         |

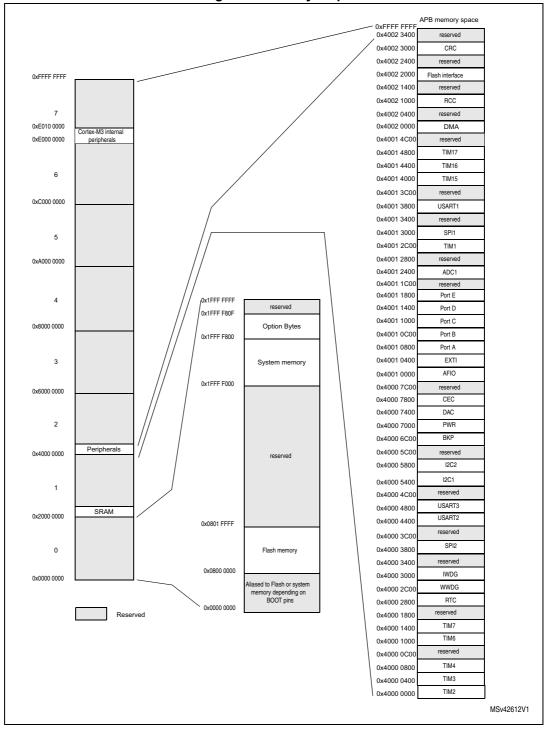

## 4 Memory mapping

The memory map is shown in Figure 7.

Figure 7. Memory map

DocID16455 Rev 9

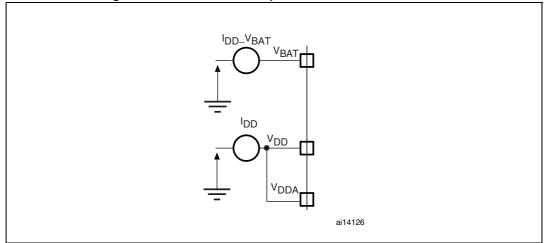

### 5.1.7 Current consumption measurement

#### Figure 11. Current consumption measurement scheme

### 5.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 5: Voltage characteristics*, *Table 6: Current characteristics*, and *Table 7: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                            | Ratings                                                                                                                                     | Min                                   | Мах                  | Unit |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------|------|

| V <sub>DD</sub> –V <sub>SS</sub>  | External main supply voltage (including $V_{DDA}$ and $V_{DD})^{\left(1\right)}$                                                            | -0.3                                  | 4.0                  |      |

| V <sub>IN</sub> <sup>(2)</sup>    | Input voltage on five volt tolerant pin                                                                                                     | V <sub>SS</sub> -0.3                  | V <sub>DD</sub> +4.0 | V    |

| VIN'                              | Input voltage on any other pin                                                                                                              | ny other pin V <sub>SS</sub> -0.3 4.0 |                      |      |

| ΔV <sub>DDx</sub>                 | Variations between different V <sub>DD</sub> power pins                                                                                     | -                                     | 50                   |      |

| V <sub>SSX</sub> -V <sub>SS</sub> | Variations between all the different ground pins                                                                                            | -                                     | 50                   | mV   |

| V <sub>ESD(HBM)</sub>             | Electrostatic discharge voltage (human body model)<br>Electrostatic discharge voltage (human body maximum ratings (escription sensitivity)) |                                       | ngs (electrical      | -    |

#### Table 5. Voltage characteristics

All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 6: Current characteristics* for the maximum allowed injected current values.

|                 |                      |                                              |                   | Typical                                   | values <sup>(1)</sup>    |      |

|-----------------|----------------------|----------------------------------------------|-------------------|-------------------------------------------|--------------------------|------|

| Symbol          | Parameter            | Conditions                                   | f <sub>HCLK</sub> | All peripherals<br>enabled <sup>(2)</sup> | All peripherals disabled | Unit |

|                 |                      |                                              | 24 MHz            | 7.3                                       | 2.6                      |      |

|                 |                      |                                              | 16 MHz            | 5.2                                       | 2                        |      |

|                 |                      |                                              | 8 MHz             | 2.8                                       | 1.3                      |      |

|                 |                      | Running on high-speed external clock with an | 4 MHz             | 2                                         | 1.1                      |      |

|                 | Supply               | 8 MHz crystal <sup>(3)</sup>                 | 2 MHz             | 1.5                                       | 1.1                      | mA   |

|                 |                      |                                              | 1 MHz             | 1.25                                      | 1                        |      |

|                 |                      |                                              | 500 kHz           | 1.1                                       | 1                        |      |

| 1               | Supply<br>current in |                                              | 125 kHz           | 1.05                                      | 0.95                     |      |

| I <sub>DD</sub> | Sleep<br>mode        |                                              | 24 MHz            | 6.65                                      | 1.9                      |      |

|                 | mode                 |                                              | 16 MHz            | 4.5                                       | 1.4                      |      |

|                 |                      |                                              | 8 MHz             | 2.2                                       | 0.7                      |      |

|                 |                      | Running on high-speed                        | 4 MHz             | 1.35                                      | 0.55                     | -    |

|                 |                      | internal RC (HSI)                            | 2 MHz             | 0.85                                      | 0.45                     |      |

|                 |                      |                                              | 1 MHz             | 0.6                                       | 0.41                     |      |

|                 |                      |                                              | 500 kHz           | 0.5                                       | 0.39                     |      |

|                 |                      |                                              | 125 kHz           | 0.4                                       | 0.37                     |      |

Table 17. Typical current consumption in Sleep mode, code running from Flash or RAM

1. Typical values are measures at  $T_A$  = 25 °C,  $V_{DD}$  = 3.3 V.

2. Add an additional power consumption of 0.8 mA for the ADC and of 0.5 mA for the DAC analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

3. An 8 MHz crystal is used as the external clock source. The AHB prescaler is used to reduce the frequency when  $f_{HCLK} > 8$  MHz, the PLL is used when  $f_{HCLK} > 8$  MHz.

### On-chip peripheral current consumption

The current consumption of the on-chip peripherals is given in *Table 18*. The MCU is placed under the following conditions:

- all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- ambient operating temperature and V<sub>DD</sub> supply voltage conditions summarized in Table 5.

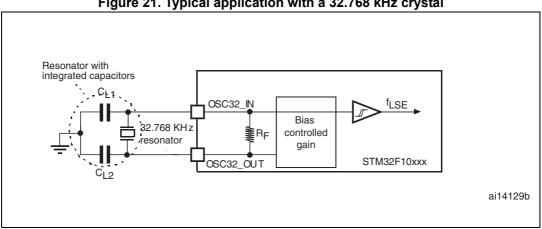

Figure 21. Typical application with a 32.768 kHz crystal

#### 5.3.7 Internal clock source characteristics

The parameters given in Table 23 are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in Table 8.

#### High-speed internal (HSI) RC oscillator

| Symbol                              | Parameter                        | Conditions                             | Min  | Тур | Мах | Unit |  |  |

|-------------------------------------|----------------------------------|----------------------------------------|------|-----|-----|------|--|--|

| f <sub>HSI</sub>                    | Frequency                        | -                                      | -    | 8   | -   | MHz  |  |  |

| DuCy <sub>(HSI)</sub>               | Duty cycle                       | -                                      | 45   | -   | 55  | %    |  |  |

|                                     | Accuracy of HSI oscillator       | $T_{A}$ = -40 to 105 $^{\circ}C^{(2)}$ | -2.4 | -   | 2.5 | %    |  |  |

| ACC <sub>HSI</sub>                  |                                  | $T_A = -10$ to 85 °C <sup>(2)</sup>    | -2.2 | -   | 1.3 | %    |  |  |

| ACCHSI                              |                                  | $T_A = 0$ to 70 °C <sup>(2)</sup>      | -1.9 | -   | 1.3 | %    |  |  |

|                                     |                                  | T <sub>A</sub> = 25 °C                 | -1   | -   | 1   | %    |  |  |

| t <sub>su(HSI)</sub> <sup>(3)</sup> | HSI oscillator startup time      | -                                      | 1    | -   | 2   | μs   |  |  |

| I <sub>DD(HSI)</sub> <sup>(3)</sup> | HSI oscillator power consumption | -                                      | -    | 80  | 100 | μA   |  |  |

Table 23 HSI oscillator characteristics<sup>(1)</sup>

1. V<sub>DD</sub> = 3.3 V, T<sub>A</sub> = –40 to 105 °C °C unless otherwise specified.

2. Guaranteed by characterization results.

3. Guaranteed by design. Not tested in production

### 5.3.8 PLL characteristics

The parameters given in *Table 26* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

| Symbol               | Parameter                      |                    | Unit |                    |      |

|----------------------|--------------------------------|--------------------|------|--------------------|------|

| Symbol               | Parameter                      | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

| £                    | PLL input clock <sup>(2)</sup> | 1                  | 8.0  | 24                 | MHz  |

| f <sub>PLL_IN</sub>  | PLL input clock duty cycle     | 40                 | -    | 60                 | %    |

| f <sub>PLL_OUT</sub> | PLL multiplier output clock    | 16                 | -    | 24                 | MHz  |

| t <sub>LOCK</sub>    | PLL lock time                  | -                  | -    | 200                | μs   |

| Jitter               | Cycle-to-cycle jitter          | -                  | -    | 300                | ps   |

#### Table 26. PLL characteristics

1. Guaranteed by characterization results.

2. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{PLL_OUT}$ .

### 5.3.9 Memory characteristics

#### Flash memory

The characteristics are given at  $T_{\text{A}}$  = –40 to 105  $^{\circ}\text{C}$  unless otherwise specified.

| Symbol             | Parameter               | Conditions                                                                 | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

|--------------------|-------------------------|----------------------------------------------------------------------------|--------------------|------|--------------------|------|

| t <sub>prog</sub>  | 16-bit programming time | T <sub>A</sub> = -40 to +105 °C                                            | 40                 | 52.5 | 70                 | μs   |

| t <sub>ERASE</sub> | Page (1 KB) erase time  | T <sub>A</sub> = -40 to +105 °C                                            | 20                 | -    | 40                 | ms   |

| t <sub>ME</sub>    | Mass erase time         | $T_A = -40$ to +105 °C                                                     | 20                 | -    | 40                 | ms   |

|                    |                         | Read mode<br>f <sub>HCLK</sub> = 24 MHz, V <sub>DD</sub> = 3.3 V           | -                  | -    | 20                 | mA   |

| I <sub>DD</sub>    | Supply current          | Write / Erase modes<br>f <sub>HCLK</sub> = 24 MHz, V <sub>DD</sub> = 3.3 V | -                  | -    | 5                  | mA   |

|                    |                         | Power-down mode / Halt,<br>$V_{DD}$ = 3.0 to 3.6 V                         | -                  | -    | 50                 | μA   |

| V <sub>prog</sub>  | Programming voltage     | -                                                                          | 2                  | -    | 3.6                | V    |

| Table 27 | . Flash | memory | characteristics |

|----------|---------|--------|-----------------|

|----------|---------|--------|-----------------|

1. Guaranteed by design.

| Symbol           | Parameter      | Conditions                                                                              |                    | Unit |     |         |

|------------------|----------------|-----------------------------------------------------------------------------------------|--------------------|------|-----|---------|

|                  |                | Conditions                                                                              | Min <sup>(1)</sup> | Тур  | Max | Onit    |

| N <sub>END</sub> | Endurance      | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                 | -    | -   | kcycles |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30                 | -    | -   |         |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                 | -    | -   | Years   |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                 | -    | -   |         |

#### Table 28. Flash memory endurance and data retention

1. Based on characterization not tested in production.

2. Cycling performed over the whole temperature range.

### 5.3.12 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibilty to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (>5 LSB TUE), out of spec current injection on adjacent pins or other functional failure (for example reset, oscillator frequency deviation).

The test results are given in Table 33

|                  |                                                            | Functional s       |                    |      |

|------------------|------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                | Negative injection | Positive injection | Unit |

|                  | Injected current on OSC_IN32,<br>OSC_OUT32, PA4, PA5, PC13 | -0                 | +0                 |      |

| I <sub>INJ</sub> | Injected current on all FT pins                            | -5                 | +0                 | mA   |

|                  | Injected current on any other pin                          | -5                 | +5                 |      |

#### Table 33. I/O current injection susceptibility

### 5.3.13 I/O port characteristics

### General input/output characteristics

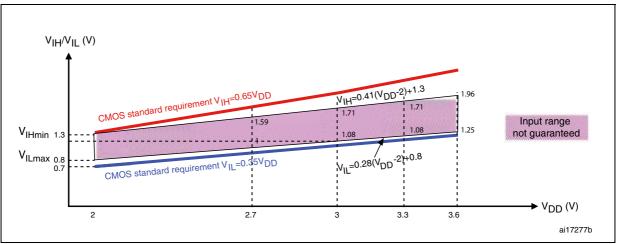

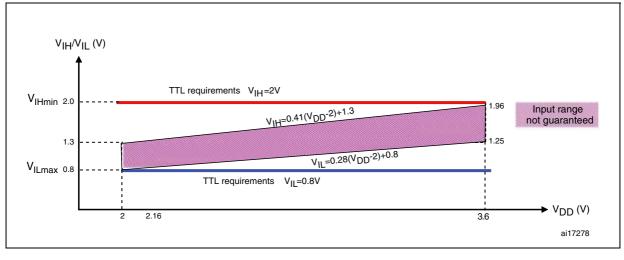

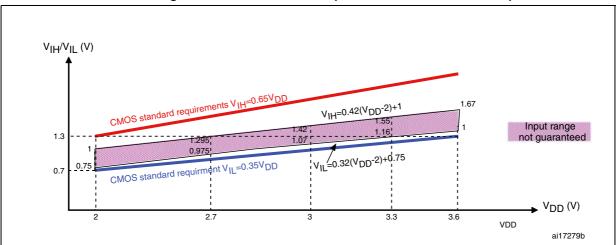

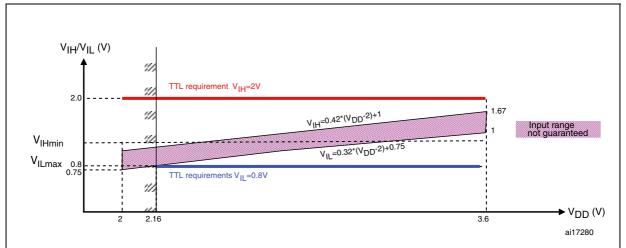

Unless otherwise specified, the parameters given in *Table 34* are derived from tests performed under the conditions summarized in *Table 8*. All I/Os are CMOS and TTL compliant.

| Symbol           | Parameter                                                                | Conditions                                                         | Min                                | Тур | Мах                                | Unit |

|------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------|-----|------------------------------------|------|

| M                | Standard I/O input low level voltage                                     |                                                                    | -0.3                               | -   | 0.28*(V <sub>DD</sub> -2 V)+0.8 V  |      |

| V <sub>IL</sub>  | I/O FT <sup>(1)</sup> input low level voltage                            | -                                                                  | -0.3                               | -   | 0.32*(V <sub>DD</sub> -2 V)+0.75 V |      |

|                  | Standard I/O input<br>high level voltage 0.41*(V <sub>DD</sub> -2 V) +1. |                                                                    | 0.41*(V <sub>DD</sub> -2 V) +1.3 V | -   | V <sub>DD</sub> +0.3               | V    |

| $V_{IH}$         | I/O FT <sup>(1)</sup> input high                                         | $V_{DD} > 2 V$                                                     | 0.42*(\/2\+1.\/                    |     | 5.5                                |      |

|                  | level voltage                                                            | V <sub>DD</sub> ≤2 V                                               | 0.42*(V <sub>DD</sub> –2)+1 V      | -   | 5.2                                |      |

| V <sub>hys</sub> | Standard I/O Schmitt<br>trigger voltage<br>hysteresis <sup>(2)</sup>     | -                                                                  | 200                                | -   | -                                  | mV   |

| * nys            | I/O FT Schmitt trigger voltage hysteresis <sup>(2)</sup>                 |                                                                    | 5% V <sub>DD</sub> <sup>(3)</sup>  | -   | -                                  | mV   |

| 1                | Input leakage                                                            | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>Standard I/Os | -                                  | -   | ±1                                 |      |

| l <sub>lkg</sub> | current <sup>(4)</sup> V <sub>IN</sub> = 5 V<br>I/O FT                   |                                                                    | -                                  | 3   | μΑ                                 |      |

| R <sub>PU</sub>  | Weak pull-up<br>equivalent resistor <sup>(5)</sup>                       | $V_{IN} = V_{SS}$                                                  | 30                                 | 40  | 50                                 | kΩ   |

| R <sub>PD</sub>  | Weak pull-down<br>equivalent resistor <sup>(5)</sup>                     | $V_{IN} = V_{DD}$                                                  | 30                                 | 40  | 50                                 | kΩ   |

| CIO              | I/O pin capacitance                                                      | -                                                                  | -                                  | 5   | -                                  | pF   |

1. FT = 5V tolerant. To sustain a voltage higher than V<sub>DD</sub>+0.3 the internal pull-up/pull-down resistors must be disabled.

2. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by design.

- 3. With a minimum of 100 mV.

- 4. Leakage could be higher than max. if negative current is injected on adjacent pins.

- 5. Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimum (~10% order).

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 22* and *Figure 23* for standard I/Os, and in *Figure 24* and *Figure 25* for 5 V tolerant I/Os.

Figure 22. Standard I/O input characteristics - CMOS port

Figure 24. 5 V tolerant I/O input characteristics - CMOS port

Figure 25. 5 V tolerant I/O input characteristics - TTL port

#### **Output driving current**

The GPIOs (general-purpose inputs/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA (with a relaxed V<sub>OL</sub>/V<sub>OH</sub>).

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 5.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating I<sub>VDD</sub> (see *Table 6*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating  $I_{VSS}$  (see *Table 6*).

| T <sub>s</sub> (cycles) | t <sub>S</sub> (μs) | R <sub>AIN</sub> max (kΩ) |

|-------------------------|---------------------|---------------------------|

| 1.5                     | 0.125               | 0.4                       |

| 7.5                     | 0.625               | 5.9                       |

| 13.5                    | 1.125               | 11.4                      |

| 28.5                    | 2.375               | 25.2                      |

| 41.5                    | 3.45                | 37.2                      |

| 55.5                    | 4.625               | 50                        |

| 71.5                    | 5.96                | NA                        |

| 239.5                   | 20                  | NA                        |

#### Table 43. $R_{AIN}$ max for $f_{ADC} = 12 \text{ MHz}^{(1)}$

1. Guaranteed by design.

| Symbol | Parameter                    | Test conditions                                                                        | Тур  | Мах  | Unit |

|--------|------------------------------|----------------------------------------------------------------------------------------|------|------|------|

| ET     | Total unadjusted error       | $f_{PCLK2} = 24 \text{ MHz},$                                                          | ±1.3 | ±2.2 |      |

| EO     | Offset error                 | f <sub>ADC</sub> = 12 MHz, R <sub>AIN</sub> < 10 kΩ<br>V <sub>DDA</sub> = 3 V to 3.6 V | ±1   | ±1.5 |      |

| EG     | Gain error                   | $V_{\text{REF+}} = V_{\text{DDA}}$                                                     | ±0.5 | ±1.5 | LSB  |

| ED     | Differential linearity error | T <sub>A</sub> = 25 °C                                                                 | ±0.7 | ±1   |      |

| EL     | Integral linearity error     | Measurements made after<br>ADC calibration                                             | ±0.8 | ±1.5 |      |

| Table 44. ADC accuracy - limited test conditions <sup>(1)(2)</sup> |

|--------------------------------------------------------------------|

|--------------------------------------------------------------------|

1. ADC DC accuracy values are measured after internal calibration.

2. Guaranteed by characterization results.

| Table | 45. | ADC | accuracy <sup>(1) (2) (3)</sup> |

|-------|-----|-----|---------------------------------|

|-------|-----|-----|---------------------------------|

| Symbol | Parameter                    | Test conditions                                                     | Тур  | Max  | Unit |

|--------|------------------------------|---------------------------------------------------------------------|------|------|------|

| ET     | Total unadjusted error       | f <sub>PCLK2</sub> = 24 MHz,                                        | ±2   | ±5   |      |

| EO     | Offset error                 | $f_{ADC}$ = 12 MHz, $R_{AIN}$ < 10 kΩ                               | ±1.5 | ±2.5 |      |

| EG     | Gain error                   | $V_{DDA} = 2.4 V$ to 3.6 V<br>T <sub>A =</sub> Full operating range | ±1.5 | ±3   | LSB  |

| ED     | Differential linearity error | Measurements made after                                             | ±1   | ±2   |      |

| EL     | Integral linearity error     | ADC calibration                                                     | ±1.5 | ±3   |      |

1. ADC DC accuracy values are measured after internal calibration.

2. Better performance could be achieved in restricted  $V_{DD}$ , frequency,  $V_{REF}$  and temperature ranges.

3. Guaranteed by characterization results.

Note:ADC accuracy vs. negative injection current: Injecting a negative current on any analog<br/>input pins should be avoided as this significantly reduces the accuracy of the conversion<br/>being performed on another analog input. It is recommended to add a Schottky diode (pin to<br/>ground) to analog pins which may potentially inject negative currents.<br/>Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in<br/>Section 5.3.12 does not affect the ADC accuracy.

## 5.3.18 DAC electrical specifications

| Symbol                           | Parameter                                                                               | Min | Тур | Max <sup>(1)</sup>          | Unit | Comments                                                                                                                |

|----------------------------------|-----------------------------------------------------------------------------------------|-----|-----|-----------------------------|------|-------------------------------------------------------------------------------------------------------------------------|

| V <sub>DDA</sub>                 | Analog supply voltage                                                                   | 2.4 | -   | 3.6                         | V    | -                                                                                                                       |

| $V_{REF^+}$                      | Reference supply voltage                                                                | 2.4 | -   | 3.6                         | V    | V <sub>REF+</sub> must always be below<br>V <sub>DDA</sub>                                                              |

| V <sub>SSA</sub>                 | Ground                                                                                  | 0   | -   | 0                           | V    | -                                                                                                                       |

| R <sub>LOAD</sub> <sup>(2)</sup> | Resistive load with buffer ON                                                           | 5   | -   | -                           | kΩ   | -                                                                                                                       |

| R <sub>0</sub> <sup>(1)</sup>    | Impedance output with buffer<br>OFF                                                     | -   | -   | 15                          | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is 1.5 M $\Omega$ |

| C <sub>LOAD</sub> <sup>(1)</sup> | Capacitive load                                                                         | -   | -   | 50                          | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                         |

| DAC_OUT<br>min <sup>(1)</sup>    | Lower DAC_OUT voltage with<br>buffer ON                                                 | 0.2 | -   | -                           | V    | It gives the maximum output<br>excursion of the DAC.<br>It corresponds to 12-bit input<br>code (0x0E0) to (0xF1C) at    |

| DAC_OUT<br>max <sup>(1)</sup>    | Higher DAC_OUT voltage with<br>buffer ON                                                | -   | -   | V <sub>DDA</sub> – 0.2      | V    | $V_{REF+} = 3.6 V \text{ and } (0x155) \text{ and} (0xEAB) \text{ at } V_{REF+} = 2.4 V$                                |

| DAC_OUT<br>min <sup>(1)</sup>    | Lower DAC_OUT voltage with<br>buffer OFF                                                | -   | 0.5 | -                           | mV   | It gives the maximum output                                                                                             |

| DAC_OUT<br>max <sup>(1)</sup>    | Higher DAC_OUT voltage with<br>buffer OFF                                               | -   | -   | V <sub>REF+</sub> –<br>1LSB | V    | excursion of the DAC.                                                                                                   |

| I <sub>DDVREF+</sub>             | DAC DC current consumption in quiescent mode (Standby mode)                             | -   | -   | 220                         | μΑ   | With no load, worst code<br>(0xF1C) at V <sub>REF+</sub> = 3.6 V in<br>terms of DC consumption on the<br>inputs         |

|                                  |                                                                                         | -   | -   | 380                         | μA   | With no load, middle code<br>(0x800) on the inputs                                                                      |

| I <sub>DDA</sub>                 | DAC DC current consumption in quiescent mode (Standby mode)                             | -   | -   | 480                         | μΑ   | With no load, worst code<br>(0xF1C) at V <sub>REF+</sub> = 3.6 V in<br>terms of DC consumption on the<br>inputs         |

| DNL <sup>(1)</sup>               | Differential non linearity<br>Difference between two                                    | -   | -   | ±0.5                        | LSB  | Given for the DAC in 10-bit configuration                                                                               |

|                                  | consecutive code-1LSB)                                                                  | -   | -   | ±2                          | LSB  | Given for the DAC in 12-bit configuration                                                                               |

| ···· (1)                         | Integral non linearity (difference<br>between measured value at                         | -   | -   | ±1                          | LSB  | Given for the DAC in 10-bit configuration                                                                               |

| INL <sup>(1)</sup>               | Code i and the value at Code i<br>on a line drawn between Code 0<br>and last Code 1023) | -   | -   | ±4                          | LSB  | Given for the DAC in 12-bit configuration                                                                               |

#### Table 46. DAC characteristics

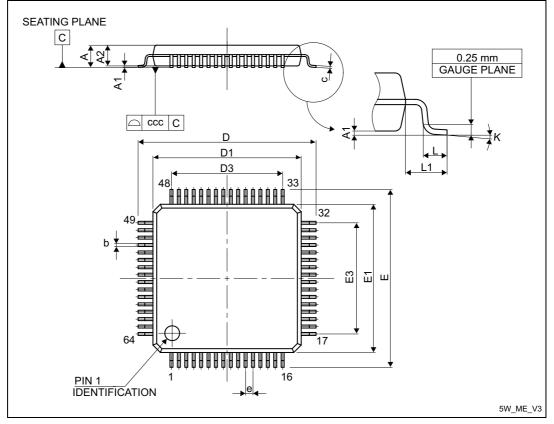

## 6.2 LQFP64 package information

Figure 40.LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package outline

1. Drawing is not in scale.

| Table 49. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package |

|---------------------------------------------------------------------|

| mechanical data                                                     |

| Current e l |       | millimeters |       |        | inches <sup>(1)</sup> | )      |  |

|-------------|-------|-------------|-------|--------|-----------------------|--------|--|

| Symbol      | Min   | Тур         | Мах   | Min    | Тур                   | Мах    |  |

| А           | -     | -           | 1.600 | -      | -                     | 0.0630 |  |

| A1          | 0.050 | -           | 0.150 | 0.0020 | -                     | 0.0059 |  |

| A2          | 1.350 | 1.400       | 1.450 | 0.0531 | 0.0551                | 0.0571 |  |

| b           | 0.170 | 0.220       | 0.270 | 0.0067 | 0.0087                | 0.0106 |  |

| С           | 0.090 | -           | 0.200 | 0.0035 | -                     | 0.0079 |  |

| D           | -     | 12.000      | -     | -      | 0.4724                | -      |  |

| D1          | -     | 10.000      | -     | -      | 0.3937                | -      |  |

| D3          | -     | 7.500       | -     | -      | 0.2953                | -      |  |

| E           | -     | 12.000      | -     | -      | 0.4724                | -      |  |

| E1          | -     | 10.000      | -     | -      | 0.3937                | -      |  |

| E3          | -     | 7.500       | -     | -      | 0.2953                | -      |  |

| Symbol |       | millimeters |       | inches <sup>(1)</sup> |        |        |

|--------|-------|-------------|-------|-----------------------|--------|--------|

|        | Min   | Тур         | Max   | Min                   | Тур    | Мах    |

| E1     | 6.800 | 7.000       | 7.200 | 0.2677                | 0.2756 | 0.2835 |

| E3     | -     | 5.500       | -     | -                     | 0.2165 | -      |

| е      | -     | 0.500       | -     | -                     | 0.0197 | -      |

| L      | 0.450 | 0.600       | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1     | -     | 1.000       | -     | -                     | 0.0394 | -      |

| k      | 0°    | 3.5°        | 7°    | 0°                    | 3.5°   | 7°     |

| CCC    | -     | -           | 0.080 | -                     | -      | 0.0031 |

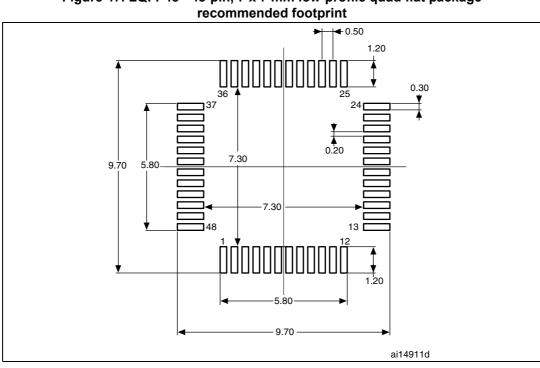

#### Table 52. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

Figure 47. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package

1. Dimensions are expressed in millimeters.

### 6.5 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 8: General operating conditions on page 34*.

The maximum chip-junction temperature,  $T_{\rm J}$  max, in degrees Celsius, may be calculated using the following equation:

$$T_J max = T_A max + (P_D max x \Theta_{JA})$$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

$\mathsf{P}_{\mathsf{I}/\mathsf{O}}$  max represents the maximum power dissipation on output pins where:

$$\mathsf{P}_{\mathsf{I}/\mathsf{O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol          | Parameter                                                                   | Value | Unit |

|-----------------|-----------------------------------------------------------------------------|-------|------|

|                 | Thermal resistance junction-ambient<br>LQFP 100 - 14 × 14 mm / 0.5 mm pitch | 46    |      |

| 0               | Thermal resistance junction-ambient<br>LQFP 64 - 10 × 10 mm / 0.5 mm pitch  | 45    | °C/W |

| Θ <sub>JA</sub> | Thermal resistance junction-ambient<br>TFBGA64 - 5 × 5 mm / 0.5 mm pitch    | 65    | C/W  |

|                 | Thermal resistance junction-ambient<br>LQFP 48 - 7 × 7 mm / 0.5 mm pitch    | 55    |      |

#### Table 53. Package thermal characteristics

#### 6.5.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.

# 8 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12-Oct-2009 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 26-Feb-2010 | 2        | <ul> <li>TFBGA64 package added (see Table 50 and Table 41).</li> <li>Note 5 modified in Table 4: Low &amp; medium-density STM32F100xx pin definitions.</li> <li>I<sub>INJ(PIN)</sub> modified in Table 6: Current characteristics. Conditions removed from Table 25: Low-power mode wakeup timings.</li> <li>Notes modified in Table 34: I/O static characteristics.</li> <li>Figure 27: Recommended NRST pin protection modified.</li> <li>Note modified in Table 39: I/O static characteristics. Figure 28: I2C bus AC waveforms and measurement circuit(1) modified.</li> <li>Table 46: DAC characteristics modified. Figure 36: 12-bit buffered /non-buffered DAC added.</li> <li>TIM2, TIM3, TIM4 and TIM15, TIM16 and TIM17 updated.</li> <li>HDMI-CEC electrical characteristics added.</li> <li>Values added to:</li> <li>Table 12: Maximum current consumption in Run mode, code with data processing running from Flash</li> <li>Table 13: Maximum current consumption in Sleep mode, code running from Flash or RAM</li> <li>Table 15: Typical and maximum current consumptions in Stop and Standby modes</li> <li>Table 18: Peripheral current consumption</li> <li>Table 29: EMS characteristics</li> <li>Table 19: Characteristics</li> <li>Table 19: TS characteristics</li> <li>Table 19: TS characteristics</li> <li>Table 19: TS characteristics</li> <li>Figure 12: Maximum current consumption in Run mode versus frequency (at 3.6 V) - code with data processing running from RAM, peripherals enabled</li> <li>Figure 13: Maximum current consumption in Run mode versus frequency (at 3.6 V) - code with data processing running from RAM, peripherals disabled</li> <li>Figure 15: Typical current consumption in Stop mode with regulator in Run mode versus temperature at VDD = 3.3 V and 3.6 V</li> <li>Figure 16: Typical current consumption in Stop mode with regulator in Run mode versus temperature at VDD = 3.3 V and 3.6 V</li> <li>Figure 16: Typical current consumption in Standby mode versus temperature at VDD = 3.3 V and 3.6 V</li> </ul> |

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 08-Jun-2012 | 7        | Updated Table 6: Current characteristics on page 34<br>Updated Table 39: I2C characteristics on page 64<br>Corrected note "non-robust " in Section 5.3.17: 12-bit ADC<br>characteristics on page 68<br>Updated Section 5.3.13: I/O port characteristics on page 57<br>Updated Section 2.2.20: GPIOs (general-purpose inputs/outputs) on<br>page 20<br>Updated Table 4: Low & medium-density STM32F100xx pin definitions<br>on page 24<br>Updated Section 5.3.1: General operating conditions on page 34<br>Updated Table 14: Maximum current consumption in Sleep mode,<br>code running from Flash or RAM on page 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 08-Jun-2015 | 8        | Updated Table 18: Peripheral current consumption, Table 31: ESD<br>absolute maximum ratings, Table 48: LQPF100 - 100-pin, 14 x 14 mm<br>low-profile quad flat package mechanical data, Table 49: LQFP64 - 64-<br>pin, 10 x 10 mm low-profile quad flat package mechanical data,<br>Table 50: TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine<br>pitch ball grid array package mechanical data, Table 51: TFBGA64<br>recommended PCB design rules (0.5 mm pitch BGA) and Table 52:<br>LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package mechanical<br>data.<br>Updated Figure 37: LQFP100 - 100-pin, 14 x 14 mm low-profile quad<br>flat package outline, Figure 38: LQFP100 - 100-pin, 14 x 14 mm low-<br>profile quad flat recommended footprint, Figure 40: LQFP64 – 10 x 10<br>mm 64 pin low-profile quad flat package outline, Figure 41: LQFP64 -<br>64-pin, 10 x 10 mm low-profile quad flat recommended footprint,<br>Figure 43: TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch thin profile fine<br>pitch ball grid array package outline, Figure 44: TFBGA64 – 64-ball, 5<br>x 5 mm, 0.5 mm pitch, thin profile fine pitch ball grid array,<br>recommended footprint, Figure 46: LQFP48 - 48-pin, 7 x 7 mm low-<br>profile quad flat package outline and Figure 47: LQFP48 - 48-pin, 7 x<br>7 mm low-profile quad flat package recommended footprint.<br>Added Figure 39: LQFP100 marking example (package top view),<br>Figure 42: LQFP64 marking example (package top view) Figure 45:<br>TFBGA64 marking example (package top view) and Figure 48:<br>LQFP48 marking example (package top view). |

| 21-Nov-2016 | 9        | Updated:<br>– Figure 7: Memory map<br>– Figure 18: High-speed external clock source AC timing diagram<br>– Figure 19: Low-speed external clock source AC timing diagram<br>– Table 19: High-speed external user clock characteristics<br>– Table 20: Low-speed external user clock characteristics<br>– Table 42: ADC characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Table 55. Document revision history (continued) |

|-------------------------------------------------|

|-------------------------------------------------|