Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                        |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 24MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                        |

| Peripherals                | DMA, PDR, POR, PVD, PWM, Temp Sensor, WDT                              |

| Number of I/O              | 51                                                                     |

| Program Memory Size        | 64KB (64K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 8K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                              |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                  |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-TFBGA                                                               |

| Supplier Device Package    | 64-TFBGA (5x5)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f100r8h6b |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of figures

| Figure 1.  | STM32F100xx value line block diagram                                                         | . 12 |

|------------|----------------------------------------------------------------------------------------------|------|

| Figure 2.  | Clock tree                                                                                   |      |

| Figure 3.  | STM32F100xx value line LQFP100 pinout                                                        | 22   |

| Figure 4.  | STM32F100xx value line LQFP64 pinout                                                         | 23   |

| Figure 5.  | STM32F100xx value line LQFP48 pinout                                                         | 23   |

| Figure 6.  | STM32F100xx value line TFBGA64 ballout                                                       |      |

| Figure 7.  | Memory map                                                                                   | 30   |

| Figure 8.  | Pin loading conditions                                                                       | 32   |

| Figure 9.  | Pin input voltage                                                                            | 32   |

| Figure 10. | Power supply scheme.                                                                         |      |

| Figure 11. | Current consumption measurement scheme                                                       |      |

| Figure 12. | Maximum current consumption in Run mode versus frequency (at 3.6 V) -                        |      |

| U          | code with data processing running from RAM, peripherals enabled.                             | 39   |

| Figure 13. | Maximum current consumption in Run mode versus frequency (at 3.6 V) -                        |      |

| U          | code with data processing running from RAM, peripherals disabled                             | 39   |

| Figure 14. | Typical current consumption on V <sub>BAT</sub> with RTC on vs. temperature                  |      |

| 0.         | at different V <sub>BAT</sub> values                                                         | 40   |

| Figure 15. | Typical current consumption in Stop mode with regulator in Run mode                          |      |

| 5          | versus temperature at $\dot{V}_{DD}$ = 3.3 V and 3.6 V                                       | 41   |

| Figure 16. | Typical current consumption in Stop mode with regulator                                      |      |

| 0          | in Low-power mode versus temperature at V <sub>DD</sub> = 3.3 V and 3.6 V                    | 41   |

| Figure 17. | Typical current consumption in Standby mode                                                  |      |

| - gane     | versus temperature at $V_{DD}$ = 3.3 V and 3.6 V                                             | 42   |

| Figure 18. | High-speed external clock source AC timing diagram                                           |      |

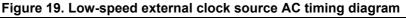

| Figure 19. | Low-speed external clock source AC timing diagram                                            |      |

| Figure 20. | Typical application with an 8 MHz crystal.                                                   |      |

| Figure 21. | Typical application with a 32.768 kHz crystal                                                |      |

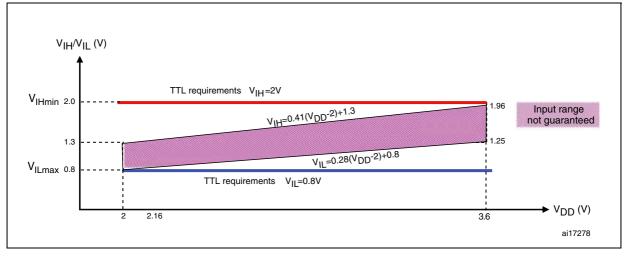

| Figure 22. | Standard I/O input characteristics - CMOS port                                               |      |

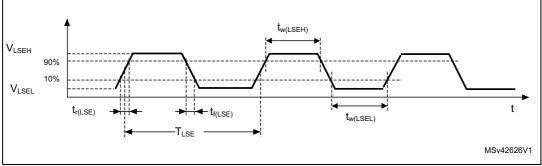

| Figure 23. | Standard I/O input characteristics - TTL port                                                |      |

| Figure 24. | 5 V tolerant I/O input characteristics - CMOS port                                           |      |

| Figure 25. | 5 V tolerant I/O input characteristics - TTL port                                            |      |

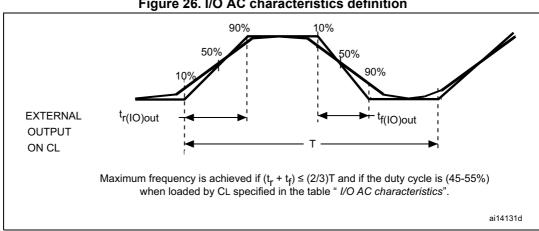

| Figure 26. | I/O AC characteristics definition                                                            |      |

| Figure 27. | Recommended NRST pin protection                                                              |      |

| Figure 28. | I <sup>2</sup> C bus AC waveforms and measurement circuit <sup>(1)</sup>                     |      |

| Figure 29. | SPI timing diagram - slave mode and CPHA = 0                                                 |      |

| Figure 30. | SPI timing diagram - slave mode and CPHA = $1^{(1)}$                                         |      |

| Figure 31. | SPI timing diagram - master mode <sup>(1)</sup>                                              | 68   |

| Figure 32. | ADC accuracy characteristics                                                                 |      |

| Figure 33. | Typical connection diagram using the ADC                                                     |      |

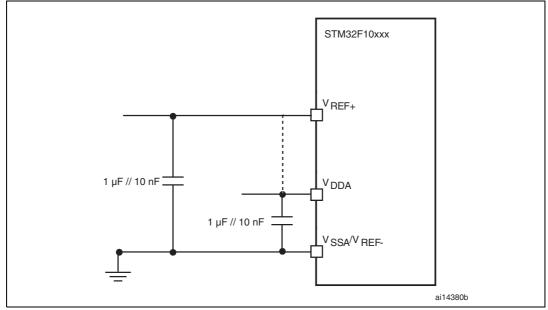

| Figure 34. | Power supply and reference decoupling (V <sub>REF+</sub> not connected to V <sub>DDA</sub> ) | 72   |

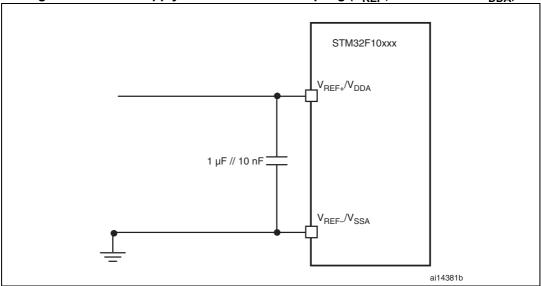

| Figure 35. | Power supply and reference decoupling ( $V_{REF+}$ connected to $V_{DDA}$ ).                 | 72   |

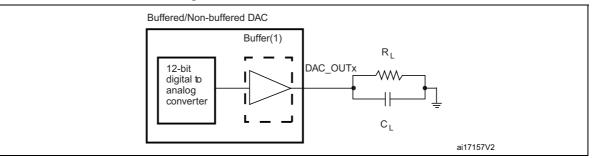

| Figure 36. | 12-bit buffered /non-buffered DAC                                                            |      |

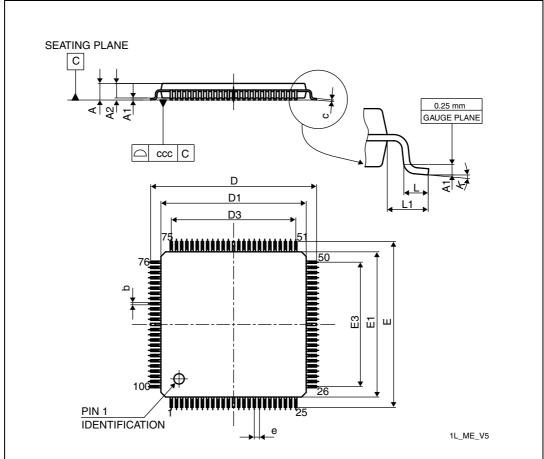

| Figure 37. | LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat package outline                          |      |

| Figure 38. | LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat                                          |      |

|            | recommended footprint.                                                                       | 78   |

| Figure 39. | LQFP100 marking example (package top view)                                                   | 79   |

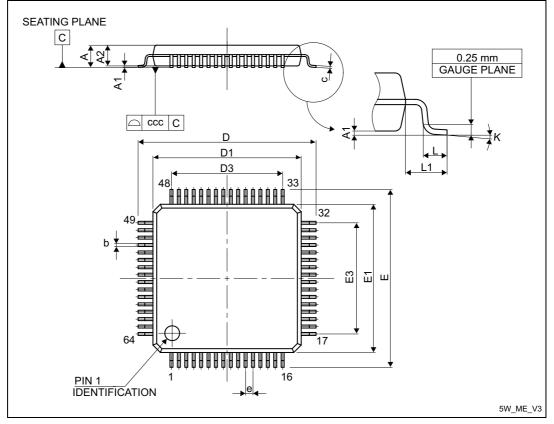

| Figure 40. | LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package outline                             |      |

| Figure 41. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat recommended footprint                      |      |

|            |                                                                                              |      |

# 2.2 Overview

# 2.2.1 ARM<sup>®</sup> Cortex<sup>®</sup>-M3 core with embedded Flash and SRAM

The ARM<sup>®</sup> Cortex<sup>®</sup>-M3 processor is the latest generation of ARM processors for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM Cortex<sup>®</sup>-M3 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The STM32F100xx value line family having an embedded ARM core, is therefore compatible with all ARM tools and software.

# 2.2.2 Embedded Flash memory

Up to 128 Kbytes of embedded Flash memory is available for storing programs and data.

# 2.2.3 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

# 2.2.4 Embedded SRAM

Up to 8 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states.

# 2.2.5 Nested vectored interrupt controller (NVIC)

The STM32F100xx value line embeds a nested vectored interrupt controller able to handle up to 41 maskable interrupt channels (not including the 16 interrupt lines of  $Cortex^{\mbox{\ensuremath{\mathbb{R}}}}$ -M3) and 16 priority levels.

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of *late arriving* higher priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

DocID16455 Rev 9

higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

### 2.2.11 Voltage regulator

The regulator has three operation modes: main (MR), low power (LPR) and power down.

- MR is used in the nominal regulation mode (Run)

- LPR is used in the Stop mode

- Power down is used in Standby mode: the regulator output is in high impedance: the kernel circuitry is powered down, inducing zero consumption (but the contents of the registers and SRAM are lost)

This regulator is always enabled after reset. It is disabled in Standby mode, providing high impedance output.

### 2.2.12 Low-power modes

The STM32F100xx value line supports three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

• Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

• Stop mode

Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low power mode.

The device can be woken up from Stop mode by any of the EXTI line. The EXTI line source can be one of the 16 external lines, the PVD output or the RTC alarm.

• Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.8 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, SRAM and register contents are lost except for registers in the Backup domain and Standby circuitry.

The device exits Standby mode when an external reset (NRST pin), a IWDG reset, a rising edge on the WKUP pin, or an RTC alarm occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped by entering Stop or Standby mode.

### 2.2.13 DMA

The flexible 7-channel general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The DMA controller supports circular buffer management avoiding the generation of interrupts when the controller reaches the end of the buffer.

### 2.2.23 DAC (digital-to-analog converter)

The two 12-bit buffered DAC channels can be used to convert two digital signals into two analog voltage signal outputs. The chosen design structure is composed of integrated resistor strings and an amplifier in noninverting configuration.

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- up to 10-bit output

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channels' independent or simultaneous conversions

- DMA capability for each channel

- external triggers for conversion

- input voltage reference V<sub>REF+</sub>

Eight DAC trigger inputs are used in the STM32F100xx. The DAC channels are triggered through the timer update outputs that are also connected to different DMA channels.

### 2.2.24 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 2 V <  $V_{DDA}$  < 3.6 V. The temperature sensor is internally connected to the ADC1\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

### 2.2.25 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP Interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target. The JTAG TMS and TCK pins are shared respectively with SWDIO and SWCLK and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

|   | 1                          | 2                    | 3       | 4       | 5       | 6 IFBGA                  | 7       | 8      |

|---|----------------------------|----------------------|---------|---------|---------|--------------------------|---------|--------|

| A | •<br>/PC14-,<br>0\&C32_lNT | , PC13-,<br>AMPER-RT | ( PB9 ) | ( PB4 ) | (PB3)   | (PA15)                   | (PA14)  | (PA13) |

| в | , PC15-,<br>OSC32_OUT      | VBAT)                | ( PB8 ) | воото   | (PD2)   | (PC11)                   | (PC10)  | (PA12) |

| C | OSC_IN                     | VSS_4                | ( PB7 ) | (PB5)   | (PC12)  | (PA10)                   | ( PA9 ) | (PA11) |

| D | OSC_OUT                    | VDD_4                | (PB6)   | ,VSS_3  | Vss_2   | ,Vss_1;                  | (PA8)   | (PC9)  |

| E | (NRST)                     | (PC1)                | (PC0)   | 'VDD_3' | VDD_2'  | ,<br>V <sub>DD_1</sub> , | (PC7)   | (PC8)  |

| F | (VSSA)                     | (PC2)                | (PA2 )  | (PA5)   | (PB0)   | (PC6)                    | (PB15)  | (PB14) |

| G | WREF+                      | PĄO-WKŲP             | ( PA3 ) | (PA6)   | (PB1)   | (PB2)                    | (PB10)  | (PB13) |

| н | V <sub>DDA</sub> ,         | ( PA1 )              | ( PA4 ) | PA7     | ( PC4 ) | (PC5)                    | (PB11)  | (PB12) |

|   |                            |                      |         |         |         |                          |         | Al1549 |

Figure 6. STM32F100xx value line TFBGA64 ballout

Table 4. Low & medium-density STM32F100xx pin definitions

|         | Pi     | ns      |        |                                |                     | 2)                         |                                                  | Alternate function | s <sup>(3)(4)</sup> |

|---------|--------|---------|--------|--------------------------------|---------------------|----------------------------|--------------------------------------------------|--------------------|---------------------|

| LQFP100 | LQFP64 | TFBGA64 | LQFP48 | Pin name                       | Type <sup>(1)</sup> | I / O level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default            | Remap               |

| 1       | -      | -       | -      | PE2                            | I/O                 | FT                         | PE2                                              | TRACECLK           | -                   |

| 2       | -      | -       | -      | PE3                            | I/O F               |                            | PE3                                              | TRACED0            | -                   |

| 3       | -      | -       | -      | PE4                            | I/O                 | FT                         | PE4                                              | TRACED1            | -                   |

| 4       | -      | -       | -      | PE5                            | I/O                 | FT                         | PE5                                              | TRACED2            | -                   |

| 5       | -      | -       | -      | PE6                            | I/O                 | FT                         | PE6                                              | TRACED3            | -                   |

| 6       | 1      | B2      | 1      | V <sub>BAT</sub>               | S                   | -                          | V <sub>BAT</sub>                                 | -                  | -                   |

| 7       | 2      | A2      | 2      | PC13-TAMPER-RTC <sup>(5)</sup> | I/O                 | -                          | PC13 <sup>(6)</sup>                              | TAMPER-RTC         | -                   |

| 8       | 3      | A1      | 3      | PC14-OSC32_IN <sup>(5)</sup>   | I/O                 | -                          | PC14 <sup>(6)</sup>                              | OSC32_IN           | -                   |

1. I = input, O = output, S = supply, HiZ= high impedance.

- Function availability depends on the chosen device. For devices having reduced peripheral counts, it is always the lower number of peripherals that is included. For example, if a device has only one SPI, two USARTs and two timers, they will be called SPI1, USART1 & USART2 and TIM2 & TIM 3, respectively. Refer to Table 2 on page 11.

- 4. If several peripherals share the same I/O pin, to avoid conflict between these alternate functions only one peripheral should be enabled at a time through the peripheral clock enable bit (in the corresponding RCC peripheral clock enable register).

- PC13, PC14 and PC15 are supplied through the power switch and since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 in output mode is restricted: the speed should not exceed 2 MHz with a maximum load of 30 pF and these IOs must *not* be used as a current source (e.g. to drive an LED).

- 6. Main function after the first backup domain power-up. Later on, it depends on the contents of the Backup registers even after reset (because these registers are not reset by the main reset). For details on how to manage these IOs, refer to the Battery backup domain and BKP register description sections in the STM32F10xxx reference manual, available from the STMicroelectronics website: www.st.com.

- 7. The pins number 2 and 3 in the VFQFPN36 package, 5 and 6 in the LQFP48 and LQFP64 packages and C1 and C2 in the TFBGA64 package are configured as OSC\_IN/OSC\_OUT after reset, however the functionality of PD0 and PD1 can be remapped by software on these pins. For more details, refer to the Alternate function I/O and debug configuration section in the STM32F10xxx reference manual.

- 8. Unlike in the LQFP64 package, there is no PC3 in the TFBGA64 package. The V<sub>REF+</sub> functionality is provided instead.

- 9. I2C2 is not present on low-density value line devices.

- 10. SPI2 is not present on low-density value line devices.

- 11. TIM4 is not present on low-density value line devices.

- 12. This alternate function can be remapped by software to some other port pins (if available on the used package). For more details, refer to the Alternate function I/O and debug configuration section in the STM32F10xxx reference manual, available from the STMicroelectronics website: www.st.com.

<sup>2.</sup> FT= 5 V tolerant.

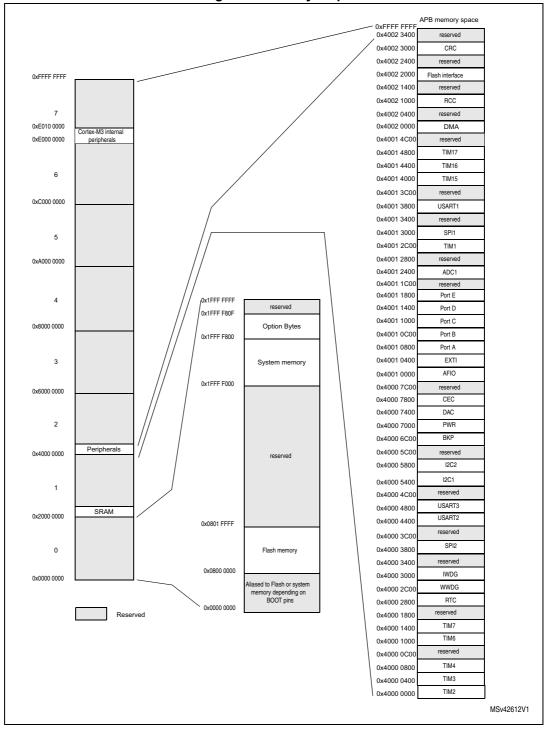

# 4 Memory mapping

The memory map is shown in Figure 7.

Figure 7. Memory map

DocID16455 Rev 9

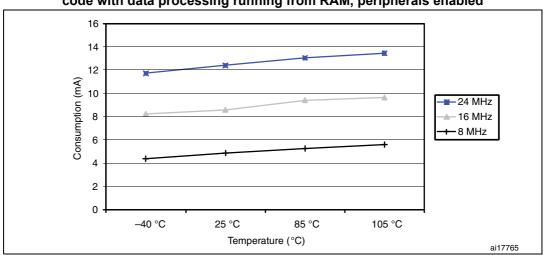

Figure 12. Maximum current consumption in Run mode versus frequency (at 3.6 V) - code with data processing running from RAM, peripherals enabled

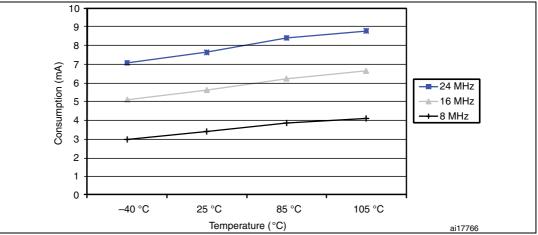

Figure 13. Maximum current consumption in Run mode versus frequency (at 3.6 V) - code with data processing running from RAM, peripherals disabled

Table 14. Maximum current consumption in Sleep mode, code running from Flash or RAM

| Symbol | Deremeter                       | Conditions                                               | £                 | Ма                                                        | Unit |      |

|--------|---------------------------------|----------------------------------------------------------|-------------------|-----------------------------------------------------------|------|------|

| Symbol | Parameter                       | Conditions                                               | f <sub>HCLK</sub> | HCLK <b>T<sub>A</sub> = 85 °C</b> T <sub>A</sub> = 105 °C |      | Unit |

|        | Supply current<br>in Sleep mode | External clock <sup>(2)</sup> all peripherals enabled    | 24 MHz            | 9.6                                                       | 10   |      |

|        |                                 |                                                          | 16 MHz            | 7.1                                                       | 7.5  |      |

|        |                                 |                                                          | 8 MHz             | 4.5                                                       | 4.8  | m 4  |

| IDD    |                                 | External clock <sup>(2)</sup> , all peripherals disabled | 24 MHz            | 3.8                                                       | 4    | mA   |

|        |                                 |                                                          | 16 MHz            | 3.3                                                       | 3.5  |      |

|        |                                 | F F                                                      | 8 MHz             | 2.7                                                       | 3    |      |

1. Guaranteed by characterization, tested in production at  $V_{DD}$  max and  $f_{HCLK}$  max with peripherals enabled.

2. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

### Low-speed external user clock generated from an external source

The characteristics given in *Table 20* result from tests performed using an low-speed external clock source, and under the ambient temperature and supply voltage conditions summarized in *Table 8*.

| Symbol                                       | Parameter                                              | Conditions                       | Min                | Тур    | Max                | Unit |

|----------------------------------------------|--------------------------------------------------------|----------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                         | User external clock source<br>frequency <sup>(1)</sup> |                                  | -                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage <sup>(1)</sup>   |                                  | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | V    |

| V <sub>LSEL</sub>                            | OSC32_IN input pin low level voltage <sup>(1)</sup>    |                                  | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> | v    |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time <sup>(1)</sup>               | -                                | 450                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub>   | OSC32_IN rise or fall time <sup>(1)</sup>              |                                  | -                  | -      | 50                 | 115  |

| C <sub>in(LSE)</sub>                         | OSC32_IN input capacitance <sup>(1)</sup>              |                                  | -                  | 5      | -                  | pF   |

| DuCy <sub>(LSE)</sub>                        | Duty cycle <sup>(1)</sup>                              |                                  | 30                 | -      | 70                 | %    |

| ١L                                           | OSC32_IN Input leakage current                         | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -      | ±1                 | μA   |

Table 20. Low-speed external user clock characteristics

1. Guaranteed by design.

### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 24 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 21*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

# 5.3.8 PLL characteristics

The parameters given in *Table 26* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

| Symbol               | Parameter                      |                    | Unit |                    |      |

|----------------------|--------------------------------|--------------------|------|--------------------|------|

| Symbol               | Parameter                      | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

| f                    | PLL input clock <sup>(2)</sup> | 1                  | 8.0  | 24                 | MHz  |

| f <sub>PLL_IN</sub>  | PLL input clock duty cycle     | 40                 | -    | 60                 | %    |

| f <sub>PLL_OUT</sub> | PLL multiplier output clock    | 16                 | -    | 24                 | MHz  |

| t <sub>LOCK</sub>    | PLL lock time                  | -                  | -    | 200                | μs   |

| Jitter               | Cycle-to-cycle jitter          | -                  | -    | 300                | ps   |

#### Table 26. PLL characteristics

1. Guaranteed by characterization results.

2. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{PLL_OUT}$ .

Figure 22. Standard I/O input characteristics - CMOS port

#### Figure 26. I/O AC characteristics definition

#### 5.3.14 **NRST** pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor, R<sub>PU</sub> (see Table 34).

Unless otherwise specified, the parameters given in Table 37 are derived from tests performed under the ambient temperature and  $V_{\text{DD}}$  supply voltage conditions summarized in Table 8.

| Symbol                               | Parameter                                       | Conditions        | Min  | Тур | Max                  | Unit |

|--------------------------------------|-------------------------------------------------|-------------------|------|-----|----------------------|------|

| V <sub>IL(NRST)</sub> <sup>(1)</sup> | NRST Input low level voltage                    | -                 | -0.5 | -   | 0.8                  | v    |

| V <sub>IH(NRST)</sub> <sup>(1)</sup> | NRST Input high level voltage                   | -                 | 2    | -   | V <sub>DD</sub> +0.5 | v    |

| V <sub>hys(NRST)</sub>               | NRST Schmitt trigger voltage<br>hysteresis      | -                 | -    | 200 | -                    | mV   |

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(2)</sup> | $V_{IN} = V_{SS}$ | 30   | 40  | 50                   | kΩ   |

| V <sub>F(NRST)</sub> <sup>(1)</sup>  | NRST Input filtered pulse                       | -                 | -    | -   | 100                  | ns   |

| V <sub>NF(NRST)</sub> <sup>(1)</sup> | NRST Input not filtered pulse                   | -                 | 300  | -   | -                    | ns   |

Table 37. NRST pin characteristics

1. Guaranteed by design.

The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to 2. the series resistance must be minimum (~10% order).

Figure 34. Power supply and reference decoupling ( $V_{REF+}$  not connected to  $V_{DDA}$ )

1.  $V_{\text{REF+}}$  is available on 100-pin packages and on TFBGA64 packages.  $V_{\text{REF-}}$  is available on 100-pin packages only.

Figure 35. Power supply and reference decoupling ( $V_{REF+}$  connected to  $V_{DDA}$ )

1.  $V_{REF+}$  and  $V_{REF-}$  inputs are available only on 100-pin packages.

# 5.3.18 DAC electrical specifications

| Symbol                           | Parameter                                                                               | Min | Тур | Max <sup>(1)</sup>          | Unit | Comments                                                                                                                |

|----------------------------------|-----------------------------------------------------------------------------------------|-----|-----|-----------------------------|------|-------------------------------------------------------------------------------------------------------------------------|

| V <sub>DDA</sub>                 | Analog supply voltage                                                                   | 2.4 | -   | 3.6                         | V    | -                                                                                                                       |

| $V_{REF^+}$                      | Reference supply voltage                                                                | 2.4 | -   | 3.6                         | V    | V <sub>REF+</sub> must always be below<br>V <sub>DDA</sub>                                                              |

| V <sub>SSA</sub>                 | Ground                                                                                  | 0   | -   | 0                           | V    | -                                                                                                                       |

| R <sub>LOAD</sub> <sup>(2)</sup> | Resistive load with buffer ON                                                           | 5   | -   | -                           | kΩ   | -                                                                                                                       |

| R <sub>0</sub> <sup>(1)</sup>    | Impedance output with buffer<br>OFF                                                     | -   | -   | 15                          | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is 1.5 M $\Omega$ |

| C <sub>LOAD</sub> <sup>(1)</sup> | Capacitive load                                                                         | -   | -   | 50                          | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                         |

| DAC_OUT<br>min <sup>(1)</sup>    | Lower DAC_OUT voltage with<br>buffer ON                                                 | 0.2 | -   | -                           | V    | It gives the maximum output<br>excursion of the DAC.<br>It corresponds to 12-bit input<br>code (0x0E0) to (0xF1C) at    |

| DAC_OUT<br>max <sup>(1)</sup>    | Higher DAC_OUT voltage with<br>buffer ON                                                | -   | -   | V <sub>DDA</sub> – 0.2      | V    | $V_{REF+} = 3.6 V \text{ and } (0x155) \text{ and} (0xEAB) \text{ at } V_{REF+} = 2.4 V$                                |

| DAC_OUT<br>min <sup>(1)</sup>    | Lower DAC_OUT voltage with<br>buffer OFF                                                | -   | 0.5 | -                           | mV   | It gives the maximum output                                                                                             |

| DAC_OUT<br>max <sup>(1)</sup>    | Higher DAC_OUT voltage with<br>buffer OFF                                               | -   | -   | V <sub>REF+</sub> –<br>1LSB | V    | excursion of the DAC.                                                                                                   |

| I <sub>DDVREF+</sub>             | DAC DC current consumption in quiescent mode (Standby mode)                             | -   | -   | 220                         | μΑ   | With no load, worst code<br>(0xF1C) at V <sub>REF+</sub> = 3.6 V in<br>terms of DC consumption on the<br>inputs         |

|                                  |                                                                                         | -   | -   | 380                         | μA   | With no load, middle code<br>(0x800) on the inputs                                                                      |

| I <sub>DDA</sub>                 | DAC DC current consumption in quiescent mode (Standby mode)                             | -   | -   | 480                         | μΑ   | With no load, worst code<br>(0xF1C) at V <sub>REF+</sub> = 3.6 V in<br>terms of DC consumption on the<br>inputs         |

| DNL <sup>(1)</sup>               | Differential non linearity<br>Difference between two                                    | -   | -   | ±0.5                        | LSB  | Given for the DAC in 10-bit configuration                                                                               |

|                                  | consecutive code-1LSB)                                                                  | -   | -   | ±2                          | LSB  | Given for the DAC in 12-bit configuration                                                                               |

| ···· (1)                         | Integral non linearity (difference<br>between measured value at                         | -   | -   | ±1                          | LSB  | Given for the DAC in 10-bit configuration                                                                               |

| INL <sup>(1)</sup>               | Code i and the value at Code i<br>on a line drawn between Code 0<br>and last Code 1023) | -   | -   | ±4                          | LSB  | Given for the DAC in 12-bit configuration                                                                               |

#### Table 46. DAC characteristics

| Table 46. DAC characteristics (continued) |                                                                                                                                                                  |     |     |                    |      |                                                                                                              |  |  |  |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------------------|------|--------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol                                    | Parameter                                                                                                                                                        | Min | Тур | Max <sup>(1)</sup> | Unit | Comments                                                                                                     |  |  |  |

|                                           | Offset error                                                                                                                                                     | -   | -   | ±10                | mV   | Given for the DAC in 12-bit configuration                                                                    |  |  |  |

| Offset <sup>(1)</sup>                     | (difference between measured value at Code (0x800) and the                                                                                                       | -   | -   | ±3                 | LSB  | Given for the DAC in 10-bit at<br>V <sub>REF+</sub> = 3.6 V                                                  |  |  |  |

|                                           | ideal value = V <sub>REF+</sub> /2)                                                                                                                              | -   | -   | ±12                | LSB  | Given for the DAC in 12-bit at $V_{REF+}$ = 3.6 V                                                            |  |  |  |

| Gain<br>error <sup>(1)</sup>              | Gain error                                                                                                                                                       | -   | -   | ±0.5               | %    | Given for the DAC in 12bit configuration                                                                     |  |  |  |

| t <sub>SETTLING</sub> <sup>(1)</sup>      | Settling time (full scale: for a 10-<br>bit input code transition between<br>the lowest and the highest input<br>codes when DAC_OUT reaches<br>final value ±1LSB | -   | 3   | 4                  | μs   | $C_{LOAD} \le 50 \text{ pF}, \text{ R}_{LOAD} \ge 5 \text{ k}\Omega$                                         |  |  |  |

| Update<br>rate <sup>(1)</sup>             | Max frequency for a correct<br>DAC_OUT change when small<br>variation in the input code (from<br>code i to i+1LSB)                                               | -   | -   | 1                  | MS/s | $C_{LOAD} \le 50 \text{ pF}, \text{ R}_{LOAD} \ge 5 \text{ k}\Omega$                                         |  |  |  |

| t <sub>wakeup</sub> (1)                   | Wakeup time from off state<br>(Setting the ENx bit in the DAC<br>Control register)                                                                               | -   | 6.5 | 10                 | μs   | $C_{LOAD} \le 50$ pF, $R_{LOAD} \ge 5$ k $\Omega$<br>input code between lowest and<br>highest possible ones. |  |  |  |

| PSRR+ <sup>(1)</sup>                      | Power supply rejection ratio (to V <sub>DDA</sub> ) (static DC measurement                                                                                       | -   | -67 | -40                | dB   | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF                                                             |  |  |  |

1. Guaranteed by characterization results.

2. Guaranteed by design.

The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

# 6 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

# 6.1 LQFP100 package information

#### Figure 37. LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat package outline

1. Drawing is not to scale. Dimensions are in millimeters.

# 6.2 LQFP64 package information

Figure 40.LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package outline

1. Drawing is not in scale.

| Table 49. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package |

|---------------------------------------------------------------------|

| mechanical data                                                     |

| Current e l | millimeters |        |       | inches <sup>(1)</sup> |        |        |

|-------------|-------------|--------|-------|-----------------------|--------|--------|

| Symbol      | Min         | Тур    | Max   | Min                   | Тур    | Мах    |

| А           | -           | -      | 1.600 | -                     | -      | 0.0630 |

| A1          | 0.050       | -      | 0.150 | 0.0020                | -      | 0.0059 |

| A2          | 1.350       | 1.400  | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b           | 0.170       | 0.220  | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| С           | 0.090       | -      | 0.200 | 0.0035                | -      | 0.0079 |

| D           | -           | 12.000 | -     | -                     | 0.4724 | -      |

| D1          | -           | 10.000 | -     | -                     | 0.3937 | -      |

| D3          | -           | 7.500  | -     | -                     | 0.2953 | -      |

| E           | -           | 12.000 | -     | -                     | 0.4724 | -      |

| E1          | -           | 10.000 | -     | -                     | 0.3937 | -      |

| E3          | -           | 7.500  | -     | -                     | 0.2953 | -      |

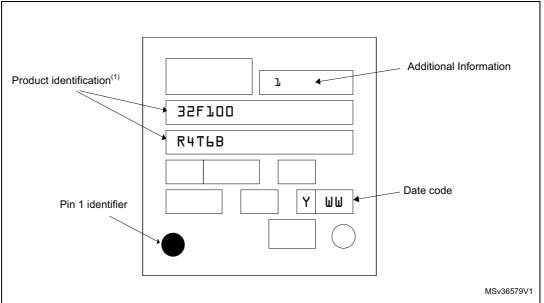

### **Device marking for LQFP64**

The following figure gives an example of topside marking and pin 1 position identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 42. LQFP64 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

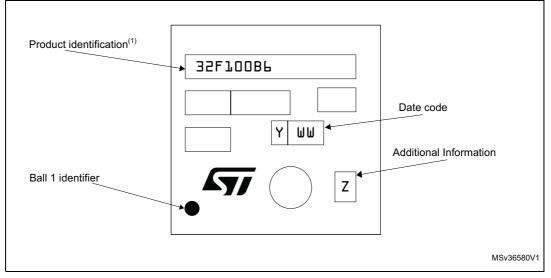

#### **Device marking for TFBGA64**

The following figure gives an example of topside marking and pin 1 position identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID16455 Rev 9