Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | ARM® Cortex®-M3                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 24MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | DMA, PDR, POR, PVD, PWM, Temp Sensor, WDT                                |

| Number of I/O              | 51                                                                       |

| Program Memory Size        | 64KB (64K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                    |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-LQFP                                                                  |

| Supplier Device Package    | 64-LQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f100r8t7btr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## List of tables

| Table 1.  | Device summary                                                            |    |

|-----------|---------------------------------------------------------------------------|----|

| Table 2.  | STM32F100xx features and peripheral counts                                | 11 |

| Table 3.  | Timer feature comparison                                                  |    |

| Table 4.  | Low & medium-density STM32F100xx pin definitions                          |    |

| Table 5.  | Voltage characteristics                                                   |    |

| Table 6.  | Current characteristics                                                   |    |

| Table 7.  | Thermal characteristics.                                                  |    |

| Table 8.  | General operating conditions                                              |    |

| Table 9.  | Operating conditions at power-up / power-down                             |    |

| Table 10. | Embedded reset and power control block characteristics.                   |    |

| Table 11. | Embedded internal reference voltage                                       |    |

| Table 12. | Maximum current consumption in Run mode, code with data processing        |    |

|           | running from Flash                                                        | 38 |

| Table 13. | Maximum current consumption in Run mode, code with data processing        |    |

|           | running from RAM.                                                         | 38 |

| Table 14. | Maximum current consumption in Sleep mode, code running from Flash or RAM |    |

| Table 15. | Typical and maximum current consumptions in Stop and Standby modes        |    |

| Table 15. | Typical current consumption in Run mode, code with data processing        | 40 |

|           | running from Flash                                                        | 12 |

| Table 17. | Typical current consumption in Sleep mode, code running from Flash or RAM |    |

| Table 17. | Peripheral current consumption                                            |    |

| Table 18. |                                                                           |    |

|           | High-speed external user clock characteristics.                           |    |

| Table 20. | Low-speed external user clock characteristics                             |    |

| Table 21. | HSE 4-24 MHz oscillator characteristics.                                  |    |

| Table 22. | LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz)            |    |

| Table 23. | HSI oscillator characteristics.                                           |    |

| Table 24. | LSI oscillator characteristics                                            |    |

| Table 25. | Low-power mode wakeup timings                                             |    |

| Table 26. | PLL characteristics                                                       |    |

| Table 27. | Flash memory characteristics                                              |    |

| Table 28. | Flash memory endurance and data retention                                 |    |

| Table 29. | EMS characteristics                                                       |    |

| Table 30. | EMI characteristics                                                       |    |

| Table 31. | ESD absolute maximum ratings                                              |    |

| Table 32. | Electrical sensitivities                                                  |    |

| Table 33. | I/O current injection susceptibility                                      |    |

| Table 34. | I/O static characteristics                                                |    |

| Table 35. | Output voltage characteristics                                            | 60 |

| Table 36. | I/O AC characteristics                                                    | 61 |

| Table 37. | NRST pin characteristics                                                  | 62 |

| Table 38. | TIMx characteristics                                                      |    |

| Table 39. | I <sup>2</sup> C characteristics                                          | 64 |

| Table 40. | SCL frequency (f <sub>PCLK1</sub> = 24 MHz, V <sub>DD</sub> = 3.3 V)      | 65 |

| Table 41. | SPI characteristics                                                       |    |

| Table 42. | ADC characteristics                                                       |    |

| Table 43. | R <sub>AIN</sub> max for f <sub>ADC</sub> = 12 MHz                        |    |

| Table 44. | ADC accuracy - limited test conditions                                    | 70 |

| Table 45. | ADC accuracy                                                              |    |

## 2.1 Device overview

The description below gives an overview of the complete range of peripherals proposed in this family.

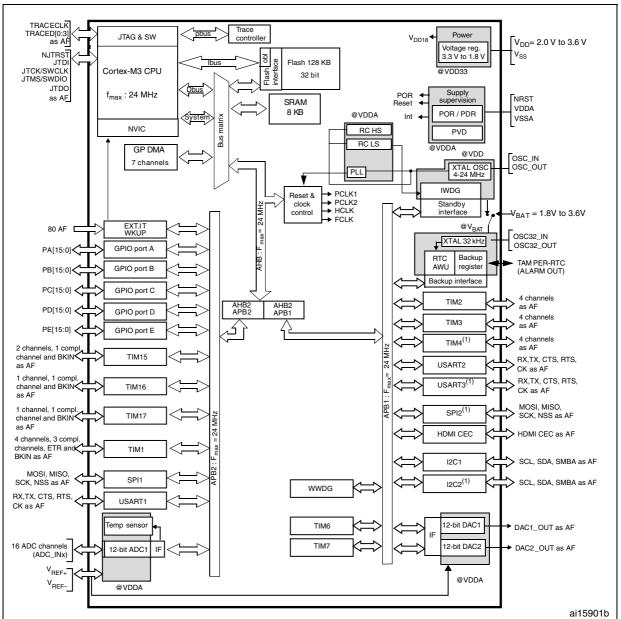

*Figure 1* shows the general block diagram of the device family.

| r                 |                                                                                                                                                  |                  |     |             |             |                |        |             |     |    |     |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|-------------|-------------|----------------|--------|-------------|-----|----|-----|

| Peri              | STM32F100Cx                                                                                                                                      |                  |     | STM32F100Rx |             |                |        | STM32F100Vx |     |    |     |

| Flash - Kbytes    |                                                                                                                                                  | 16               | 32  | 64          | 128         | 16             | 32     | 64          | 128 | 64 | 128 |

| SRAM - Kbytes     |                                                                                                                                                  | 4                | 4   | 8           | 8           | 4              | 4      | 8           | 8   | 8  | 8   |

| Timers            | Advanced-control                                                                                                                                 |                  | 1   |             | 1           |                | 1      |             | 1   |    | 1   |

| Timers            | General-purpose                                                                                                                                  | 5                | (1) | (           | 6           | 5(             | [1)    | (           | 6   |    | 6   |

|                   | SPI                                                                                                                                              | 1                | (2) | :           | 2           | 1 <sup>(</sup> | (2)    | :           | 2   |    | 2   |

| Communication     | l <sup>2</sup> C                                                                                                                                 | 1                | (3) | :           | 2           | 1(             | (3)    | :           | 2   |    | 2   |

| interfaces        | USART                                                                                                                                            | 2 <sup>(4)</sup> |     | ;           | 3           |                | (4)    | 3           |     | 3  |     |

|                   | CEC                                                                                                                                              |                  |     |             | 1           |                |        |             |     |    |     |

| 12-bit synchroniz | zed ADC                                                                                                                                          | 1                |     |             | 1           |                |        | 1           |     |    |     |

| number of chanr   | nels                                                                                                                                             | 10 channels      |     |             | 16 channels |                |        | 16 channels |     |    |     |

| GPIOs             |                                                                                                                                                  | 37               |     |             | 51          |                |        | 80          |     |    |     |

| 12-bit DAC        |                                                                                                                                                  | 2                |     |             |             |                |        |             |     |    |     |

| Number of chann   | nels                                                                                                                                             | 2                |     |             |             |                |        |             |     |    |     |

| CPU frequency     |                                                                                                                                                  |                  |     |             |             |                | 24 MHz | 2           |     |    |     |

| Operating voltag  | le                                                                                                                                               | 2.0 to 3.6 V     |     |             |             |                |        |             |     |    |     |

| Operating tempe   | Ambient operating temperature: -40 to +85 °C /-40 to +105 °C (see <i>Table 8</i> )<br>Junction temperature: -40 to +125 °C (see <i>Table 8</i> ) |                  |     |             |             |                |        |             |     |    |     |

| Packages          | LQFP48 LQFP64, TFBGA64 LQFF                                                                                                                      |                  |     |             |             | FP100          |        |             |     |    |     |

1. TIM4 not present.

2. SPI2 is not present.

3. I2C2 is not present.

4. USART3 is not present.

Figure 1. STM32F100xx value line block diagram

1. Peripherals not present in low-density value line devices.

2. AF = alternate function on I/O port pin.

3.  $T_A = -40$  °C to +85 °C (junction temperature up to 105 °C) or  $T_A = -40$  °C to +105 °C (junction temperature up to 125 °C).

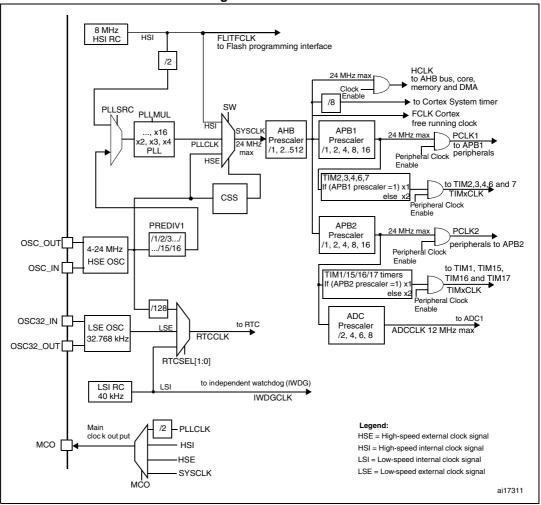

Figure 2. Clock tree

1. To have an ADC conversion time of 1.2  $\mu s,$  APB2 must be at 24 MHz.

## 2.2 Overview

## 2.2.1 ARM<sup>®</sup> Cortex<sup>®</sup>-M3 core with embedded Flash and SRAM

The ARM<sup>®</sup> Cortex<sup>®</sup>-M3 processor is the latest generation of ARM processors for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM Cortex<sup>®</sup>-M3 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The STM32F100xx value line family having an embedded ARM core, is therefore compatible with all ARM tools and software.

## 2.2.2 Embedded Flash memory

Up to 128 Kbytes of embedded Flash memory is available for storing programs and data.

## 2.2.3 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

## 2.2.4 Embedded SRAM

Up to 8 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states.

## 2.2.5 Nested vectored interrupt controller (NVIC)

The STM32F100xx value line embeds a nested vectored interrupt controller able to handle up to 41 maskable interrupt channels (not including the 16 interrupt lines of  $Cortex^{\mbox{\ensuremath{\mathbb{R}}}}$ -M3) and 16 priority levels.

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of *late arriving* higher priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

DocID16455 Rev 9

## 2.2.6 External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 18 edge detector lines used to generate interrupt/event requests. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 80 GPIOs can be connected to the 16 external interrupt lines.

## 2.2.7 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-24 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example on failure of an indirectly used external crystal, resonator or oscillator).

Several prescalers allow the configuration of the AHB frequency, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the AHB and the APB domains is 24 MHz.

## 2.2.8 Boot modes

At startup, boot pins are used to select one of three boot options:

- Boot from user Flash

- Boot from system memory

- Boot from embedded SRAM

The boot loader is located in System Memory. It is used to reprogram the Flash memory by using USART1. For further details please refer to AN2606.

## 2.2.9 **Power supply schemes**

- $V_{DD}$  = 2.0 to 3.6 V: External power supply for I/Os and the internal regulator. Provided externally through  $V_{DD}$  pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 2.0 to 3.6 V: External analog power supplies for ADC, DAC, Reset blocks, RCs and PLL (minimum voltage to be applied to V<sub>DDA</sub> is 2.4 V when the ADC or DAC is used).

$V_{DDA}$  and  $V_{SSA}$  must be connected to  $V_{DD}$  and  $V_{SS},$  respectively.

• V<sub>BAT</sub> = 1.8 to 3.6 V: Power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

## 2.2.10 Power supply supervisor

The device has an integrated power on reset (POR)/power down reset (PDR) circuitry. It is always active, and ensures proper operation starting from/down to 2 V. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$ , without the need for an external reset circuit.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is

Their counters can be frozen in debug mode.

#### Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger generation. They can also be used as a generic 16-bit time base.

#### Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

## Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

## SysTick timer

This timer is dedicated for OS, but could also be used as a standard down counter. It features:

- A 24-bit down counter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0.

- Programmable clock source

## 2.2.16 I<sup>2</sup>C bus

The I<sup>2</sup>C bus interface can operate in multimaster and slave modes. It can support standard and fast modes.

It supports dual slave addressing (7-bit only) and both 7/10-bit addressing in master mode. A hardware CRC generation/verification is embedded. The interface can be served by DMA and it supports SM Bus 2.0/PM Bus.

## 2.2.17 Universal synchronous/asynchronous receiver transmitter (USART)

The STM32F100xx value line embeds three universal synchronous/asynchronous receiver transmitters (USART1, USART2 and USART3).

The available USART interfaces communicate at up to 3 Mbit/s. They provide hardware management of the CTS and RTS signals, they support IrDA SIR ENDEC, the multiprocessor communication mode, the single-wire half-duplex communication mode and have LIN Master/Slave capability.

The USART interfaces can be served by the DMA controller.

|         | Pi     | ns      |        |                               |                     | y 31<br>ล                  |                                                  | Alternate function                                                                                |                          |

|---------|--------|---------|--------|-------------------------------|---------------------|----------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------|

| LQFP100 | LQFP64 | TFBGA64 | LQFP48 | Pin name                      | Type <sup>(1)</sup> | I / O level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                                                           | Remap                    |

| 9       | 4      | B1      | 4      | PC15-OSC32_OUT <sup>(5)</sup> | I/O                 | -                          | PC15 <sup>(6)</sup>                              | OSC32_OUT                                                                                         | -                        |

| 10      | -      | -       | -      | V <sub>SS_5</sub>             | S                   | -                          | V <sub>SS_5</sub>                                | -                                                                                                 | -                        |

| 11      | -      | -       | -      | V <sub>DD_5</sub>             | S                   | -                          | $V_{DD_5}$                                       | -                                                                                                 | -                        |

| 12      | 5      | C1      | 5      | OSC_IN                        | Ι                   | -                          | OSC_IN                                           | -                                                                                                 | PD0 <sup>(7)</sup>       |

| 13      | 6      | D1      | 6      | OSC_OUT                       | 0                   | -                          | OSC_OUT                                          | -                                                                                                 | PD1 <sup>(7)</sup>       |

| 14      | 7      | E1      | 7      | NRST                          | I/O                 | -                          | NRST                                             | -                                                                                                 | -                        |

| 15      | 8      | E3      | -      | PC0                           | I/O                 | -                          | PC0                                              | ADC1_IN10                                                                                         | -                        |

| 16      | 9      | E2      | -      | PC1                           | I/O                 | -                          | PC1                                              | ADC1_IN11                                                                                         | -                        |

| 17      | 10     | F2      | -      | PC2                           | I/O                 | -                          | PC2                                              | ADC1_IN12                                                                                         | -                        |

| 18      | 11     | _(8)    | -      | PC3                           | I/O                 | -                          | PC3                                              | ADC1_IN13                                                                                         | -                        |

| 19      | 12     | F1      | 8      | V <sub>SSA</sub>              | S                   | -                          | V <sub>SSA</sub>                                 | -                                                                                                 | -                        |

| 20      | -      | -       | -      | V <sub>REF-</sub>             | S                   | -                          | V <sub>REF-</sub>                                | -                                                                                                 | -                        |

| 21      | -      | G1      | -      | V <sub>REF+</sub>             | S                   | -                          | V <sub>REF+</sub>                                | -                                                                                                 | -                        |

| 22      | 13     | H1      | 9      | V <sub>DDA</sub>              | S                   | -                          | V <sub>DDA</sub>                                 | -                                                                                                 | -                        |

| 23      | 14     | G2      | 10     | PA0-WKUP                      | I/O                 | -                          | PA0                                              | WKUP / USART2_CTS <sup>(12)</sup> /<br>ADC1_IN0 /<br>TIM2_CH1_ETR <sup>(12)</sup>                 | -                        |

| 24      | 15     | H2      | 11     | PA1                           | I/O                 | -                          | PA1                                              | USART2_RTS <sup>(12)</sup> /<br>ADC1_IN1 / TIM2_CH2 <sup>(12)</sup>                               | -                        |

| 25      | 16     | F3      | 12     | PA2                           | I/O                 | -                          | PA2                                              | USART2_TX <sup>(12)</sup> /<br>ADC1_IN2 / TIM2_CH3 <sup>(12)</sup> /<br>TIM15_CH1 <sup>(12)</sup> | -                        |

| 26      | 17     | G3      | 13     | PA3                           | I/O                 | -                          | PA3                                              | USART2_RX <sup>(12)</sup> /<br>ADC1_IN3 / TIM2_CH4 <sup>(12)</sup><br>/ TIM15_CH2 <sup>(12)</sup> | -                        |

| 27      | 18     | C2      | -      | V <sub>SS_4</sub>             | S                   | -                          | V <sub>SS_4</sub>                                | -                                                                                                 | -                        |

| 28      | 19     | D2      | -      | V <sub>DD_4</sub>             | S                   | -                          | V <sub>DD_4</sub>                                | -                                                                                                 | -                        |

| 29      | 20     | H3      | 14     | PA4                           | I/O                 | -                          | PA4                                              | SPI1_NSS <sup>(12)</sup> /ADC1_IN4<br>USART2_CK <sup>(12)</sup> /<br>DAC1_OUT                     | -                        |

| 30      | 21     | F4      | 15     | PA5                           | I/O                 | -                          | PA5                                              | SPI1_SCK <sup>(12)</sup> /ADC1_IN5 /<br>DAC2_OUT                                                  | -                        |

| 31      | 22     | G4      | 16     | PA6                           | I/O                 | -                          | PA6                                              | SPI1_MISO <sup>(12)</sup> /ADC1_IN6/<br>TIM3_CH1 <sup>(12)</sup>                                  | TIM1_BKIN /<br>TIM16_CH1 |

| 32      | 23     | H4      | 17     | PA7                           | I/O                 | -                          | PA7                                              | SPI1_MOSI <sup>(12)</sup> /ADC1_IN7/<br>TIM3_CH2 <sup>(12)</sup>                                  | TIM1_CH1N<br>/ TIM17_CH1 |

Table 4. Low & medium-density STM32F100xx pin definitions (continued)

DocID16455 Rev 9

25/96

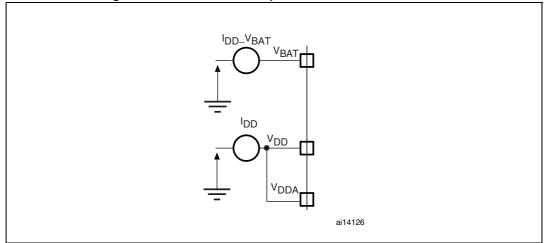

## 5.1.7 Current consumption measurement

#### Figure 11. Current consumption measurement scheme

## 5.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 5: Voltage characteristics*, *Table 6: Current characteristics*, and *Table 7: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                            | Ratings                                                                          | Min                                     | Мах                  | Unit |

|-----------------------------------|----------------------------------------------------------------------------------|-----------------------------------------|----------------------|------|

| V <sub>DD</sub> –V <sub>SS</sub>  | External main supply voltage (including $V_{DDA}$ and $V_{DD})^{\left(1\right)}$ | -0.3                                    | 4.0                  |      |

| V <sub>IN</sub> <sup>(2)</sup>    | Input voltage on five volt tolerant pin                                          | V <sub>SS</sub> -0.3                    | V <sub>DD</sub> +4.0 | V    |

| VIN <sup>(=)</sup>                | Input voltage on any other pin                                                   | V <sub>SS</sub> -0.3                    | 4.0                  |      |

| ΔV <sub>DDx</sub>                 | Variations between different V <sub>DD</sub> power pins                          | -                                       | 50                   |      |

| V <sub>SSX</sub> -V <sub>SS</sub> | Variations between all the different ground pins                                 | -                                       | 50                   | mV   |

| V <sub>ESD(HBM)</sub>             | Electrostatic discharge voltage (human body model)                               | see Section 5.<br>maximum rati<br>sensi | -                    |      |

#### Table 5. Voltage characteristics

All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 6: Current characteristics* for the maximum allowed injected current values.

## 5.3.4 Embedded reference voltage

The parameters given in *Table 11* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

| Symbol                                | Parameter                                                           | Conditions                        | Min  | Тур  | Мах                 | Unit   |

|---------------------------------------|---------------------------------------------------------------------|-----------------------------------|------|------|---------------------|--------|

| V                                     | Internal reference voltage                                          | –40 °C < T <sub>A</sub> < +105 °C | 1.16 | 1.20 | 1.26                | V      |

| V <sub>REFINT</sub>                   | Internal reference voltage                                          | –40 °C < T <sub>A</sub> < +85 °C  | 1.16 | 1.20 | 1.24                | V      |

| T <sub>S_vrefint</sub> <sup>(1)</sup> | ADC sampling time when<br>reading the internal<br>reference voltage | -                                 | -    | 5.1  | 17.1 <sup>(2)</sup> | μs     |

| V <sub>RERINT</sub> <sup>(2)</sup>    | Internal reference voltage spread over the temperature range        | V <sub>DD</sub> = 3 V ±10 mV      | -    | -    | 10                  | mV     |

| T <sub>Coeff</sub> <sup>(2)</sup>     | Temperature coefficient                                             | -                                 | -    | -    | 100                 | ppm/°C |

Table 11. Embedded internal reference voltage

1. Shortest sampling time can be determined in the application by multiple iterations.

2. Guaranteed by design.

## 5.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 11: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to Dhrystone 2.1 code.

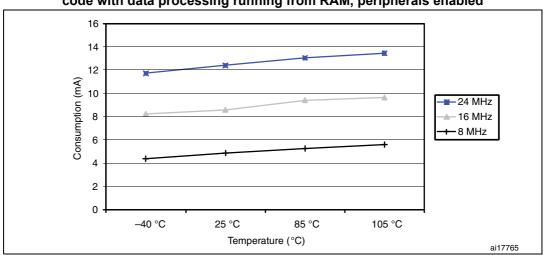

## Maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load)

- All peripherals are disabled except if it is explicitly mentioned

- Prefetch in on (reminder: this bit must be set before clock setting and bus prescaling)

- When the peripherals are enabled f<sub>PCLK1</sub> = f<sub>HCLK</sub>/2, f<sub>PCLK2</sub> = f<sub>HCLK</sub>

The parameters given in *Table 12* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

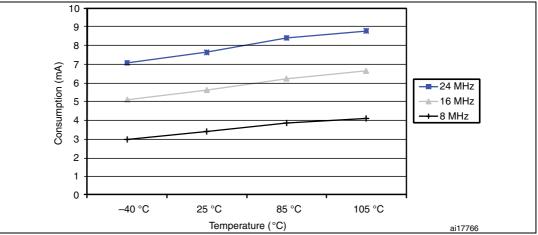

Figure 12. Maximum current consumption in Run mode versus frequency (at 3.6 V) - code with data processing running from RAM, peripherals enabled

Figure 13. Maximum current consumption in Run mode versus frequency (at 3.6 V) - code with data processing running from RAM, peripherals disabled

Table 14. Maximum current consumption in Sleep mode, code running from Flash or RAM

| Cumhal | Deremeter                       | Conditions                                            | £                 | Ма                     | Unit                    |      |  |

|--------|---------------------------------|-------------------------------------------------------|-------------------|------------------------|-------------------------|------|--|

| Symbol | Parameter                       | Conditions                                            | f <sub>HCLK</sub> | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |  |

|        | Supply current<br>in Sleep mode | External clock <sup>(2)</sup> all peripherals enabled | 24 MHz            | 9.6                    | 10                      |      |  |

|        |                                 |                                                       | 16 MHz            | 7.1                    | 7.5                     |      |  |

|        |                                 |                                                       | 8 MHz             | 4.5                    | 4.8                     | m 4  |  |

| IDD    |                                 |                                                       | 24 MHz            | 3.8                    | 4                       | mA   |  |

|        |                                 |                                                       | 16 MHz            | 3.3                    | 3.5                     |      |  |

|        |                                 | F F                                                   | 8 MHz             | 2.7                    | 3                       |      |  |

1. Guaranteed by characterization, tested in production at  $V_{DD}$  max and  $f_{HCLK}$  max with peripherals enabled.

2. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

|                      |                                         |                                                                                                                                                   |                                                  | Тур <sup>(1)</sup>                               |                                                  |                           |                            |      |

|----------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|---------------------------|----------------------------|------|

| Symbol               | Parameter                               | Conditions                                                                                                                                        | V <sub>DD</sub> /<br>V <sub>BAT</sub><br>= 2.0 V | V <sub>DD</sub> /<br>V <sub>BAT</sub> =<br>2.4 V | V <sub>DD</sub> /<br>V <sub>BAT</sub><br>= 3.3 V | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                      | Supply<br>current in<br>Stop mode       | Regulator in Run mode,<br>Low-speed and high-speed<br>internal RC oscillators and<br>high-speed oscillator OFF (no<br>independent watchdog)       | -                                                | 23.5                                             | 24                                               | 190                       | 350                        |      |

|                      |                                         | Regulator in Low-Power mode,<br>Low-speed and high-speed<br>internal RC oscillators and<br>high-speed oscillator OFF (no<br>independent watchdog) | -                                                | 13.5                                             | 14                                               | 170                       | 330                        |      |

| I <sub>DD</sub>      | Supply<br>current in<br>Standby<br>mode | Low-speed internal RC<br>oscillator and independent<br>watchdog ON                                                                                | -                                                | 2.6                                              | 3.4                                              | -                         | -                          | μA   |

|                      |                                         | Low-speed internal RC<br>oscillator ON, independent<br>watchdog OFF                                                                               | -                                                | 2.4                                              | 3.2                                              | -                         | -                          |      |

|                      |                                         | Low-speed internal RC<br>oscillator and independent<br>watchdog OFF, low-speed<br>oscillator and RTC OFF                                          | -                                                | 1.7                                              | 2                                                | 4                         | 5                          |      |

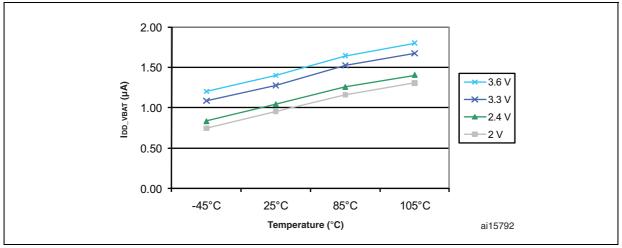

| I <sub>DD_VBAT</sub> | Backup<br>domain<br>supply current      | Low-speed oscillator and RTC<br>ON                                                                                                                | 0.9                                              | 1.1                                              | 1.4                                              | 1.9                       | 2.2                        |      |

| Table 15. Typical and maximum current consu | motions in Stop and Standby modes  |

|---------------------------------------------|------------------------------------|

| Table 15. Typical and maximum current consu | inplions in Slop and Standby modes |

1. Typical values are measured at  $T_A = 25$  °C.

# Figure 14. Typical current consumption on $\rm V_{BAT}$ with RTC on vs. temperature at different $\rm V_{BAT}$ values

#### Low-speed external user clock generated from an external source

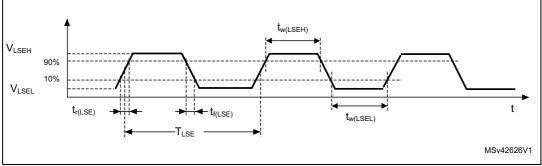

The characteristics given in *Table 20* result from tests performed using an low-speed external clock source, and under the ambient temperature and supply voltage conditions summarized in *Table 8*.

| Symbol                                       | Parameter                                              | Conditions                       | Min                | Тур    | Max                | Unit |

|----------------------------------------------|--------------------------------------------------------|----------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                         | User external clock source<br>frequency <sup>(1)</sup> |                                  | -                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage <sup>(1)</sup>   |                                  | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | V    |

| V <sub>LSEL</sub>                            | OSC32_IN input pin low level voltage <sup>(1)</sup>    |                                  | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> | v    |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time <sup>(1)</sup>               | -                                | 450                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub>   | OSC32_IN rise or fall time <sup>(1)</sup>              |                                  | -                  | -      | 50                 | 115  |

| C <sub>in(LSE)</sub>                         | OSC32_IN input capacitance <sup>(1)</sup>              |                                  | -                  | 5      | -                  | pF   |

| DuCy <sub>(LSE)</sub>                        | Duty cycle <sup>(1)</sup>                              |                                  | 30                 | -      | 70                 | %    |

| ١L                                           | OSC32_IN Input leakage current                         | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -      | ±1                 | μA   |

Table 20. Low-speed external user clock characteristics

1. Guaranteed by design.

## High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 24 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 21*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

## Low-speed internal (LSI) RC oscillator

| Table 24. LSI oso | illator characteristics <sup>(1)</sup> | ) |

|-------------------|----------------------------------------|---|

|-------------------|----------------------------------------|---|

| Symbol                              | Parameter                                          | Min | Тур  | Мах | Unit |

|-------------------------------------|----------------------------------------------------|-----|------|-----|------|

| f <sub>LSI</sub>                    | Frequency                                          | 30  | 40   | 60  | kHz  |

| $\Delta f_{LSI(T)}$                 | Temperature-related frequency drift <sup>(2)</sup> | -9  | -    | 9   | %    |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time                        | -   | -    | 85  | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption                   | -   | 0.65 | 1.2 | μA   |

1.  $V_{DD}$  = 3 V,  $T_A$  = -40 to 105 °C °C unless otherwise specified.

2. Guaranteed by characterization results.

3. Guaranteed by design.

#### Wakeup time from low-power mode

The wakeup times given in *Table 25* are measured on a wakeup phase with an 8-MHz HSI RC oscillator. The clock source used to wake up the device depends from the current operating mode:

- Stop or Standby mode: the clock source is the RC oscillator

- Sleep mode: the clock source is the clock that was set before entering Sleep mode.

All timings are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

| Symbol                              | Parameter                                           | Тур | Unit |

|-------------------------------------|-----------------------------------------------------|-----|------|

| t <sub>WUSLEEP</sub> <sup>(1)</sup> | Wakeup from Sleep mode                              | 1.8 | μs   |

| twustop <sup>(1)</sup>              | Wakeup from Stop mode (regulator in run mode)       | 3.6 |      |

| 'WUSTOP'                            | Wakeup from Stop mode (regulator in low-power mode) | 5.4 | μs   |

| t <sub>WUSTDBY</sub> <sup>(1)</sup> | Wakeup from Standby mode                            | 50  | μs   |

Table 25. Low-power mode wakeup timings

1. The wakeup times are measured from the wakeup event to the point at which the user application code reads the first instruction.

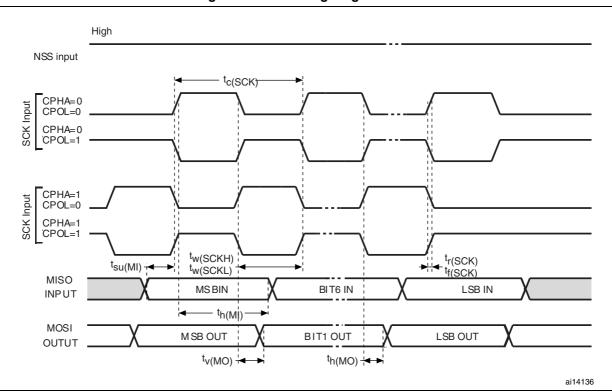

Figure 31. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

#### HDMI consumer electronics control (CEC)

Refer to *Section 5.3.12: I/O current injection characteristics* for more details on the input/output alternate function characteristics.

## 5.3.17 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 42* are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 8*.

Note: It is recommended to perform a calibration after each power-up.

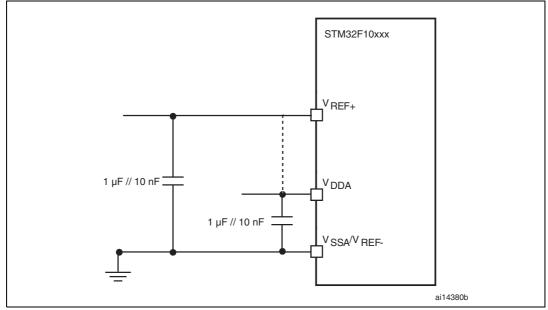

Figure 34. Power supply and reference decoupling ( $V_{REF+}$  not connected to  $V_{DDA}$ )

1.  $V_{\text{REF+}}$  is available on 100-pin packages and on TFBGA64 packages.  $V_{\text{REF-}}$  is available on 100-pin packages only.

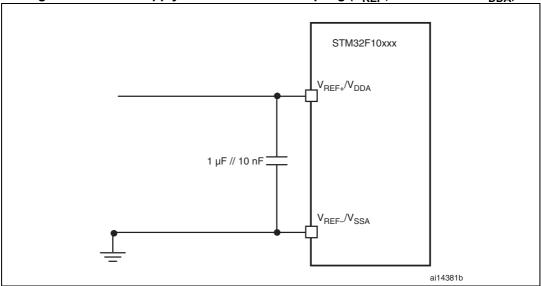

Figure 35. Power supply and reference decoupling ( $V_{REF+}$  connected to  $V_{DDA}$ )

1.  $V_{REF+}$  and  $V_{REF-}$  inputs are available only on 100-pin packages.

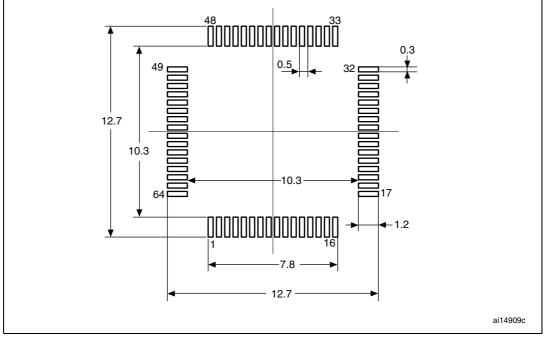

| Symbol |       | millimeters |       | inches <sup>(1)</sup> |        |        |

|--------|-------|-------------|-------|-----------------------|--------|--------|

|        | Min   | Тур         | Мах   | Min                   | Тур    | Мах    |

| е      | -     | 0.500       | -     | -                     | 0.0197 | -      |

| К      | 0°    | 3.5°        | 7°    | 0°                    | 3.5°   | 7°     |

| L      | 0.450 | 0.600       | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1     | -     | 1.000       | -     | -                     | 0.0394 | -      |

| CCC    | -     | -           | 0.080 | -                     | -      | 0.0031 |

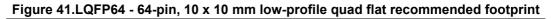

# Table 49. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat packagemechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are in millimeters.

# Table 50. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ballgrid array package mechanical data

| Symbol |     | millimeters |       |     | inches <sup>(1)</sup> |        |

|--------|-----|-------------|-------|-----|-----------------------|--------|

|        | Min | Тур         | Max   | Min | Тур                   | Мах    |

| E1     | -   | 3.500       | -     | -   | 0.1378                | -      |

| е      | -   | 0.500       | -     | -   | 0.0197                | -      |

| F      | -   | 0.750       | -     | -   | 0.0295                | -      |

| ddd    | -   | -           | 0.080 | -   | -                     | 0.0031 |

| eee    | -   | -           | 0.150 | -   | -                     | 0.0059 |

| fff    | -   | -           | 0.050 | -   | -                     | 0.0020 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

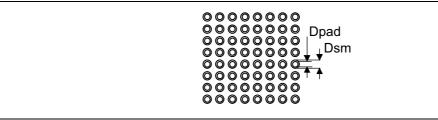

## Figure 44. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball grid array, recommended footprint

## Table 51. TFBGA64 recommended PCB design rules (0.5 mm pitch BGA) Image: Comparison of the second secon

| Dimension         | Recommended values                                               |  |

|-------------------|------------------------------------------------------------------|--|

| Pitch             | 0.5                                                              |  |

| Dpad              | 0.280 mm                                                         |  |

| Dsm               | 0.370 mm typ. (depends on the soldermask registration tolerance) |  |

| Stencil opening   | 0.280 mm                                                         |  |

| Stencil thickness | Between 0.100 mm and 1.125 mm                                    |  |

| Pad trace width   | 0.100 mm                                                         |  |

R8\_FP\_V1

## 6.4 LQFP48 package information

SEATING PLANE A2 F 0.25 mm GAUGE PLANE ĸ D A1 D1 L1 D3 24 37 Œ b **CHE** <u>ш</u> ш Ē ----------£ 48 13 PIN 1 IDENTIFICATION 1 12 e 5B\_ME\_V2

Figure 46. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline

1. Drawing is not to scale.

| Table 52. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package |

|-------------------------------------------------------------------|

| mechanical data                                                   |

|        | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур   | Мах   | Min                   | Тур    | Max    |

| А      | -           | -     | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220 | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090       | -     | 0.200 | 0.0035                | -      | 0.0079 |

| D      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |

| D1     | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |

| D3     | -           | 5.500 | -     | -                     | 0.2165 | -      |

| Е      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |

## 8 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 12-Oct-2009 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 26-Feb-2010 | 2        | <ul> <li>TFBGA64 package added (see Table 50 and Table 41).</li> <li>Note 5 modified in Table 4: Low &amp; medium-density STM32F100xx pin definitions.</li> <li>I<sub>INJ(PIN)</sub> modified in Table 6: Current characteristics. Conditions removed from Table 25: Low-power mode wakeup timings.</li> <li>Notes modified in Table 34: I/O static characteristics.</li> <li>Figure 27: Recommended NRST pin protection modified.</li> <li>Note modified in Table 39: I/O static characteristics. Figure 28: I2C bus AC waveforms and measurement circuit(1) modified.</li> <li>Table 46: DAC characteristics modified. Figure 36: 12-bit buffered /non-buffered DAC added.</li> <li>TIM2, TIM3, TIM4 and TIM15, TIM16 and TIM17 updated.</li> <li>HDMI-CEC electrical characteristics added.</li> <li>Values added to:</li> <li>Table 12: Maximum current consumption in Run mode, code with data processing running from Flash</li> <li>Table 13: Maximum current consumption in Sleep mode, code running from Flash or RAM</li> <li>Table 15: Typical and maximum current consumptions in Stop and Standby modes</li> <li>Table 18: Peripheral current consumption</li> <li>Table 29: EMS characteristics</li> <li>Table 19: Characteristics</li> <li>Table 19: TS characteristics</li> <li>Table 19: TS characteristics</li> <li>Table 19: TS characteristics</li> <li>Figure 12: Maximum current consumption in Run mode versus frequency (at 3.6 V) - code with data processing running from RAM, peripherals enabled</li> <li>Figure 13: Maximum current consumption in Run mode versus frequency (at 3.6 V) - code with data processing running from RAM, peripherals disabled</li> <li>Figure 15: Typical current consumption in Stop mode with regulator in Run mode versus temperature at VDD = 3.3 V and 3.6 V</li> <li>Figure 16: Typical current consumption in Stop mode with regulator in Run mode versus temperature at VDD = 3.3 V and 3.6 V</li> <li>Figure 16: Typical current consumption in Standby mode versus temperature at VDD = 3.3 V and 3.6 V</li> </ul> |  |  |