Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | ARM® Cortex®-M3                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 24MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | DMA, PDR, POR, PVD, PWM, Temp Sensor, WDT                                |

| Number of I/O              | 51                                                                       |

| Program Memory Size        | 128KB (128K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                    |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-LQFP                                                                  |

| Supplier Device Package    | 64-LQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f100rbt6btr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

# 2.2.11 Voltage regulator

The regulator has three operation modes: main (MR), low power (LPR) and power down.

- MR is used in the nominal regulation mode (Run)

- LPR is used in the Stop mode

- Power down is used in Standby mode: the regulator output is in high impedance: the kernel circuitry is powered down, inducing zero consumption (but the contents of the registers and SRAM are lost)

This regulator is always enabled after reset. It is disabled in Standby mode, providing high impedance output.

## 2.2.12 Low-power modes

The STM32F100xx value line supports three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

• Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

• Stop mode

Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low power mode.

The device can be woken up from Stop mode by any of the EXTI line. The EXTI line source can be one of the 16 external lines, the PVD output or the RTC alarm.

• Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.8 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, SRAM and register contents are lost except for registers in the Backup domain and Standby circuitry.

The device exits Standby mode when an external reset (NRST pin), a IWDG reset, a rising edge on the WKUP pin, or an RTC alarm occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped by entering Stop or Standby mode.

#### 2.2.13 DMA

The flexible 7-channel general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The DMA controller supports circular buffer management avoiding the generation of interrupts when the controller reaches the end of the buffer.

### 2.2.23 DAC (digital-to-analog converter)

The two 12-bit buffered DAC channels can be used to convert two digital signals into two analog voltage signal outputs. The chosen design structure is composed of integrated resistor strings and an amplifier in noninverting configuration.

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- up to 10-bit output

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channels' independent or simultaneous conversions

- DMA capability for each channel

- external triggers for conversion

- input voltage reference V<sub>REF+</sub>

Eight DAC trigger inputs are used in the STM32F100xx. The DAC channels are triggered through the timer update outputs that are also connected to different DMA channels.

#### 2.2.24 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 2 V <  $V_{DDA}$  < 3.6 V. The temperature sensor is internally connected to the ADC1\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

### 2.2.25 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP Interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target. The JTAG TMS and TCK pins are shared respectively with SWDIO and SWCLK and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

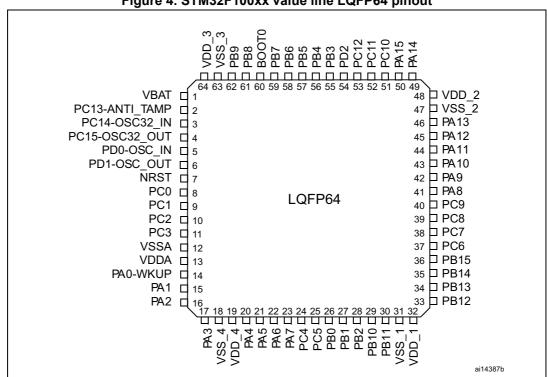

Figure 4. STM32F100xx value line LQFP64 pinout

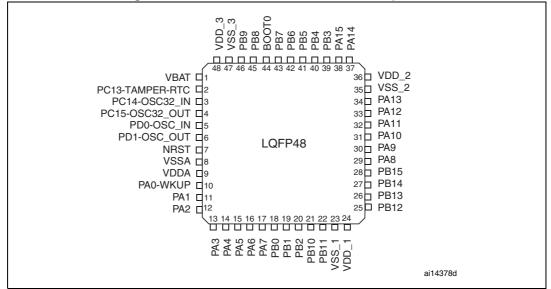

#### Figure 5. STM32F100xx value line LQFP48 pinout

DocID16455 Rev 9

|   | 1                          | 2                    | 3       | 4       | 5       | 6 IFBGA                  | 7       | 8      |

|---|----------------------------|----------------------|---------|---------|---------|--------------------------|---------|--------|

| A | •<br>/PC14-,<br>0\&C32_lNT | , PC13-,<br>AMPER-RT | ( PB9 ) | ( PB4 ) | (PB3)   | (PA15)                   | (PA14)  | (PA13) |

| в | , PC15-,<br>OSC32_OUT      | VBAT)                | ( PB8 ) | воото   | (PD2)   | (PC11)                   | (PC10)  | (PA12) |

| C | OSC_IN                     | VSS_4                | ( PB7 ) | (PB5)   | (PC12)  | (PA10)                   | ( PA9 ) | (PA11) |

| D | OSC_OUT                    | VDD_4                | (PB6)   | ,VSS_3  | Vss_2   | ,Vss_1;                  | (PA8)   | (PC9)  |

| E | (NRST)                     | (PC1)                | (PC0)   | 'VDD_3' | VDD_2'  | ,<br>V <sub>DD_1</sub> , | (PC7)   | (PC8)  |

| F | (VSSA)                     | (PC2)                | (PA2 )  | (PA5)   | (PB0)   | (PC6)                    | (PB15)  | (PB14) |

| G | WREF+                      | PĄO-WKŲP             | ( PA3 ) | (PA6)   | (PB1)   | (PB2)                    | (PB10)  | (PB13) |

| н | V <sub>DDA</sub> ,         | ( PA1 )              | (PA4)   | PA7     | ( PC4 ) | (PC5)                    | (PB11)  | (PB12) |

|   |                            |                      |         |         |         |                          |         | Al1549 |

Figure 6. STM32F100xx value line TFBGA64 ballout

Table 4. Low & medium-density STM32F100xx pin definitions

|         | Pi     | ns      |        |                                |                     | 2)                         |                                                  | Alternate function | s <sup>(3)(4)</sup> |

|---------|--------|---------|--------|--------------------------------|---------------------|----------------------------|--------------------------------------------------|--------------------|---------------------|

| LQFP100 | LQFP64 | TFBGA64 | LQFP48 | Pin name                       | Type <sup>(1)</sup> | I / O level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default            | Remap               |

| 1       | -      | -       | -      | PE2                            | I/O                 | FT                         | PE2                                              | TRACECLK           | -                   |

| 2       | -      | -       | -      | PE3                            | I/O                 | FT                         | PE3                                              | TRACED0            | -                   |

| 3       | -      | -       | -      | PE4                            | I/O                 | FT                         | PE4                                              | TRACED1            | -                   |

| 4       | -      | -       | -      | PE5                            | I/O                 | FT                         | PE5                                              | TRACED2            | -                   |

| 5       | -      | -       | -      | PE6                            | I/O                 | FT                         | PE6                                              | TRACED3            | -                   |

| 6       | 1      | B2      | 1      | V <sub>BAT</sub>               | S                   | -                          | V <sub>BAT</sub>                                 | -                  | -                   |

| 7       | 2      | A2      | 2      | PC13-TAMPER-RTC <sup>(5)</sup> | I/O                 | -                          | PC13 <sup>(6)</sup>                              | TAMPER-RTC         | -                   |

| 8       | 3      | A1      | 3      | PC14-OSC32_IN <sup>(5)</sup>   | I/O                 | -                          | PC14 <sup>(6)</sup>                              | OSC32_IN           | -                   |

# 5 Electrical characteristics

# 5.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

### 5.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

### 5.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 3.3$  V (for the 2 V  $\leq V_{DD} \leq 3.6$  V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\Sigma$ ).

#### 5.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

# 5.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 8*.

#### 5.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 9*.

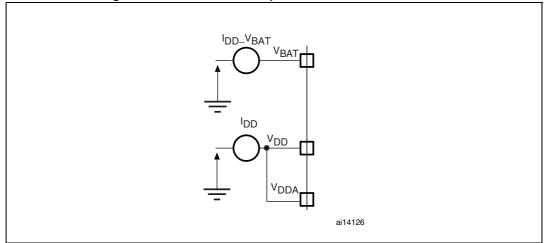

### 5.1.7 Current consumption measurement

#### Figure 11. Current consumption measurement scheme

# 5.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 5: Voltage characteristics*, *Table 6: Current characteristics*, and *Table 7: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                                                                                                          | Ratings                                                                          | Min                  | Мах                                           | Unit |

|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------|-----------------------------------------------|------|

| V <sub>DD</sub> –V <sub>SS</sub>                                                                                | External main supply voltage (including $V_{DDA}$ and $V_{DD})^{\left(1\right)}$ | -0.3                 | 4.0                                           |      |

| V <sub>IN</sub> <sup>(2)</sup> Input voltage on five volt tolerant pin           Input voltage on any other pin |                                                                                  | V <sub>SS</sub> -0.3 | V <sub>DD</sub> +4.0                          | V    |

|                                                                                                                 |                                                                                  | V <sub>SS</sub> -0.3 | 4.0                                           |      |

| ΔV <sub>DDx</sub>                                                                                               | Variations between different V <sub>DD</sub> power pins                          | -                    | 50                                            |      |

| V <sub>SSX</sub> -V <sub>SS</sub>                                                                               | Variations between all the different ground                                      |                      | 50                                            | mV   |

| V <sub>ESD(HBM)</sub>                                                                                           | Electrostatic discharge voltage (human body model)                               |                      | 3.11: Absolute<br>ngs (electrical<br>itivity) | -    |

#### Table 5. Voltage characteristics

All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 6: Current characteristics* for the maximum allowed injected current values.

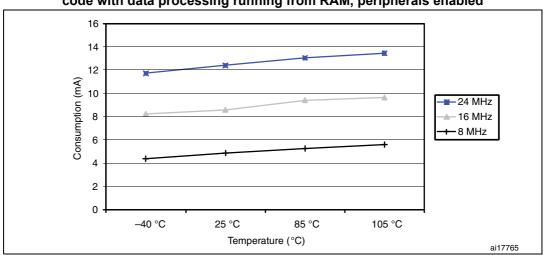

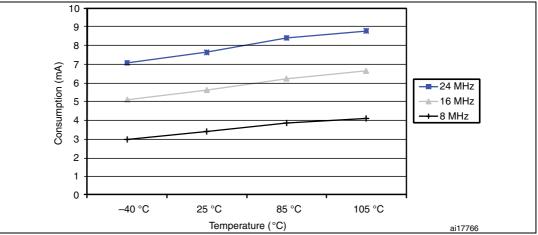

Figure 12. Maximum current consumption in Run mode versus frequency (at 3.6 V) - code with data processing running from RAM, peripherals enabled

Figure 13. Maximum current consumption in Run mode versus frequency (at 3.6 V) - code with data processing running from RAM, peripherals disabled

Table 14. Maximum current consumption in Sleep mode, code running from Flash or RAM

| Symbol | Deremeter                                             | Conditions                                               | £                 | Ма                     | Unit                                                   |      |

|--------|-------------------------------------------------------|----------------------------------------------------------|-------------------|------------------------|--------------------------------------------------------|------|

| Symbol | Parameter                                             | Conditions                                               | f <sub>HCLK</sub> | T <sub>A</sub> = 85 °C | $T_{A} = 105 ^{\circ}C$ $10$ $7.5$ $4.8$ $4$ $3.5$ $3$ | Unit |

|        |                                                       |                                                          | 24 MHz            | 9.6                    | 10                                                     |      |

|        | External clock <sup>(2)</sup> all peripherals enabled | 16 MHz                                                   | 7.1               | 7.5                    |                                                        |      |

|        | Supply current                                        | F F                                                      | 8 MHz             | 4.5                    | 4.8                                                    | m 4  |

| IDD    | in Sleep mode                                         | (2)                                                      | 24 MHz            | 3.8                    | 4                                                      | mA   |

|        |                                                       | External clock <sup>(2)</sup> , all peripherals disabled | 16 MHz            | 3.3                    | 3.5                                                    |      |

|        |                                                       | F F                                                      | 8 MHz             | 2.7                    | 3                                                      |      |

1. Guaranteed by characterization, tested in production at  $V_{DD}$  max and  $f_{HCLK}$  max with peripherals enabled.

2. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

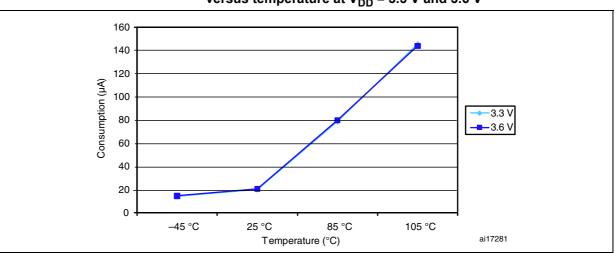

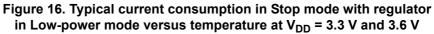

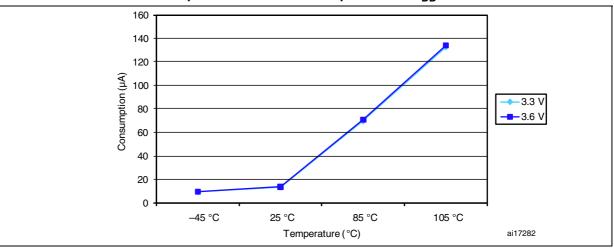

Figure 15. Typical current consumption in Stop mode with regulator in Run mode versus temperature at  $V_{DD}$  = 3.3 V and 3.6 V

|                 |                   | -                                            |                   | Typical                                   | values <sup>(1)</sup>                                                                                                                                                                                              |      |  |  |

|-----------------|-------------------|----------------------------------------------|-------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|

| Symbol          | Parameter         | Conditions                                   | f <sub>HCLK</sub> | All peripherals<br>enabled <sup>(2)</sup> | All peripherals<br>disabled           9.3           6.6           3.9           2.5           1.75           1.4           1.2           1.05           8.6           6           3.3           1.9           1.15 | Unit |  |  |

|                 |                   |                                              | 24 MHz            | 12.8                                      | 9.3                                                                                                                                                                                                                |      |  |  |

|                 |                   |                                              | 16 MHz            | 9.3                                       | 6.6                                                                                                                                                                                                                |      |  |  |

|                 |                   |                                              | 8 MHz             | 5.1                                       | 3.9                                                                                                                                                                                                                |      |  |  |

|                 |                   | Running on high-speed external clock with an | 4 MHz             | 3.2                                       | 2.5                                                                                                                                                                                                                |      |  |  |

|                 |                   | 8 MHz crystal <sup>(3)</sup>                 | 2 MHz             | 2.1                                       | 1.75                                                                                                                                                                                                               |      |  |  |

|                 |                   |                                              | 1 MHz             | 1.55                                      | 1.4                                                                                                                                                                                                                |      |  |  |

|                 |                   |                                              | 500 kHz           | 1.3                                       | 1.2                                                                                                                                                                                                                |      |  |  |

|                 | Supply current in |                                              | 125 kHz           | 1.1                                       | 1.05                                                                                                                                                                                                               | mA   |  |  |

| I <sub>DD</sub> | Run mode          |                                              | 24 MHz            | 12.2                                      | 8.6                                                                                                                                                                                                                | ША   |  |  |

|                 |                   |                                              |                   | 16 MHz                                    | 8.5                                                                                                                                                                                                                | 6    |  |  |

|                 |                   |                                              | 8 MHz             | 4.6                                       | 3.3                                                                                                                                                                                                                |      |  |  |

|                 |                   | Running on high-speed                        | 4 MHz             | 2.6                                       | 1.9                                                                                                                                                                                                                |      |  |  |

|                 |                   | internal RC (HSI)                            | 2 MHz             | 1.5                                       | 1.15                                                                                                                                                                                                               |      |  |  |

|                 |                   |                                              | 1 MHz             | 0.9                                       | 0.8                                                                                                                                                                                                                |      |  |  |

|                 |                   |                                              | 500               | 500 kHz                                   | 0.65                                                                                                                                                                                                               | 0.6  |  |  |

|                 |                   |                                              | 125 kHz           | 0.45                                      | 0.43                                                                                                                                                                                                               |      |  |  |

Table 16. Typical current consumption in Run mode, code with data processingrunning from Flash

1. Typical values are measures at  $T_A = 25$  °C,  $V_{DD} = 3.3$  V.

2. Add an additional power consumption of 0.8 mA for the ADC and of 0.5 mA for the DAC analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

3. An 8 MHz crystal is used as the external clock source. The AHB prescaler is used to reduce the frequency when  $f_{HCLK} < 8$  MHz, the PLL is used when  $f_{HCLK} > 8$  MHz.

| Symbol                                            | Parameter                                                                                     | Conditions                                                                      | Min | Тур | Max | Unit |  |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----|-----|-----|------|--|

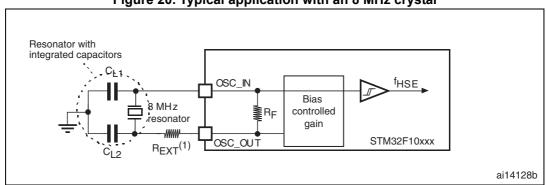

| f <sub>OSC_IN</sub>                               | Oscillator frequency                                                                          | -                                                                               | 4   | 8   | 24  | MHz  |  |

| R <sub>F</sub>                                    | Feedback resistor                                                                             | -                                                                               | -   | 200 | -   | kΩ   |  |

| C <sub>L1</sub><br>C <sub>L2</sub> <sup>(3)</sup> | Recommended load capacitance versus equivalent serial resistance of the crystal $(R_S)^{(4)}$ | R <sub>S</sub> = 30 Ω                                                           | -   | 30  | -   | pF   |  |

| i <sub>2</sub>                                    | HSE driving current                                                                           | V <sub>DD</sub> = 3.3 V<br>V <sub>IN</sub> = V <sub>SS</sub> with 30 pF<br>load | -   | -   | 1   | mA   |  |

| 9 <sub>m</sub>                                    | Oscillator transconductance                                                                   | Startup                                                                         | 25  | -   | -   | mA/V |  |

| t <sub>SU(HSE)</sub>                              | Startup time                                                                                  | V <sub>DD</sub> is stabilized                                                   | -   | 2   | -   | ms   |  |

Table 21. HSE 4-24 MHz oscillator characteristics<sup>(1)(2)</sup>

1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

- 2. Guaranteed by characterization results.

- 3. It is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator.  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ .

- 4. The relatively low value of the RF resistor offers a good protection against issues resulting from use in a humid environment, due to the induced leakage and the bias condition change. However, it is recommended to take this point into account if the MCU is used in tough humidity conditions.

- t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

1. R<sub>EXT</sub> value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 22*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

Note: For  $C_{L1}$  and  $C_{L2}$  it is recommended to use high-quality ceramic capacitors in the 5 pF to 15 pF range selected to match the requirements of the crystal or resonator.  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ .

Load capacitance  $C_L$  has the following formula:  $C_L = C_{L1} \times C_{L2} / (C_{L1} + C_{L2}) + C_{stray}$  where  $C_{stray}$  is the pin capacitance and board or trace PCB-related capacitance. Typically, it is between 2 pF and 7 pF.

For further details, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

**Caution:** To avoid exceeding the maximum value of  $C_{L1}$  and  $C_{L2}$  (15 pF) it is strongly recommended to use a resonator with a load capacitance  $C_L \le 7$  pF. Never use a resonator with a load capacitance of 12.5 pF.

**Example:** if you choose a resonator with a load capacitance of  $C_L$  = 6 pF, and  $C_{stray}$  = 2 pF, then  $C_{L1}$  =  $C_{L2}$  = 8 pF.

| Symbol                              | Parameter                                                                                     | Co                                                                                  | onditions                              | Min | Тур | Мах  | Unit |

|-------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------|-----|-----|------|------|

| R <sub>F</sub>                      | Feedback resistor                                                                             |                                                                                     | -                                      | -   | 5   | -    | MΩ   |

| $C_{L1} C_{L2}^{(2)}$               | Recommended load capacitance versus equivalent serial resistance of the crystal $(R_S)^{(3)}$ | R <sub>S</sub> = 30 KΩ<br>V <sub>DD</sub> = 3.3 V V <sub>IN</sub> = V <sub>SS</sub> |                                        | -   | -   | 15   | pF   |

| l <sub>2</sub>                      | LSE driving current                                                                           | V <sub>DD</sub> = 3                                                                 | .3 V V <sub>IN</sub> = V <sub>SS</sub> | -   | -   | 1.4  | μA   |

| 9 <sub>m</sub>                      | Oscillator transconductance                                                                   |                                                                                     | 5                                      | -   | -   | µA/V |      |

|                                     |                                                                                               |                                                                                     | T <sub>A</sub> = 50 °C                 | -   | 1.5 | -    |      |

|                                     |                                                                                               |                                                                                     | T <sub>A</sub> = 25 °C                 | -   | 2.5 | -    |      |

|                                     |                                                                                               |                                                                                     | T <sub>A</sub> = 10 °C                 | -   | 4   | -    |      |

| t (4)                               | Startun tima                                                                                  | V <sub>DD</sub> is                                                                  | T <sub>A</sub> = 0 °C                  | -   | 6   | -    |      |

| t <sub>SU(LSE)</sub> <sup>(4)</sup> | Startup time                                                                                  | stabilized                                                                          | T <sub>A</sub> = -10 °C                | -   | 10  | -    | S    |

|                                     |                                                                                               |                                                                                     | T <sub>A</sub> = -20 °C                | -   | 17  | -    |      |

|                                     |                                                                                               |                                                                                     | T <sub>A</sub> = -30 °C                | -   | 32  | -    |      |

|                                     |                                                                                               |                                                                                     | T <sub>A</sub> = -40 °C                | -   | 60  | -    |      |

Table 22. LSE oscillator characteristics  $(f_{LSE} = 32.768 \text{ kHz})^{(1)}$

1. Guaranteed by characterization results.

2. Refer to the note and caution paragraphs above the table.

- The oscillator selection can be optimized in terms of supply current using an high quality resonator with small R<sub>S</sub> value for example MSIV-TIN32.768 kHz. Refer to crystal manufacturer for more details

- 4. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

### Low-speed internal (LSI) RC oscillator

| Table 24. LSI oso | illator characteristics <sup>(1)</sup> | ) |

|-------------------|----------------------------------------|---|

|-------------------|----------------------------------------|---|

| Symbol                              | Parameter                                          | Min | Тур  | Max | Unit |

|-------------------------------------|----------------------------------------------------|-----|------|-----|------|

| f <sub>LSI</sub>                    | Frequency                                          | 30  | 40   | 60  | kHz  |

| $\Delta f_{LSI(T)}$                 | Temperature-related frequency drift <sup>(2)</sup> | -9  | -    | 9   | %    |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time                        | -   | -    | 85  | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption                   | -   | 0.65 | 1.2 | μA   |

1.  $V_{DD}$  = 3 V,  $T_A$  = -40 to 105 °C °C unless otherwise specified.

2. Guaranteed by characterization results.

3. Guaranteed by design.

#### Wakeup time from low-power mode

The wakeup times given in *Table 25* are measured on a wakeup phase with an 8-MHz HSI RC oscillator. The clock source used to wake up the device depends from the current operating mode:

- Stop or Standby mode: the clock source is the RC oscillator

- Sleep mode: the clock source is the clock that was set before entering Sleep mode.

All timings are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

| Symbol                              | Parameter                                           | Тур | Unit |

|-------------------------------------|-----------------------------------------------------|-----|------|

| t <sub>WUSLEEP</sub> <sup>(1)</sup> | Wakeup from Sleep mode                              | 1.8 | μs   |

| t <sub>WUSTOP</sub> <sup>(1)</sup>  | Wakeup from Stop mode (regulator in run mode)       | 3.6 |      |

| 'WUSTOP'                            | Wakeup from Stop mode (regulator in low-power mode) | 5.4 | μs   |

| t <sub>WUSTDBY</sub> <sup>(1)</sup> | Wakeup from Standby mode                            | 50  | μs   |

Table 25. Low-power mode wakeup timings

1. The wakeup times are measured from the wakeup event to the point at which the user application code reads the first instruction.

# 5.3.9 Memory characteristics

#### Flash memory

The characteristics are given at  $T_{\text{A}}$  = –40 to 105  $^{\circ}\text{C}$  unless otherwise specified.

| Symbol             | Parameter               | Conditions                                                                 | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

|--------------------|-------------------------|----------------------------------------------------------------------------|--------------------|------|--------------------|------|

| t <sub>prog</sub>  | 16-bit programming time | T <sub>A</sub> = -40 to +105 °C                                            | 40                 | 52.5 | 70                 | μs   |

| t <sub>ERASE</sub> | Page (1 KB) erase time  | T <sub>A</sub> = -40 to +105 °C                                            | 20                 | -    | 40                 | ms   |

| t <sub>ME</sub>    | Mass erase time         | $T_A = -40$ to +105 °C                                                     | 20                 | -    | 40                 | ms   |

|                    |                         | Read mode<br>f <sub>HCLK</sub> = 24 MHz, V <sub>DD</sub> = 3.3 V           | -                  | -    | 20                 | mA   |

| I <sub>DD</sub>    | Supply current          | Write / Erase modes<br>f <sub>HCLK</sub> = 24 MHz, V <sub>DD</sub> = 3.3 V | -                  | -    | 5                  | mA   |

|                    |                         | Power-down mode / Halt,<br>$V_{DD}$ = 3.0 to 3.6 V                         | -                  | -    | 50                 | μA   |

| V <sub>prog</sub>  | Programming voltage     | -                                                                          | 2                  | -    | 3.6                | V    |

| Table 27 | . Flash | memory | characteristics |

|----------|---------|--------|-----------------|

|----------|---------|--------|-----------------|

1. Guaranteed by design.

| Symbol                         | Parameter      | Conditions                                                                              |                    | Value |     |         |

|--------------------------------|----------------|-----------------------------------------------------------------------------------------|--------------------|-------|-----|---------|

|                                |                | Conditions                                                                              | Min <sup>(1)</sup> | Тур   | Max | Unit    |

| N <sub>END</sub>               | Endurance      | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                 | -     | -   | kcycles |

|                                |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30                 | -     | -   |         |

| t <sub>RET</sub> Data retentio | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                 | -     | -   | Years   |

|                                | -              | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                 | -     | -   |         |

#### Table 28. Flash memory endurance and data retention

1. Based on characterization not tested in production.

2. Cycling performed over the whole temperature range.

# 5.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (Electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- **FTB**: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 29*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                                                    | Level/Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, $T_A$ = +25 °C,<br>f <sub>HCLK</sub> = 24 MHz, LQFP100<br>package, conforms to<br>IEC 61000-4-2                             | 2B          |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD} = 3.3 \text{ V}, T_A = +25 ^{\circ}\text{C},$<br>$f_{HCLK} = 24 \text{ MHz}, \text{LQFP100}$<br>package, conforms to<br>IEC 61000-4-4 | 4A          |

Table 29. EMS characteristics

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and pre qualification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second. To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

# 5.3.13 I/O port characteristics

### General input/output characteristics

Unless otherwise specified, the parameters given in *Table 34* are derived from tests performed under the conditions summarized in *Table 8*. All I/Os are CMOS and TTL compliant.

| Symbol           | Parameter                                                            | Conditions                                                         | Min                                | Тур | Мах                                | Unit |  |

|------------------|----------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------|-----|------------------------------------|------|--|

| M                | Standard I/O input low level voltage                                 |                                                                    | -0.3                               | -   | 0.28*(V <sub>DD</sub> -2 V)+0.8 V  |      |  |

| V <sub>IL</sub>  | I/O FT <sup>(1)</sup> input low level voltage                        | -                                                                  | -0.3                               | -   | 0.32*(V <sub>DD</sub> -2 V)+0.75 V |      |  |

|                  | Standard I/O input<br>high level voltage                             |                                                                    | 0.41*(V <sub>DD</sub> -2 V) +1.3 V | -   | V <sub>DD</sub> +0.3               | V    |  |

| V <sub>IH</sub>  | I/O FT <sup>(1)</sup> input high                                     | $V_{DD} > 2 V$                                                     | 0.42*(\/2\+1.\/                    |     | 5.5                                |      |  |

|                  | level voltage                                                        | V <sub>DD</sub> ≤2 V                                               | 0.42*(V <sub>DD</sub> –2)+1 V      | -   | 5.2                                |      |  |

| V <sub>hys</sub> | Standard I/O Schmitt<br>trigger voltage<br>hysteresis <sup>(2)</sup> | -                                                                  | 200                                | -   | -                                  | mV   |  |

| ♥ hys            | I/O FT Schmitt trigger voltage hysteresis <sup>(2)</sup>             |                                                                    | 5% V <sub>DD</sub> <sup>(3)</sup>  | -   | -                                  | mV   |  |

| 1                | Input leakage                                                        | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>Standard I/Os | -                                  | -   | ±1                                 |      |  |

| l <sub>lkg</sub> | current <sup>(4)</sup>                                               | V <sub>IN</sub> = 5 V<br>I/O FT                                    | -                                  | -   | 3                                  | μA   |  |

| R <sub>PU</sub>  | Weak pull-up<br>equivalent resistor <sup>(5)</sup>                   | $V_{IN} = V_{SS}$                                                  | 30                                 | 40  | 50                                 | kΩ   |  |

| R <sub>PD</sub>  | Weak pull-down<br>equivalent resistor <sup>(5)</sup>                 | $V_{IN} = V_{DD}$                                                  | 30                                 | 40  | 50                                 | kΩ   |  |

| CIO              | I/O pin capacitance                                                  | -                                                                  | -                                  | 5   | -                                  | pF   |  |

1. FT = 5V tolerant. To sustain a voltage higher than V<sub>DD</sub>+0.3 the internal pull-up/pull-down resistors must be disabled.

2. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by design.

- 3. With a minimum of 100 mV.

- 4. Leakage could be higher than max. if negative current is injected on adjacent pins.

- 5. Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimum (~10% order).

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 22* and *Figure 23* for standard I/Os, and in *Figure 24* and *Figure 25* for 5 V tolerant I/Os.

| Symbol                           | Parameter                                          | Conditions                                            | Min                                                   | Тур                | Мах                | Unit               |

|----------------------------------|----------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|--------------------|--------------------|--------------------|

| $V_{DDA}$                        | Power supply                                       | -                                                     | 2.4                                                   | -                  | 3.6                | V                  |

| $V_{REF^+}$                      | Positive reference voltage                         | -                                                     | 2.4                                                   | -                  | V <sub>DDA</sub>   | V                  |

| I <sub>VREF</sub>                | Current on the V <sub>REF</sub> input pin          | -                                                     | -                                                     | 160 <sup>(1)</sup> | 220 <sup>(1)</sup> | μA                 |

| f <sub>ADC</sub>                 | ADC clock frequency                                | -                                                     | 0.6                                                   | -                  | 12                 | MHz                |

| f <sub>S</sub> <sup>(2)</sup>    | Sampling rate                                      | -                                                     | 0.05                                                  | -                  | 1                  | MHz                |

| <b>f</b> (2)                     |                                                    | f <sub>ADC</sub> = 12 MHz                             | -                                                     | -                  | 705                | kHz                |

| f <sub>TRIG</sub> <sup>(2)</sup> | External trigger frequency                         | -                                                     | -                                                     | -                  | 17                 | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub> <sup>(3)</sup>  | Conversion voltage range                           | -                                                     | 0 (V <sub>SSA</sub> tied to ground)                   | -                  | $V_{REF}$ +        | V                  |

| $R_{AIN}^{(2)}$                  | External input impedance                           | See <i>Equation 1</i> and <i>Table 43</i> for details | -                                                     | -                  | 50                 | κΩ                 |

| $R_{ADC}^{(2)}$                  | Sampling switch resistance                         | -                                                     | -                                                     | -                  | 1                  | κΩ                 |

| C <sub>ADC</sub> <sup>(2)</sup>  | Internal sample and hold capacitor                 | -                                                     | -                                                     | -                  | 8                  | pF                 |

| <b>•</b> (2)                     | Calibratian time                                   | f <sub>ADC</sub> = 12 MHz                             | 6.9                                                   |                    | μs                 |                    |

| t <sub>CAL</sub> <sup>(2)</sup>  | Calibration time                                   | -                                                     | 83                                                    |                    | 1/f <sub>ADC</sub> |                    |

| <b>↓</b> (2)                     | Injection trigger conversion                       | f <sub>ADC</sub> = 12 MHz                             | -                                                     | -                  | 0.25               | μs                 |

| t <sub>lat</sub> (2)             | latency                                            | -                                                     | -                                                     | -                  | 3 <sup>(4)</sup>   | 1/f <sub>ADC</sub> |

| t (2)                            | Regular trigger conversion                         | f <sub>ADC</sub> = 12 MHz                             | -                                                     | -                  | 0.166              | μs                 |

| t <sub>latr</sub> (2)            | latency                                            | -                                                     | -                                                     | -                  | 2 <sup>(4)</sup>   | 1/f <sub>ADC</sub> |

| + (2)                            | O annu lin a time a                                |                                                       | 0.125                                                 | -                  | 20.0               | μs                 |

| t <sub>S</sub> <sup>(2)</sup>    | Sampling time                                      | f <sub>ADC</sub> = 12 MHz                             | 1.5                                                   | -                  | 239.5              | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(2)</sup> | Power-up time                                      | -                                                     | 0                                                     | 0                  | 1                  | μs                 |

|                                  | <b>T</b> ( )                                       | f <sub>ADC</sub> = 12 MHz                             | 1.17                                                  | -                  | 21                 | μs                 |

| t <sub>CONV</sub> <sup>(2)</sup> | Total conversion time<br>(including sampling time) | -                                                     | 14 to 252 (t <sub>S</sub> for sa<br>successive approx |                    |                    | 1/f <sub>ADC</sub> |

| Table 42. ADC characteristic | CS |

|------------------------------|----|

|------------------------------|----|

1. Based on characterization results, not tested in production.

2. Guaranteed by design.

V<sub>REF+</sub> can be internally connected to V<sub>DDA</sub> and V<sub>REF-</sub> can be internally connected to V<sub>SSA</sub>, depending on the package. Refer to *Table 4: Low & medium-density STM32F100xx pin definitions* and *Figure 6* for further details.

4. For external triggers, a delay of 1/f<sub>PCLK2</sub> must be added to the latency specified in *Table 42*.

## Equation 1: R<sub>AIN</sub> max formula:

$$R_{AIN} < \frac{I_{S}}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$$

The above formula (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. Here N = 12 (from 12-bit resolution).

| T <sub>s</sub> (cycles) | t <sub>S</sub> (μs) | R <sub>AIN</sub> max (kΩ) |

|-------------------------|---------------------|---------------------------|

| 1.5                     | 0.125               | 0.4                       |

| 7.5                     | 0.625               | 5.9                       |

| 13.5                    | 1.125               | 11.4                      |

| 28.5                    | 2.375               | 25.2                      |

| 41.5                    | 3.45                | 37.2                      |

| 55.5                    | 4.625               | 50                        |

| 71.5                    | 5.96                | NA                        |

| 239.5                   | 20                  | NA                        |

#### Table 43. $R_{AIN}$ max for $f_{ADC} = 12 \text{ MHz}^{(1)}$

1. Guaranteed by design.

| Symbol | Parameter                    | Test conditions                                                                        | Тур  | Мах  | Unit |

|--------|------------------------------|----------------------------------------------------------------------------------------|------|------|------|

| ET     | Total unadjusted error       | $f_{PCLK2} = 24 \text{ MHz},$                                                          | ±1.3 | ±2.2 |      |

| EO     | Offset error                 | f <sub>ADC</sub> = 12 MHz, R <sub>AIN</sub> < 10 kΩ<br>V <sub>DDA</sub> = 3 V to 3.6 V | ±1   | ±1.5 |      |

| EG     | Gain error                   | $V_{\text{REF+}} = V_{\text{DDA}}$                                                     | ±0.5 | ±1.5 | LSB  |

| ED     | Differential linearity error | T <sub>A</sub> = 25 °C                                                                 | ±0.7 | ±1   |      |

| EL     | Integral linearity error     | Measurements made after<br>ADC calibration                                             | ±0.8 | ±1.5 |      |

| Table 44. ADC accuracy - limited test conditions <sup>(1)(2)</sup> |

|--------------------------------------------------------------------|

|--------------------------------------------------------------------|

1. ADC DC accuracy values are measured after internal calibration.

2. Guaranteed by characterization results.

| Table | 45. | ADC | accuracy <sup>(1) (2) (3)</sup> |

|-------|-----|-----|---------------------------------|

|-------|-----|-----|---------------------------------|

| Symbol | Parameter                    | Test conditions                                                                                                                                                             | Тур  | Max  | Unit |

|--------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|

| ET     | Total unadjusted error       | f <sub>PCLK2</sub> = 24 MHz,                                                                                                                                                | ±2   | ±5   |      |

| EO     | Offset error                 | $f_{ADC} = 12 \text{ MHz}, R_{AIN} < 10 \text{ k}\Omega$<br>$V_{DDA} = 2.4 \text{ V to } 3.6 \text{ V}$<br>$T_{A} = \text{Full operating range}$<br>Measurements made after | ±1.5 | ±2.5 |      |

| EG     | Gain error                   |                                                                                                                                                                             | ±1.5 | ±3   | LSB  |

| ED     | Differential linearity error |                                                                                                                                                                             | ±1   | ±2   |      |

| EL     | Integral linearity error     | ADC calibration                                                                                                                                                             | ±1.5 | ±3   |      |

1. ADC DC accuracy values are measured after internal calibration.

2. Better performance could be achieved in restricted  $V_{DD}$ , frequency,  $V_{REF}$  and temperature ranges.

3. Guaranteed by characterization results.

Note:ADC accuracy vs. negative injection current: Injecting a negative current on any analog<br/>input pins should be avoided as this significantly reduces the accuracy of the conversion<br/>being performed on another analog input. It is recommended to add a Schottky diode (pin to<br/>ground) to analog pins which may potentially inject negative currents.<br/>Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in<br/>Section 5.3.12 does not affect the ADC accuracy.

# 5.3.19 Temperature sensor characteristics

| Symbol                                | Parameter                                      | Min  | Тур  | Max       | Unit  |

|---------------------------------------|------------------------------------------------|------|------|-----------|-------|

| T <sub>L</sub> <sup>(1)</sup>         | V <sub>SENSE</sub> linearity with temperature  | -    | ±1   | <u>+2</u> | °C    |

| Avg_Slope <sup>(1)</sup>              | Average slope                                  | 4.0  | 4.3  | 4.6       | mV/°C |

| V <sub>25</sub> <sup>(1)</sup>        | Voltage at 25°C                                | 1.32 | 1.41 | 1.50      | V     |

| t <sub>START</sub> <sup>(2)</sup>     | Startup time                                   | 4    | -    | 10        | μs    |

| T <sub>S_temp</sub> <sup>(3)(2)</sup> | ADC sampling time when reading the temperature | -    | -    | 17.1      | μs    |

#### Table 47. TS characteristics

1. Guaranteed by characterization results.

2. Guaranteed by design.

3. Shortest sampling time can be determined in the application by multiple iterations.

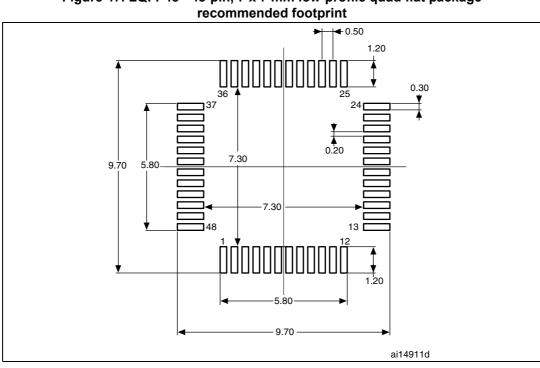

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min         | Тур   | Max   | Min                   | Тур    | Мах    |

| E1     | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |

| E3     | -           | 5.500 | -     | -                     | 0.2165 | -      |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |

| k      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |

| CCC    | -           | -     | 0.080 | -                     | -      | 0.0031 |

#### Table 52. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

Figure 47. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package

1. Dimensions are expressed in millimeters.

# 6.5 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 8: General operating conditions on page 34*.

The maximum chip-junction temperature,  $T_{\rm J}$  max, in degrees Celsius, may be calculated using the following equation:

$$T_J max = T_A max + (P_D max x \Theta_{JA})$$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

$\mathsf{P}_{\mathsf{I}/\mathsf{O}}$  max represents the maximum power dissipation on output pins where:

$$\mathsf{P}_{\mathsf{I}/\mathsf{O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol          | Parameter                                                                   | Value | Unit |  |

|-----------------|-----------------------------------------------------------------------------|-------|------|--|

| Q <sub>JA</sub> | Thermal resistance junction-ambient<br>LQFP 100 - 14 × 14 mm / 0.5 mm pitch | 46    |      |  |

|                 | Thermal resistance junction-ambient<br>LQFP 64 - 10 × 10 mm / 0.5 mm pitch  | 45    | °C/W |  |

|                 | Thermal resistance junction-ambient<br>TFBGA64 - 5 × 5 mm / 0.5 mm pitch    | 65    |      |  |

|                 | Thermal resistance junction-ambient<br>LQFP 48 - 7 × 7 mm / 0.5 mm pitch    | 55    |      |  |

#### Table 53. Package thermal characteristics

#### 6.5.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.