Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M4F                                                        |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 72MHz                                                                   |

| Connectivity               | CANbus, HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART       |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 52                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 32K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                            |

| Data Converters            | A/D 16x12b, 21x16b; D/A 3x12b                                           |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 66-UFBGA, WLCSP                                                         |

| Supplier Device Package    | 66-WLCSP (3.8x4.2)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f378rcy6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| r                              |                    | Table 2. Device 0                                                                                                        |                    | I                    |  |  |

|--------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------|--|--|

| Peri                           | pheral             | STM32F<br>378Cx                                                                                                          | STM32F<br>378Rx    | STM32F<br>378Vx      |  |  |

| Flash (Kbytes)                 |                    | 256                                                                                                                      |                    |                      |  |  |

| SRAM (Kbytes)                  | )                  |                                                                                                                          | 32                 |                      |  |  |

| Timers                         | General<br>purpose |                                                                                                                          |                    |                      |  |  |

|                                | Basic              |                                                                                                                          | 3 (16-bit)         |                      |  |  |

| Comm.<br>interfaces            | SPI/I2S            |                                                                                                                          | 3                  |                      |  |  |

|                                | l <sup>2</sup> C   |                                                                                                                          | 2                  |                      |  |  |

|                                | USART              | 3                                                                                                                        |                    |                      |  |  |

|                                | CAN                |                                                                                                                          | 1                  |                      |  |  |

| Capacitive sensing channels    |                    | 14 17                                                                                                                    |                    | 24                   |  |  |

| 12-bit ADCs                    |                    | 1                                                                                                                        |                    |                      |  |  |

| 16-bit ADCs Sig                | gma- Delta         | 3                                                                                                                        |                    |                      |  |  |

| 12-bit DACs ou                 | tputs              | 3                                                                                                                        |                    |                      |  |  |

| Analog compar                  | ator               | 2                                                                                                                        |                    |                      |  |  |

| Max. CPU freq                  | uency              | 72 MHz                                                                                                                   |                    |                      |  |  |

| Main operating                 | voltage            | 1.8 V +/- 8%                                                                                                             |                    |                      |  |  |

| 16-bit SDADC operating voltage |                    | 2.2 to 3.6 V                                                                                                             |                    |                      |  |  |

| Operating temperature          |                    | Ambient operating temperature:<br>-40 to 85 °C / -40 to 105 °C<br>Junction temperature:<br>-40 to 105 °C / -40 to 125 °C |                    |                      |  |  |

| Packages                       |                    | LQFP48                                                                                                                   | LQFP64,<br>WLCSP66 | LQFP100,<br>UFBGA100 |  |  |

# **3** Functional overview

# 3.1 ARM® Cortex®-M4 core with embedded Flash and SRAM

The ARM Cortex-M4 processor is the latest generation of ARM processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The ARM Cortex-M4 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The processor supports a set of DSP instructions which allow efficient signal processing and complex algorithm execution.

Its single precision FPU speeds up software development by using metalanguage development tools, while avoiding saturation.

With its embedded ARM core, the STM32F378xx family is compatible with all ARM tools and software.

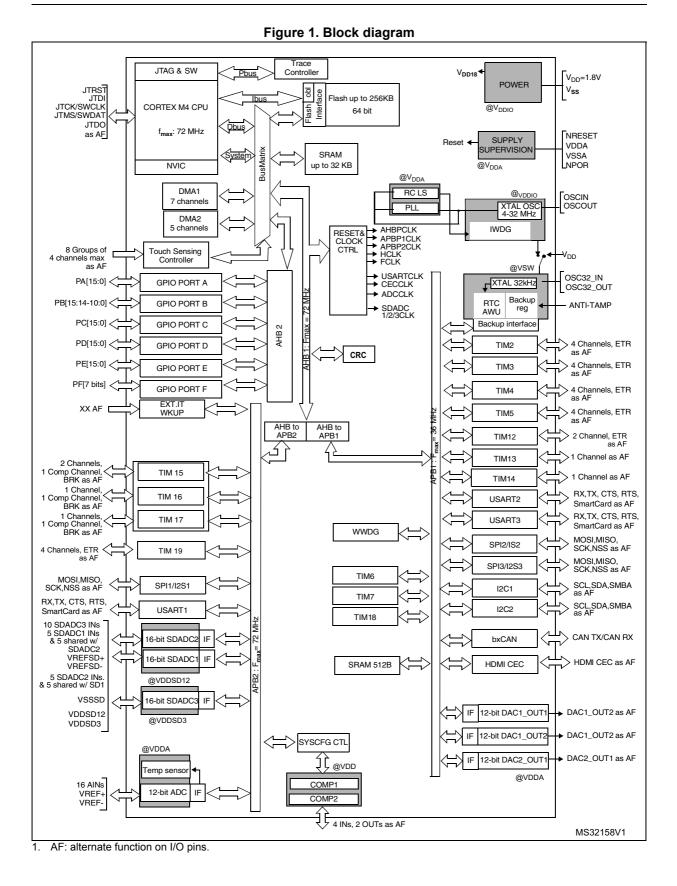

*Figure 1* shows the general block diagram of the STM32F378xx family.

# 3.2 Memory protection unit

The memory protection unit (MPU) is used to separate the processing of tasks from the data protection. The MPU can manage up to 8 protection areas that can all be further divided up into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes of addressable memory.

The memory protection unit is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real-time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

The Cortex-M4 processor is a high performance 32-bit processor designed for the microcontroller market. It offers significant benefits to developers, including:

- Outstanding processing performance combined with fast interrupt handling

- Enhanced system debug with extensive breakpoint and trace capabilities

- Efficient processor core, system and memories

- Ultralow power consumption with integrated sleep modes

- Platform security robustness with optional integrated memory protection unit (MPU).

With its embedded ARM core, the STM32F378xx devices are compatible with all ARM development tools and software.

# 3.3 Embedded Flash memory

All STM32F378xx devices feature up to 256 Kbytes of embedded Flash memory available for storing programs and data. The Flash memory access time is adjusted to the CPU clock frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 48 MHz and 2 wait states above).

# 3.4 Cyclic redundancy check (CRC) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code using a configurable generator polynomial value and size.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at linktime and stored at a given memory location.

# 3.5 Embedded SRAM

All STM32F378xx devices feature up to 32 Kbytes of embedded SRAM with hardware parity check. The memory can be accessed in read/write at CPU clock speed with 0 wait states.

# 3.6 Boot modes

At startup, Boot0 pin and Boot1 option bit are used to select one of three boot options:

- Boot from user Flash

- Boot from system memory

- Boot from embedded SRAM

The boot loader is located in system memory. It is used to reprogram the Flash memory by using USART1 (PA9/PA10), USART2 (PD5/PD6) or I2C (PB6/PB7).

# 3.7 **Power management**

## 3.7.1 Power supply schemes

- $V_{DD}$ : external power supply for I/Os and core. It is provided externally through  $V_{DD}$  pins, and can be 1.8 V +/- 8%.

- V<sub>DDA</sub> = 1.65 to 3.6 V:

- external analog power supplies for Reset blocks, RCs and PLL

- supply voltage for 12-bit ADC, DACs and comparators (minimum voltage to be applied to V<sub>DDA</sub> is 2.4 V when the 12-bit ADC and DAC are used).

- V<sub>DDSD12</sub> and V<sub>DDSD3</sub> = 2.2 to 3.6 V: supply voltages for SDADC1/2 and SDADCD3 sigma delta ADCs. Independent from V<sub>DD</sub>/V<sub>DDA</sub>.

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers when V<sub>DD</sub> is not present.

41/131

DocID025608 Rev 4

5

|             |               |                      |                      |                | Та            | able 12. Alte          | rnate functio          | ons for port PA | 4             |                |               |               |      |              |

|-------------|---------------|----------------------|----------------------|----------------|---------------|------------------------|------------------------|-----------------|---------------|----------------|---------------|---------------|------|--------------|

| Pin<br>Name | AF0           | AF1                  | AF2                  | AF3            | AF4           | AF5                    | AF6                    | AF7             | AF8           | AF9            | AF10          | AF11          | AF14 | AF15         |

| PA0         | -             | TIM2_<br>CH1_<br>ETR | TIM5_<br>CH1_<br>ETR | TSC_<br>G1_IO1 | -             | -                      | -                      | USART2_CTS      | COMP1<br>_OUT | -              | -             | TIM19<br>_CH1 | -    | EVENT<br>OUT |

| PA1         | RTC_<br>REFIN | TIM2_<br>CH2         | TIM5_<br>CH2         | TSC_<br>G1_IO2 | -             | -                      | SPI3_SCK/<br>I2S3_CK   | USART2_RTS      | -             | TIM15_<br>CH1N | -             | TIM19<br>_CH2 | -    | EVENT<br>OUT |

| PA2         | -             | TIM2_<br>CH3         | TIM5_<br>CH3         | TSC_<br>G1_IO3 | -             | -                      | SPI3_MISO/<br>I2S3_MCK | USART2_TX       | COMP2<br>_OUT | TIM15_<br>CH1  | -             | TIM19<br>_CH3 | -    | EVENT<br>OUT |

| PA3         | -             | TIM2_<br>CH4         | TIM5_<br>CH4         | TSC_<br>G1_IO4 | -             | -                      | SPI3_MOSI<br>/I2S3_SD  | USART2_RX       | -             | TIM15_<br>CH2  | -             | TIM19<br>_CH4 | -    | EVENT<br>OUT |

| PA4         | -             | -                    | TIM3_<br>CH2         | TSC_<br>G2_IO1 | -             | SPI1_NSS/<br>I2S1_WS   | SPI3_NSS/<br>I2S3_WS   | USART2_CK       | -             | -              | TIM12<br>_CH1 | -             | -    | EVENT<br>OUT |

| PA5         | -             | TIM2_<br>CH1_<br>ETR | -                    | TSC_<br>G2_IO2 | -             | SPI1_SCK/<br>I2S1_CK   | -                      | CEC             | -             | TIM14_<br>CH1  | TIM12<br>_CH2 | -             | -    | EVENT<br>OUT |

| PA6         | -             | TIM16_<br>CH1        | TIM3_<br>CH1         | TSC_<br>G2_IO3 | -             | SPI1_MISO<br>/I2S1_MCK | -                      | -               | COMP1<br>_OUT | TIM13_<br>CH1  | -             | -             | -    | EVENT<br>OUT |

| PA7         | -             | TIM17_<br>CH1        | TIM3_<br>CH2         | TSC_<br>G2_IO4 | -             | SPI1_MOSI<br>/I2S1_SD  | -                      | -               | COMP2<br>_OUT | TIM14_<br>CH1  | -             | -             | -    | EVENT<br>OUT |

| PA8         | МСО           | -                    | TIM5_<br>CH1_<br>ETR | -              | I2C2_<br>SMBA | SPI2_SCK/<br>I2S2_CK   | -                      | USART1_CK       | -             | -              | TIM4_<br>ETR  | -             | -    | EVENT<br>OUT |

| PA9         | -             | -                    | TIM13<br>_CH1        | TSC_<br>G4_IO1 | I2C2_<br>SCL  | SPI2_MISO<br>/I2S2_MCK | -                      | USART1_TX       | -             | TIM15_<br>BKIN | TIM2_<br>CH3  | -             | -    | EVENT<br>OUT |

| PA10        | -             | TIM17_<br>BKIN       | -                    | TSC_<br>G4_IO2 | I2C2_<br>SDA  | SPI2_MOSI<br>/I2S2_SD  | -                      | USART1_RX       | -             | TIM14_<br>CH1  | TIM2_<br>CH4  | -             | -    | EVENT<br>OUT |

| PA11        | -             | -                    | TIM5_<br>CH2         | -              | -             | SPI2_NSS/<br>I2S2_WS   | SPI1_NSS/<br>I2S1_WS   | USART1_CTS      | COMP1<br>_OUT | CAN_<br>RX     | TIM4_<br>CH1  | -             | -    | EVENT<br>OUT |

| PA12        | -             | TIM16_<br>CH1        | TIM5_<br>CH3         | -              | -             | -                      | SPI1_SCK/<br>I2S1_CK   | USART1_RTS      | COMP2<br>_OUT | CAN_TX         | TIM4_<br>CH2  | -             | -    | EVENT<br>OUT |

Pinouts and pin description

STM32F378xx

Pinouts and pin description

44/131

|          | Table 14. Alternate functions for port PC |          |              |            |     |                    |                    |           |  |  |  |

|----------|-------------------------------------------|----------|--------------|------------|-----|--------------------|--------------------|-----------|--|--|--|

| Pin Name | AF0                                       | AF1      | AF2          | AF3        | AF4 | AF5                | AF6                | AF7       |  |  |  |

| PC0      | -                                         | EVENTOUT | TIM5_CH1_ETR | -          | -   | -                  | -                  | -         |  |  |  |

| PC1      | -                                         | EVENTOUT | TIM5_CH2     | -          | -   | -                  | -                  | -         |  |  |  |

| PC2      | -                                         | EVENTOUT | TIM5_CH3     | -          | -   | SPI2_MISO/I2S2_MCK | -                  | -         |  |  |  |

| PC3      | -                                         | EVENTOUT | TIM5_CH4     | -          | -   | SPI2_MOSI/I2S2_SD  | -                  | -         |  |  |  |

| PC4      | -                                         | EVENTOUT | TIM13_CH1    | TSC_G3_IO1 | -   | -                  | -                  | USART1_TX |  |  |  |

| PC5      | -                                         | EVENTOUT | -            | TSC_G3_IO2 | -   | -                  | -                  | USART1_RX |  |  |  |

| PC6      | -                                         | EVENTOUT | TIM3_CH1     | -          | -   | SPI1_NSS/I2S1_WS   | -                  | -         |  |  |  |

| PC7      | -                                         | EVENTOUT | TIM3_CH2     | -          | -   | SPI1_SCK/I2S1_CK   | -                  | -         |  |  |  |

| PC8      | -                                         | EVENTOUT | TIM3_CH3     | -          | -   | SPI1_MISO/I2S1_MCK | -                  | -         |  |  |  |

| PC9      | -                                         | EVENTOUT | TIM3_CH4     | -          | -   | SPI1_MOSI/I2S1_SD  | -                  | -         |  |  |  |

| PC10     | -                                         | EVENTOUT | TIM19_CH1    | -          | -   | -                  | SPI3_SCK/I2S3_CK   | USART3_TX |  |  |  |

| PC11     | -                                         | EVENTOUT | TIM19_CH2    | -          | -   | -                  | SPI3_MISO/I2S3_MCK | USART3_RX |  |  |  |

| PC12     | -                                         | EVENTOUT | TIM19_CH3    | -          | -   | -                  | SPI3_MOSI/I2S3_SD  | USART3_CK |  |  |  |

| PC13     | -                                         | -        | -            | -          | -   | -                  | -                  | -         |  |  |  |

| PC14     | -                                         | -        | -            | -          | -   | -                  | -                  | -         |  |  |  |

| PC15     | -                                         | -        | -            | -          | -   | -                  | -                  | -         |  |  |  |

DocID025608 Rev 4

57

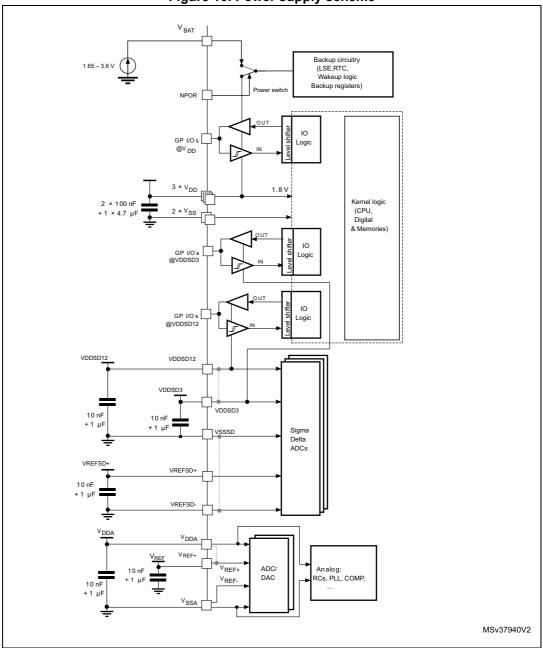

## 6.1.6 Power supply scheme

Figure 10. Power supply scheme

1. Dotted lines represent the internal connections on low pin count packages, joining the dedicated supply pins.

**Caution:** Each power supply pair (V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub> etc..) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

|                                 |                                      |                                                                         |                   | -                      | Гур                     |      |

|---------------------------------|--------------------------------------|-------------------------------------------------------------------------|-------------------|------------------------|-------------------------|------|

| Symbol                          | Parameter                            | Conditions                                                              | f <sub>HCLK</sub> | Peripherals<br>enabled | Peripherals<br>disabled | Unit |

|                                 |                                      |                                                                         | 72 MHz            | 42.6                   | 6.7                     |      |

|                                 |                                      | Running from HSE                                                        | 64 MHz            | 38.0                   | 6.0                     |      |

|                                 |                                      | crystal clock 8 MHz,<br>code executing                                  | 48 MHz            | 28.7                   | 4.5                     |      |

|                                 |                                      | from Flash or RAM,                                                      | 32 MHz            | 19.3                   | 3.1                     |      |

|                                 |                                      | PLL on                                                                  | 24 MHz            | 14.6                   | 2.4                     |      |

|                                 | Supply current in<br>Sleep mode from |                                                                         | 16 MHz            | 9.8                    | 1.7                     | mA   |

| I <sub>DD</sub>                 | V <sub>DD</sub> supply               |                                                                         | 8 MHz             | 4.8                    | 0.8                     | IIIA |

|                                 |                                      | Running from HSE                                                        | 4 MHz             | 3.0                    | 0.7                     |      |

|                                 |                                      | crystal clock 8 MHz,<br>code executing<br>from Flash or RAM,<br>PLL off | 2 MHz             | 1.9                    | 0.6                     | -    |

|                                 |                                      |                                                                         | 1 MHz             | 1.3                    | 0.6                     |      |

|                                 |                                      |                                                                         | 500 kHz           | 1.0                    | 0.6                     |      |

|                                 |                                      |                                                                         | 125 kHz           | 0.8                    | 0.5                     |      |

|                                 |                                      |                                                                         | 72 MHz            | 243.1                  | 243.1                   |      |

|                                 |                                      | Running from HSE                                                        | 64 MHz            | 214.1                  | 214.1                   |      |

|                                 |                                      | crystal clock 8 MHz, code executing                                     | 48 MHz            | 159.4                  | 159.4                   |      |

|                                 |                                      | from Flash or RAM,                                                      | 32 MHz            | 109.1                  | 109.1                   |      |

|                                 |                                      | PLL on                                                                  | 24 MHz            | 84.7                   | 84.7                    |      |

| I <sub>DDA</sub> <sup>(1)</sup> | Supply current in<br>Sleep mode from |                                                                         | 16 MHz            | 60.6                   | 60.6                    |      |

| 'DDA` ′                         | V <sub>DDA</sub> supply              |                                                                         | 8 MHz             | 1.0                    | 1.0                     | μA   |

|                                 |                                      | Running from HSE                                                        | 4 MHz             | 1.0                    | 1.0                     | -    |

|                                 |                                      | crystal clock 8 MHz,<br>code executing                                  | 2 MHz             | 1.0                    | 1.0                     |      |

|                                 |                                      | from Flash or RAM,                                                      | 1 MHz             | 1.0                    | 1.0                     |      |

|                                 |                                      | PLL off                                                                 | 500 kHz           | 1.0                    | 1.0                     |      |

|                                 |                                      |                                                                         | 125 kHz           | 1.0                    | 1.0                     |      |

1. V<sub>DDA</sub> monitoring is off, V<sub>DDSD12</sub> monitoring is off.

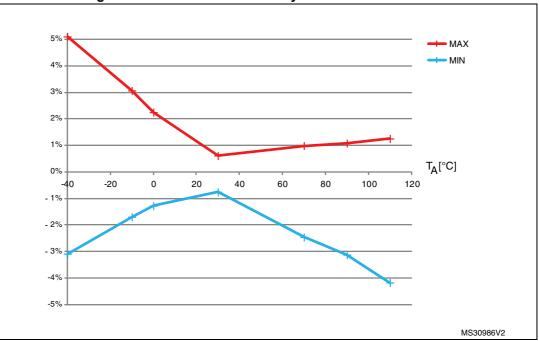

Figure 17. HSI oscillator accuracy characterization results

#### Low-speed internal (LSI) RC oscillator

Table 41. LSI oscillator characteristics<sup>(1)</sup>

| Symbol                              | Parameter                        | Min | Тур  | Мах | Unit |

|-------------------------------------|----------------------------------|-----|------|-----|------|

| f <sub>LSI</sub>                    | Frequency                        | 30  | 40   | 60  | kHz  |

| t <sub>su(LSI)</sub> <sup>(2)</sup> | LSI oscillator startup time      | -   | -    | 85  | μs   |

| I <sub>DD(LSI)</sub> <sup>(2)</sup> | LSI oscillator power consumption | -   | 0.75 | 1.2 | μA   |

1.  $V_{DDA}$  = 3.3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

.

2. Guaranteed by design.

## 6.3.8 PLL characteristics

The parameters given in *Table 42* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 22*.

| Table 42. PL | L characteristics |

|--------------|-------------------|

|--------------|-------------------|

| Symbol               | Parameter                      |                   | Unit |                    |      |

|----------------------|--------------------------------|-------------------|------|--------------------|------|

| Symbol               | Falameter                      | Min               | Тур  | Мах                | Unit |

| £                    | PLL input clock <sup>(1)</sup> | 1 <sup>(2)</sup>  | -    | 24 <sup>(2)</sup>  | MHz  |

| f <sub>PLL_IN</sub>  | PLL input clock duty cycle     | 40 <sup>(2)</sup> | -    | 60 <sup>(2)</sup>  | %    |

| f <sub>PLL_OUT</sub> | PLL multiplier output clock    | 16 <sup>(2)</sup> | -    | 72                 | MHz  |

| t <sub>LOCK</sub>    | PLL lock time                  | -                 | -    | 200 <sup>(2)</sup> | μs   |

| Jitter               | Cycle-to-cycle jitter          | -                 | -    | 300 <sup>(2)</sup> | ps   |

1. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{PLL_OUT}$ .

2. Guaranteed by design.

## 6.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 45*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol Parameter  |                                                                                                                                   | Conditions                                                                                                     | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------|

|                   |                                                                                                                                   | $V_{DD}$ = 1.8 V, LQFP100, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 72 MHz<br>conforms to IEC 61000-4-2 | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD}$ = 1.8 V, LQFP100, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 72 MHz<br>conforms to IEC 61000-4-4 | 4A              |

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

| Table | 48. | Electrical | sensitivities  |

|-------|-----|------------|----------------|

| Table | τυ. | LICCUICAI  | 30113111411103 |

| Symbol | Parameter             | Conditions                                    | Class      |

|--------|-----------------------|-----------------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +105 \text{ °C conforming to JESD78A}$ | II level A |

## 6.3.12 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of  $-5 \mu$ A/+0  $\mu$ A range), or other functional failure (for example reset occurrence or oscillator frequency deviation).

The test results are given in Table 49.

# 6.3.13 I/O port characteristics

## General input/output characteristics

Unless otherwise specified, the parameters given in *Table 50* are derived from tests performed under the conditions summarized in *Table 22*. All I/Os are CMOS and TTL compliant.

| Symbol           | Parameter                                               | Conditions                                                                                            | Min                                        | Тур                | Мах                                      | Unit |  |

|------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------|------------------------------------------|------|--|

|                  |                                                         | TC and TTa I/O                                                                                        | -                                          | -                  | 0.3V <sub>DD</sub> +0.07 <sup>(2)</sup>  |      |  |

|                  | Low level input                                         | FT and FTf I/O                                                                                        | -                                          | -                  | 0.475V <sub>DD</sub> -0.2 <sup>(2)</sup> |      |  |

|                  | voltage                                                 | BOOT0                                                                                                 | -                                          | -                  | 0.3V <sub>DD</sub> -0.3 <sup>(2)</sup>   |      |  |

|                  |                                                         | All I/Os except BOOT0 pin                                                                             | -                                          | -                  | 0.3V <sub>DD</sub>                       | v    |  |

|                  |                                                         | TC and TTa I/O                                                                                        | 0.445V <sub>DD</sub> +0.398 <sup>(2)</sup> | -                  | -                                        | v    |  |

| V                | High level input                                        | FT and FTf I/O                                                                                        | 0.5V <sub>DD+0.2</sub> <sup>(2)</sup>      | -                  | -                                        |      |  |

| V <sub>IH</sub>  | voltage                                                 | BOOT0                                                                                                 | 0.2V <sub>DD</sub> +0.95 <sup>(2)</sup>    | -                  | -                                        |      |  |

|                  |                                                         | All I/Os except BOOT0 pin                                                                             | 0.7V <sub>DD</sub>                         | -                  | -                                        |      |  |

|                  |                                                         | TC and TTa I/O                                                                                        | -                                          | 200 <sup>(2)</sup> | -                                        |      |  |

| V <sub>hys</sub> | Schmitt trigger<br>hysteresis                           | FT and FTf I/O                                                                                        | -                                          | 100 <sup>(2)</sup> | -                                        | mV   |  |

|                  |                                                         | BOOT0                                                                                                 |                                            | 300 <sup>(2)</sup> | -                                        |      |  |

|                  |                                                         | TC, FT, FTf and POR I/O<br>TTa in digital mode<br>V <sub>SS</sub> ≤ V <sub>IN</sub> ≤ V <sub>DD</sub> | -                                          | -                  | ±0.1                                     |      |  |

|                  |                                                         | TTa in digital mode<br>V <sub>DD</sub> ≤V <sub>IN</sub> ≤V <sub>DDA</sub>                             | -                                          | -                  | 1                                        |      |  |

| l <sub>lkg</sub> | Input leakage<br>current <sup>(3)</sup>                 | TTa in analog mode<br>V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DDA</sub>                              | -                                          | -                  | ±0.2                                     | μA   |  |

|                  |                                                         | FT and FTf I/O <sup>(3)</sup><br>V <sub>DD</sub> ≤V <sub>IN</sub> ≤5 V                                | -                                          | -                  | 10                                       |      |  |

|                  |                                                         | $\begin{array}{c} POR \\ V_{DDA} \leq V_{IN} \leq 5 V \end{array}$                                    |                                            | -                  | - 10                                     |      |  |

| R <sub>PU</sub>  | Weak pull-up<br>equivalent<br>resistor <sup>(4)</sup>   | V <sub>IN</sub> = V <sub>SS</sub>                                                                     | 25                                         | 40                 | 55                                       | kΩ   |  |

| R <sub>PD</sub>  | Weak pull-down<br>equivalent<br>resistor <sup>(4)</sup> | valent $V_{IN} = V_{DD}$ 25 40                                                                        |                                            | 40                 | 55                                       | K22  |  |

| C <sub>IO</sub>  | I/O pin capacitance                                     | -                                                                                                     | -                                          | 5                  | -                                        | pF   |  |

| Table 50. I/C | static characteristics | (1) |

|---------------|------------------------|-----|

|---------------|------------------------|-----|

VDDSD12 is the external power supply for the PB10, and PE7 to PE15 I/O pins (the I/O pin ground is internally connected to VSS). VDDSD3 is the external power supply for PB14 to PB15 and PD8 to PD15 I/O pins (the I/O pin ground is internally connected to VSS). For those pins all V<sub>DD</sub> supply references in this table are related to their given VDDSDx power supply.

2. Guaranteed by design.

3. Leakage could be higher than maximum value, if negative current is injected on adjacent pins.

Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimal (~10% order).

Note:I/O pins are powered from V\_DD voltage except pins which can be used as SDADC inputs:- The PB10 and PE7 to PE15 I/O pins are powered from V\_DDSD12.

- PB14 to PB15 and PD8 to PD15 I/O pins are powered from V\_{DDSD3}. All I/O pin ground is internally connected to V\_{SS}.

$V_{DD}$  mentioned in the Table 50 represents power voltage for a given I/O pin ( $V_{DD}$  or  $V_{DDSD12}$  or  $V_{DDSD3}$ ).

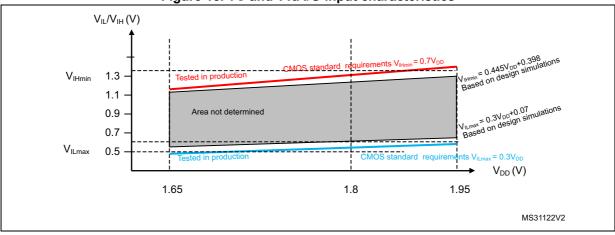

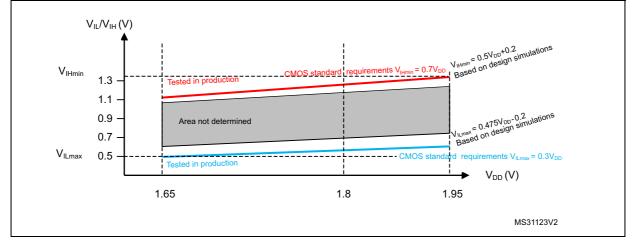

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology parameters. The coverage of these requirements is shown in *Figure 18* for standard I/Os, and in *Figure 19* for 5 V tolerant I/Os. The following curves are design simulation results, not tested in production.

Figure 18. TC and TTa I/O input characteristics

Figure 19. Five volt tolerant (FT and FTf) I/O input characteristics

## Output driving current

The GPIOs (general purpose input/outputs) can sink or source up to ± 8 mA, and sink or source up to ± 20 mA (with a relaxed  $V_{OL}/V_{OH})$ .

- ADC accuracy vs. negative injection current: Injecting a negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 6.3.13 does not

- affect the ADC accuracy.

- 3. Better performance may be achieved in restricted V<sub>DDA</sub>, frequency and temperature ranges.

- 4. Guaranteed by characterization results.

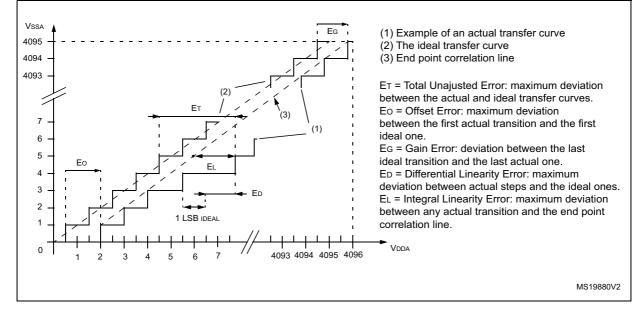

#### Figure 28. ADC accuracy characteristics

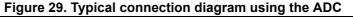

1. Refer to *Table* 59 for the values of  $R_{SRC}$ ,  $R_{ADC}$  and  $C_{ADC}$ .

C<sub>parasitic</sub> represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high C<sub>parasitic</sub> value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced.

## **General PCB design guidelines**

Power supply decoupling should be performed as shown in *Figure 10*. The 10 nF capacitor should be ceramic (good quality) and it should be placed as close as possible to the chip.

| Symbol                       | Parameter                               |                                                        |                  |                                        | ditions                     | laracteris                   | Min  | Тур  | Max  | Unit           | Note                                                                 |      |      |      |  |  |                              |   |   |      |   |  |

|------------------------------|-----------------------------------------|--------------------------------------------------------|------------------|----------------------------------------|-----------------------------|------------------------------|------|------|------|----------------|----------------------------------------------------------------------|------|------|------|--|--|------------------------------|---|---|------|---|--|

|                              | Analog                                  | One channel, gain = 0.5,<br>f <sub>ADC</sub> = 1.5 MHz |                  |                                        |                             |                              | -    | 540  | -    |                | see<br>reference                                                     |      |      |      |  |  |                              |   |   |      |   |  |

| Rain                         | input<br>impedance                      | On<br>M⊦                                               |                  | annel, gai                             | n = 0.5, f <sub>4</sub>     | <sub>ADC</sub> = 6           | -    | 135  | -    | kΩ             | manual for detailed                                                  |      |      |      |  |  |                              |   |   |      |   |  |

|                              |                                         | On                                                     | e ch             | annel, gai                             | n = 8, f <sub>AD</sub>      | <sub>C</sub> = 6 MHz         | -    | 47   | -    |                | description                                                          |      |      |      |  |  |                              |   |   |      |   |  |

| t <sub>CALIB</sub>           | Calibration time                        | f <sub>AD</sub>                                        | - C              | 6 MHz, on                              | e offset c                  | alibration                   | -    | 5120 | -    | μs             | 30720/f <sub>ADC</sub>                                               |      |      |      |  |  |                              |   |   |      |   |  |

| t <sub>STAB</sub>            | Stabilizatio<br>n time                  | Fro                                                    | om p             | ower dowi                              | n f <sub>ADC</sub> = 6      | MHz                          | -    | 100  | -    | μs             | 600/f <sub>ADC</sub> ,<br>75/f <sub>ADC</sub> if<br>SLOWCK<br>= 1    |      |      |      |  |  |                              |   |   |      |   |  |

|                              | Wakeup                                  | f <sub>AD</sub>                                        | <sub>C</sub> = 0 | 6 MHz                                  |                             |                              | -    | 50   | -    |                | 300/f <sub>ADC</sub>                                                 |      |      |      |  |  |                              |   |   |      |   |  |

| t <sub>STANDBY</sub>         | from<br>standby<br>time                 | f <sub>AD</sub>                                        | <sub>C</sub> =   | 1.5 MHz                                |                             |                              | -    | 50   | -    | μs             | 75/f <sub>ADC</sub> if<br>SLOWCK<br>= 1                              |      |      |      |  |  |                              |   |   |      |   |  |

|                              |                                         |                                                        |                  | f <sub>ADC</sub> =<br>1.5 MHz          |                             | V <sub>REFSD+</sub><br>= 3.3 | -    | -    | 110  |                | after offset<br>calibration                                          |      |      |      |  |  |                              |   |   |      |   |  |

|                              |                                         | e                                                      | gain = 1         | f <sub>ADC</sub> =<br>6 MHz            |                             | V <sub>REFSD+</sub><br>= 1.2 | -    | -    | 110  | -<br>-<br>- uV |                                                                      |      |      |      |  |  |                              |   |   |      |   |  |

|                              |                                         | Differential mode                                      | 0)               |                                        | V <sub>DDSDx</sub><br>= 3.3 | V <sub>REFSD+</sub><br>= 3.3 | -    | -    | 100  |                |                                                                      |      |      |      |  |  |                              |   |   |      |   |  |

|                              |                                         | fferenti                                               | gain = 8         | f <sub>ADC</sub> =                     |                             | V <sub>REFSD+</sub><br>= 1.2 | -    | -    | 70   |                |                                                                      |      |      |      |  |  |                              |   |   |      |   |  |

| 50                           | Offset                                  | D                                                      |                  | 6 MHz                                  |                             | V <sub>REFSD+</sub><br>= 3.3 | -    | -    | 100  |                |                                                                      |      |      |      |  |  |                              |   |   |      |   |  |

| EO                           | error                                   |                                                        |                  | f <sub>ADC</sub> =<br>1.5 MHz          |                             | V <sub>REFSD+</sub><br>= 3.3 | -    | -    | 90   |                |                                                                      |      |      |      |  |  |                              |   |   |      |   |  |

|                              |                                         |                                                        | =                |                                        |                             | V <sub>REFSD+</sub><br>= 1.2 | -    | -    | 2100 |                |                                                                      |      |      |      |  |  |                              |   |   |      |   |  |

|                              |                                         | mode                                                   | mode             | mode                                   | mode                        | mode                         | mode | mode | mode | mode           | mode                                                                 | mode | mode | gain |  |  | V <sub>REFSD+</sub><br>= 3.3 | - | - | 2000 | 1 |  |

|                              |                                         | ended                                                  | = 8              | _                                      |                             | V <sub>REFSD+</sub><br>= 1.2 | -    | -    | 1500 | -              |                                                                      |      |      |      |  |  |                              |   |   |      |   |  |

|                              |                                         | Single ended mode                                      | gain             |                                        |                             | V <sub>REFSD+</sub><br>= 3.3 | -    | -    | 1800 |                |                                                                      |      |      |      |  |  |                              |   |   |      |   |  |

| D <sub>voffsettem</sub><br>p | Offset drift<br>with<br>temperatur<br>e |                                                        |                  | ntial or sing<br>1, V <sub>DDSDx</sub> |                             | mode,                        | -    | 10   | 15   | uV/K           | -                                                                    |      |      |      |  |  |                              |   |   |      |   |  |

| EG                           | Gain error                              |                                                        |                  | s, differen<br>mode                    | tial mode                   | single                       | -2.4 | -2.7 | -3.1 | %              | negative<br>gain error =<br>data result<br>are greater<br>than ideal |      |      |      |  |  |                              |   |   |      |   |  |

Table 70. SDADC characteristics (continued)<sup>(1)</sup>

| Symbol | Parameter                             |                   |          | Conditions                    |                              | Min | Тур | Max | Unit       | Note |

|--------|---------------------------------------|-------------------|----------|-------------------------------|------------------------------|-----|-----|-----|------------|------|

| EGT    | Gain drift<br>with<br>temperatur<br>e |                   |          | 1, differential mode,<br>node | single                       | -   | 0   | -   | ppm<br>/K  | -    |

|        |                                       | ۵                 | -        |                               | V <sub>REFSD+</sub><br>= 1.2 | -   | -   | 16  |            |      |

|        |                                       | al mod            | gain = 1 |                               | V <sub>REFSD+</sub><br>= 3.3 | -   | -   | 14  |            |      |

|        |                                       | Differential mode | 8 =      |                               | V <sub>REFSD+</sub><br>= 1.2 | -   | -   | 26  |            |      |

|        | Integral                              | ā                 | gain =   | V - 2 2                       | V <sub>REFSD+</sub><br>= 3.3 | -   | -   | 14  |            |      |

| EL     | linearity<br>error <sup>(2)</sup>     | de                | -<br>-   | $V_{DDSDx} = 3.3$             | V <sub>REFSD+</sub><br>= 1.2 | -   | -   | 31  | - LSB<br>- | -    |

|        |                                       | Single ended mode | gain =   |                               | V <sub>REFSD+</sub><br>= 3.3 | -   | -   | 23  |            |      |

|        |                                       |                   | 8        |                               | V <sub>REFSD+</sub><br>= 1.2 | -   | -   | 80  |            |      |

|        |                                       |                   | gain     |                               | V <sub>REFSD+</sub><br>= 3.3 | -   | -   | 35  |            |      |

|        |                                       | Ð                 | -<br>-   |                               | V <sub>REFSD+</sub><br>= 1.2 | -   | -   | 2.4 |            | -    |

|        |                                       | Differential mode | gain :   |                               | V <sub>REFSD+</sub><br>= 3.3 | -   | -   | 1.8 | -<br>LSB   |      |

|        |                                       |                   | 8 =      |                               | V <sub>REFSD+</sub><br>= 1.2 | -   | -   | 3.6 |            |      |

| ED     | Differential                          |                   | gain :   | V - 2 2                       | V <sub>REFSD+</sub><br>= 3.3 | -   | -   | 2.9 |            |      |

| ED     | linearity<br>error                    | de                | -        | V <sub>DDSDx</sub> = 3.3      | V <sub>REFSD+</sub><br>= 1.2 | -   | -   | 3.2 |            |      |

|        |                                       | Single ended mode | gain = 1 |                               | V <sub>REFSD+</sub><br>= 3.3 | -   | -   | 2.8 |            |      |

|        |                                       |                   | 00<br>11 |                               | V <sub>REFSD+</sub><br>= 1.2 | -   | -   | 4.1 |            |      |

|        |                                       | Sin               | gain =   |                               | V <sub>REFSD+</sub><br>= 3.3 | -   | -   | 3.3 |            |      |

Table 70. SDADC characteristics (continued)<sup>(1)</sup>

| Symbol             | Parameter                |                   |          | Con                           | ditions                     |                                              | Min      | Тур      | Max      | Unit     | Note     |          |          |          |          |          |                    |  |                                              |    |    |   |  |  |

|--------------------|--------------------------|-------------------|----------|-------------------------------|-----------------------------|----------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|--------------------|--|----------------------------------------------|----|----|---|--|--|

|                    |                          |                   |          | f <sub>ADC</sub> =<br>1.5 MHz |                             | $V_{\text{REFSD+}} = 3.3^{(3)}$              | 84       | 85       | -        |          | -        |          |          |          |          |          |                    |  |                                              |    |    |   |  |  |

|                    |                          | e                 | gain = 1 | f <sub>ADC</sub> =            |                             | $V_{\text{REFSD}^+}$<br>= 1.2 <sup>(4)</sup> | 86       | 88       | -        |          |          |          |          |          |          |          |                    |  |                                              |    |    |   |  |  |

|                    |                          | Differential mode | 0,       | 6 MHz                         |                             | V <sub>REFSD+</sub><br>= 3.3                 | 88       | 92       | -        |          |          |          |          |          |          |          |                    |  |                                              |    |    |   |  |  |

|                    | Signal to<br>noise ratio | ifferent          | gain = 8 | f <sub>ADC</sub> =<br>6 MHz   |                             | $V_{\text{REFSD}^+}$<br>= 1.2 <sup>(4)</sup> | 76       | 78       | -        |          |          |          |          |          |          |          |                    |  |                                              |    |    |   |  |  |

|                    |                          | Ω                 |          |                               | V <sub>DDSDx</sub><br>= 3.3 | V <sub>REFSD+</sub><br>= 3.3                 | 82       | 86       | -        |          |          |          |          |          |          |          |                    |  |                                              |    |    |   |  |  |

| SNR <sup>(5)</sup> |                          |                   |          | f <sub>ADC</sub> =<br>1.5 MHz |                             | $V_{\text{REFSD}^+}$<br>= 3.3 <sup>(3)</sup> | 76       | 80       | -        | dB       |          |          |          |          |          |          |                    |  |                                              |    |    |   |  |  |

|                    |                          |                   | gain = 1 | f <sub>ADC</sub> =<br>1.5 MHz |                             | V <sub>REFSD+</sub><br>= 3.3                 | 80       | 84       | -        |          |          |          |          |          |          |          |                    |  |                                              |    |    |   |  |  |

|                    |                          | ended mode        |          | jain = 1                      | jain = 1                    | jain = 1                                     | jain = 1 | jain = 1 | jain = 1 | jain = 1 | jain = 1 | jain = 1 | jain = 1 | jain = 1 | jain = 1 | gain = 1 | f <sub>ADC</sub> = |  | $V_{\text{REFSD}^+}$<br>= 1.2 <sup>(4)</sup> | 77 | 81 | - |  |  |

|                    |                          |                   |          | 6 MHz                         |                             | V <sub>REFSD+</sub><br>= 3.3                 | 85       | 90       | -        |          |          |          |          |          |          |          |                    |  |                                              |    |    |   |  |  |

|                    |                          | Single (          | = 8      | f <sub>ADC</sub> =<br>6 MHz   |                             | $V_{\text{REFSD}^+}$<br>= 1.2 <sup>(4)</sup> | 66       | 71       | -        |          |          |          |          |          |          |          |                    |  |                                              |    |    |   |  |  |

|                    |                          |                   | gain =   |                               |                             | V <sub>REFSD+</sub><br>= 3.3                 | 74       | 78       | -        | ]        |          |          |          |          |          |          |                    |  |                                              |    |    |   |  |  |

Table 70. SDADC characteristics (continued)<sup>(1)</sup>

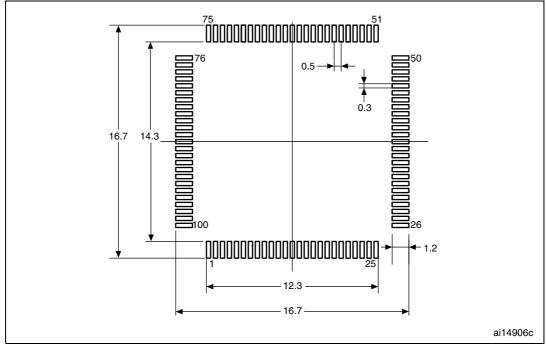

# Figure 38. LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

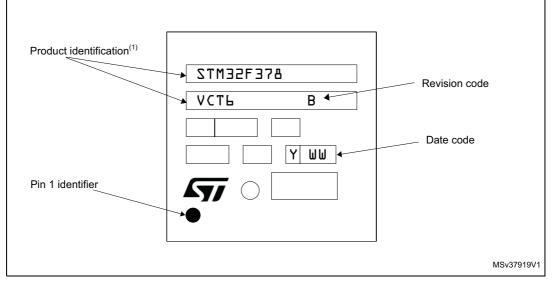

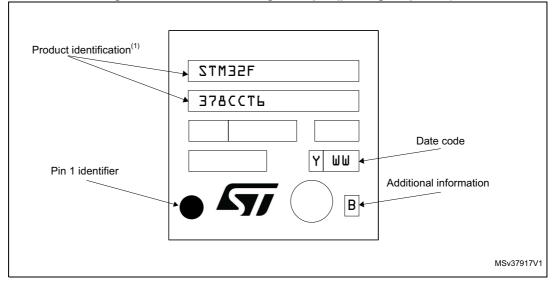

## Device marking for LQFP100

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

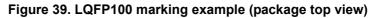

# Figure 44. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

#### **Device marking for LQFP48**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 45. LQFP48 marking example (package top view)

Samples marked "ES" are to be considered as "Engineering Samples": i.e. they are intended to be sent to customer for electrical compatibility evaluation and may be used to start customer qualification where specifically authorized by ST in writing. In no event ST will be liable for any customer usage in production. Only if ST has authorized in writing the customer qualification Engineering Samples can be used for reliability qualification trials.

# 7.6 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 22: General operating conditions*.

The maximum chip-junction temperature,  $T_{\rm J}$  max, in degrees Celsius, may be calculated using the following equation:

$T_J max = T_A max + (P_D max x Q_{JA})$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- Q<sub>JA</sub> is the package junction-to-ambient thermal resistance, in °C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

$P_{I/O}$  max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I/O}} \max = \mathsf{S} \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \mathsf{S}((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol        | Parameter                                                                        | Value | Unit |

|---------------|----------------------------------------------------------------------------------|-------|------|

|               | <b>Thermal resistance junction-ambient</b><br>LQFP64 - 10 × 10 mm / 0.5 mm pitch | 45    |      |

|               | <b>Thermal resistance junction-ambient</b><br>LQFP48 - 7 × 7 mm                  | 55    |      |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP100 - 14 × 14 mm / 0.5 mm pitch       | 46    | °C/W |

|               | Thermal resistance junction-ambient<br>BGA100 - 7 x 7 mm                         | 59    |      |

|               | Thermal resistance junction-ambient<br>WLCSP66 - 0.400 mm                        | 53    |      |

#### Table 78. Package thermal characteristics

#### 7.6.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org